中断1

中断响应过程1

中断: ② 调用入口地址,断点入栈,相当于LCALL指令; ③ 进入中断服务程序。

中断处理

• 中断处理就是执行中断服务程序,从中断入口地 址开始执行,直到返回指令(RETI)为止。此过程 一般包括三部分内容,一是保护现场,二是处理 中断源的请求,三是恢复现场。

• 通常,主程序和中断服务程序都会用到累加器A、 状态寄存器PSW及其他一些寄存器。在执行中断服 务程序时,CPU若用到上述寄存器,就会破坏原先 存在这些寄存器中的内容,中断返回,将会造成 主程序的混乱。因此,在进入中断服务程序后, 一般要先保护现场,然后再执行中断处理程序, 在返回主程序以前,再恢复现场。

中断可实现两级中断嵌套。高优先级中断源可中断正在执行的 低优先级中断服务程序,除非执行了低优先级中断服务程序的 CPU关中断指令。同级或低优先级的中断不能中断正在执行的 中断服务程序。

1. CPU的中断响应条件

CPU响应中断必须首先满足以下三个基本条件。 (1) 有中断源发出中断请求。 (2) 中断总允许位EA=1。 (3) 请求中断的中断源的中断允许位为1。

中断处理可以分为 中断请求

中断响应 中断处理 中断返回

四个过程

1.中断请求

若有多个中断源,CPU就需要判断优先级 ⅰ当同时有多个中断请求信号,先响应优先级别高的中断请求。 ⅱ高优先级中断请求信号可中断低优先级中断服务。

2. 中断优先级的判定

中断源的优先级别分为高级和低级,通过由软件设置中断优先 级寄存器IP相关位来设定每个中断源的级别。 如果几个同一优先级别的中断源同时向CPU请求中断,CPU通 过硬件查询电路首先响应自然优先级较高的中断源的中断请求。

• 中断返回通过执行中断返回指令RETI来实现,该 指令的功能是首先将相应的优先级状态触发器置0, 以开放同级别中断源的中断请求;其次,从堆栈 区把断点地址取出,送回到程序计数器PC中。因 此,不能用RET指令代替RETI指令。

INT0及INT1中断计数

湖南科技大学潇湘学院课程设计课程设计名称:《单片机接口技术》课程设计题目: INT0及INT1的中断计数学生姓名:学院:专业及班级:学号:指导教师:2016 年 12月 19日摘要单片机的外部中断有两种触发方式可选:电平触发和边沿触发。

电平触发方式时,中断标志寄存器不锁存中断请求信号。

也就是说,单片机把每个机器周期的S5P2采样到的外部中断源口线的电平逻辑直接赋值到中断标志寄存器。

标志寄存器对于请求信号来说是透明的。

这样当中断请求被阻塞而没有得到及时响应时,将被丢失。

换句话说,要使电平触发的中断被CPU响应并执行,必须保证外部中断源口线的低电平维持到中断被执行为止。

因此当CPU正在执行同级中断或更高级中断期间,产生的外部中断源(产生低电平)如果在该中断执行完毕之前撤销(变为高电平)了,那么将得不到响应,就如同没发生一样。

同样,当CPU在执行不可被中断的指令(如RETI)时,产生的电平触发中断如果时间太短,也得不到执行。

边沿触发方式时,中断标志寄存器锁存了中断请求。

中断口线上一个从高到低的跳变将记录在标志寄存器中,直到CPU响应并转向该中断服务程序时,由硬件自动清除。

因此当CPU正在执行同级中断(甚至是外部中断本身)或高级中断时,产生的外部中断(负跳变)同样将被记录在中断标志寄存器中。

在该中断退出后,将被响应执行。

如果你不希望这样,必须在中断退出之前,手工清除外部中断标志。

一个中断如果在没有到响应之前就已经被手工清除,则该中断将被CPU忽略。

就如同没有发生一样。

目录1设计要求及目的 .............................................. .. (1)1.1 设计要求INT0及INT1中断计数................................................ .11.2 设计目的................................................ (1)2 方案设计和选择................................................ (1)2.1原件选择................................................ .. (1)2.1.1单片机的选择................................................ ...................1-33 调试过程................................................ (3)3.1软件调试................................................ .........................3-64 心得体会................................................ .. (6)5 参考文献................................................ .. (7)第一章设计要求和目的1.1 设计要求INT0及INT1中断计数(1)每次按下第1个计数键时,第1组计数值累加并显示在右边3只数码管上(2)每次按下第2个计数键时,第2组计数值累加并显示在左边3只数码管上(3)后两个按键分别清零 1.2 设计目的本设计的目的是为提高自己的实际动手能力以及对外部中断的原理和单片机C51语言的相关知识有更深刻理解。

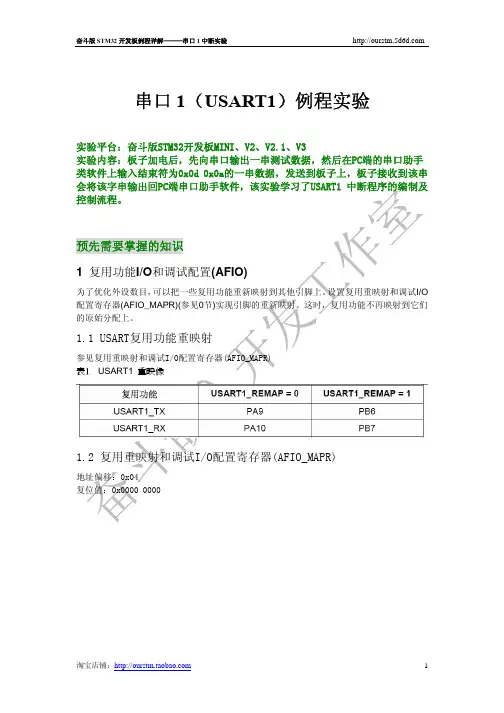

奋斗STM32开发板串口1中断例程详解及实验手册

淘宝店铺:

8

奋斗版 STM32 开发板例程详解———串口 1 中断实验

应答起始位。发送和接收由一共用的波特率发生器驱动,当发送器和接收器的使能位分别置 位时,分别为其产生时钟。每个功能块的详细资料如下给出。 图2 字长设置

单字节通信

清零TXE 位总是通过对数据寄存器的写操作来完成的。TXE 位由硬件来设置,它表明: ● 数据已经从TDR 移送到移位寄存器,数据发送已经开始 ● TDR 寄存器被清空 ● 下一个数据可以被写进USART_DR 寄存器而不会覆盖先前的数据如果TXEIE 位被设置,此 标志将产生一个中断。如果此时USART 正在发送数据,对USART_DR 寄存器的写操作把数据 存进TDR 寄存器,并在当前传输结束时把该数据复制进移位寄存器。如果此时USART 没有在 发送数据,处于空闲状态,对USART_DR 寄存器的写操作直接把数据放进移位寄存器,数据 传输开始,TXE 位立即被置起。当一帧发送完成时(停止位发送后),TC 位被置起,并且 如果USART_CR1 寄存器中的TCIE 位被置起时,中断产生。先读一下USART_SR 寄存器,再写 一下USART_DR 寄存器,可以完成对TC 位的清零。 注意: TC 位也可以通过对它软件写0 来清除。此清零方式只在多缓冲器通信模式 下推荐使用。

断开符号

淘宝店铺:

10

奋斗版 STM32 开发板例程详解———串口 1 中断实验

置位SBK位可发送一个断开符号。断开帧长度取决M位(见图166)。如果SBK位被置1,在完成 当前数据发送后,将在TX线上发送一个断开符号。断开字符发送完成时(在断开符号的停止 位时)SBK被硬件复位。USART在最后一个断开帧的结束处插入一逻辑1 位,以保证能识别下 一帧的起始位。 注意:如果在开始发送断开帧之前,软件又复位了SBK 位,断开符号将不被发送。如果要发 送两个连续的断开帧,SBK 位应该在前一个断开符号的停止位之后置起。

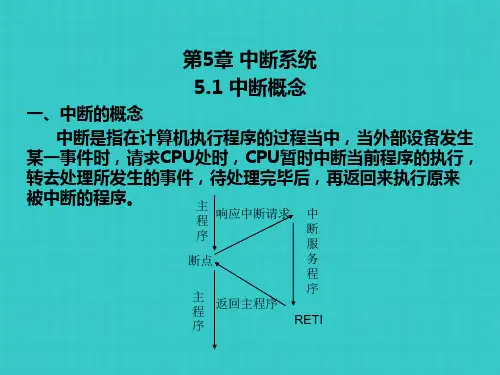

中断系统中断概念一中断的概念中断是指在计算机执行

中断源

入口地址

INT0

0003H

T0

000BH

INT1

0013H

T1

001BH

串行口

0023H

(5)中断返回

S(E串ETM串串5(1.FEXSO)1行行行用10T:)V串:B口 口 口字EI行定自PEX节,T口#1时然00操:外中8/优计作HR断部先数指X允中级D器令00许断00:(T22控0133),中外HH制T断部位X标D中志(断位1)中断允许控制位

5.5 中断优先级控制 1、中断优先级寄存器

IP

BCH BCH BBH BAH B9H B8H

B8H X X X PS PT1 PX1 PT0 PX0

高优先级

MCS-51系列单片机有两级中断级

低优先级

PX0,PT0,PX1,PT1,PS分别为INT0,T0,INT1,T1 串行口中断优先级控制位,当相应位为0时为低优先级,相应 为1时为高优先级。

例5 .2 要将T1定时器定义为最高优先级,其他中断定义为低 优先级,如何设置IP?

(1M M)用OO字VV 节AIE操8,H作,##指88E令EHH E串串 例串P中IT串(TCTRRTUP0行行:行断行1000US:)::口 口口 源 口HE响外置TI定定应N1部相PT时时,中ES_中应//TWT断计计断2R的0:后数数:X定0优D触,器器00入0时先000(发于TT口222计级00333)方中地运 运数HHH触式断T址行行器发X选返控控TD器0择回制制(,状T前位位1)态,,T为2应中1该断撤控销制中位断请求。 (2S)E用T位B E操A作 P中生S…ITUE1断的…TS:B是 事 .H外E指件部TP在,1S中W计待断算处0机理触执完发行毕方程后式序,选的再择过返程回当来中执,行当原外来部被设中备断发的生程某序一。事件时,请求CPU处时,CPU暂时中断当前程序的执行,转去处理所发 SSSEEETTTBBB EEETTX010 EI(P先为ST中S1中生N0EXES假4级了断断的T0TT:)1串设,BB。 使 处 是 事转行允PEE这理指件T入TA口许些过在,00相中,打单程计待应断P开0元可算处X0的允0I的分机理01N0中B许,1T值为执完H31断控PH在三行毕及T服制1中个程后定,务位断阶序,时P程程段的再器S序分序:过返T入0别中中程回,T口为不断当来1,I禁被响中执NT止冲应,行0其,掉,当原他T,中外来0中在断部被,断进处设中IN,入理备断T试1中,发的设,断中生程置T1服断某序IE串务返一。. 行程回事口序。件中前时断,,优要请先将求级有C控P关U制寄处位存时,器,当保C相P护U应起暂位来时为。中0断时当为前低程优序先的级执,行相,应转为去1时处为理高所优发

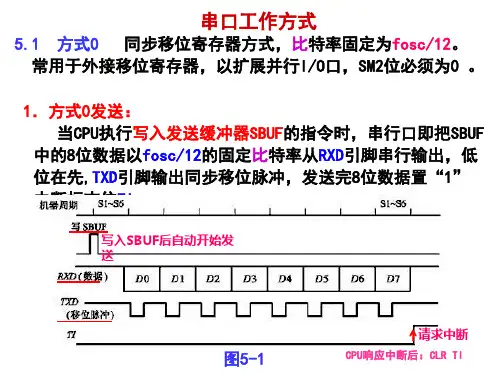

51单片机串口工作方式0和1解析

RXD

7.1.1 串行口控制寄存器SCON b7 b6 b5 b4 b3 b2 b1 TI b0 RI

SM0 SM1 SM2 REN TB8 RB8

9FH 9EH 9DH 9CH 9BH 9AH 99H 98H

SM0、SM1 —— 串行接口工作方式定义位

• SM0、SM1 = 00 —— 方式 0,8位同步移位寄存器 • SM0、SM1 = 01 —— 方式 1,10 位异步接收发送 • SM0、SM1 = 10 —— 方式 2,11 位异步接收发送 • SM0、SM1 = 11 —— 方式 3,11 位异步接收发送 注意: 方式 0 的特点,方式 2、方式 3 的差异

寄存器 SCON、PCON、SBUF

寄存器 IE、IP

• MCS-51 单片机串Fra bibliotek接口工作方式 方式 0 方式 2 方式 1 方式 3

有两个数据缓冲寄存器 SBUF,一个输入移位寄存器,一个 串行控制寄存器SCON和一个特殊功能寄存器PCON等组成。 8 位SBUF是全双工串行接口寄存器, 它是特殊功能寄存器, 地址为 99H,不可位寻址;串行输出时为发送数据缓冲器,发送

时钟振荡频率为6MHz或12 MHz时,产生的比特率偏差较大, 故用到串口通信时通常选用11.0592MHZ晶体振荡器。

串行口的结构

• MCS-51 单片机串行接口的硬件

P3.0 位的第二功能 —— 收端 RXD P3.1 位的第二功能 —— 发端 TXD

• MCS-51 单片机串行接口的控制

比特率 比特率

= /12

P.110

=

/32 计1次 计3次 计3次 计6次 计12次 计24次

=

/12/计次/16

单片机实验IRQ0IRQ1IRQ2中断

*P_IOA_Data = 0x0000;

*P_IOB_Dir = 0x000f;

*P_IOB_Attrib = 0x000f;

*P_IOB_Data = 0x0000;

//设置定时器A、B的属性

*P_TimerA_Ctrl = C_TMA1_4KHz | C_TMA2_1;

asm("INT IRQ");//开IRQ中断

while (1){

*P_Watchdog_Clear = C_WDTCLR;

}

return 0;

}

//isr.c

#include "SPCE061A.h"

void BREAK(void) __attribute__ ((ISR));

void FIQ(void) __attribute__ ((ISR));

后,翻转IOB口低四位输出电平以控制接在IOB低四位端口的发光二极管。程序运行时,可以

观察到接在IOA低四位端口的发光二极管亮灭的周期为4s,而接在IOB低四位端口的为2s【实验原理】

【实验原理】

IRQ0_fosc/1024、IRQ1_TMA、IRQ2_TMB中断源,通过写P_INT_Ctrl来允许中断,通过IRQ ON、

1、实验中遇到的问题及解决办法

答:1、问题:对不同中断信号频率的设置需要符合程序运行的方式,LED灯的闪烁频率太快时就无法看见其在闪烁,交替闪烁的快慢也会随之变化,在程序的编写上要严格按照规则编写,否则就会出错,因此在实验中一定要弄清楚其缘由。

2、解决方法:通过实际的计算测量。老师的引导,同学之间的相互交流沟通学习,一步步的完成了此实验,并在老师的详细讲解下熟悉了个窗口的功能及硬件的了解和正确的连接,做出与实验目的相符合的结果。

1系统中断与时钟节拍

1 系统中断与时钟节拍1.1 系统中断中断是种硬件机制用于通知CPU有个异步事件发生了中断旦被系统识别CPU则保存部分(或全部)现场(context)即部分(或全部)寄存器值跳转到专门子称为中断服务子(ISR)中断服务子做事件处理处理完成后执行任务调度回到就绪态优先级最高任务开始运行(对于可剥夺型内核)中断使得CPU可以在事件发生时才予以处理而不必让微处理器连续不断地查询(polling)是否有事件发生通过两条特殊指令:关中断(disable errupt)和开中断(enable errupt)可以让微处理器不响应或响应中断在实时环境中关中断时间应尽量短关中断影响中断响应时间关中断时间太长可能会引起中断丢失中断服务处理时间应该尽可能短中断服务所做事情应该尽可能少应把大部分工作留给任务去做1.2 系统时钟节拍时钟节拍是特定周期性中断(时钟中断)这个中断可以看作是系统心脏脉动操作系统通过时钟中断来确定时间间隔实现时间延时及确定任务超时中断之间时间间隔取决于不同应用般在10~200 ms之间时钟节拍式中断使得内核可以将任务延时若干个整数时钟节拍以及当任务等待事件发生时提供等待超时依据时钟节拍频率越快系统额外开销就越大系统定义了32位无符号整数OSTime来记录系统启动后时钟滴答数目用户必须在多任务系统启动以后再开启时钟节拍器也就是在OSStart之后μC/OSII中时钟节拍服务是通过在中断服务子中OSTimeTick实现时钟节拍中断服务子示意代码如下:void OSTickISR(void) {保存处理器寄存器值;OSIntEnter 或是将OSIntNesting加1;OSTimeTick ;OSIntExit ;恢复处理器寄存器值;执行中断返回指令;}2 时钟管理系统2.1 μC/OSII时钟管理系统μC/OSII原有时钟管理系统类似于Linux但是比Linux简单得多它仅向用户提供个周期性信号OSTime时钟频率可以设置在10~100 Hz时钟硬件周期性地向CPU发出时钟中断系统周期性响应时钟中断每次时钟中断到来时中断处理更新个全局变量OSTimeμC/OSII时钟中断服务核心是OSTimeTick OSTimeTick 用来判断延时任务是否延时结束从而将其置于就绪态其伪代码如下:void OSTimeTick(void) {OSTimeTickHook;// 用户定义时钟节拍外连while { (除空闲任务外所有任务)OS_ENTER_CRITICAL;//关中断对所有任务延时时间递减;扫描时间到期任务并且唤醒该任务;OS_EXIT_CRITICAL;//开中断指针指向下个任务;}OSTime;//累计从开机以来时间}在μC/OSII时钟节拍中需要执行用户定义时钟节拍外连OSTimeTickHook 以及对任务链表进行扫描并且递减任务延时这样就造成了时钟节拍OSTimeTick 有两点不足:①在时钟中断中处理额外任务OSTimeIickHook 这样增加了中断处理负担影响了定时服务准确性;②在关中断情况下扫描任务链表任务越多所需要时间越长而长时间关中断对中断响应有不利影响是中断处理应当避免2.2 改进时钟管理系统针对上述OSTimeTick 不足之处需加以改进来优化时钟节拍在Linux中般对中断响应分为两部分:立即中断服务和底半中断处理(bottom half)立即中断服务仅仅做重要并且能快速完成工作而把不太重要需要较长时间完成工作放在底半处理部分来完成这样就可以提高中断响应速度μC/OSII不支持底半处理为了减轻时钟中断处理工作量来提高μC/OSII时钟精确度可以将部分在每次时钟中断需处理工作内容放在任务级来完成这样就可以减少每次时钟中断处理CPU消耗从而提高中断响应速度和μC/OSII时钟精确度为此定义任务OSTimeTask 由它来处理原来在OSTimeTick中需要处理操作μC/OSII采用基于优先级抢占式调度策略而每次时钟中断处理结束后需要首先调度该任务执行因此让任务OSTimeTask具有系统内最高优先级由它执行用户定义时钟节拍外连OSTimeTickHook 以及对所有任务延时时间进行递减并把到期任务链入到链表OSTCBRList中OSTCBRList管理所有到期任务OSTimeTask伪代码如下:void OSTimeTask {OSTimeTickHook//用户定义时间处理while { (除空闲任务外所有任务)对所有任务延时时间进行递减;把所有要到期任务链入到OSTCBRList链表中;} 任务状态改为睡眠OSSched 进行任务调度;}在任务OSTimeTask中执行原来在时钟中断处理用户OSTimeIickHook 并实现将延时到期任务链入到OSTCBRList链表中这样在时钟中断中就只需要扫描任务到期链表而不需要扫描整个链表减少了关中断时间,OSTCBRList为新建链表它管理所有到期任务,同时需要减少OSTimeTick 执行工作量只对OSTCBRList链表扫描这样也减少了关中断时间OSTimeTick 伪代码如下:void OSTimeTick(void) {OSTime;OS_TCB* ptcb=OSTCBList;// OSTCBRList指向所有到期任务链表while(ptchb!=null){关中断;唤醒任务;开中断;指针指向下个任务;}}。

usart1中断方式

| RCC_APB2Periph_AFIO, ENABLE);

在此说明,不用设置RCC_APB2Periph_AFIO也是可以的,也就是在此没有使用复用功能。

if(RxCounter == NbrOfDataToRead)

{

/* Disable the USART Receive interrupt */

USART_ITConfig(USART1, USART_IT_RXNE, DISABLE);

}

}

}

}

至此程序就结束了。

我们就会有个疑问,main()只包括前三个步骤的初始化和一个死循环,那么中断又是如何触发的呢,main()的结构如下:

int main(void)

{

/* System Clocks Configuration */

RCC_Configuration();

{

/* Write one byte to the transmit data register */

USART_SendData(USART1, TxBuffer[TxCounter++]);

if(TxCounter == NbrOfDataToTransfer)

}

if(USART_GetITStatus(USART1, USART_IT_TXE) != RESET)

{

/* Write one byte to the transmit data register */

INT0及INT1中断计数

湖南科技大学潇湘学院课程设计课程设计名称:《单片机接口技术》课程设计题目: INT0及INT1的中断计数学生姓名:学院:专业及班级:学号:指导教师:2016 年 12月 19日摘要单片机的外部中断有两种触发方式可选:电平触发和边沿触发。

电平触发方式时,中断标志寄存器不锁存中断请求信号。

也就是说,单片机把每个机器周期的S5P2采样到的外部中断源口线的电平逻辑直接赋值到中断标志寄存器。

标志寄存器对于请求信号来说是透明的。

这样当中断请求被阻塞而没有得到及时响应时,将被丢失。

换句话说,要使电平触发的中断被CPU响应并执行,必须保证外部中断源口线的低电平维持到中断被执行为止。

因此当CPU正在执行同级中断或更高级中断期间,产生的外部中断源(产生低电平)如果在该中断执行完毕之前撤销(变为高电平)了,那么将得不到响应,就如同没发生一样。

同样,当CPU在执行不可被中断的指令(如RETI)时,产生的电平触发中断如果时间太短,也得不到执行。

边沿触发方式时,中断标志寄存器锁存了中断请求。

中断口线上一个从高到低的跳变将记录在标志寄存器中,直到CPU响应并转向该中断服务程序时,由硬件自动清除。

因此当CPU正在执行同级中断(甚至是外部中断本身)或高级中断时,产生的外部中断(负跳变)同样将被记录在中断标志寄存器中。

在该中断退出后,将被响应执行。

如果你不希望这样,必须在中断退出之前,手工清除外部中断标志。

一个中断如果在没有到响应之前就已经被手工清除,则该中断将被CPU忽略。

就如同没有发生一样。

目录1设计要求及目的 ......................................... . (1)1.1 设计要求INT0及INT1中断计数........................................... (1)1.2 设计目的............................................ . (1)2 方案设计和选择........................................... .. (1)2.1原件选择............................................ (1)2.1.1单片机的选择............................................ .......................1-33 调试过程........................................... . (3)3.1软件调试............................................ .............................3-64 心得体会........................................... . (6)5 参考文献........................................... . (7)第一章设计要求和目的1.1 设计要求INT0及INT1中断计数(1)每次按下第1个计数键时,第1组计数值累加并显示在右边3只数码管上(2)每次按下第2个计数键时,第2组计数值累加并显示在左边3只数码管上(3)后两个按键分别清零 1.2 设计目的本设计的目的是为提高自己的实际动手能力以及对外部中断的原理和单片机C51语言的相关知识有更深刻理解。

计算机组成原理中断名词解释(一)

计算机组成原理中断名词解释(一)计算机组成原理中断1. 什么是中断•定义:中断是计算机系统中一种可以改变程序执行流程的事件,可以打断正在执行的程序,并将控制权转移给特定处理程序。

•例子:当一个设备完成了对CPU的请求并需要CPU进行响应时,它会发送一个中断信号,中断处理程序会被触发以处理设备的请求。

2. 中断控制器•定义:中断控制器是计算机系统中的一个硬件设备,它负责将来自不同设备的中断信号进行调度,并确定是否将其传递给CPU进行处理。

•例子:8259A是Intel x86计算机系统中常用的中断控制器,它可以处理多个不同类型的中断,并按优先级将它们传递给CPU。

3. 中断向量表•定义:中断向量表是记录不同中断类型对应中断处理程序入口地址的数据结构,每个中断类型有一个对应的中断向量表项,通常是一个指向中断处理程序的指针。

•例子:在x86架构中,中断向量表是一个位于内存中的256个入口的数组,每个入口存储着对应中断处理程序的地址。

4. 中断处理程序•定义:中断处理程序是一段特定的代码,用于处理特定类型的中断事件。

它会在中断发生时被中断处理器调用,以执行相应的处理逻辑。

•例子:当用户按下键盘上的某个键时,操作系统的键盘中断处理程序会被触发,它会读取键盘输入并将其传递给相应的应用程序。

5. 中断请求线•定义:中断请求线是用于将中断信号通知中断控制器的硬件线路。

不同设备通常使用不同的中断请求线,中断控制器通过检测这些线路上的信号来确定哪些设备发出了中断请求。

•例子:在x86系统中,IRQ0是时钟中断请求线,IRQ1是键盘中断请求线。

6. 中断屏蔽•定义:中断屏蔽是一种机制,通过控制中断控制器,禁止特定的中断类型触发中断处理程序,以防止干扰正在执行的关键任务。

•例子:当计算机执行特定的任务时,操作系统可以屏蔽所有硬盘中断,以确保任务不会被硬盘中断打断。

7. 异常•定义:异常是一种特殊的中断类型,通常指的是由软件错误或非法操作引起的中断事件。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

每个仲裁器可以处理基于 1 位仲裁器模式控制(ARB_MODE) 和选择控制信号(ARB_SEL)的 2 位的 6 个中断请求,如下

如果 ARB_SEL 位为 00b,优先级顺序为 REQ0、REQ1、REQ2、 REQ3、REQ4 和 REQ5。 如果 ARB_SEL 位为 01b,优先级顺序为 REQ0、REQ2、REQ3、 REQ4、REQ1 和 REQ5。 如果 ARB_SEL 位为 10b,优先级顺序为 REQ0、REQ3、REQ4、 REQ1、REQ2 和 REQ5。 如果 ARB_SEL 位为 11b,优先级顺序为 REQ0、REQ4、REQ1、 REQ2、REQ3 和 REQ5。 仲裁器的 REQ0 的优先级总是最高并且 REQ5 的优先级总是最低 有时嵌入式系统里要在外部接口上挂载一些外部设备,这些设备并不是一 个通用嵌入式系统里必备硬件,比如:蓝牙模块,各种传感器,WIFI无线通信 模块,这些硬件也要产生中断让CPU来处理数据,因此这些外设硬件通过中断 信号线连接到中断控制器上,它们产生的中断叫做外部中断信号。它们有着和 内部中断一样的处理机制,只不过,它没有一个固定的中断号与之对应,硬件 与嵌入式系统的连接方式与中断处理完全由系统硬件与软件设计者实现。

是计算机分时操作系统在处理多个作业程序时,决 定各个作业程序接受系统资源的优先等级的参数。

S3C2440支持60种中断,多个硬件可能同 时产生中断请求,由于CPU只能处理一个 中断,中断控制器怎么选择出一个最佳的 中断,交给ARM内核进行处理呢? 中断 控制器采用优先级仲裁比较的方式进行选 择,找出优先级最高的中断源。中断控制 器将60种中断源分成7组,如右图所示, 它类似体育赛事里的比赛方式,所有参赛 选手在小组赛PK,选择出小组赛最优秀选 手,然后进入决赛阶段和其它小组最优先 选择再PK,最后优胜者就是总冠军。其中 ARBITER0~ARBITER5为“小组赛”阶段, 中断源信号在各自小组里进行优先级仲裁, 选择出最高优先级中断信号,每小组选出 的中断信号送到ARBITER6,也就是决赛 阶段,选择出最高优先级中断信号,交给 ARM内核。

假如我们正在看书,突然电话响 了。我们要去接电话。接完电话继续 看书。生活中有很多中断的例子。

是指cpu在正常运行程序时,由于内部或 外部事件引起cpu暂时中止执行现行程序, 转去执行另一程序,处理发生的事件,处 理完毕后又自动返回原来的程序继续运行。

中断请求由硬件产生,根据中断源类型分别将中断信号送到 SUBSRCPND(SubSourcePending)和SRCPND(SourcePending) 寄存器,SUBSRCPND是子中断源暂存寄存器,用来保存子中断源信 号,SRCPND是中断源暂存寄存器,用来保存中断源信号。中断信号 可通过编程方式屏蔽掉,SUBMASK是子中断源屏蔽寄存器,可以屏 蔽指定的子中断信号, MASK功能同SUBMASK用来屏蔽中断源信号。 中断分为两种模式:一般中断IRQ和快速中断FIQ,MODE是中断模式 判断寄存器,用来判断当前中断是否为快速中断,如果为快速中断直 接将快速中断信号送给ARM内核,如果不是快速中断,还要将中断信 号进行仲裁选择。S3C2440A支持多达60种中断,很有可能多个硬件 同时产生中断请求,这时要求中断控制器做出裁决,Priority是中断源 优先级仲裁选择器,当多个中断产生时,选择出优先级最高的中断源 进行处理,INTPND是中断源结果寄存器,里面存放优先级仲裁出的 唯一中断源。