任务3 VHDL的赋值语句

任务3 VHDL的赋值语句

x

选择信号赋值语句( With_Select_When )

所有的“WHEN”子句必须是互斥的 一般用

“When Others”来处理未考虑 到的情况 (<=)

只有一个参考信号和赋值符

Y=ab+

cd

ENTITY logic IS ――实体说明,定义实体名为logic PORT( a,b,c,d:IN BIT; ――输入端口说明 y :OUT BIT); ――输出端口说明 END logic; ――定义a,b,c,d是输入端口信号,y是输出端口信号 ARCHITECTURE jia OF logic IS SIGNAL e,f:BIT; ――定义e,f是内部信号 BEGIN f ﹤﹦ a AND b; ――以下三条并行语句与顺序无关 y﹤﹦ f OR e; e﹤﹦c XOR d; END jia;

进行的,或者说是并行运行的,其执行 方式与书写的顺序无关。

来,也可以是互为独立、互不相关、异 步运行的(如多时钟情况)。

在执行中,并行语句之间可以有信息往

每一并行语句内部的语句运行方式可以

有两种不同的方式,即并行执行方式(如 块语句)和顺序执行方式(如进程语句)。

Architecture

Begin

j <= w when x when y when z when ‘0 ’ ; (a (b (c (d = = = = ‘1 ’) ‘1 ’) ‘1 ’) ‘1 ’) else else else else

允许有多个 控制信号

选择信号赋值语句(With_Select_When)

语法格式:

WITH selection_signal SELECT signal_name <= value_1 WHEN value_2 WHEN ... value_n WHEN value_x WHEN

VHDL基本语句

例

ARCHITECTURE example OF mux4 IS BEGIN PROCESS (sel) 注 BEGIN ●CASE中的选择值必须在表达式的取值范围内; CASE sel IS WHEN 0=> q <= d0 ; ●CASE语句是无序的,所有表达式值都是并行 WHEN 1=> q <= d1 ; 处理;而IF语句是有序的,最起始、最优先 WHEN 2=> q<= d3 ; WHEN 3=> q<= d4 ; 的先处理; WHEN others => NULL; ●可以有很多分支,但OTHERS分支只能有一个, END CASE; 且只能位于最后;用来使所有选择值能涵盖表 END PROCESS; END example; 达式的所有取值,以免插入不必要的锁存器

3、用于多选控制的IF语句:

格式 IF 条件1 THEN

<顺序处理语句1>;

ELSIF 条件2 THEN <顺序处理语句2>; : ELSIF 条件n-1 THEN <顺序处理语句n-1>; ELSE <顺序处理语句n>; END IF;

P1: PROCESS (clk) BEGIN

IF (clk‘ event and clk=‗1‘ ) THEN

顺序语句

赋值语句

VHDL设计实体内的数据传递以及对端口界面外部数据的读写 都必须通过赋值语句的运行来实现。 功能是将一个值或表达式的运算结果传递给某一数据对象。 赋值语句有两种: 信号赋值语句和变量赋值语句 区别

任务3VHDL的赋值语句

说明语句

构

造

功能描述语句

体

块语句

结

进程语句

构

信号赋值语句

图

子程序调用语句

元件例化语句

并行语句

构 造 体

并行语句1 signal

并行语句2 signal

并行语句3

并行语句

各种并行语句在结构体中的执行是同步 进行的,或者说是并行运行的,其执行 方式与书写的顺序无关。

在执行中,并行语句之间可以有信息往 来,也可以是互为独立、互不相关、异 步运行的(如多时钟情况)。

s

例:4 选 1 数据选择器

2

a b

c

Architecture a of mux4_1 is d

Begin

mux x

x <= (a AND NOT(s(1)) AND NOT(s(0))) OR

(b AND NOT(s(1)) AND s(0)) OR

(c AND s(1) AND NOT(s(0))) OR

j <= w when (a = ‘1’) else x when (b = ‘1’) else y when (c = ‘1’) else z when (d = ‘1’) else ‘0’ ;

允许有多个 控制信号

选择信号赋值语句(With_Select_When)

语法格式:

WITH selection_signal SELECT signal_name <= value_1 WHEN value_a, value_2 WHEN value_b, ... value_n WHEN value_n, value_x WHEN OTHERS;

WHEN “00”=>y<=‘1’; --当ab=00时,y=1

vhdl条件赋值语句

vhdl条件赋值语句vhdl是一种硬件描述语言,用于描述硬件电路的行为和结构。

在vhdl中,条件赋值语句是一种常用的语法结构,用于根据特定条件给变量赋值。

下面列举了10个关于vhdl条件赋值语句的例子。

1. 当输入信号X为1时,将输出信号Y赋值为0;否则将Y赋值为1。

```vhdlprocess (X)beginif X = '1' thenY <= '0';elseY <= '1';end if;end process;```2. 当输入信号A为0时,将输出信号B赋值为C的值;否则将B赋值为D的值。

```vhdlprocess (A, C, D)beginif A = '0' thenB <= C;elseB <= D;end if;end process;```3. 根据输入信号Sel的值,选择对应的输入信号并赋值给输出信号Out。

```vhdlprocess (Sel, In1, In2, In3)begincase Sel iswhen "00" =>Out <= In1;when "01" =>Out <= In2;when "10" =>Out <= In3;when others =>Out <= "0000";end case;end process;```4. 如果输入信号X大于等于Y,则将输出信号Z赋值为1;否则将Z赋值为0。

```vhdlprocess (X, Y)beginif X >= Y thenZ <= '1';elseZ <= '0';end if;end process;```5. 当输入信号Valid为1且输入信号Data的值为偶数时,将输出信号Even赋值为1;否则将Even赋值为0。

VHDL语言_信号赋值语句

在例4.1程序中,我 们对信号s进行了多 次赋值,经过仿真, 系统报如下错误:

ERROR: Signal “s”

has multiple sources 。

信号赋值语句

2.进程外部几个信号的赋值语句是并行执行的 即信号赋值语句中的信号发生变化,便执行该条赋 值语句。

例4.2: library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity test is

信号赋值语句

四、信号赋值语句的使用注意事项 1.进程外部不能对同一信号多次赋值 进程的概念将在下一单元介绍

例4.1: library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity test is

w<=y3 or y2 or y1 or y0; --简单赋值

end liti_arch;

信号赋值语句

三、选择赋值语句 选择赋值语句格式如下: with 表达式 select 信号名 <=信号值 when 选择值, 信号值 when 选择值, … 信号值 when 选择值; 信号值 when others;

y1<=a1)and not a(2) and a(0); --简单赋值

y0<=a(0)and not a(1) and a(2); --简单赋值

w<=y3 or y2 or y1 or y0;

--简单赋值

end shiti 1;

描述中使用了VHDL自有的and、or、not运算符, not运算符的优先级别最高。

VHDL语言的顺序语句

目 录

• 顺序语句概述 • 顺序语句概述 • 赋值语句 • 条件语句 • 循环语句 • 控制流语句

01

CATALOGUE

顺序语句概述

过程块(process block)

过程块是顺序语句的一种形式,它包含一系列的顺序语句,按照一定的顺序执行。

过程块通常在仿真过程中按照时间顺序逐行执行。

loop-statement循环语句

语法示例

```vhdl

loop_statement: process(some_signal)

loop-statement循环语句

01

02

begin

• 循环体

03

if some_condition then

loop-statement循环语句

• 条件满足时执行的代码

并行过程块(concurrent process block)

并行过程块是另一种形式的顺序语句,它包含一系列的顺序语句,这些语句在仿真过程中同时执行。

并行过程块通常用于描述数字系统的并发行为。

02

CATALOGUE

赋值语句

连续赋值语句

总结词

在连续赋值语句中,信号或变量的值 在每个仿真时间步都会更新。

case语句

end case;

```

conditional语句

描述:类似于其他编程语言中的三元操作符。

01

02

语法

```vhdl

03

04

signal_name <= "0" when condition else "1";

```

05

06

上述语句表示,如果条件为真,则将 `signal_name`设置为"0",否则设置为 "1"。

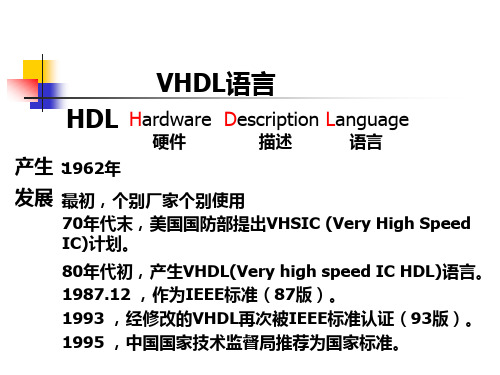

VHDL语言

VHDL语言的基本结构

实体结构

ENTITY 实体名 IS PORT ( 端口名1,端口名2,…端口名n :方向 数据类型名; … 端口名a,端口名b,…端口名m :方向 数据类型名);

80年代初,产生VHDL(Very high speed IC HDL)语言。 1987.12 ,作为IEEE标准(87版)。 1993 ,经修改的VHDL再次被IEEE标准认证(93版)。 1995 ,中国国家技术监督局推荐为国家标准。

VHDL语言的优点

支持自上而下的设计方法(整体描述)

半加器描述事例: WHEN “00” => so<=‘0’; co<=‘0’ ; WHEN “01” => so<=‘1’; co<=‘0’ ; WHEN “10” => so<=‘1’; co<=‘0’ ; WHEN “11” => so<=‘0’; co<=‘1’ ;

P.42 表3-3

VHDL语言的基本结构

实体 用以描述外部端口

构造体 用以描述内部结构及行为

实体结构

ENTITY 实体名 IS PORT ( 端口名1,端口名2,…端口名n :方向 数据类型名; … 端口名a,端口名b,…端口名m :方向 数据类型名);

END 实体名;

半加器实体说明举例 ENTITY h_adder IS

。 l任何标识符必须以英文字母开头。 l必须是单一下划线“_”,且其前后都必须有英文字母或数字。 l标识符中的英语字母不分大小写。 l允许包含图形符号(如回车符、换行符等),也允许包含空格符。

vhdl顺序语句

vhdl顺序语句VHDL(VHSIC Hardware Description Language)是一种硬件描述语言,用于描述数字电路和系统的结构和行为。

在VHDL中,顺序语句用于按照特定的顺序执行操作。

下面将列举10个VHDL顺序语句的示例。

1. 赋值语句(Signal Assignment Statement):使用“:=”操作符将一个信号或变量赋给另一个信号或变量。

例如:```vhdlsignal a, b : std_logic;signal c : std_logic;c := a and b;```2. 过程调用语句(Procedure Call Statement):用于调用已定义的过程。

例如:```vhdlprocess(clk)beginif rising_edge(clk) thenmy_procedure(param1, param2);end if;end process;```3. 条件语句(If-then-else Statement):根据条件执行不同的语句块。

例如:```vhdlif a = '1' thenb <= '0';elseb <= '1';end if;```4. 选择语句(Case Statement):根据选择的值执行相应的语句块。

例如:```vhdlcase sel iswhen "00" =>out <= a;when "01" =>out <= b;when "10" =>out <= c;when others =>out <= '0';end case;```5. 循环语句(Loop Statement):用于重复执行一组语句。

例如:```vhdlprocessbeginloopif a = '1' thenb <= '0';elseb <= '1';end if;wait for 10 ns;end loop;end process;```6. 退出语句(Exit Statement):用于提前退出循环语句。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

进行的,或者说是并行运行的,其执行 方式与书写的顺序无关。

来,也可以是互为独立、互不相关、异 步运行的(如多时钟情况)。

在执行中,并行语句之间可以有信息往

每一并行语句内部的语句运行方式可以

有两种不同的方式,即并行执行方式(如 块语句)和顺序执行方式(如进程语句)。

Architecture

Begin

ARCHITECTURE

式 BEGIN p1:PROCESS(a,b) VARIABLE comb:STD_LOGIC_VECTOR(1 DOWNTO 0); -变量定义 BEGIN comb:= a & b; --变量赋值(此处为用并置运算符将 a和b连接成一个两位矢量) CASE comb IS --CASE_WHEN多项选择语句 WHEN “00”=>y<=„1‟; --当ab=00时,y=1 WHEN “01”=>y<=„1‟; --当ab=01时,y=1 WHEN “10”=>y<=„1‟; --当ab=10时,y=1 WHEN “11”=>y<=„0‟; --当ab=11时,y=0 WHEN OTHERS=>y<=„X‟; --当ab的取值为其他情况时, y的取值不确定 END CASE; END PROCESS p1; END 赋值语句

语法格式:

signal_name <= 逻辑表达式

VHDL支持所有的标准逻辑运算:

AND, OR, NOT, XOR, XNOR, NAND

例:4

选 1 数据选择器

a b c d

s

2 x

mux

Architecture a of mux4_1 is Begin x <= (a AND NOT(s(1)) AND NOT(s(0))) OR (b AND NOT(s(1)) AND s(0)) OR (c AND s(1) AND NOT(s(0))) OR (d AND s(1) AND s(0)) ; 逻辑表达式 End a;

x <= a when (s = “00”) else b when (s = “01”) else c when (s = “10”) else d; 隐含了所有未

列出的条件 隐含了优 先权 s 2 x

s是Std_Logic_Vector数据

类型。 其每一位值包括 ‘0’,’1’,’X‟,‟Z‟等

任务3

掌握VHDL的基本功能描述语 句 ----信号赋值语句

构造体 说明语句

构 造 体 结 构 图

功能描述语句 块语句 进程语句 信号赋值语句 子程序调用语句

元件例化语句

并行语句

并行语句1 signal 并行语句2 signal

并行语句3

构 造 体

并行语句

各种并行语句在结构体中的执行是同步

j <= w when x when y when z when „0‟ ; (a (b (c (d = = = = „1‟) „1‟) „1‟) „1‟) else else else else

允许有多个 控制信号

选择信号赋值语句(With_Select_When)

语法格式:

WITH selection_signal SELECT signal_name <= value_1 WHEN value_2 WHEN ... value_n WHEN value_x WHEN

LIBRARY IEEE; --调用IEEE库 USE IEEE.STD_LOGIC_1164.ALL ENTITY logic IS ――实体说明,定义实体名为logic PORT( a,b,c,d:IN STD_LOGIC; ――输入端口说明 y :OUT STD_LOGIC); ――输出端口说明 END logic; ――定义a,b,c,d是输入端口信号,y是输出端口信号 ARCHITECTURE jia OF logic IS SIGNAL e, f: STD_LOGIC ; ――定义e、f是内部信号 BEGIN f ﹤﹦ a AND b; ――以下三条并行语句与顺序无关 y﹤﹦ f OR e; e﹤﹦ c XOR d; END jia;

Y=ab+

cd

ENTITY logic IS ――实体说明,定义实体名为logic PORT( a,b,c,d:IN BIT; ――输入端口说明 y :OUT BIT); ――输出端口说明 END logic; ――定义a,b,c,d是输入端口信号,y是输出端口信号 ARCHITECTURE jia OF logic IS SIGNAL e,f:BIT; ――定义e,f是内部信号 BEGIN f ﹤﹦ a AND b; ――以下三条并行语句与顺序无关 y﹤﹦ f OR e; e﹤﹦c XOR d; END jia;

条件信号赋值语句( When_Else )

语法格式:

signal_name <=

value_1 WHEN condition1 ELSE value_2 WHEN condition2 ELSE ... value_n WHEN conditionn ELSE value_x;

When_Else语句举例(1)

nand2_2 OF nand2 IS --结构体2:行为描述方

CONFIGURATION

pz OF nand2 IS

--配置语句,

指明用哪一个结构体 FOR nand2_1 END FOR; END CONFIGURATION;

ENTITY mux21a IS ――实体说明,定义实体名为 mux21 PORT(a,b:IN BIT; ――输入端口说明,定义a,b,s 为输入端口信号 s:IN BIT; y:OUT BIT); ――输出端口说明,定义y为 输出端口信号 END ENTITY mux21a; ARCHITECTURE one OF mux21a IS ――结构体说明 BEGIN y﹤﹦a WHEN s=‘0‟ ELSE ――当s=0时,y=a b; ――当s≠0时,y=b END ARCHITECTURE one;

进程和进程之 间是并行的 进程和进程之 间的数据交换 通过信号完成 进程内部是顺 序语句

PROCESSn

进程语句

基本格式:

[进程名称:] PROCESS(敏感信号1,敏感信号2,……)

〈说明区〉 BEGIN 〈顺序语句〉 END PROCESS [进程名称];

LIBRARY IEEE; --调用IEEE库 USE IEEE.STD_LOGIC_1164.ALL; --调用IEEE库 中的STD_LOGIC_1164.ALL程序包 ENTITY nand2 IS --实体说 (PORT a,b: IN STD_LOGIC; --输入端口说明 Y: OUT STD_LOGIC); --输出端口说明 END nand2; ARCHITECTURE nand2_1 OF nand2 IS --结构体1: 数据流描述方式 BEGIN y﹤﹦a NAND b; --简单并行信号赋值语 句 END nand2_1;

a b c d

mux

条件信号赋值语句( When_Else )

根据指定条件对信号赋值,条件可以为

任意逻辑表达式

根据条件出现的先后次序,ELSE子句

有优先权(按顺序逐条测试条件)

最后一个

的条件

ELSE子句隐含了所有未列出

每一子句的结尾没有标点,只有最后一

句有分号

When_Else语句举例(2)

value_a, value_b, value_n, OTHERS;

With_Select_When语句举例(1)

LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY cmpl_sig IS PORT ( a, b,c,d: IN STD_LOGIC; x : OUT STD_LOGIC); s s: IN STD_LOGIC_VECTOR(1 downto 0); 2 END cmpl_sig; ARCHITECTURE logic OF cmpl_sig IS a BEGIN b WITH s SELECT mux c x <=a WHEN “00”, b WHEN “01”, d c WHEN “10”, d WHEN OTHERS; 加Others语句

x

选择信号赋值语句( With_Select_When )

所有的“WHEN”子句必须是互斥的 一般用

“When Others”来处理未考虑 到的情况 (<=)

只有一个参考信号和赋值符

每一子句结尾是逗号,最后一句是分号 每个WHEN子句可以包含多个条件:

With_Select_Then语句举例(2)

WITH s SELECT x <= a WHEN ”000” | “001” | “010”, b WHEN "101" | "111", c WHEN OTHERS; 表示或逻辑

构造体 说明语句

构 造 体 结 构 图

功能描述语句 块语句

进程语句 信号赋值语句 子程序调用语句 元件例化语句

进程语句

Architecture

Begin

进程1

进程2

When-Else A <= “0011” 进程1

End

进程2 A <= “0011”

When-Else

End

构造体 说明语句

构 造 体 结 构 图

功能描述语句 块语句 进程语句 信号赋值语句 子程序调用语句

元件例化语句

信号赋值语句

直接信号赋值语句 条件信号赋值语句

VHDL中最重要的语句,具有并行和