LEC11 中文

诺雅克产品快速选型

251000Contents 目录25~47终端类Ex9PN 系列小型断路器(相线+中性线)Ex9BD 系列直流小型断路器Ex9BP 系列光伏专用直流小型断路器Ex9LE 剩余电流动作附件Ex9PLE 剩余电流动作保护断路器Ex9I 系列隔离开关Ex9F 系列熔断器Ex9U 系列电涌保护器Ex9B 系列小型断路器Ex9BM 系列小型断路器48~6667~6970~73控制类箱体类智能仪表Ex9Ci 系列低功耗交流接触器Ex9R 系列热过载继电器Ex9RC 系列中间继电器Ex9CC 系列电容接触器Ex9QC 系列电磁起动器Ex9QS 系列星--三角电磁起动器NEV 直流继电器Ex9C 系列交流接触器光伏汇流箱SUP 监控装置PMR700智能电动机保护器PMA700智能电力参数测量仪01~24配电类Ex9A 系列空气断路器Ex9M 系列塑壳断路器ExATS 系列自动转换开关019A16、9A32、9A40选型说明空气断路器Ex9A Ex9A 3P 产品代号极数代号16:1600A32:3200A40:4000A 16:1600A,1250A,1000A,800A,630A,400A 32:3200A,2900A,2500A,2000A,1600A 40:4000A,3200A,2900A,2500A,2000A Smart Unit 智能控制器SU30A:电流型30A SU40A:电流型40A SU50A:电流型5.0A SU30D:电压型30D SU40D:电压型40D SU50D:电压型50D SU30P:电能型30P SU40P:电能型40P SU50P:电能型50P SU30H:谐波型30HSU40H:谐波型40HSU50H:谐波型50HSU30GP:发电机电能型30GP SU30GH:发电机谐波型30GP AC230:交流230V AC400:交流400VDC220:直流220VDC110:直流110VDC24:直流24V N:55kA Q:65kA R:85kA H:100kA 9A16可选N 、Q 9A32可选Q 、R 、H 9A40可选Q 、R 、H 3P :三极4P :四极D/O :抽屉式(可省略)F :固定式无特殊要求此处无代号有特殊要求根据要求适时指定代号壳架等级额定电流代号额定电流代号智能控制器代号控制回路电源电压代号分断能力代号安装方式代号特殊要求代号161600SU 30A AC230N D/O OTHER 选型举例:“Ex9A16 3P 1250 F SU40P AC230”的含义为Ex9A 系列1600壳架的、三极的、1250A 的、固定式的、带多功能电能型4.0P 控制器的、控制回路电源电压为交流230V 的空气断路器。

c 11标准 中文版

c 11标准中文版C 11标准中文版。

C 11标准是C语言的一个重要标准,它对C语言的语法、语义和库函数做出了一系列的改进和扩充。

C语言作为一种通用的高级语言,一直以来都受到广泛的应用和关注。

C 11标准的出台,为C语言的发展注入了新的活力,也使得C语言在现代编程领域中更加具有竞争力和适用性。

C 11标准在原有C语言的基础上做出了许多改进和扩展,其中最主要的改进包括对多线程编程的支持、泛型编程的支持、对内存模型和原子操作的支持等。

这些改进使得C语言在并发编程、泛型编程和底层系统编程等方面有了更好的表现和支持。

在多线程编程方面,C 11标准引入了线程和原子操作的支持,使得C语言在多核和多线程编程方面更加方便和高效。

开发者可以利用C 11标准提供的线程库和原子操作来实现并发编程,这为C语言的应用场景提供了更多可能性。

在泛型编程方面,C 11标准引入了泛型选择和泛型表达式的支持,使得C语言在泛型编程方面更加灵活和强大。

开发者可以利用C 11标准提供的泛型特性来编写更加通用和可复用的代码,这为C语言的应用领域提供了更多的可能性。

在内存模型和原子操作方面,C 11标准引入了对内存模型和原子操作的支持,使得C语言在底层系统编程方面更加健壮和可靠。

开发者可以利用C 11标准提供的内存模型和原子操作来编写更加高效和安全的底层系统代码,这为C语言的应用场景提供了更多的保障和支持。

总的来说,C 11标准的出台对C语言的发展起到了积极的推动作用,使得C 语言在现代编程领域中更加具有竞争力和适用性。

C 11标准的改进和扩展为C语言的应用场景提供了更多的可能性和支持,也为C语言的未来发展注入了新的活力。

相信在C 11标准的指引下,C语言将会在未来的编程领域中继续发挥重要的作用,为软件开发和系统编程提供更加强大和灵活的工具和支持。

iooq11参数

iooq11参数

新技术的发展与普及,使得q11参数在当今社会越来越受到重视。

随着电脑技术的进步,q11参数的推广应用也受到沿海一带国家的一些企业和科研单位的重视。

下面,我将对q11参数的类别、实现原理、参数调整以及应用等方面作出详细的介绍。

q11参数的类别主要包括语言处理参数,精确搜索参数以及自然语言处理参数。

语言处理参数是指使用算法建立一个保存词语处理参数的字典。

精确搜索参数是指在多种语言中进行搜索,使其能够准确地定位用户搜索的信息。

自然语言处理参数是指利用计算机技术来识别自然语言的参数。

q11参数的实现原理是通过层次性的把模块分为三个层面:模块层面、语义层面和表示层面。

其中,模块层面的模块主要用于切分输入的语句;语义层面的模块用于提取语义;表示层面的模块用于将语义表示为一定的参数。

q11参数的参数调整是通过改变模块参数、语义参数以及表示参数来实现的。

模块参数包括分割符、词尾符和长度限制;语义参数则包括类别参数、复杂性参数以及情感参数;表示参数主要有词频参数和频率参数。

q11参数的应用非常广泛,可以用于语言建模,知识图谱的建模,情感分析,自然语言处理,文本挖掘,智能对话等等。

例如,它可以被用于社会民意调查中,通过q11参数,我们可以准确地定位社会民意的真实反馈,从而进行更有价值的调查分析。

总之,q11参数是一种新型的技术,它具有精确性、高效性和高灵活性,能够解决许多复杂的自然语言处理问题,在文本分析、智能对话领域有着重要的应用价值。

九年级全一册英语课程讲解unit11

九年级全一册英语课程讲解unit11Unit 11 of the 9th grade English curriculum covers a variety of topics, including environmental issues, pollution, and ways to preserve the environment. In this unit, students will learn about the impact of pollution on the planet, the importance of recycling, and the role of individuals in protecting the environment.One of the key themes in this unit is the concept of sustainability. Students will learn about the ways in which humans impact the environment through activities such as deforestation, pollution, and overconsumption. They will also explore the importance of sustainable practices, such as recycling, using renewable energy sources, and reducing waste.To help students understand the impact of pollution on the environment, teachers can use a variety of resources, such as documentaries, articles, and interactive activities. Students can also participate in hands-on projects, such as creating a recycling program at school or organizing a community clean-up event.In addition to learning about the environmental issues facing the planet, students will also learn about the ways in which they can take action to protect the environment. Thiscould include simple actions such as reducing water usage, recycling paper and plastic, and using environmentally-friendly products.Overall, Unit 11 provides students with a comprehensive understanding of environmental issues and the importance of preserving the planet for future generations. By incorporating hands-on activities, discussions, and real-world examples, teachers can help students develop a sense of environmental responsibility and a commitment to protecting the planet.。

02378_mike11中文教程

2024/1/24

3

软件背景及发展历程

起源

MIKE11软件起源于丹麦水资源及水环境研究所( DHI)的研究项目,是一款广泛应用于水资源、水环 境、水利工程等领域的模拟软件。

发展历程

自问世以来,MIKE11软件不断升级和完善,逐渐增 加了新的模块和功能,如水文模拟、水质模拟、洪 水模拟等,以满足用户不断增长的需求。

完善水文气象监测网络,提高预报精度。

优化调度规则,提高水库调节能力。

2024/1/24

加强水库与上下游的协调联动,实现区域水资源优化配 置。

24

06

MIKE11在水利工程中的高级应用

2024/1/24

25

水质模拟与评估方法探讨

80%

水质模型构建

利用MIKE11构建水质模型,包 括污染物输移、转化和衰减等过 程,以模拟河流、湖泊等水域的 水质变化。

5. 选择安装路径,可以使用默认路径或自定义路径 ,然后点击“下一步”。

6. 选择需要安装的组件,建议勾选所有组件以确保 软件功能完整,然后点击“下一步”。

2024/1/24

10

安装步骤详解

7. 点击“安装”按钮开始安装,安 装过程中请耐心等待。

8. 安装完成后,点击“完成”按钮退 出安装程序。

2024/1/24

数据校验与调整

在输入模型前,对数据进行校验和调整,确保数 据的合理性和准确性。

19

结果可视化与输出格式选择

结果可视化

输出格式选择

利用MIKE 11的内置工具或第三方软件对模 拟结果进行可视化展示,如水位、流量、 流速等参数的时空分布。

根据需求选择合适的输出格式,如文本文 件、Excel、图形文件等。

ICHQ11中文版

ICH Q11中文版原料药开发与制造(Q11)人用药注册技术要求国际协调会议2012年5月1日版(上)□翻译徐禾丰郭鸽编者按5月24日,本版刊登了业内专家对国际人用药品注册技术要求协调会议(ICH)发布的Q11《原料药开发与制造》指南内容的独家介绍。

该文件对化学与生物原料药开发的基本原则及开发方式进行了调整,鉴于其将对我国原料药研发和生产领域产生较大影响,本版特将该文件具体内容的译文分上下两期(今日和6月7日)予以刊载,以期给国内原料药企业及有关部门以借鉴。

原料药开发与制造(化学实体与生物技术/生物制品实体,Q11)由人用药注册技术要求国际协调会议(ICH)专家工作组提出,并根据ICH程序现向三个缔约方(欧盟、日本和美国)的药政部门推荐供采用的最终文本。

1. 简介本指南描述了原料药工艺开发及对工艺理解的方法,也指明了ICH-M4Q(ICH药品注册CTD格式质量部分)通用技术文件(CTD)模块3中从第3.2.S.2.2节(制造过程与工艺控制描述)到第3.2.S.2.6节(制造工艺开发)应当提供的信息。

描述了原料药相关的开发和制造方面,包括降低杂质的步骤设计。

另外,ICH-Q11进一步澄清了ICH的药物开发(Q8)、质量风险管理(Q9)及制药质量体系(Q10)中关于原料药开发和制造的原则及概念。

企业在开发原料药时可以选择使用其他方法。

本指南的目的是,用“传统”与“加强”这两个术语来区别两种不同的开发方式。

在传统方式中,工艺参数的设定点及操作范围是确定的,原料药的控制策略通常基于工艺可重复性的证据,并且测试结果符合已经建立的验收标准。

在强化方式中,更加广泛地使用风险管理以及科学知识来辨识与理解影响关键质量属性(CQA)的工艺参数及单元操作,设计可用于原料药整个生命周期的适当的控制策略,其中可能包括建立设计空间。

正如在ICH-Q8中对制剂产品所讨论的,充分理解原料药及其制造工艺,可以奠定一个更加灵活的监管方式基础。

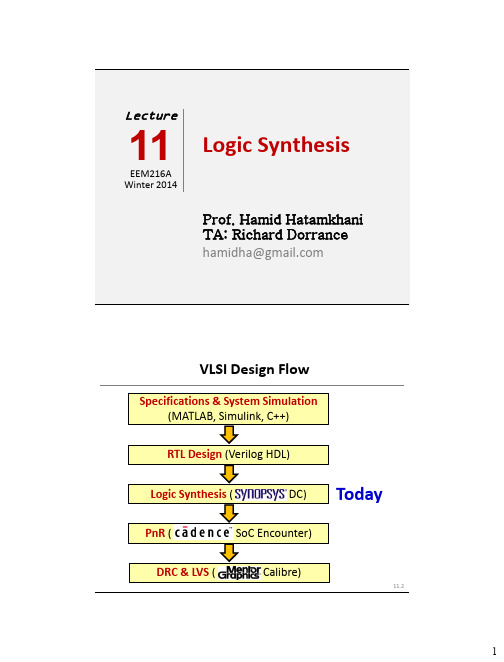

Lec-11_Synthesis

Logic SynthesisProf. Hamid HatamkhaniTA: Richard Dorrancehamidha@Lecture11 EEM216A Winter 2014 D. Markovic / Slide 2 VLSI Design FlowRTL Design (Verilog HDL)Specifications & System Simulation(MATLAB, Simulink, C++)Logic Synthesis ( DC) PnR ( SoC Encounter)DRC & LVS ( Calibre)Today11.2D. Markovic / Slide 3 Logic Synthesis•Conceptual overview & tool setup•RTL modification•Technology libraries•Design environment & constraints•Major synthesis commands•Gate-level simulation11.3D. Markovic / Slide 4 Synthesis:WHY, HOW, WHAT11.4D. Markovic / Slide 5 Why Need Synthesis?•Quick (re)design time•Separate functionality, technology-dependent parameters, and design constraints•Fast timing/area/power estimates11.5 D. Markovic / Slide 6 How to do Synthesis?OptimizedGate-level NetlistArchitectural Mapping Designware LibLogic Optimization Technology LibRTL Design (your .v files) Database of Adders, Multipliers, Shifters… Gate sizing,Logic Transformation RCA, CLA…MUXAND + OR + INV … Synthesis Commands(your .tcl files)11.6D. Markovic / Slide 7 What can Synthesis Provide?•Timing/Area/Power reports•Gate-level netlist (.vg) & timing info. in standard delay format (.sdf) for timing-aware simulationA 10000010B 00111100C 10111110A 10000010B 00111100C 10111110assign C = A + B ;before synth.after synth.Glitch & Delay 11.7D. Markovic / Slide 8 Script Example (.tcl Files)remove_design –allsource ./SET_CON/T40GP_LibSetup.tcllappend search_path ./HDL ./SYN analyze -format verilog Adder.vset PROCESS _T40GPset DESIGN_NAME ADD elaborate $DESIGN_NAMElink set_operating_conditions -min ff1p16vn40c -max ss0p95v125cset_wire_load_selection_group "predcaps"set TCLK 1.9 set TCU 0.1source ./SET_CON/T40GP_VarSetup.tcl set_false_path -from [get_ports ACLR_]uniquifycompile -only_design_rulecompile _ultra -no_autoungroupcompile -inc -only_hold_time set_fix_multiple_port_nets -all -buffer_constants [get_designs *]remove_unconnected_ports -blast_buses [get_cells -hier] report_timing -path full -delay min -max_paths 10 > $LOGPATH$TOPLEVEL$PROCESS.holdtiming report_timing -path full -delay max -max_paths 10 > $LOGPATH$TOPLEVEL$PROCESS.setuptiming report_area -hierarchy > $LOGPATH$TOPLEVEL$PROCESS.areareport_power -hier -hier_level 2 > $LOGPATH$TOPLEVEL$PROCESS.power1. Setup Technology Library2. Read RTL design & doarchitectural mapping3. Setup design constraint4. Compile design5. Get Reports 11.8D. Markovic / Slide 9 Tool Setup on WorkstationNow you’re ready to use Synopsys Design Compiler1.Login 2.Edit .cshrc file, or directly type3.Type dc_shell to open DCSet path = (w/apps3/Synopsys/Design_Compiler/vF-2011.09/bin $path) Source /w/apps3/Synopsys/Design_Compiler/vF-2011.09/SETUP11.9D. Markovic / Slide 10 Logic Synthesis•Conceptual overview & tool setup•RTL modification•Technology libraries•Design environment & constraints•Major synthesis commands•Gate-level simulation11.10D. Markovic / Slide 11 The Importance of HDL Coding Styles Different coding styles that are functionally eqvl. may be mapped into HWs having different timing/areaGood coding style: Better start point for DC to reach optimal gate-level resultsE = A + B + C + D E = (A + B ) + (C + D )A B C D E A BE CD11.11D. Markovic / Slide 12 Enable Cool Features from DC#1: Gated Clock#2: Synopsys Directives11.12D. Markovic / Slide 13 Go Low-Power using Clock Gating 30~50% Power Savings @ Block LevelTwo steps for gated-clock syn.: (1)Delete Else state-ments in seq. logics; (2)DC commands (shown later) Q D EN CLK 10DFF always@(posedge CLK ) if(EN ) Q <= D ; else Q <= Q ;always@(posedge CLK ) if(EN ) Q <= D ;STILL NOEN CLKLatchD QDFF 11.13D. Markovic / Slide 14 Case Directives Supported by DC (1) tell DC to interpret incomplete case specially Keyword: // synopsys_parallel_case// synopsys_full_case(RTL simulator ignores, but DC understands) reg A, B;wire [2:0] SEL ; always@(*) {A, B} = 2’b0 ;casez(SEL) 3’b?11: B = 1 ;3’b1??: A = 1 ;endcasePut it after thecase declaration// synopsys_parallel_case11.14D. Markovic / Slide 15 Case Directives Supported by DC (2) •Synopsys_full_case•Treats o/p of unstated case items as don’t care •Ignored if the case statement is complete •As a result, no latch is created•Synopsys_parallel_case•Treats all case items as non-overlapped ; implement each of them seperately•As a result, no priority logic is createdNote: Potential discrepancy b/w RTL simulation and gate-level simulation 11.15 D. Markovic / Slide 16 Example : RTL the Same, Gate-Level Different reg A, B;wire [2:0] SEL ;always@(*){A, B} = 2’b0 ; casez(SEL ) 3’b?11: B = 1 ; 3’b1??: A = 1 ;endcase reg A, B;wire [2:0] SEL ;always@(*){A, B} = 2’b0 ; casez(SEL ) // synopsys_parallel_case 3’b?11: B = 1 ; 3’b1??: A = 1 ;endcase Lec. 8.46 SEL[2]SEL[1]SEL[0]B A SEL[2]SEL[1]SEL[0]B A Priority Logic Independent Logic11.16D. Markovic / Slide 17 Logic Synthesis•Conceptual overview & tool setup•RTL modification•Technology libraries•Design environment & constraints•Major synthesis commands•Gate-level simulation11.17 D. Markovic / Slide 18 What are Technology Libraries About? (1) library ("saed32rvt_ss0p95v125c") {operating_conditions (ss0p95v125c) {process : 0.99; voltage : 0.950000;temperature : 125.000000; tree_type : "best_case_tree";}wire_load (ForQA) {capacitance : 0.029396;resistance : 2.273000e-03;area : 0.010000;slope : 30.285426; fanout_length ("1", "8.2750360");... } wire_load ("8000") {...}...wire_load_selection (predcaps) {wire_load_from_area (0.000000,200.000000, "ForQA"); wire_load_from_area (200.000000,8000.000000, "8000"); ...} Operating condition(process, voltage, temp.)Wire-load model(rough est. of wiringparasitics before PnR)Wire-load selection(based on synth. area of your design)11.18D. Markovic / Slide 19 What are Technology Libraries About? (2)detailed information of each standard cellCell NameAreaFunctionalityPin CapacitanceLeakage Power7x7 Look-up Tables (LUT) for Dynamic Power &Propagation Delay of all i/o Paths(idx1: input transition time; idx2: o/p capacitance)11.19 D. Markovic / Slide 20 What are Technology Libraries About? (3) cell (AND2X1_RVT) {area : 2.033152; cell_leakage_power : 1.404953e+05;leakage_power () { when : "!A1&!A2"; value : "5.6919234e+04"; }...pin (Y) {related_power_pin : "VDD"; related_ground_pin : "VSS"; direction : "output";...max_capacitance : 8.000000; max_transition : 0.194746;internal_power () {related_pin : "A1";rise_power ("power_outputs_1") {index_1("0.016, 0.032, 0.064, 0.128, 0.256, 0.512, 1.024");index_2("0.1, 0.25, 0.5, 1, 2, 4, 8");values ("0.9612064, 0.9624440, 0.9509065, 0.9587265, 0.9569466, 0.9523558, 0.9245481", \ ...}timing () {related_pin : "A1";cell_rise ("del_1_7_7") {index_1("0.016, 0.032, 0.064, 0.128, 0.256, 0.512, 1.024");index_2("0.1, 0.25, 0.5, 1, 2, 4, 8");values ("0.0400985, 0.0415339, 0.0437422, 0.0477826, 0.0546696, 0.0667816, 0.0888995", \ ...}11.20D. Markovic / Slide 21 Access Synopsys 32nm Technology Libs. Path: /w/apps2/public.2/tech/synopsys/32-28nm/SAED32_EDK/lib/stdcell_rvt /db_nldm (rvt: regular-V th . Can change to hvt and lvt for high-Vth and low-V th libraries)There you can find various libraries, eachwith different design corners. We selectsaed32rvt_ff1p16vn40c.db for hold-time analysis&saed32rvt_ss0p95v125c.db for setup-time analysis Note: .db files are only used by DC. If you want to read library information as in page 11.18~20, access the corresponding .lib files11.21 D. Markovic / Slide 22 Setup Technology Librariesset search_path “$search_path \/w/apps2/public.2/tech/synopsys/32-28nm/SAED32_EDK/lib/stdcell_rvt/db_nldm ” set target_library “saed32rvt_ff1p16vn40c.db saed32rvt_ss0p95v125c.db”set link_library “* saed32rvt_ff1p16vn40c.db saed32rvt_ss0p95v125c.db dw_foundation.sldb ” set synthetic_library “dw_foundation.sldb ”# Define work path (note: The work path must exist, so you need to create a folder WORK first) define_design_lib WORK -path ./WORKset alib_library_analysis_path “./alib-52/”(save above scripts in a .tcl file, and source it after you open DC)•DC follows search_path to find libraries you specify •DC uses cells in target library for logic optimization (so we need to do set_target_library first)•Remember: Use backslash \ before changing lines to avoid compilation errors.11.22D. Markovic / Slide 23 Logic Synthesis•Conceptual overview & tool setup•RTL modification•Technology libraries•Design environment & constraints•Major synthesis commands•Gate-level simulation11.23 D. Markovic / Slide 24 Large Area Small Short DelayLong •••• • •Synthesis is Constraint-DrivenCourtesy: SynopsysYou set the goals (through design constraints ) DC optimizes the design to meet your goals11.24D. Markovic / Slide 25 Logic Synthesis is Timing-Drivenlogic logic logic logic logic Clk “set_input_delay” (affects input logic) “set_output_delay ” (affects output logic) “create_clock” (affects internal logic) (input) (internal) (output)your current design•Input delay : Arrival of an external path with r.p.t the clock edge•Output delay : timing from an o/p (of current design ) to a register i/p (of other submodules)11.25D. Markovic / Slide 26 Describe Design Constraints•Clocks•Period, latency, uncertainty •Design rules •Maximum transition •Maximum capacitance•Maximum fanout •Input-related •Driving cells, Input delay •Output-related •Load, Output delay•Exception paths•False paths, multi-cycle paths•Optimization goal•Maximum area/power # Especially important for bottom-up design methodology# Accurate constraints (not too tight/loose): Good integ. results 11.26D. Markovic / Slide 27 Ideal vs. Real Clocklatency uncertainty transition(jitter+ skew)ideal clockCourtesy: Synopsys 11.27periodD. Markovic / Slide 28 Clock Description•create_clock: define clock’s waveform (e.g. period) •set_fix_hold: respect the hold time requirement of all clocked flip-flops•set_dont_touch_network: do not buffer clock network •Specify uncertainty (skew + jitter) of clock network11.28create_clock -name “CLK" -period 2.0 [get_ports “CLK"] set_fix_hold CLKset_dont_touch_network [get_clocks “CLK"] set_clock_uncertainty 0.1 [get_clocks “CLK"]D. Markovic / Slide 29 Maximum TransitionSets the max_transition attribute to a specified value on specified clocks group, ports or designs.8.29set_max_transition 0.15 current_designvalue object listTip: Check the max_transition variable in .lib file to setup more realistic numbersTransition Time D. Markovic / Slide 30 Maximum CapacitanceSets the max_capacitance attribute to a specified value on the specified input ports and designs.(“*” means “all designs including submodules ”)8.30set_max_capacitance 1.000 [get_designs *]value object list Tip: Check the max_capacitance variable in.lib file to setup more realistic numbersD. Markovic / Slide 31 Maximum FanoutSets the max_fanout attribute to a specified value on specified input ports and/or designs. 8.31set_max_fanout 1.000 [get_designs *] value object listTip: Check the fanout_load variable of cells in .lib file to setup more realistic numbersGate FanoutLoad Total Fanout Load = 0.90.10.8D. Markovic / Slide 32 Output LoadSets the set_load attribute to a specified value on specified output ports and/or designs.8.32set_load 1.000 [all_outputs]value object listTip: Check the capacitance variable of cell input pins in .lib file to setup more realistic numbersDesignD. Markovic / Slide 33 Driving CellsSets attributes on input or inout ports of the current design, specifying that a library cell or output pin of a library cell drives specified ports.set_driving_cell [-library lib] [-lib_celllib_cell_name] [-pin pin_name]8.33set ALL_IN_BUT_CLK [remove_from_collection [all_inputs] “CLK"]set_driving_cell -no_design_rule -librarysaed32rvt_ss0p95v125c.db :saed32rvt_ss0p95v125c -lib_cell DFFASRX2_RVT -pin Q $ALL_IN_BUT_CLK D. Markovic / Slide 34 Input & Output DelaySets delay on pins or portsrelative to a (ideal) clock signal.set_input_delay -max delay_value [-clock clock_name] set_input_delay -min delay_value [-clock clock_name]set_output_delay -max delay_value [-clock clock_name] set_output_delay -min delay_value [-clock clock_name]8.34set_input_delay 0.6 -clock “CLK" $ALL_IN_BUT_CLKset_input_delay -min 0.3 -clock “CLK" $ALL_IN_BUT_CLKset_output_delay 0.6 -clock “CLK" [all_outputs]set_output_delay -min 0.3 -clock “CLK" [all_outputs]D. Markovic / Slide 35 False PathsRemoves timing constraints from particular paths, but still needs to satisfy design rule(transition, capacitance, fanout).set_false_path -from [from_list]8.35set_false_path -from [get_ports ACLR_]set_false_path -from [get_ports SI] D. Markovic / Slide 36 Maximum Area/Power11.36set_max_total_power 0.0set_max_area 0.0desired areadesired powerOptimization goals for your design (DC will do it best to satisfy them, w/o violating the three design rules)D. Markovic / Slide 37 Operating ConditionDefines the operating conditionsfor the current design.set_operating_conditions[-min min_condition] [-max max_condition]8.37set_operating_conditions-min ff1p16vn40c -max ss0p95v125cfor hold-time check for setup-time checkD. Markovic / Slide 38 Wire-load Models and ModesSpecify a selection group to use for determining a wire load model to be assigned to designs andcells or to a specified cluster.set_wire_load_selection_group group_name -max set_wire_load_selection_group group_name -min8.38set_wire_load_selection_group "predcaps"DC will select proper model based on synthesisarea (again, lookup this name in .lib file)D. Markovic / Slide 39 Logic Synthesis•Conceptual overview & tool setup•RTL modification•Technology libraries•Design environment & constraints•Major synthesis commands•Gate-level simulation 11.39 D. Markovic / Slide 40 Preview: Use Synthesis Commands Properly •Not all commands introduced are necessarily needed •Things MUST doanalyze, elaborate, and link designuniquify (required by the follow-up PnR tool)remove unconnected portscompile design•Things can do based on your needsungroupclock gating creationSuggestion : Learn by playing w/ different commands and observing the differences 11.40D. Markovic / Slide 41 Analyze DesignsAnalyzes the HDL files and stores the intermediateformat in the specified library.analyze [-format vhdl | verilog | sverilog] file_list8.41analyze –format verilog {adder.v} D. Markovic / Slide 42 Elaborate & Link DesignsBuilds a design from the intermediate format of a Verilog module, a VHDL entity and architecture,or a VHDL configuration.elaborate design_name8.42set DESIGN_NAME adderelaborate $DESIGN_NAMED. Markovic / Slide 43 Ungroup & UniquifyRemoves a level of hierarchy.ungroup cell_list | -all [-flatten]Removes multiple-instantiated hierarchy in the current design by creating a unique design foreach of the cell instances.uniquify [-force] [-cell cell_list]8.43ungroup -flatten -all uniquifyD. Markovic / Slide 44 CompilePerforms logic-level and gate-level synthesis andoptimization on the current design.compile [-no_design_rule | -only_design_rule | -only_hold_time] [-map_effort medium | high] [-boundary_optimization]8.44compile -only_design_rulecompile -map_effort mediumcompile -boundary_optimizationcompile -only_hold_timeD. Markovic / Slide 45 Gated Clock Creation11.45set_clock_gating_registers -include_instances[all_registers -clock "CLK"]set_clock_gating_style -num_stages 2 -sequential_celllatch -minimum_bitwidth 8 -max_fanout 32insert_clock_gating –globalpropagate_constraints -gate_clockFour commands to construct clock gating(note: Modify RTL as in pp. 13 to enable this feature)D. Markovic / Slide 46 Remove Unconnected PortsRemoves unconnected ports or pins from cells,references, and subdesigns.11.46remove_unconnected_ports -blast_buses [get_cells -hier]D. Markovic / Slide 47 Report Designs (1)11.471. report_timing -path full -delay min -max_paths 10 -nworst 2 > Design.holdtiming2. report_timing -path full -delay max -max_paths 10 -nworst 2 > Design.setuptiming3. report_area -hierarchy > Design.area4. report_power -hier -hier_level 2 > Design.power5. report_resources > Design.resources6. report_constraint -verbose > Design.constraint7. check_design > Design.check_design8. check_timing > Design.check_timingD. Markovic / Slide 48 Report Designs (2)11.481. Define Naming Rules for your gate-level netlist: change_names -hierarchy -rule verilogdefine_name_rules name_rule -allowed "a-z A-Z 0-9 _" \ -max_length 255 -type celldefine_name_rules name_rule -allowed "a-z A-Z 0-9 _[]" \ -max_length 255 -type netdefine_name_rules name_rule -map {{"\\*cell\\*" "cell"}} change_names -hierarchy -rules name_rule2. Save netlist , timing information …etcwrite -format verilog -hierarchy -output Design.vgwrite -format ddc -hierarchy -output Design.ddcwrite_sdf Design.sdfwrite_sdc Design.sdcD. Markovic / Slide 49 Logic Synthesis•Conceptual overview & tool setup•RTL modification•Technology libraries•Design environment & constraints•Major synthesis commands•Gate-level simulation11.49 D. Markovic / Slide 50 Slight Modification of Original Testbench.v •RTL simulation: design.v + testbench.v•Gate-level simulation: design.vg + design.sdf (from DC) + testbench.v (w/ slight modification) 11.50`timescale 1ns/10ps module Test ; ADD AddSim (…) ; … … … … … … endmodule `timescale 1ns/10psmodule Test ;ADD AddSim (…) ;initial beginend……endmodule$sdf_annotate (“design.sdf ", AddSim);D. Markovic / Slide 51 Any Questions?The “Man” is always there for you, 24/7 (type man <syntax you want to lookup> in DC)or check out various user manuals online11.51 D. Markovic / Slide 52 Synthesis Summary11.52•Synthesis tool makes VLSI design a lot easier •Easy to use: .v files + .tcl files•Easy to switch designs to any technology by changing associated libraries•Easy to have accurate area/timing/power estimate •Easy to match the best archit. with design constraints•But… not a substitue for thinking•Mind your coding styles•Handmade optimization (e.g. using shift-and-add for constant multiplication) still needed。

VC11 + 过程信号源(PROSSE SOURCE)概要说明

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

二、基金的定价与费率

开放式基金单位的交易价格:

1. 发行价:发行时的认购价,面值加一定的手续费。 资产净值NAV:每个基金单位的价值。

总资产 总负债 单位基金资产净值 基金单位总数

2. 申购价=基金资产净值+手续费

(4.1)

3. 赎回价=基金资产净值-手续费

15

三、基金的收益分配与清盘

(一)基金收益的来源 基金投资所得利息、股利收入、资本利得。 (二)开放式基金收益的分配 根据基金契约及召募说明书的规定进行。每年至少 一次。

分配现金

红利再投资:投资者将收益再投资于基金,折算 成相应的基金单位。许多基金为鼓励再投资,低 收或免收申购费率。

16

第三节 封闭式基金

一、基金的发行与交易

发行基金单位数固定,在发行期满或基金规模达到 预定规模时,不再接受投资者的认购或赎回。交易 通过集中交易市场撮合,其交易流程与股票买卖相 同。

有两种报价:

一、集中交易市场每日看板上的报价;

二、基金公司每日计算的净值。

当市价低于净值时,即折价;反之,为溢价。 例P334

发行流程:

(1)基金管理公司代表基金发起人在监管机构指定 的报刊上刊登发行公告、召募说明书、基金契约等 文件。进行路演。柜台发行。 (2)通过证券营业所网点和商业银行代销渠道,向 投资者发行基金单位。 (3)发行结束后,基金管理人不得动用,应将募集 的资金划入验资账户,由有资格的机构和个人验资。 自批准之日起3个月内募集的资金超过该基金批准规 模80%的,该基金方可成立。 (4)自批准之日起3个月内募集的资金少于该基金 批准规模80%的,该基金不得成立,基金发起人承 担基金募集费用。已募集的资金加计利息,在30天 内退还基金认购人。

6

(三)投资基金称谓

英国:单位信托是主要形式,指契约型开放 式基金。投资信托(公司型封闭式基金); 开放式投资公司(公司型开放式基金)。 美国:基金业统称为投资公司或共同基金。 投资公司既指公司型基金,也指契约型基金; 共同基金包括开放式和封闭式基金,开放式 占主导。

我国:只有契约型基金,没有投资信托和共 同基金。

21

封闭式基金:基金规模在发行前确定,投资者不 能再追加申购或提前赎回。

2. 按组织形态分:

公司型投资基金:又叫共同基金,是具有共同投 资目的的投资者,依据公司法组成的,投资于特 定投资对象的股份制投资公司。通过发行股份的 方式筹集资金,委托特定的基金管理人或投资顾 问运用资金进行投资。 契约型基金:基于一定的信托契约而成立的基金, 一般由基金管理公司(委托人)、基金保管机构 (受托人)、和投资者(受益人)三方通过信托 投资契约而建立。

8

二、投资基金的优势

1.专业化的管理

2、分散投资

3、具有规模经济的优势 4、流动性好

9

三、基金的投资目标与策略

(1)债券基金。 分为政府债券基金、企业债券基金、金融债券基 金、短期债券基金、长期债券基金等。 积极组合管理策略: 水平分析:基于对市场利率的预测。如果预 期利率上升,就缩短债券组合的久期。 债券互换:同时买入和卖出具有相近特性的 债券,获得收益级差。 消极债券组合管理策略: 指数策略、 免疫策略(免于市场利率波动的风险 )

一般采用定期定量的收益分配:每月或每季度分配一 次,收益分配保持相对固定的比例或金额。 基金收益的来源:基金投资所得利息收入、股利收入、 资本利得。 基金收益扣除相关费用后为基金净收益,用于基金分 配。 封闭式基金有一个存续期,到期后,一是基金可以清 算投资者拿回基金净值,基金结束。二是转型成为可 直接按净值申购和赎回的开放式基金,“封转开”。

4

3. 按投资风险与收益分

成长型基金:把追求资本的长期成长作为投资 目的的投资基金。 收入型基金:目标为能为投资者带来较高当期 收入,投资对象主要为能带来的的投资基金。

均衡型基金:确保投资者本金、当期收入的同 时兼顾长期成长。

5

4. 按募集方式分

公募投资基金:公开募集的投资基金。通过证 监会审核、在证券公司等基金营销网点销售、 在各种交易行情中可以看到信息的基金。 私募投资基金:以非公开方式,向少数个人和 机构投资者募集资金而设立的基金。

基金的投资目标Biblioteka 策略(2)货币市场基金 风险低、流动性好。收益会随市场利率上升而上升。但 长期收益率较低。 (3)混合基金。混合投资于股票、债券、货币市场工具。 资产配置基金:在股票、债券、货币市场工具的中保 持固定投资比例。 平衡型基金:投资于一个特定的股票、债券组合来赚 取资产保值、一定现金收入、资本增值。 灵活组合基金:某类资产可持100% 混合收入型基金:求高收入,资本增值不作为目标。

11

12

其他: 期货基金 期权基金 指数基金 QDII基金

13

第二节 开放式基金

一、基金的发行与交易

开放式基金:发行基金单位数额不固定,投资者可随时认购 或赎回基金单位,认购或赎回的价格按基金净资产值计算。 发行与交易的特点: 1. 柜台发行:在基金管理公司的柜台发行。 2. 由代理人发行。发行人不是具有独立的法人资格的基金 公司,而是作为受托人的基金管理公司。 3. 在认购一段时间后(3个月),基金持有人可将基金反售 给发行人,发行人可将这些基金证券继续出售。 4. 基金证券的发售价格依基金证券每单位净资产的变动而 不同。 5. 基金发行数量没有限额。

第11章 证券投资基金

第一节

投资基金的基础

一、投资基金

通过发行基金单位,集中投资者的资金,由 基金托管人托管,由基金管理人管理和运用资金, 从事股票、债券、外汇、货币等金融工具投资, 以获得收益。

2

投资基金分类:

1. 按能否增加或赎回分:

开放式基金:基金设立后,投资者可以随时申购 或赎回基金单位,基金规模不固定。

二、基金的定价与费率

开放式基金单位的交易价格:通常来讲, 1. IPO呈现溢价:溢价通常认为代表发行费用 和与创立相关的起步费。 2. 封闭式基金发行后若干时间,溢价变为折扣。 此后,偶有变溢价,折扣也会大副波动。

3. 封闭式基金开放时,其市价上升至基金净值 水平。

4. 费率较低。

19

20

三、基金的收益分配与清盘