CHP3存储器

大地电磁学_chp3一维正演

3.1 电磁场基本方程式

• 物质方程:

D E 1 H B j E (3 5) (3 6) (3 7)

• 为介质的介电常数(电容率), 为导磁率,这些 参数较多地以相对介电常数 r 和相对导磁率 r形式 给出,它们是介质参数 或 和真空中相应的参数 0或 0的比值。

3.3 层状一维介质的正演问题

• (一)、水平层状一维介质中的电磁波 与均匀各向同性介质的大地电磁波相同之处:

1. 水平方向电磁波均匀,均可分成两组线性偏振波(TE 波、TM波) 2. E和H正交,无垂直分量(Ez、Hz=0) 3. 波阻抗与测量轴方向无关。

不同之处:

1. 由于电性分界面的存在,电磁波发生反射和透射 2. 界面阻抗概念

E i H H E H 0 E 0

• 第四个方程是因为导电介质内部电荷密度实际上 为0,公式时间因子隐含在场E和H中,上式是大 地电磁测深理论研究的出发点。

3.1 电磁场基本方程式

(三)、电磁场波动方程与边界条件 将大地电磁场满足的谐变场麦克斯韦方程组的第 一个方程两边取旋度,并将第二个方程代入,可 得 E i ( H) i E 2 2 由于 E ( E) E E 2 2 2 从而得到 E i E ,或写成 E k E 0 其中,k 2 i k i

H y H0 ye

it

e

2

z (1i )

10 T

• 它表示随时间谐变的电磁场在均匀各向同性的大 地介质中传播时,沿传播方向是谐变的,并且按 指数规律衰减。 • 集肤深度(穿透深度):场幅衰减到地面值的1/e 时电磁波所传播的距离,用p来表示: 2 p 1

chp3

CAI

14

3.3 DRAM存储器

3.3.1 DRAM存储位元的记忆原理 3.3.2 DRAM芯片的逻辑结构 3.3.3 读/写周期、刷新周期 3.3.4 存储器容量的扩充 3.3.5 高级的DRAM结构 3.3.6 DRAM主存读/写的正确性校验

15

3.3.1 DRAM存储位元的记忆原理

SRAM存储器的存储位元是一个触发器, 它具有两个稳定的状态。而DRAM存储器的存 储位元是由一个MOS晶体管和电容器组成的 记忆电路,如图3.6所示。

读与写的互锁逻辑 控制信号中CS是片选信号, CS有效时(低电平),门G1、G2 均被打开。OE为读出使能信号, OE有效时(低电平),门G2开启, 当写命令WE=1时(高电平),门 G1关闭,存储器进行读操作。写操 作时,WE=0,门G1开启,门G2 关闭。注意,门G1和G2是互锁的, 一个开启时另一个必定关闭,这样 保证了读时不写,写时不读。

3

3.1.2 存储器的分级

目前存储器的特点是:

• 速度快的存储器价格贵,容量小; • 价格低的存储器速度慢,容量大。

在计算机存储器体系结构设计时,我们希 望存储器系统的性能高、价格低,那么在存储 器系统设计时,应当在存储器容量,速度和价 格方面的因素作折中考虑,建立了分层次的存 储器体系结构如下图所示。

8

3.2.1 基本的静态存储元阵列

1、存储位元 2、三组信号线

CAI

地址线 数据线

行线 列线

控制线

9

3.2.2 基本的SRAM逻辑结构

SRAM芯大多采用 双译码方式,以便 组织更大的存储容 量。采用了二级译 码:将地址分成x 向、y向两部分如 图所示。

chp3 酒店财务会计记账过程

Transfer journal information to ledger account

3.2.1General journal

General Journal

J1

Date Accounts Titles and Explanation

4.The Trial Balance

5.Electronic Data Processing

3.1 The Accounts

An individual accounting record of increases and decrease in…

Account A basic storage unit for data

300

100000

100 50000

220

50000

Account Title Cash Date Accounts/Explanation Jan Initial investment

Loan from bank

Account No.

Ref.

4 GJ1

GJ1

100 Debit 100000 50000

Assets

100-199

160 Property and Equipment 161 Land 162 Buildings 163 Accumulated Depreciation-Buildings 164 Leaseholds and Leaseholds

Improvements 165 Accumulated Depreciation- Leaseholds 166 Furniture and Fixtures 167 Accumulated Depreciation- Furniture

FPGA可编程逻辑器件芯片XCKU3P-2FFVB676I中文规格书

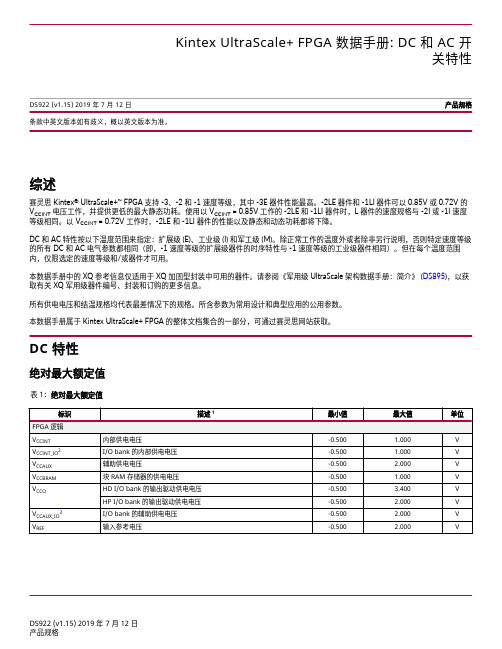

综述赛灵思 Kintex ® UltraScale+™ FPGA 支持 -3、-2 和 -1 速度等级,其中 -3E 器件性能最高。

-2LE 器件和 -1LI 器件可以 0.85V 或 0.72V 的V CCINT 电压工作,并提供更低的最大静态功耗。

使用以 V CCINT = 0.85V 工作的 -2LE 和 -1LI 器件时,L 器件的速度规格与 -2I 或 -1I 速度等级相同。

以 V CCINT = 0.72V 工作时,-2LE 和 -1LI 器件的性能以及静态和动态功耗都将下降。

DC 和 AC 特性按以下温度范围来指定:扩展级 (E)、工业级 (I) 和军工级 (M)。

除正常工作的温度外或者除非另行说明,否则特定速度等级的所有 DC 和 AC 电气参数都相同(即,-1 速度等级的扩展级器件的时序特性与 -1 速度等级的工业级器件相同)。

但在每个温度范围内,仅限选定的速度等级和/或器件才可用。

本数据手册中的 XQ 参考信息仅适用于 XQ 加固型封装中可用的器件。

请参阅《军用级 UltraScale 架构数据手册:简介》 (DS895),以获取有关 XQ 军用级器件编号、封装和订购的更多信息。

所有供电电压和结温规格均代表最差情况下的规格。

所含参数为常用设计和典型应用的公用参数。

本数据手册属于 Kintex UltraScale+ FPGA 的整体文档集合的一部分,可通过赛灵思网站获取。

DC 特性绝对最大额定值Kintex UltraScale+ FPGA 数据手册: DC 和 AC 开关特性条款中英文版本如有歧义,概以英文版本为准。

表 18:LVDS_25 DC 规格标识DC 参数最小值典型值最大值单位V CCO1供电电压 2.375 2.500 2.625V1003506002mV V IDIFF差分输入电压:(Q - Q), Q = High(Q - Q), Q = HighV ICM输入共模电压0.300 1.200 1.425V 注释:1.HD I/O bank 中的 LVDS_25 仅支持输入。

MSP430寄存器配置指导

微控网为你准备的 MSP430F 单片机入门必修课

微控网

MSP430F1XX 系列时钟模块图 时基模块结构如上图:

MSP430 系列单片机基础时钟主要是由低频晶体振荡器,高频晶体振荡器,数字控制 振荡器(DCO),锁频环(FLL)及 FLL+等模块构成。由于 430 系列单片机中的型号不同, 而时钟模块也将有所不同。虽然不同型号的单片机的时基模块有所不同,但这些模块产 生出来的结果是相同的.在 MSP430F13、14 中是有 TX2 振荡器的,而 MSP430F11X,F11X1 中是用 LFXT1CLK 来代替 XT2CLK 时钟信号的.在时钟模块中有 3 个(对于 F13,F14)时钟 信号源(或 2 个时钟信号源,对于 F11X、F11X1):

BCSCTL1 基本时钟系统控制寄存器 1

7

6

5

4

XT2OFF TXS DIVA.1 DIVA.0

3 XT5V

2

1

0

Rsel.2 Resl.1 Resl.0

XT2OFF 控制 XT2 振荡器的开启与关闭。 TX2OFF=0,XT2 振荡器开启。 TX2OFF=1,TX2 振荡器关闭(默认为 TX2 关闭)

微控网

句:_BIS_SR(LMP3_bits)和_BIC_SR(LPM3 bits) LPM3 和 LPM3_EXIT

它们的定义是一样的。这里说明在 C 语言环境中有些定义的函数是不可见的。但你可以 从 in430.h 文件看到它们的定义。

DCOCTL DCO 控制寄存器

cctlx捕获比较控制寄存器151413121110ccis1scssccicapoutmodxcciexccioutcovccifxtimera有多个捕获比较模块每个模块都有自己的控制寄存器cctlxcaptmod10选择捕获模式00禁止捕获模式01上升沿捕获10下降沿捕获11上升沿与下降沿都捕获ccisi0在捕获模式中用来定提供捕获事件的输入端00选择ccixa01选择ccixb10选择gnd11选择vccscs选择捕获信号与定时器时钟同步异步关系0异步捕获1同步捕获异步捕获模式允许在请求时立即将ccifg置位和捕获定时器值适用于捕获信号的周期远大于定时器时钟周期的情况

Chp-3 硬件层 -5 计算部件

用户触摸屏幕时,会打断光束,此时能够确定断点的位 置

28

触摸屏

声表面波 (SAW)

把在水平和竖直坐标轴上的相交的高频声波投射到屏幕的 表面

当手指触摸到屏幕时,相应的传感将检测到断点,并确定触 摸的位置

29

同步处理

一种并行方法是用多个处理器把同一个程序应用到多个数据 集上

23

触摸屏

触摸屏 能探测到用户在屏幕上用手指或书写笔的触摸,并 作出响应。 这儿有三种类型:

电阻式 电容式 红外 声表面波 (SAW)

24

触摸屏

图 5.6 触摸屏

25

触摸屏

电阻式触摸屏 由两个由导电材料制成的分层构成

一层是水平线,一层是竖直线 当上面的分层被按下以后,它将与下面的分层接触, 使电流流通 接触的竖直线和水平线说明了触摸屏的位置

第五章

计算部件

章节目标

读懂一则计算机广告,明白其中的话。 列出冯•诺伊曼机的部件和它们的功能。 描述冯•诺伊曼机的读取—译解—执行周期。

2

章节目标

描述如何组织和访问计算机内存。 列出并描述不同的辅助存储设备。 定义三种并行计算机的配置。

3

计算机部件

请看下面一则台式电脑的广告:

为什么?

21

磁盘

寻到时间 读写头定位到指定的磁道所花费的时间 等待时间 把指定的扇区定位到读写头之下所花费的时间 存取时间

你能定义它吗?

22

光盘

CD 使用激光读取存储在塑料盘上的信息;数据是均匀分布在整 个光盘上的。 CD-ROM 只读存储器 CD-DA 音频光盘 CD-WORM 一次写入多次读出光盘 RW or RAM 既能读又能写 DVD 数字化视频光盘(Digital Versatile Disk), 能够存放集合了 音频和视频的多媒体信息。

chp-3 运输解析

2018/10/16

case

6

根据管理目的制定了一些物流管理方案。很重要的一条应该就是

,出车登记表的使用,主要作用是收集历史数据、观察工作效率、 实施成本监督、反映工作问题、提供提升依据。 其实,把司机或配送人员的工资和配送成本结合起来,会取得不 错的效果,但是当配送增加的收益小到不能激发司机和配送人员 的公司利益第一的思想认识的时候,结合出车登记表的管理,就 非常的有必要了。 当然,还有很多好的制度管理方法,正所谓,寸有所长,尺有所 短。要让任何一种管理方法真正发挥它的积极作用,要结合自身 情况加以融会贯通。并要求不懈的坚持。 把制度执行成习惯,才 能达到无为管理的至高境界

18

2018/10/16

邮政运输少不得的是邮车

19

2018/10/16

20

蒸汽机

2018/10/16

21

内燃机车

2018/10/16

22

电力机车

下一页 小资料:英国皇家邮政局运输装备变迁

2018/10/16

运输的作用

23

可以创造商品的空间效用,实现商品价值 可以扩大商品的销售范围,提高人民生活水平

2018/10/16

case

28

美国布鲁克林酿酒厂的物流策略 布鲁克林酿酒厂是一家美国公司,却在日本市场取得了巨大

成功,每年销售额达到200亿美元,其秘诀之一就是将产品 —啤酒空运到日本,以保证其独一无二的新鲜度。 在次之前,由于空运的高成本无一家企业通过航运啤酒到日 本。布鲁克林酿酒厂于1989年11月将它的第一箱布鲁克林拉 格运到日本,并在最初的几个月里使用了各种航运承运人。 最后,日本金刚砂航运公司被选为布鲁克林酿酒厂唯一的航 运承运人。金刚砂公司之所以被选中,是因为它向布鲁克林 酿酒厂提供了增值服务。金刚砂公司在其国际机场的终点站 交付啤酒,并在飞往东京的商航班上安排运输,金刚砂公司 通过其日本报关办理清关手续。这些服务有利于保证产品完 全符合保鲜要求。

陕西师范大学_计算机组成原理_课件ppt_白中英第5版_chp3

∙31/171∙ 陕西师范大学 计算机科学学院

图(a)表示写1到存储 位元。此时输出缓 冲器关闭、刷新缓 冲器关闭,输入缓 冲器打开(R/W为 低),输入数据 DIN=1送到存储元位 读放 线上,而行选线为 高,打开MOS管, 于是位线上的高电 平给电容器充电, 表示存储了1。

播放I

MOS管

∙27/171∙ 陕西师范大学 计算机科学学院

3.2 SRAM存储器

∙28/171∙ 陕西师范大学 计算机科学学院

3.2 SRAM存储器

∙29/171∙ 陕西师范大学 计算机科学学院

3.3 DRAM存储器

一、DRAM存储位元的记忆原理

› ›

SRAM存储器的存储位元是锁存器,它具 有两个稳定的状态。 DRAM存储器的存储位元是由一个MOS 晶体管和电容器组成的记忆电路,如图 3.6所示。

图(c)表示从存储位 元读出1。输入缓冲 器和刷新缓冲器关闭, 输出缓冲器/读放打 开(R/W为高)。行 选线为高,打开 MOS管,电容上所 存储的1送到位线上, 通过输出缓冲器读出 放大器发送到DOUT, 即DOUT=1。

∙34/171∙ 陕西师范大学 计算机科学学院

图(d)表示(c)读出1后 存储位元重写1。由于 (c)中读出1是破坏性 读出,必须恢复存储 位元中原存的1。此时 输入缓冲器关闭,刷 新缓冲器打开,输出 缓冲器读放打开, DOUT=1经刷新缓冲器 送到位线上,再经 MOS管写到电容上。

∙14/171∙ 陕西师范大学 计算机科学学院

3.2 SRAM存储器

主存(内部存储器)是半导体存储器。根

据信息存储的机理不同可以分为两类: 相对而言 › 静态读写存储器(SRAM): 存取速度快,一般用作Cache › 动态读写存储器(DRAM): 存储容量大,一般用作主存

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1、某半导体存储器总容量4Kⅹ8。

其中固化区2K字节,选用EPROM芯片2716(2Kⅹ8);

工作区2K字节,选用SRAM芯片2114(1Kⅹ4)。

确定需要的芯片型号和数量,画出图并求出每个芯片的地址范围。

存储器总容量为4Kⅹ8,共12条地址线A0~A11,8条数据线,各存储器芯片的地址分配和片选逻辑如下表。

先确定所需芯片数:固化区2Kⅹ8,需2716一块;工作区2Kⅹ8,2块2114拼接为一组容量为1Kⅹ8,需2组,共4块2114。

见下图。

2.某以8088为CPU的微型计算机内存RAM区为00000H~3FFFFH,若采用6264(8KX8)、62256(32KX8)、2164(8KX4)、21256(32KX4)各需要多少芯片?其各自的片内和片间地址线分别是多少(全地址译码方式)?

3.利用全地址译码将6264芯片接在8088系统总线上,地址范围为BE000H~BFFFFH,试画出连接电路图。

A13A14A15A16A17A19MEMW A0A1

A12

D0BUS

8088系统

A18

4.RAM 6116芯片有2K×8位的容量,它的片内地址选择线和数据线分别是 。

A)A0~A15和D0~D15 B)A0~A10和D0~D7 C)A0~A11和D0~D7 D)A0~A11和D0~D15

5. 用一片EPROM 芯片构成系统内存,其地址范围为F0000H ~F0FFFH ,无地址重叠,该

内存的存储容量为 。

A)2KB B)4KB C)8KB D)16KB

1.00000H ~3FFFFH 所占的存储空间为:40000H=218

=256kX8bit ∴若采用

6264(8KX8) 则需要(256kX8)/(8kX8)=32(片)

6264的片内地址线是13根,片间地址线是7根(全地址译码); 62256(32KX8) 则需要(256kX8)/(32kX8)=8(片)

62256的片内地址线是15根,片间地址线是5根(全地址译码); 2164(8KX4) 则需要(256kX8)/(8kX4)=64(片)

2164的片内地址线是13根,片间地址线是7根(全地址译码); 21256(32KX4) 则需要(256kX8)/(32kX4)=16(片)

21256的片内地址线是15根,片间地址线是5根(全地址译码);。