同步二、十进制计数器共30页

同步和异步十进制加法计数器的设计

同步和异步十进制加法计数器的设计全文共四篇示例,供读者参考第一篇示例:同步和异步是计算机系统中常用的两种通信机制,它们在十进制加法计数器设计中起到了至关重要的作用。

在这篇文章中,我们将深入探讨同步和异步十进制加法计数器的设计原理及应用。

让我们来了解一下十进制加法计数器的基本概念。

十进制加法计数器是一种用于执行十进制数字相加的数字电路。

它通常包含多个十进制加法器单元,每个单元用于对应一个十进制数位的运算。

在进行加法操作时,每个数位上的数字相加后,可能会产生进位,这就需要进位传递的机制来满足计数器的正确操作。

在同步十进制加法计数器中,每个十进制加法器单元都与一个时钟信号同步,所有的操作都按照时钟信号的节拍来进行。

具体来说,当一个数位的加法计算完成后,会将结果通过进位端口传递给下一个数位的加法器单元,这样就能确保每个数位的计算都是按照特定的顺序来进行的。

同步十进制加法计数器的设计较为简单,在时序控制方面有很好的可控性,但由于需要受限于时钟信号的频率,其速度受到了一定的限制。

在实际应用中,根据不同的需求可以选择同步或异步十进制加法计数器。

如果对计数器的速度要求较高,并且能够承受一定的设计复杂度,那么可以选择异步设计。

如果对计数器的稳定性和可控性要求较高,而速度不是首要考虑因素,那么同步设计可能更为适合。

无论是同步还是异步,十进制加法计数器的设计都需要考虑诸多因素,如延迟、数据传输、进位控制等。

通过合理的设计和优化,可以实现一个高性能和稳定的十进制加法计数器,在数字电路、计算机硬件等领域中有着广泛的应用。

同步和异步十进制加法计数器的设计都有其各自的优势和劣势,需要根据具体的需求来选择合适的设计方案。

通过不断的研究和实践,我们可以进一步完善十进制加法计数器的设计,为计算机系统的性能提升和应用拓展做出贡献。

希望这篇文章能够为大家提供一些启发和帮助,让我们共同探索数字电路设计的奥秘,开拓计算机科学的新境界。

第二篇示例:同步和异步计数器都是数字电路中常见的设计,用于实现特定的计数功能。

二进制十进制同步加法计数器 逻辑ic芯片

二进制十进制同步加法计数器逻辑ic芯片二进制十进制同步加法计数器是一种逻辑集成电路(IC)芯片,可用于进行二进制的加法和计数操作。

它主要由逻辑门和触发器构成,能够实现数字计数与加法运算的功能。

在本文中,我将详细介绍二进制十进制同步加法计数器的工作原理、设计流程以及应用场景。

首先,让我们了解一下二进制和十进制的概念。

二进制是一种由0和1组成的数制,用来表示数字和进行计算。

而十进制是指以10为基数的数制,由0至9的数字组成。

二进制数字的加法和十进制数字的加法有着类似的原理,但操作方法稍有不同。

二进制十进制同步加法计数器的主要功能是进行加法和计数操作。

它能够将输入的二进制数值与当前内部存储的数值相加,并将结果输出。

在进行计数操作时,只需要连续输入0、1的脉冲信号即可完成对二进制数值的计数。

二进制十进制同步加法计数器的实现主要依赖于逻辑门和触发器。

逻辑门用来实现不同输入信号的逻辑运算,而触发器则用于存储并传递逻辑运算的结果。

常见的逻辑门有AND门、OR门、NOT门等,触发器常用的有RS触发器、D触发器等。

在设计二进制十进制同步加法计数器时,需要根据具体的需求来选择适当的逻辑门和触发器,并将它们按照一定的电路连接方式进行组合,以实现所需的功能。

以下是一个简单的设计流程供参考:1.确定计数器的位数:根据需求确定计数器需要的位数,决定计数范围和精度。

2.选择逻辑门和触发器:根据计数器的位数和功能需求选择适当的逻辑门和触发器。

3.连接逻辑门和触发器:按照设计需求将选择好的逻辑门和触发器进行连接,形成计数器的核心电路。

4.确定输入和输出信号:确定计数器的输入信号和输出信号,并设计合适的接口电路进行连接。

5.进行测试和调试:将设计好的电路进行实物搭建,并通过信号发生器等设备产生输入信号进行测试和调试。

二进制十进制同步加法计数器的应用场景非常广泛。

例如,在数字电路和计算机体系结构中,计数器被广泛用于时序控制、频率分频等功能的实现。

计数器的分类

1. 按照进位制数(计数器的模数)划分:★ 二进制计数器随着计数脉冲(时钟脉冲)的输入,按照二进制数规律计数的计数器称为二进制计数器,再具体划分,2个状态循环的是1位二进制计数器,4个状态循环的是2位二进制计数器,8个状态循环的是3位二进制计数器,以此类推。

★ 十进制计数器随着计数脉冲(时钟脉冲)的输入,按照十进制数规律计数的计数器称为十进制计数器,与二进制计数器的内涵不同的是,这里不区分位数,也就是说,十进制计数器就是10个状态循环的计数器。

★进制计数器 除了上述的二进制计数器和十进制计数器外,其他进制(其他 个状态循环)的计数器,都统称为进制计数器。

2. 按计数的增减趋势(状态迁移顺序)划分:★ 加法计数器工作循环中,状态以递增规律迁移的计数器就称为加法计数器,也叫递增计数器。

★ 减法计数器工作循环中,状态以递减规律迁移的计数器就称为减法计数器,也叫递减计数器。

★ 可逆计数器既可以进行递增计数,也可以进行递减计数的计数器,称为可逆计数器,也叫双向计数器。

一般而言,可逆计数器设置有加减控制信号,加减控制信号的不同信号输入,决定了该计数器具体的状态迁移顺序,上一节中,【例8.2.2】所示电路就是一个典型的可逆计数器。

3. 按时钟脉冲输入方式(计数器工作方式)划分:★ 同步计数器计数器电路中,使用的触发器类型相同,且共用相同的计数脉冲(时钟脉冲)信号时,就称为同步计数器,其内部的触发器的工作点一致,状态变化同时发生。

★ 异步计数器计数器电路中,使用的触发器的工作点不一致,状态变化的时间不一致,就称为异步计数器。

从电路结构上看,异步计数器内部,往往有的触发器的时钟信号是输入的计数脉冲,有的触发器的时钟信号却是其他触发器的输出状态。

N N N按照时钟脉冲输入方式来划分计数器种类,其实际含义,和时序逻辑电路分为同步时序电路和异步时序电路的划分是一致的,常常就称为计数器按照工作方式的区分。

综合上述三种分类方式,形成了计数器繁多的种类区分,如图8.3.1所示。

两位十进制计数资料

两位十进制计数器

电路结构及原理

用CD4518完成两位十进制计数,其中第一个十进制计数器接成:IEN端做计数允许端(高电平有效),1CP做计数时钟输入端(上升沿触发有效),进行个位数计数;第二个十进制计数器接成:2CP端做计数允许端(低电平有效),2EN做计数时钟输入端(下降沿触发有效,从第一个十进制计数器的1Q3做进位脉冲提供,异步计数连接方式),进行十进数的计数。

两位计数器输出的8421BCD码直接输入各自的译码驱动芯片CD4511进行译码。

序号元件名称标称参数型号数量。

同步计数器

根据二进制加法运算规则可知,在一个多位二进制数的末位上加1时, 若其中第 i 位(即任何一位)以下各位皆为1时,则第 i 位应改变状态 (由0变成1,由l变成0)。而最低位的状态在每次加1时都要改变。

由此,当计数器用 T 触发器构成时,第 i 位触发器输入端的逻,n-1) 只有最低位例外,每次输入计数脉冲时它都要翻转,故T0=1

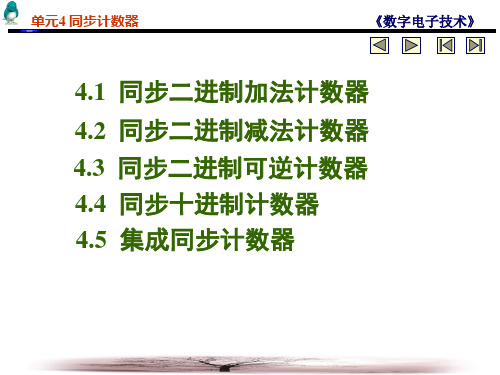

单元4 同步计数器

《数字电子技术》

单元4 同步计数器

《数字电子技术》

单元4 同步计数器

《数字电子技术》

单元4 同步计数器

课堂练习

《数字电子技术》

1、试分析时序电路的逻辑功能,写出电路的驱动方程、状 态方程和输出方程,画出电路状态转换图,检查电路能否 自启动。

R ____

J

____

K

____

F

;

单元4 同步计数器

《数字电子技术》

(2)圆心编程

圆心编程

条件

平面选择

旋转方向 G90时

终点位置 G时

圆心的坐标

指令 G17 G18 G19 G02 G03 X、Y、Z

X、Y、Z I、J、K

说明 圆弧在XY平面上 圆弧在ZX平面上 圆弧在YZ平面上

顺时针方向 逆时针方向 终点数据是工件坐标系中的坐标值

自动倒棱角

在倒棱/倒角过程中有的情况在倒角/倒棱前加“,”; 有的情况下不加

N0010 G91 G01 X100.0,C10.0; N0020 X100.0 Y100.0;

单元4 同步计数器

《数字电子技术》

单元4 同步计数器

2.任意角度倒棱角C/倒圆弧R

R后的数值指令倒圆R的半径值。 N0010 G91 G01 X100.0,R10.0; N0020 X100.0 Y100.0;

同步十进制计数器

同步与异 步十进制计数 器的功能和工 作波形相同, 但时钟控制方 式及电路构成 不同。 计数顺序 0 1 2 3 4 5 6 7 8 9 10 计

Q3 0 0 0 0 0 0 0 0 1 1 0

数 器 状 Q2 Q1 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 0 0 0 0 0 0

本节小结:

计数器是一种应用十分广泛的时序电路,除 用于计数、分频外,还广泛用于数字测量、运算 和控制,从小型数字仪表,到大型数字电子计算 机,几乎无所不在,是任何现代数字系统中不可 缺少的组成部分。 计数器可利用触发器和门电路构成。但在实 际工作中,主要是利用集成计数器来构成。在用 集成计数器构成N进制计数器时,需要利用清零 端或置数控制端,让电路跳过某些状态来获得N 进制计数器。

Q0高 Q1高 Q2高 Q3高 CTT CT74LS161 CO CTP (高位) CR LD D0 D1 D2 D3 1 1 × ×××

1

1

1 × ×××

讨论

将上图中的“161”换成“160”,则构成几进制计数器?

讨论总结

(1)两个十进制计数器级联构成 100 进制计数器。从高位 Q3 Q2 Q1 Q0 读出的是十位数,而从低位 Q3 Q2 Q1 Q0 读出 的是个位数。 (2)两个 4 位二进制计数器级联则构成 8 位二进制计数器, 即 256 进制计数器。从高位 Q3 Q2 Q1 Q0 读出的是高 4 位 二进制数,而从低位 Q3 Q2 Q1 Q0 读出的是低 4 位二进制

方案 2: 用 “160” 的后七个状态 0011 ~ 1001 实现七进制计数。 计数顺序 0 1 2 3 4 5 6 7 8 9 10 计 数 器 状 态 进位输出 Q3 Q2 Q1 Q0 CO 0 0 0 0 0 D3D2D1D0=0011 0 0 0 1 0 0 0 1 0 0 0 0 1 1 0 0 1 0 0 0 0 1 0 1 0 0 1 1 0 0 LD = Q3 Q0或CO 0 1 1 1 0 1 0 0 0 0 1 0 0 1 1 0 0 0 0 0

十进制同步加法计数器

性能测试

测试环境

为保证测试结果的准确性和可靠 性,需要搭建一个标准的测试环 境,包括适当的电源、时钟源、

输入信号和输出负载等。

测试方法

按照规定的测试方法,对计数器的 各项性能指标进行测试,如计数范 围、计数速度、功耗和集成度等。

测试数据记录

详细记录测试过程中的各项数据, 如输入信号的频率、电源电压、输 出信号的状态等。

THANK YOU

感谢各位观看

发。

十进制同步加法计数器是一种同步计数 器,它可以在时钟信号的控制下进行加

法运算,并输出十进制数的计数值。

Hale Waihona Puke 02十进制同步加法计数器的工作原理

同步计数器的概念

同步计数器

一种数字逻辑电路,能够按照给 定的时钟信号进行计数操作。

工作原理

在每个时钟周期内,同步计数器 对输入的时钟信号进行检测,并 根据时钟信号的变化进行计数操 作。

05

十进制同步加法计数器的性能分析

性能指标

计数范围

计数速度

计数器的最大计数值和最小计数值,即其 能计数的十进制数的范围。

计数器完成一次计数操作所需的时间,通 常以纳秒或微秒为单位。

功耗

集成度

计数器在工作过程中消耗的电能,通常以 毫瓦或瓦为单位。

计数器内部电路的规模和复杂度,通常以 门电路的数量来表示。

进位输出

当计数器达到9态时,会产生一个 进位输出信号,表示需要将这个 进位值加到更高位的计数器中。

回零操作

在每个时钟周期结束时,计数 器会自动回零,即回到0态,准

备进行下一次计数操作。

03

十进制同步加法计数器的设计

设计步骤

确定计数器的进制

电路中的计数器和触发器

电路中的计数器和触发器计数器和触发器是电路中常用的数字逻辑元件,它们在电子设备和计算机系统中扮演着重要的角色。

本文将重点介绍计数器和触发器的基本原理、工作方式以及应用领域。

一、计数器计数器是一种能够在一定条件下实现自动计数的电子元件。

它能够按照一定规律进行数字计数,并在达到预设值时产生相应的输出信号。

常见的计数器有二进制计数器、十进制计数器等。

1. 二进制计数器二进制计数器是最基本的计数器之一。

它使用二进制数字表示计数值,每次计数递增或递减1。

例如,一个4位二进制计数器可以从0000计数到1111,在达到1111后重新回到0000。

二进制计数器通常由触发器构成,触发器在计数信号的驱动下进行状态变化。

2. 十进制计数器十进制计数器是按照十进制数字进行计数的计数器。

它通常由多个二进制计数器组合而成,每个二进制计数器负责计数一个十进制位。

例如,一个4位十进制计数器可以从0000计数到9999,在达到9999后重新回到0000。

3. 同步计数器和异步计数器计数器可以分为同步计数器和异步计数器。

同步计数器的各个触发器按照统一的时钟信号进行状态变化,计数过程同步进行。

而异步计数器的各个触发器可以独立地进行状态变化,计数过程异步进行。

二、触发器触发器是一种能够储存和改变输入信号状态的器件。

它可以进行状态的存储和传递,常用于电路中的时序控制和存储元件。

常见的触发器有RS触发器、D触发器、JK触发器等。

1. RS触发器RS触发器是最简单的触发器之一。

它由两个交叉连接的非门和一个反馈路径构成。

RS触发器有两个输入端S和R,通过控制这两个输入端的状态,可以实现触发器的置位(Set)和复位(Reset)操作。

2. D触发器D触发器是基于RS触发器发展而来的触发器。

它只有一个输入端D,通过时钟信号的控制实现输入信号的存储和传递。

D触发器常用于时序控制电路和寄存器中。

3. JK触发器JK触发器是一种全功能触发器,可以实现RS触发器和D触发器的所有功能,同时具有更高的稳定性。