4同步二进制加法计数器

11级数字逻辑与数字系统练习题答案

页眉内容1.一位十六进制数可以用 C 位二进制数来表示。

2.十进制数25用8421BCD 码表示为 B 。

3. 以下表达式中符合逻辑运算法则的是 D 。

A . 1B . 2C . 4D . 16 A .10 101 B .0010 0101 C . D .10101 A .C ·C =C 2 B .1+1=10 C .0<1 D .A +1=14. 当逻辑函数有n 个变量时,共有 D 个变量取值组合? 5.A+BC= C 。

6.在何种输入情况下,“与非”运算的结果是逻辑0。

DA. nB. 2nC. n 2D. 2n A .A +B B.A +C C.(A +B )(A +C ) D.B +C A .全部输入是0 B.任一输入是0 C.仅一输入是0 D.全部输入是17. 以下电路中可以实现“线与”功能的有 C 。

8.以下电路中常用于总线应用的有 A 。

A .与非门B .三态输出门C .集电极开路门D . C M O S 与非门 A .T S L 门 B .O C 门 C . 漏极开路门D .C M O S 与非门9.若在编码器中有50个编码对象,则要求输出二进制代码位数为 B 位。

10.一个16选一的数据选择器,其地址输入(选择控制输入)端有 C 个。

A .5B .6C .10D .50 A .1 B .2 C .4 D .1611.四选一数据选择器的数据输出Y 与数据输入X i 和地址码A i 之间的逻辑表达式为Y = A 。

A .3X A A X A A X A A X A A 01201101001+++B .001X A AC .101X A AD .3X A A 0112.一个8选一数据选择器的数据输入端有 E 个。

A .1B .2C .3D .4E .813.在下列逻辑电路中,不是组合逻辑电路的有 D 。

A .译码器B .编码器C .全加器D .寄存器14.八路数据分配器,其地址输入端有 c 个。

数字电子技术基础第四章习题及参考答案

数字电子技术基础第四章习题及参考答案第四章习题1.分析图4-1中所示的同步时序逻辑电路,要求:(1)写出驱动方程、输出方程、状态方程;(2)画出状态转换图,并说出电路功能。

CPY图4-12.由D触发器组成的时序逻辑电路如图4-2所示,在图中所示的CP脉冲及D作用下,画出Q0、Q1的波形。

设触发器的初始状态为Q0=0,Q1=0。

D图4-23.试分析图4-3所示同步时序逻辑电路,要求:写出驱动方程、状态方程,列出状态真值表,画出状态图。

CP图4-34.一同步时序逻辑电路如图4-4所示,设各触发器的起始状态均为0态。

(1)作出电路的状态转换表;(2)画出电路的状态图;(3)画出CP作用下Q0、Q1、Q2的波形图;(4)说明电路的逻辑功能。

图4-45.试画出如图4-5所示电路在CP波形作用下的输出波形Q1及Q0,并说明它的功能(假设初态Q0Q1=00)。

CPQ1Q0CP图4-56.分析如图4-6所示同步时序逻辑电路的功能,写出分析过程。

Y图4-67.分析图4-7所示电路的逻辑功能。

(1)写出驱动方程、状态方程;(2)作出状态转移表、状态转移图;(3)指出电路的逻辑功能,并说明能否自启动;(4)画出在时钟作用下的各触发器输出波形。

CP图4-78.时序逻辑电路分析。

电路如图4-8所示:(1)列出方程式、状态表;(2)画出状态图、时序图。

并说明电路的功能。

1C图4-89.试分析图4-9下面时序逻辑电路:(1)写出该电路的驱动方程,状态方程和输出方程;(2)画出Q1Q0的状态转换图;(3)根据状态图分析其功能;1B图4-910.分析如图4-10所示同步时序逻辑电路,具体要求:写出它的激励方程组、状态方程组和输出方程,画出状态图并描述功能。

1Z图4-1011.已知某同步时序逻辑电路如图4-11所示,试:(1)分析电路的状态转移图,并要求给出详细分析过程。

(2)电路逻辑功能是什么,能否自启动?(3)若计数脉冲f CP频率等于700Hz,从Q2端输出时的脉冲频率是多少?CP图4-1112.分析图4-12所示同步时序逻辑电路,写出它的激励方程组、状态方程组,并画出状态转换图。

数字电路-练习B

数字电子技术练习一、填空题1.=⊕⊕⊕4434421K A偶数个A A A ① 。

2.逻辑函数F=A +B+C D 的反函数F = ① ,对偶式为 ②。

触发器的特征方程为 ① ,JK 触发器的特征方程为 ② 。

4.构造一个模10计数器需要 ① 个状态, ② 个触发器。

5.将JK 触发器的J 端和K 端连在一起,就得到了 ① 触发器。

6. ① 型触发器克服了空翻现象。

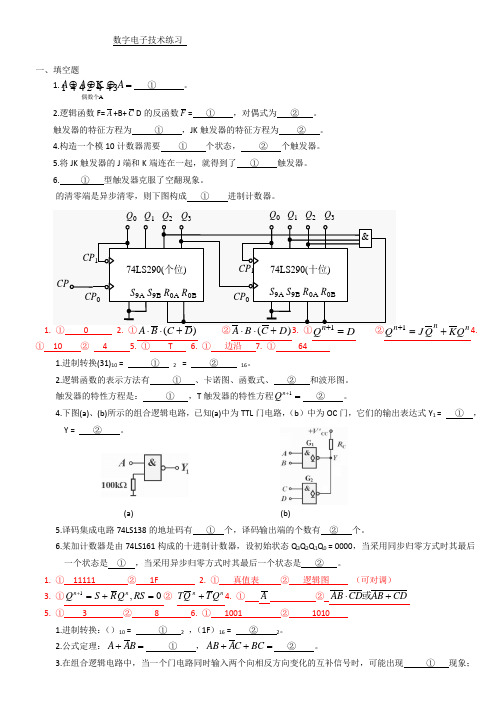

的清零端是异步清零,则下图构成 ① 进制计数器。

1. ① 02. ①)(D C B A +⋅⋅ ②)(D C B A +⋅⋅3. ①D Q n =+1 ②n nn Q K Q J +=+1 4.① 10 ② 4 5. ① T 6. ① 边沿 7. ① 641.进制转换(31)10 = ① 2 = ② 16。

2.逻辑函数的表示方法有 ① 、卡诺图、函数式、 ② 和波形图。

触发器的特性方程是: ① ,T 触发器的特性方程=+1n Q② 。

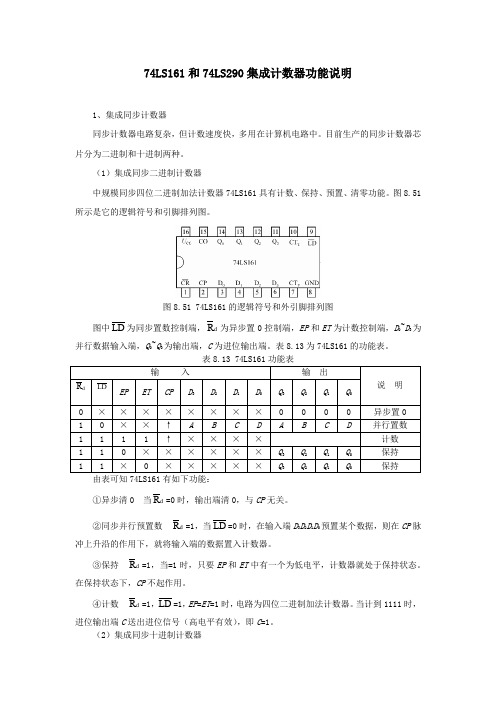

4.下图(a)、(b)所示的组合逻辑电路,已知(a)中为TTL 门电路,(b )中为OC 门,它们的输出表达式Y 1 = ① ,Y = ② 。

(a)(b)5.译码集成电路74LS138的地址码有 ① 个,译码输出端的个数有 ② 个。

6.某加计数器是由74LS161构成的十进制计数器,设初始状态Q 3Q 2Q 1Q 0 = 0000,当采用同步归零方式时其最后一个状态是 ① ,当采用异步归零方式时其最后一个状态是 ② 。

1. ① 11111 ② 1F2. ① 真值表 ② 逻辑图 (可对调)3. ①0,1=+=+RS Q R S Qn n ② n n Q T Q T + 4. ① A ② CD AB CD AB +⋅或5. ① 3 ② 86. ① 1001② 10101.进制转换:()10 = ① 2 ,(1F )16 = ② 2。

2.公式定理:=+B A A ① ,=++BC C A AB ② 。

74LS161和74LS290集成计数器功能说明

74LS161和74LS290集成计数器功能说明1、集成同步计数器同步计数器电路复杂,但计数速度快,多用在计算机电路中。

目前生产的同步计数器芯片分为二进制和十进制两种。

(1)集成同步二进制计数器中规模同步四位二进制加法计数器74LS161具有计数、保持、预置、清零功能。

图8.51所示是它的逻辑符号和引脚排列图。

图8.51 74LS161的逻辑符号和外引脚排列图图中LD为同步置数控制端,d R为异步置0控制端,EP和ET为计数控制端,D0~D3为并行数据输入端,Q0~Q3为输出端,C为进位输出端。

表8.13为74LS161的功能表。

R=0时,输出端清0,与CP无关。

①异步清0 当dR=1,当LD=0时,在输入端D3D2D1D0预置某个数据,则在CP脉②同步并行预置数d冲上升沿的作用下,就将输入端的数据置入计数器。

R=1,当=1时,只要EP和ET中有一个为低电平,计数器就处于保持状态。

③保持d在保持状态下,CP不起作用。

R=1,LD=1,EP=ET=1时,电路为四位二进制加法计数器。

当计到1111时,④计数d进位输出端C送出进位信号(高电平有效),即C=1。

(2)集成同步十进制计数器集成同步十进制加法计数器74LS160的管脚图和功能表与74LS161基本相同,唯一不同的是74LS160是十进制计数器,而74LS161是二进制计数器。

2、集成异步计数器异步计数电路简单,但计数速度慢,多用于仪器、仪表中。

(1)集成计数器74LS290图8.52是二-五-十进制集成计数器74LS290的逻辑结构图。

它兼有二进制、五进制和十进制三种计数功能。

当十进制计数时,又有8421BCD 和5421BCD 码选用功能,表8.14是它的功能表。

95481213131011CP 0CP 1Q 0Q 1Q 3Q 2R O(1)R O(2)S 9(1)S 9(2)图8.52 74LS290的逻辑结构图由表可知,74LS290具有如下功能:①异步置0 当R 0(1)=R 0(2)=1且S 9(1)或S 9(2)中任一端为0,则计数器清零,即Q D Q C Q B Q A =0000。

4位同步二进制加法计数器计数最大值

4位同步二进制加法计数器是一种常见的数字电路,用于实现二进制计数。

它可以将二进制数字表示为电信号,并且在每次输入脉冲时进行递增。

下面将详细介绍4位同步二进制加法计数器及其计数的最大值。

一、4位同步二进制加法计数器的原理1. 4位同步二进制加法计数器由4个触发器组成,每个触发器对应一个二进制位。

当输入一个脉冲时,每个触发器根据前一位的状态以及输入脉冲的信号进行状态转换。

这样就实现了二进制数的递增。

2. 触发器之间通过门电路连接,用于控制触发器状态的变化。

这些门电路可以根据具体的设计选择不同的逻辑门,常见的有AND门、OR 门、NOT门等。

3. 4位同步二进制加法计数器是同步计数器,即所有触发器同时接收输入脉冲,确保计数的同步性。

二、4位同步二进制加法计数器的计数最大值1. 4位二进制数的表示范围是0~15,因此4位同步二进制加法计数器的计数最大值为15。

2. 在计数到15后,再输入一个脉冲,计数器将重新从0开始计数,即实现了循环计数。

三、4位同步二进制加法计数器的应用1. 4位同步二进制加法计数器常用于数字电子钟、信号发生器等数字电路中,用于实现计数和定时功能。

2. 它还可以作为其他数字电路的组成部分,用于构建更复杂的逻辑功能。

3. 在数字系统中,计数器是十分重要的组件,它能够实现数字信号的计数和控制,广泛应用于各种数字系统中。

4位同步二进制加法计数器是一种重要的数字电路,通过它可以实现对二进制数的递增计数。

其计数的最大值为15,应用领域广泛。

希望本文内容能够对读者有所启发。

四、4位同步二进制加法计数器的工作原理4位同步二进制加法计数器是一种晶体管数字集成电路,它利用触发器和逻辑门等基本元件构成,能够实现二进制数字的加法计数。

在4位同步二进制加法计数器中,每个触发器代表一个二进制位,通过输入脉冲的控制,能够实现对二进制数的递增计数。

具体来说,当输入一个脉冲信号时,4位同步二进制加法计数器会根据触发器之间的连线和逻辑门的作用,根据之前的状态和输入脉冲的信号进行状态转换,从而实现二进制数的递增。

数字电路复习题

一、判断题(对的打“√”,错的打“×”共20 分)1、对于多输入端的CMOS与非门,在使用时不用的输入端悬空即可()2、TTL与非门的输入端接地时,其输入电流为零()3、在TTL门电路输出需要线与连接时,必须使用集电极开路门()4、组合逻辑电路中一定含有触发器()5、由卡诺图化简法得出的表达式不一定是最简表达式()6、基本RS触发器受触发脉冲CP控制()7、JK触发器,J=K=1时是计数状态()8、译码器是时序逻辑电路()9、组成七进制计数器最少需要四个触发器()10、施密特触发器的正、负向阈值电压相同()一、判断题(对的打“√”,错的打“×”共20 分)1、对于多输入端的TTL与非门,在使用时不用的输入端悬空即可()2、CMOS与非门的输入端接地时,其输入电流为零()3、对于低电平有效的“三态与非门”,当控制端E=1时是高阻态()4、组合逻辑电路的输出不但和现在的输入有关还和原状态有关()5、由公式化简法得出的表达式不一定是最简表达式()6、同步RS触发器受触发脉冲CP控制()7、JK触发器,当置“1”端S D=0时触发器的状态为“1”()8、计数器是时序逻辑电路()9、组成十进制计数器最少需要四个触发器()10、施密特触发器的正、负向阈值电压不相同()一选择题1、在二进制译码器中,若输入有4位代码,则输出有()信号。

① 2个②4个③8个④16个2、在下列电路中,只有()属于组合逻辑电路。

①触发器②计数器③数据选择器④寄存器3、组合逻辑电路的竞争-冒险是由于()引起的。

①电路不是最简②电路有多个输出③电路中存在延迟④电路使用不同的门电路4、能实现从多个输入端中选出一路作为输出的电路称为()。

①触发器②计数器③数据选择器④译码器5、能完成两个1位二进制数相加并考虑到低位来的进位的器件称为()①编码器②译码器③全加器④半加器6、只本位数而不考虑低位来的进位的加法称为()①全加②半加③全减④半减7、用代码代表特定信号或将代码赋予特定含义的过程称为()①译码②编码③数据选择④奇偶校验8、把代码的特定含义翻译出来得过程称为()①译码②编码③数据选择④奇偶校验9、如需要判断两个二进制数的大小或相等,可以使用()电路。

4位同步二进制加法计数器

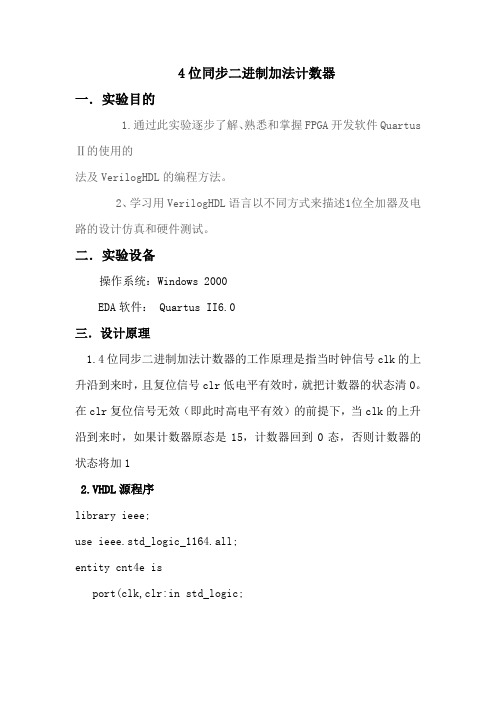

4位同步二进制加法计数器一.实验目的1.通过此实验逐步了解、熟悉和掌握FPGA开发软件Quartus Ⅱ的使用的法及VerilogHDL的编程方法。

2、学习用VerilogHDL语言以不同方式来描述1位全加器及电路的设计仿真和硬件测试。

二.实验设备操作系统:Windows 2000EDA软件: Quartus II6.0三.设计原理1.4位同步二进制加法计数器的工作原理是指当时钟信号clk的上升沿到来时,且复位信号clr低电平有效时,就把计数器的状态清0。

在clr复位信号无效(即此时高电平有效)的前提下,当clk的上升沿到来时,如果计数器原态是15,计数器回到0态,否则计数器的状态将加12.VHDL源程序library ieee;use ieee.std_logic_1164.all;entity cnt4e isport(clk,clr:in std_logic;cout:out std_logic;q:buffer integer range 0 to 15);end cnt4e;architecture one of cnt4e isbeginprocess(clk,clr)beginif clk'event and clk='1'thenif clr='1'thenif q=15 then q<=0;cout<='0';elsif q=14 then q<=q+1;cout<='1';else q<=q+1;end if;else q<=0;cout<='0';end if;end if;end process;end one;四.实验步骤:1.在Quartus II6.0中执行“file”->“new”命令,打开编辑文件类型对话框,选择"VHDL File",在文本框里输入源程序,并将文件cnt4e.vhd保存在创建的目录下。

数字逻辑、数电试卷【含答案】 (25)

第3章习题一、单选题1.1个触发器可记录一位二进制代码,它有(C )个稳态。

A)0 B)1 C)2 D)32.对于JK触发器,若J=K,则可完成(C )触发器的逻辑功能。

A)D B)RS C)T D)T'3.对于JK触发器,若K=J则可完成(A )触发器的逻辑功能。

A)D B)RS C)T D)T'4.基本RS锁存器输入端禁止的情况为(A )。

A)R=1 S=1 B)R=1 S=1C)R=0 S=0 D)RS=05.触发器的异步置位端Set、Clr不能同时取值为(A )。

A)Set=1,Clr=1 B)Set=0,Clr=0C)Set=1,Clr=0 D)Set=0,Clr=16.JK触发器在J、K端同时输入高电平,处于(D )功能。

A)置0 B)置1 C)保持D)翻转7.时序逻辑电路的特点是(C )。

A)仅由门电路组成B)无反馈通路C)有记忆功能D)无记忆功能8.4个触发器构成的8421BCD码计数器共有(A )个无效状态。

A)6 B)8 C)10 D)49.4位二进制计数器计数容量为(C )。

A)4 B)8 C)16 D)1010.要构成五进制计数器,至少需要(D )个触发器。

A)2 B)3 C)4 D)511.N进制计数器的特点是设初态后,每来(C )个Clk,计数器又重回初态。

A)N-1 B)N+1 C)N D)2N12.将两片4位二进制同步加法计数器芯片级联,最大可构成(C )进制计数器。

A)16 B)255 C)256 D)10013.由4个触发器组成的二进制加法计数器,当初始状态为1010时,经过(C )个Clk脉冲,计数器的状态会变为0101。

A)4 B)10 C)11 D)1614.触发器符号中Clk输入端的小圆圈表示(D )。

A)高电平有效B)低电平有效C)上升沿触发D)下降沿触发二、判断题1. 触发器有互补的输出,通常规定Q=1、Q=0称触发器为0态。

(✗)2. D触发器的特性方程为Q n+1=D,与Q n无关,所以它没有记忆功能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

QD QC QB QA

0000 0001 0010 0011 0100 /1 /0 10011000 0111 0110 0101

/0 /0 /0 /0

/0

/0

12 2 例:用三块74161构成 进制计数器

Q0

Q1 Q2

Q3

Q4

Q5

Q6

Q7

Q8

Q9

Q10

Q11

“1”

P QA QB QC QD T Oc CP Cr LD A B C D 1

4.同步二进制加法计数器

Q0

1 CP

J K Q F0 K J Q F1 K

Q1

J Q F2

Q2

Q0

1 CP

J K Q F0 K J Q F1

Q1

J K Q F2

Q2

(1)驱动方程:

J 0 K0 1 J 1 K1 Q0 J 2 K 2 Q 0011 0100 1010 /1 /0 暂态 10011000 0111 0110 0101

/0 /0 /0 /0

/0

/0

/0

/0

2.置位法 C “1” CP

P QA QB QC QD T Oc

CP Cr LD A B C D 1

同步置位 等下一个(第十 个)脉冲到来后 才置位。 /0 /0

6.同步二进制可逆计数器

Q0 Q1 1

J K Q F0 K J Q F1 K J Q F2

Q2

CP

X 当X=1时,是加法计数器 当X=0时,是减法计数器

三、中规模集成计数器

同步集成计数器TTL74161(16进制)

Cr 0 LD 0 保持 计数 进位

__ __

异步清零 同步置位 LD C r 1, PT 0 LD C r P T 1 LD C r P T Q A QB QC QD 1

特点: 1.最低位来一个脉冲反转一次 (T’触发器) 2.其它位均在其所有的低位全为1时,来 一个时钟脉冲后反转。 (T触发器)

5.同步二进制减法计数器

Q0 Q1 Q2 1

J K Q F0 K J Q F1 K J Q F2

CP

特点: 1.最低位来一个脉冲反转一次 (T’触发器) 2.其它位均在其所有的低位全为0时,来 一个时钟脉冲后反转。 (T触发器)

__ __ __ __ __ __

P QA QB QC QD T Oc

CP Cr LD A B C D

例:利用反馈复(置)位法将74161构成十进 制计数器

1.复位法 “1” CP C

P QA QB QC QD T Oc

CP Cr LD A B C D 1

X X X X

异步清零

QD QC QB QA

(4)状态转换图:

Q2Q1Q0

000 001 010 011 111 110 101 100

(5)时序图:维阻式

CP Q0 Q1 Q2

二分频器 f/2 四分频器 f/4 八分频器 f/8

(5B)时序图:边沿式

CP Q0 Q1 Q2

二分频器 f/2 四分频器 f/4

八分频器 f/8

Q0n 1 Q

__ n 0 __ n 1 __ n 0

Q1n 1 Q0n Q Q Q1n

n 1 n Q2 Q0n Q1n Q Q Q Q2 __ n 2 _____ n n 0 1

Q0 1 时反转 Q0 Q1 1 时反转

(3)状态转换真值表:

CP Q2 0 1 2 3 4 5 6 7 8 0 0 0 1 1 1 1 0 Q1 0 0 1 1 0 0 1 1 0 Q0 0 1 0 1 0 1 0 1 0

1

P QA QB QC QD T Oc CP Cr LD A B C D 1

P QA QB QC QD T Oc CP Cr LD A B C D 1

CP

作业:

P316 17,19,

第四版:P246 8, 9, 10

P192 9(1),12,13