四位同步二进制计数器74LS161

74 161 计数器

54161/741614位二进制同步计数器(异步清除)简要说明:161为可预置的4位二进制同步计数器,共有54/74161和54/74LS161两种线路结构型式,其主要电特性的典型值如下:型号 F MAX P DCT54161/CT74161 32MHz 305mWCT54LS161/CT74LS161 32MHz 93mW161的清除端是异步的。

当清除端CLEAR为低电平时,不管时钟端CLOCK状态如何,即可完成清除功能。

161的预置是同步的。

当置入控制器LOAD为低电平时,在CLOCK上升沿作用下,输出端QA-QD与数据输入端A-D相一致。

对于54/74161,当CLOCK由低至高跳变或跳变前,如果计数控制端ENP、ENT为高电平,则LOAD应避免由低至高电平的跳变,而54/74LS161无此种限制。

161的计数是同步的,靠CLOCK同时加在四个触发器上而实现的。

当ENP、ENT均为高电平时,在CLOCK上升沿作用下QA-QD同时变化,从而消除了异步计数器中出现的计数尖峰。

对于54/74161,只有当CLOCk为高电平时,ENP、ENT才允许由高至低电平的跳变,而54/74LS161的ENP、ENT跳变与CLOCK无关。

161有超前进位功能。

当计数溢出时,进位输出端(RCO)输出一个高电平脉冲,其宽度为QA的高电平部分。

在不外加门电路的情况下,可级联成N位同步计数器。

对于54/74LS161,在CLOCk出现前,即使ENP、ENT、CLEAR发生变化,电路的功能也不受影响。

管脚图:引出端符号:PCO 进位输出端CLOCK 时钟输入端(上升沿有效)CLEAR 异步清除输入端(低电平有效)ENP 计数控制端ENT 计数控制端ABCD 并行数据输入端LOAD 同步并行置入控制端(低电平有效)QA-QD 输出端功能表:说明:H-高电平L-低电平X-任意↑-低到高电平跳变极限值电源电压------------------------------------------------7V输入电压54/74161-----------------------------------------5.5V54/74LS161---------------------------------------7VENP与ENT间电压54/74161-----------------------------------------5.5V 工作环境温度54×××------------------------------ -55~125℃74×××------------------------------------0~70℃ 贮存温度-------------------------------------- -65~150℃推荐工作条件:CT54161/CT74161 CT54LS161/CT74LS161单位最小额定最大最小额定最大54 4.5 5 5.5 5.5V 电源电压Vcc74 4.75 5 5.25 4.75 5 5.25输入高电平电压V IH 2 2 V54 0.80.7V 输入低电平电压V IL74 0.80.8输出高电平电流I OH-800-400 μA54 16 4mA 输出低电平电流I OL74 16 8时钟频率f CP0 25 0 25 MHzCLOCK 25 25ns 脉冲宽度tWCLEAR 20 20A-D、ENP 20 20ns 建立时间t setLOAD 25 20保持时间t H0 0 ns 时序图:逻辑图静态特性(T A 为工作环境温度范围)`161 `LS161参数测试条件【1】最小最大最小最大单位I IK =-12mA -1.5V IK 输入钳位电压 Vcc 最小I IK =-18mA-1.5 V54 2.4 2.5V OH 输出高电平电压Vcc=最小,V IH =2V ,V IL =最大, I OH =最大74 2.42.7V54 0.4 0.4V OL 输出低电平电压 V CC =最小,V IH =2V ,V IL =最大,I OL =最大740.40.5VA -D,ENP,CLEAR1 0.1I I 最大输入电压时输入电流 LOAD,CLOCk,ENT Vcc=最大 V I =5.5V (‘LS161为7V )1 0.2 mAA -D,ENP,CLEAR40 20LOAD 40 40 I IH 输入高电平电流 CLOCK,ENT Vcc=最大 V IH =2.4V (‘LS161为2.7V )80 40 μA A -D,ENP,CLEAR-1.6-0.4 LOAD -1.6 -0.8 V IL 输入低电平电流CLOCK,ENTVcc=最大 V IL =0.4V-3.2-0.8 mA 54-20-57-20 -100I OS 输出短路电流 Vcc=最大74-18-57-20 -100mA54 85 31IccH 输出高电平时电源电流Vcc=最大,LOAD 先接高电平,再接低电平,其余输入接高电平 74 94 31 mA54 91 32IccL 输出低电平时电源电流Vcc=最大,CLOCK 先接高电平,再接低电平,其余输入接低电平74101 32mA【1】:测试条件中的“最大”和“最小”用推荐工作条件中的相应值。

74LS161 实验讲解

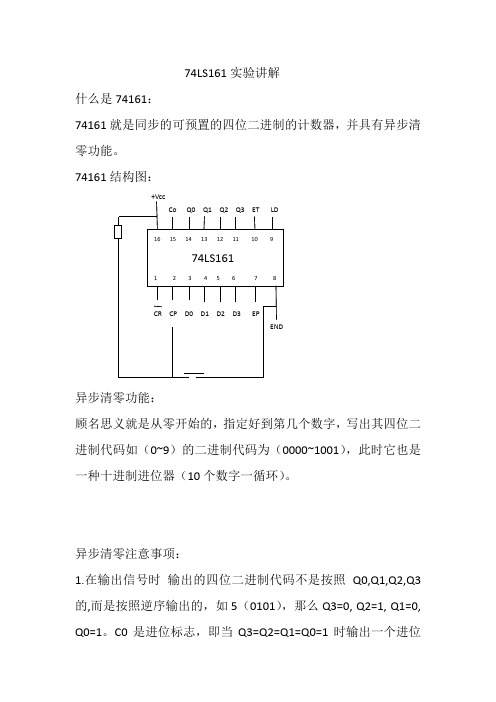

74LS161实验讲解什么是74161:74161就是同步的可预置的四位二进制的计数器,并具有异步清零功能。

74161结构图:异步清零功能:顾名思义就是从零开始的,指定好到第几个数字,写出其四位二进制代码如(0~9)的二进制代码为(0000~1001),此时它也是一种十进制进位器(10个数字一循环)。

异步清零注意事项:1.在输出信号时输出的四位二进制代码不是按照Q0,Q1,Q2,Q3的,而是按照逆序输出的,如5(0101),那么Q3=0, Q2=1, Q1=0, Q0=1。

C0是进位标志,即当Q3=Q2=Q1=Q0=1时输出一个进位信号1,否则输出0。

9(1010),Q3=1, Q2=0, Q1=0, Q0=1。

2.当循环到数字9时,由于Q3=1,Q0=1,那么瞬时就会把“0”信号传入CR,数字“9”会被瞬时清零,很难被看清(除非相应慢)。

想要克服这种情况,必须把9改成10(1010)。

这样才能看清9,然后再变成0。

异步清零(十进制(0~9))结构实验图:因为到数字10时(1010)Q3=1, Q2=0, Q1=1, Q0=0,发现只有当Q3=Q1=1时才开始循环,那么依照《电工与电子技术》第198页的表8-9。

只有让CR为”L”,即”0”才开始清零操作。

可以吧Q3和Q1与非的结果送入+Vcc C0Q0 Q1 Q2 Q3 ET LD同步并行:1.同异步清零相似,但是同步并行的功能比异步清零更完善,即可以恢复到初始状态。

2.与异步清零不同,因为异步清零只能从零开始,到某个位置回复到零在开始循环。

二同步并行并没有这种局限,它能从任意位置开始,然后到指定的位置,在恢复到一开始设置的位置循环。

注意事项:1.与异步清零相似的注意事项,在输入输出的,都是按照逆序输入输出的d3,d2,d1,d0. Q3,Q2,Q1,Q0.2.因为下图的LD没有带上非号,而课本第198表8-9上的LD上有非号,所以连接电路时还是注意一下。

74LS161和74LS290集成计数器功能说明

74LS161和74LS290集成计数器功能说明1、集成同步计数器同步计数器电路复杂,但计数速度快,多用在计算机电路中。

目前生产的同步计数器芯片分为二进制和十进制两种。

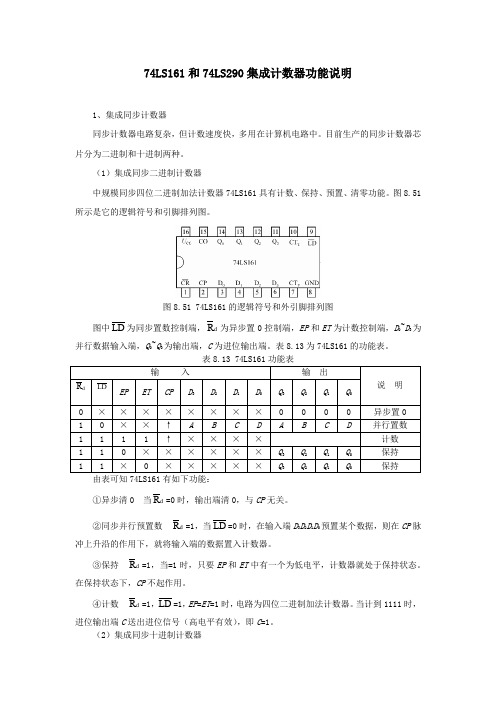

(1)集成同步二进制计数器中规模同步四位二进制加法计数器74LS161具有计数、保持、预置、清零功能。

图8.51所示是它的逻辑符号和引脚排列图。

图8.51 74LS161的逻辑符号和外引脚排列图图中LD为同步置数控制端,d R为异步置0控制端,EP和ET为计数控制端,D0~D3为并行数据输入端,Q0~Q3为输出端,C为进位输出端。

表8.13为74LS161的功能表。

R=0时,输出端清0,与CP无关。

①异步清0 当dR=1,当LD=0时,在输入端D3D2D1D0预置某个数据,则在CP脉②同步并行预置数d冲上升沿的作用下,就将输入端的数据置入计数器。

R=1,当=1时,只要EP和ET中有一个为低电平,计数器就处于保持状态。

③保持d在保持状态下,CP不起作用。

R=1,LD=1,EP=ET=1时,电路为四位二进制加法计数器。

当计到1111时,④计数d进位输出端C送出进位信号(高电平有效),即C=1。

(2)集成同步十进制计数器集成同步十进制加法计数器74LS160的管脚图和功能表与74LS161基本相同,唯一不同的是74LS160是十进制计数器,而74LS161是二进制计数器。

2、集成异步计数器异步计数电路简单,但计数速度慢,多用于仪器、仪表中。

(1)集成计数器74LS290图8.52是二-五-十进制集成计数器74LS290的逻辑结构图。

它兼有二进制、五进制和十进制三种计数功能。

当十进制计数时,又有8421BCD 和5421BCD 码选用功能,表8.14是它的功能表。

95481213131011CP 0CP 1Q 0Q 1Q 3Q 2R O(1)R O(2)S 9(1)S 9(2)图8.52 74LS290的逻辑结构图由表可知,74LS290具有如下功能:①异步置0 当R 0(1)=R 0(2)=1且S 9(1)或S 9(2)中任一端为0,则计数器清零,即Q D Q C Q B Q A =0000。

74ls161功能

74ls161功能

74LS161是一种四位二进制同步计数器,具有以下功能:

1. 递增计数:74LS161可以在时钟信号的驱动下完成二进制计数的递增。

当触发时钟信号时,计数器会将输出值加1,并将其显示在输出端口上。

2. 自动复位:计数器可以经过一定的计数周期后自动返回初始计数值。

通过连接复位信号到复位引脚,计数器可以在达到指定周期后自动复位到预定计数值,从而实现循环计数的功能。

3. 异步并行装载:计数器可以通过设置和存储加载值,以异步并行的方式将某个特定的初始值加载到计数器中。

这个初始值可以通过外部引脚或与其他逻辑电路相连的引脚传输,从而实现计数器的初始化。

4. 消隐功能:计数器内部具有输出控制门电路,可以根据特定的控制信号控制输出的使能情况。

当消隐使能信号有效时,计数器的输出将被禁用和消隐,从而可以达到隐藏输出的目的。

5. 异常检测:计数器内部具有检测器电路,可以检测并报告计数器的溢出和下溢情况。

当计数器的计数值超过最大值或低于最小值时,检测器将会触发异常信号,从而向其他逻辑电路报告异常情况。

总的来说,74LS161是一种功能强大的计数器,可以实现二进制数值的递增、循环计数、异步并行装载、消隐功能以及异常情况的检测和报告。

它在数字系统设计中起到重要的作用,广泛应用于计数、时序控制和状态机等领域。

74ls161引脚图与管脚功能表资料

74ls161引脚图与管脚功能表资料

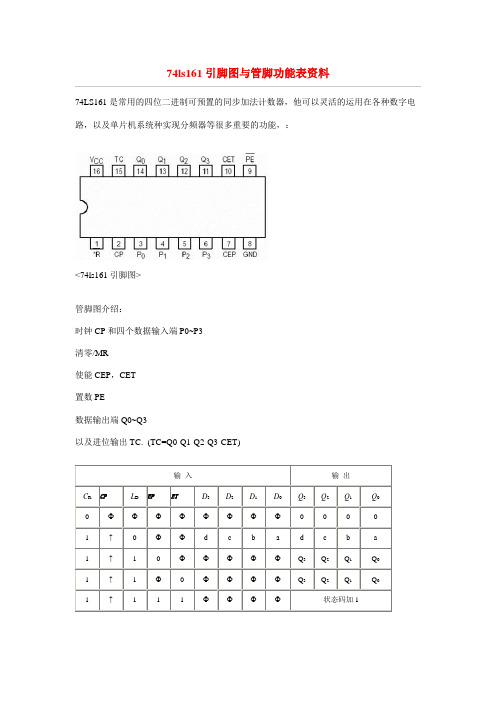

74LS161是常用的四位二进制可预置的同步加法计数器,他可以灵活的运用在各种数字电路,以及单片机系统种实现分频器等很多重要的功能,:

<74ls161引脚图〉

管脚图介绍:

时钟CP和四个数据输入端P0~P3

清零/MR

使能CEP,CET

置数PE

数据输出端Q0~Q3

以及进位输出TC。

(TC=Q0·Q1·Q2·Q3·CET)

输入输出

C R CP L

D EP ET D3D2D1D0Q3 Q2Q1Q0

0 Ф Ф Ф Ф Ф Ф Ф Ф 0 0 0 0

1 ↑ 0 Ф Ф d c b a d c b a

1 ↑ 1 0 Ф Ф Ф Ф Ф Q3 Q2Q1Q0

1 ↑ 1 Ф 0 Ф Ф Ф Ф Q3 Q2Q1Q0

1 ↑ 1 1 1 Ф Ф Ф Ф 状态码加1

<74LS161功能表〉

从74LS161功能表功能表中可以知道,当清零端CR=“0”,计数器输出Q3、Q2、Q1、Q0立即为全“0",这个时候为异步复位功能。

当CR=“1”且LD=“0”时,在CP信号上升沿作用后,74LS161输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3,D2,D1,D0的状态一样,为同步置数功能。

而只有当CR=LD=EP=ET=“1”、CP脉冲上升沿作用后,计数器加1。

7 4LS161还有一个进位输出端CO,其逻辑关系是CO= Q0·Q1·Q2·Q3·CET。

合理应用计数器的清零功能和置数功能,一片74LS161可以组成16进制以下的任意进制分频器.。

计数器74LS161功能及其应用17页

5

2.应用举例 (1)同步二进制加法计数

实现四位二进制加法计数

08.01.2020

6

(2)构成16以内的任意进制加法计数器: ① 设计思想:利用脉冲反馈法 用 S0 , S1 , S2… , SM…SN 表 示 输 入 0 , 1 ,

2,…,N个计数脉冲CP时计数器的状态。 SM可以为S0,但需小于SN。

十进制数50对应的二进制数为0011 0010

实现从0000 0000到0011 0001的50进制计数器

08.01.2020

15

作业题

5-8 5-9 5-10

08.01.2020

16

谢谢!

xiexie!

对于异步置数:在输入第N个计数脉冲CP后,通 过控制电路,利用状态SN产生一个有效置数信号,送 给异步置数端,使计数器立刻返回到初始的预置数状 态SM,即实现了SM~SN-1计数。

对于同步置数:在输入第N-1个计数脉冲CP时,

利用状态SN-1产生一个有效置数信号,送给同步置数控 制端,等到输入第N个计数脉冲CP时,计数器返回到

改08.0变1.202与0 非门的输入信号, 可以实现其它进制计数11。

用74LS161构成从0开始计数的十进制计数器

利用与非门拾取状态1010 实现十进制计数 (0000到1001) 改08.0变1.202与0 非门的输入信号 ,可以实现其它进制计数12。

(3)利用多片74LS161实现大容量计数 ① 先用级联法 计数器的级联是将多个集成计数器(如M1进制、

状态 输出

图3-35 74LS161的外引线图CP输入图3-36 74LS161的逻并辑符行号 输入

表5-14 74LS161的功能表

异步清0功 能最优先

计数器74LS161功能及其应用

状态 输出

图3-35 74LS161的外引线图 图3-36 74LS161的逻辑符号 CP输入 并行

输入

表5-14 74LS161的功能表

异步清0功 能最优先 同步并 行置数 CP上升 沿有效

2013-5-30

CO= Q3 Q2 Q1 Q0 CTT

4

2013-5-30

图5-22 74LS161的时序图

5

2.应用举例 (1)同步二进制加法计数

实现四位二进制加法计数

2013-5-30 6

(2)构成16以内的任意进制加法计数器: ① 设计思想:利用脉冲反馈法 用 S0 , S1 , S2… , SM…SN 表 示 输 入 0 , 1 , 2,…,N个计数脉冲CP时计数器的状态。 SM可以为S0,但需小于SN。

② 分析74LS161的置数功能:

③ 反馈信号的拾取 可利用与非门拾取状态SN或SN-1 可利用进位输出CO拾取状态1111

2013-5-30

8

④ 电路举例(以十进制计数器为例)

十进制计数器的计数状态顺序表

2013-5-30

9

图5-23 74LS161构成十进制计数器

利用进位输出CO取状态1111 令D3 D2 D1 D0=0110

5.4

中规模集成计数器及其应用

结束 放映

5.4.2 同步四位二进制计数器74LS161

1. 74LS161的逻辑功能

2. 应用举例

2013-5-30

1

复习

实现异步N进制计数器的级联法 ? 实现异步N进制计数器的脉冲反馈法?

2013-5-30

2

5.4.2 同步四位二进制计数器74LS161

1. 74LS161的逻辑功能

74ls161引脚图与管脚功能表资料

74ls161引脚图与管脚功能表资料74LS161是常用的四位二进制可预置的同步加法计数器,他可以灵活的运用在各种数字电路,以及单片机系统种实现分频器等很多重要的功能,:<74ls161引脚图>管脚图介绍:时钟CP和四个数据输入端P0~P3清零/MR使能CEP,CET置数PE数据输出端Q0~Q3以及进位输出TC. (TC=Q0·Q1·Q2·Q3·CET)<74LS161功能表>从74LS161功能表功能表中可以知道,当清零端CR=“0”,计数器输出Q3、Q2、Q1、Q0立即为全“0”,这个时候为异步复位功能。

当CR=“1”且LD=“0”时,在CP信号上升沿作用后,74LS161输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3,D2,D1,D0的状态一样,为同步置数功能。

而只有当CR=LD=EP=ET=“1”、CP脉冲上升沿作用后,计数器加1。

74LS161还有一个进位输出端CO,其逻辑关系是CO= Q0·Q1·Q2·Q3·CET。

合理应用计数器的清零功能和置数功能,一片74LS161可以组成16进制以下的任意进制分频器。

二进制计数器电路简单,运算也方便,但人们最习惯的是十进制,所以在应用中常使用十进制计数器。

使用较多的十进制计数器是按照8421BCD码进行计数的电路,计数器由“0000”状态开始计数,每10个脉冲一个循环,也就是第10个脉冲到来时,由“1001”变为“0000”,就实现了“逢十进一” ,同时产生一个进位信号。

74LS160是集成同步十进制计数器,它是按8421BCD码进行加法计数的,74LS160的引脚图、逻辑功能与74LS161相同,只是计数状态是按照十进制加法规律来计数的,因此不再重述。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

四位同步二进制计数器74LS161

————————————————————————————————作者:————————————————————————————————日期:

四位同步二进制计数器74LS161

逻辑符号如图所示:

逻辑功能如下表所示:74LS161功能表

P

T

CP 功能

1 × 0 ×

×

1 × 1 0 ×

1 0 1 1 ×

1 1 1 1 0

↑

↑

×

×

×

计数

并行输入

保持

保持(CO=0)

清零

CP是时钟脉冲信号端,是异步清零端,是同步置数控制端,P和T为计数允许控制端,D0~D3为并行数据输入端,Q0~Q3为数据输出端,CO为进位输出端。

由功能表可以看出该芯片具有以下功能:

(1)清零功能。

当时,计数器异步清零。

即只要,计数器输出状态立刻变为“0000”。

(2)同步并行置数功能。

当、时,在CP上升沿作

用下,并行输入数据D0~D3进入计数器,使计数器的输出端状态为Q3 Q2Q1 Q0=D3D2 D1D0。

(3)保持功能。

当、时,若P·T=0,则计数器保持原来状态不变。

对于进位输出信号有两种情况:如果T=0,则CO=0;如果T=1,则CO= Q3 ·Q2·Q1 ·Q0

(4)计数功能。

当、时,若P=T=1,则在时钟脉冲CP上升沿的连续作用下,计数器输出(Q3Q2Q1Q0)的状态按0000→0001→0010→0011→0100→0101→0110→0111→1000→1001

→1010→1011→1100→1101→1110→1111→0000的次序循环变化,完成十六进制(或称四位二进制)加法计数。

并且当计数器计到1111时,进位输出端CO输出为1,其他状态时CO输出为0。