计算机组成原理 实验(一)

计算机组成原理实验(接线、实验步骤)

计算机组成原理实验(接线、实验步骤)实验⼀运算器[实验⽬的]1.掌握算术逻辑运算加、减、乘、与的⼯作原理;2.熟悉简单运算器的数据传送通路;3.验证实验台运算器的8位加、减、与、直通功能;4.验证实验台4位乘4位功能。

[接线]功能开关:DB=0 DZ=0 DP=1 IR/DBUS=DBUS接线:LRW:GND(接地)IAR-BUS# 、M1、M2、RS-BUS#:接+5V控制开关:K0:SW-BUS# K1:ALU-BUSK2:S0 K3:S1 K4:S2K5:LDDR1 K6:LDDR2[实验步骤]⼀、(81)H与(82)H运算1.K0=0:SW开关与数据总线接通K1=0:ALU输出与数据总线断开2.开电源,按CLR#复位3.置数(81)H:在SW7—SW0输⼊10000001→LDDR2=1,LDDR1=0→按QD:数据送DR2置数(82)H:在SW7—SW0输⼊10000010→LDDR2=0,LDDR1=1→按QD:数据送DR1 4.K0=1:SW开关与数据总线断开K1=1:ALU输出与数据总线接通5. S2S1S0=010:运算器做加法(观察结果在显⽰灯的显⽰与进位结果C的显⽰)6.改变S2S1S0的值,对同⼀组数做不同的运算,观察显⽰灯的结果。

⼆、乘法、减法、直通等运算1.K0K1=002.按CLR#复位3.分别给DR1和DR2置数4.K0K1=115. S2S1S0取不同的值,执⾏不同的运算[思考]M1、M2控制信号的作⽤是什么?运算器运算类型选择表选择操作S2 S1 S00 0 0 A&B0 0 1 A&A(直通)0 1 0 A+B0 1 1 A-B1 0 0 A(低位)ΧB(低位)完成以下表格ALU-BUS SW-BUS# 存储器内容S2S1S0 DBUS C输⼊时:计算时:DR1:01100011DR2:10110100(与)DR1:10110100DR2:01100011(直通)DR1:01100011DR2:01100011(加)DR1:01001100DR2:10110011(减)DR1:11111111DR2:11111111(乘)实验⼆双端⼝存储器[实验⽬的]1.了解双端⼝存储器的读写;2.了解双端⼝存储器的读写并⾏读写及产⽣冲突的情况。

计算机组成原理实验报告

实验一:数字逻辑——交通灯系统设计子实验1:7 段数码管驱动电路设计(1)理解利用真值表的方式设计电路的原理;(2)利用Logisim 真值表自动生成电路的功能,设计一个 7 段数码管显示驱动。

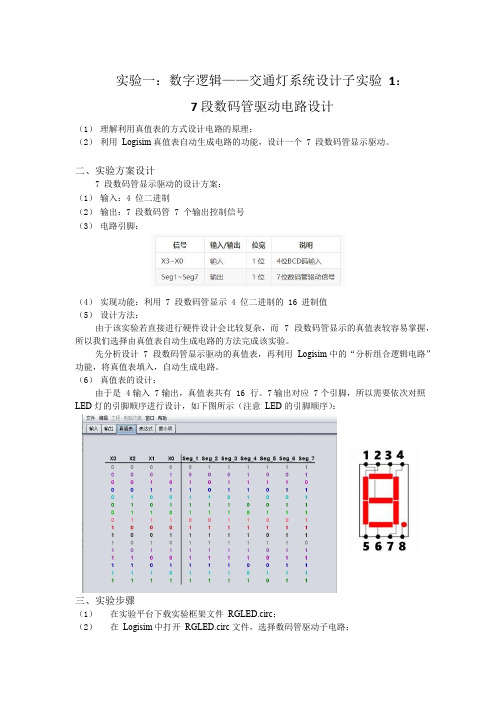

二、实验方案设计7 段数码管显示驱动的设计方案:(1)输入:4 位二进制(2)输出:7 段数码管 7 个输出控制信号(3)电路引脚:(4)实现功能:利用 7 段数码管显示 4 位二进制的 16 进制值(5)设计方法:由于该实验若直接进行硬件设计会比较复杂,而7 段数码管显示的真值表较容易掌握,所以我们选择由真值表自动生成电路的方法完成该实验。

先分析设计 7 段数码管显示驱动的真值表,再利用Logisim 中的“分析组合逻辑电路”功能,将真值表填入,自动生成电路。

(6)真值表的设计:由于是 4输入 7输出,真值表共有 16 行。

7输出对应 7个引脚,所以需要依次对照LED 灯的引脚顺序进行设计,如下图所示(注意LED 的引脚顺序):三、实验步骤(1)在实验平台下载实验框架文件RGLED.circ;(2)在Logisim 中打开RGLED.circ 文件,选择数码管驱动子电路;(3)点击“工程”中的“分析组合逻辑电路”功能,先构建4输入和7输出,再在“真值表”中,将已设计好的真值表的所有数值仔细对照着填入表格中,确认无误后点击“生成电路”,自动生成的电路如下图所示:(4)将子电路封装为如下形式:(5)进行电路测试:·自动测试在数码管驱动测试子电路中进行测试;·平台评测自动测试结果满足实验要求后,再利用记事本打开RGLED.circ 文件,将所有文字信息复制粘贴到Educoder 平台代码区域,点击评测按钮进行测试。

四、实验结果测试与分析(1)自动测试的部分结果如下:(2)平台测试结果如下:综上,本实验测试结果为通过,无故障显示。

本实验的关键点在于:在设计时需要格外注重LED 灯的引脚顺序,保证0-9 数字显示的正确性,设计出正确的真值表。

《计算机组成原理》实验报告一

《计算机组成原理》实验报告一一、实验目的:编写程序、上机调试、运行程序是进一步学习和掌握汇编语言程序设计的必要手段。

通过本次实验, 学习、掌握运行汇编程序的相关知识。

1、二、实验内容:2、熟悉实验用微机的软、硬件配置(1)硬件: Intel Celeron 500GHz CPU、128M内存(8M作共享显存)、intel810芯片主板、集成i752显卡、maxtro20G硬盘、ps/2接口鼠标、PS/2接口键盘。

(2)软件:DOS 操作系统Windows98 seMASM汇编语言程序3、熟悉运行汇编语言所需的应用程序汇编程序使MASM连接程序使用LINK程序调试程序使用DEBUG程序4、熟悉汇编语言源程序上机操作过程(1)编辑源文件(选择可使用的文本编辑器)(2)汇编源程序文件(3)连接目标文件(4)运行可执行文件5、汇编操作举例用edit编辑myprog.asm文件;(见下图)用MASM.exe编译myprog.asm生成myprog.obj文件;C:\masm\bin> masm.exe由图中可以看出:0 个警告错误0个严格错误汇编通过, 生成mygrog.obj目标文件(如果有严格错误, 汇编不能通过, 必须返回编辑状态更改程序。

)用link.exe命令链接myhprog.obj生成myprog.exe文件!C:\masm\bin> link.exeC:\masm\bin> myprog.exe运行程序结果为:屏幕显示“Hi! This is a dollar sign terminated string.”三、实验总结:1.可以在DOS或Windows状态编辑汇编源程序2.可以使用EDIT 或记事本编辑汇编源程序, 源程序必须以.asm为扩展名。

在记事本中保存文件时, 可以加双引号“myprog.asm”,文件名就不会出现myprog.asm.txt的错误3.熟悉相关的DOS 命令cd 进入子目录mkdir 建立子目录xcopy *.* /s 拷贝当前目录下所有文件及子目录format a: 格式化A盘4.在Windows 系统下运行汇编程序, 有时会有问题, 建议大家熟悉DOS命令,DOS编辑工具, 在DOS状态下运行汇编程序。

计算机组成原理实验一

实验一算术逻辑运算实验1.实验目的和要求1、掌握简单运算器的组成以及数据传送通路。

2、验证运算功能发生器(74LS181)的组合功能。

2.实验原理实验中所用的运算器数据通路如图1-1所示。

其中运算器由两片74LS181以并/串形式构成8位字长的ALU。

运算器的两个数据输入端分别由两个锁存器(74LS273)锁存,锁存器的输入连至数据总线,数据输入开关用来给出参与运算的数据,并经过一三态门(74LS245)和数据总线相连。

运算器的输出经过一个三态门(74LS245)和数据总线相连。

数据显示灯已和数据总线相连,用来显示数据总线内容。

图1-l 运算器数据通路图图1-2中已将实验需要连接的控制信号用箭头标明(其他实验相同,不再说明)。

其中除T4为脉冲信号,其它均为电平控制信号。

实验电路中的控制时序信号均已内部连至相应时序信号引出端,进行实验时,还需将S3、S2、S1、S0、Cn、M、LDDR1、LDDR2、ALU_G、SW_G各电平控制信号与开关单元中的二进制数据开关进行跳线连接,其中ALU_G、SW_G为低电平有效,LDDR1、LDDR2为高电平有效。

按动微动开关START,即可获得实验所需的单脉冲。

3.主要仪器设备(实验用的软硬件环境)1、ZY15CompSys12BB 计算机组成原理及系统结构教学实验箱一台2、排线若干4.操作方法与实验步骤l、按图1-2连接实验线路,仔细检查无误后,接通电源。

(图中箭头表示需要接线的地方,接总线和控制信号时要注意高低位一一对应,可用彩排线的颜色来进行区分)图1-2算术逻辑运算实验接线图2、用输入单元的二进制数据开关向寄存器DR1和DR2置数,数据开关的内容可以用与开关对应的指示灯来观察,灯亮表示开关量为“1”,灯灭表示开关量为“0”。

以向DR1中置入11000001(C1H)和向DR2中置入01000011(43H)为例,具体操作步骤如下:首先使各个控制电平的初始状态为:CLR=1,LDDR1=0,LDDR2=0,ALU_G=1,SW_G=1,S3 S2 S1 S0 M CN=111111,并将控制台单元的开关SP05打在“NORM”状态,然后按下图所示步骤进行。

计算机组成原理实验1-汇编语言实验

微处理器与接口技术实验指导实验一监控程序与汇编语言程序设计实验一、实验要求1、实验之前认真预习,明确实验的目的和具体实验内容,设计好主要的待实验的程序,做好实验之前的必要准备。

2、想好实验的操作步骤,明确通过实验到底可以学习哪些知识,想一想怎么样有意识地提高教学实验的真正效果。

3、在教学实验过程中,要爱护教学实验设备,认真记录和仔细分析遇到的现象与问题,找出解决问题的办法,有意识地提高自己创新思维能力。

4、实验之后认真写出实验报告,重点在于预习时准备的内容,实验数据,实验过程、遇到的现象和解决问题的办法,自己的收获体会,对改进教学实验安排的建议等。

善于总结和发现问题,写好实验报告是培养实际工作能力非常重要的一个环节,应给以足够的重视。

二、实验目的【1】学习和了解TEC-XP16教学实验系统监控命令的用法;【2】学习和了解TEC-XP16教学实验系统的指令系统;【3】学习简单的TEC-XP16教学实验系统汇编程序设计。

三、实验注意事项(一)实验箱检查【1】连接电源线和通讯线前TEC-XP16实验系统的电源开关一定要处于断开状态,否则可能会对TEC-XP16实验系统上的芯片和PC机的串口造成损害。

【2】五位控制开关的功能示意图如下:【3】几种常用的工作方式【开关拨到上方表示为1,拨到下方为0】(二)软件操作注意事项【1】用户在选择串口时,选定的是PC机的串口1或串口2,而不是TEC-XP16实验系统上的串口。

即选定的是用户实验时通讯线接的PC机的端口;【2】如果在运行到第五步时没有出现应该出现的界面,用户需要检查是不是打开了两个软件界面,若是,关掉其中一个再试;【3】有时若TEC-XP16实验系统不通讯,也可以重新启动软件或是重新启动PC再试;【4】在打开该应用软件时,其它的同样会用到该串口的应用软件要先关掉。

(三)联机通讯失败自检如果上述的硬件和软件的操作都正确,联机却依旧失败,可以进行如下测试:【1】测试PC机的串口是否能正常工作,或是换一台PC或换同一台PC的另一个串口再试,在换串口时要将TEC-XP16实验系统断电,换完后重新启动实验系统和软件;【2】检查机器上的元器件插接是否正确(建议用户对照能够正常通讯的实验系统进行详细检查),有没有被学生动过,尤其是扩展内存和扩展I/O接口时,芯片方向是否插对,片选信号有没有连接;【3】检查相应的短路子是否连接正确;【4】建议教师预留一台运行正常的TEC-XP16实验系统备用,机器出问题后可以对照检查。

计算机组成原理第一次实验报告

K20

K19

K18

K17

K16

0

1

0

1

0

1

0

1

置控制信号:

K11(RRD)

K10(RWR)

K1(SB)

K0(SA)

1

0

1

1

给出CLOCK脉冲上升沿。

(2) R?的读出

自己设置RRD、RWR、SB及SA信号,观察R?的红色指示灯及液晶显示内容。

读R0:

置控制信号:

K11(RRD)

K10(RWR)

数据输出选择器原理图

X2 X1 X0

输出寄存器

0 0 0

IN-OE外部中断

0 0 1

IA-OE中断向量

0 1 0

ST-OE堆栈寄存器

0 1 1

PC-OE PC寄存器

1 0 0

D-OE直通门

1 0 1

R-OE右移门

1 1 0

L-OE左移门

1 1 1

没有输出

三、实验内容

1、A、W的写入

按下表连线

连接

信号孔

µPC原理图

当RES=0时,µPC被清0;

当IREN=0时,在CK的上升沿,预置数据被打入µPC。指令总线(IBUS)上的数据可来自一片74HC245。

当IREN=1时,在CK的上升沿,µPC加1。

(二)程序计数器PC

程序计数器PC由2片74HC161组成,能完成加1和预置数功能。程序计数器的输出由74HC245保存,74HC245与74HC161的输出相连,74HC245(2)的输出连接地址总线,74HC245(1)的输出接到数据总线(当LDPC=0时)。

二、实验原理

(一)寄存器

计算机组成原理实验一运算器组成实验

实验一 运算器组成实验一、实验目的1.熟悉双端口通用寄存器堆的读写操作。

2.熟悉简单运算器的数据传送通路。

3.验证运算器74LS181的算术逻辑功能。

4.按给定数据,完成指定的算术、逻辑运算。

二、实验电路ALU-BUS#DBUS7DBUS0Cn#C三态门(244)三态门(244)ALU(181)ALU(181)S3S2S1S0MA7A6A5A4F7F6F5F4F3F2F1F0B3B2B1B0Cn+4CnCnCn+4LDDR2T2T2LDDR1LDRi T3SW-BUS#DR1(273)DR2(273)双端口通用寄存器堆RF(ispLSI1016)RD1RD0RS1RS0WR1WR0数据开关(SW7-SW0)数据显示灯A3A2A1A0B7B6B5B4图3.1 运算器实验电路LDRi T3AB三态门R S -B U S #图3.1示出了本实验所用的运算器数据通路图。

参与运算的数据首先通过实验台操作板上的八个二进制数据开关SW7-SW0来设置,然后输入到双端口通用寄存器堆RF 中。

RF(U54)由一个ispLSI1016实现,功能上相当于四个8位通用寄存器,用于保存参与运算的数据,运算后的结果也要送到RF 中保存。

双端口寄存器堆模块的控制信号中,RS1、RS0用于选择从B 端口(右端口)读出的通用寄存器,RD1、RD0用于选择从A 端口(左端口)读出的通用寄存器。

而WR1、WR0用于选择写入的通用寄存器。

LDRi 是写入控制信号,当LDRi=1时,数据总线DBUS上的数据在T3写入由WR1、WR0指定的通用寄存器。

RF的A、B端口分别与操作数暂存器DR1、DR2相连;另外,RF的B端口通过一个三态门连接到数据总线DBUS上,因而RF中的数据可以直接通过B端口送到DBUS上。

DR1(U47)和DR2(U48)各由1片74LS273构成,用于暂存参与运算的数据。

DR1接ALU 的A输入端口,DR2接ALU的B输入端口。

计组实验报告(共10篇)

计组实验报告(共10篇)计组实验报告计算机组成原理实验报告一一、算术逻辑运算器1. 实验目的与要求:目的:①掌握算术逻辑运算器单元ALU(74LS181)的工作原理。

②掌握简单运算器的数据传输通道。

③验算由74LS181等组合逻辑电路组成的运输功能发生器运输功能。

④能够按给定数据,完成实验指定的算术/逻辑运算。

要求:完成实验接线和所有练习题操作。

实验前,要求做好实验预习,掌握运算器的数据传送通道和ALU 的特性,并熟悉本实验中所用的模拟开关的作用和使用方法。

实验过程中,要认真进行实验操作,仔细思考实验有关的内容,把自己想得不太明白的问题通过实验去理解清楚,争取得到最好的实验结果,达到预期的实验教学目的。

实验完成后,要求每个学生写出实验报告。

2. 实验方案:1.两片74LS181(每片4位)以并/串联形式构成字长为8为的运算器。

2.8为运算器的输出经过一个输入双向三态门(74LS245)与数据总线相连,运算器的两个数据输入端分别与两个8位寄存器(74LS273)DR1和DR2的输出端相连,DR1和DR2寄存器是用于保存参加运算的数据和运算的结果。

寄存器的输入端于数据总线相连。

3.8位数据D7~D0(在“INPUT DEVICE”中)用来产生参与运算的数据,并经过一个输出三态门(74LS245)与数据总线相连。

数据显示灯(BUS UNIT)已与数据总线相连,用来显示数据总线上所内容。

4.S3、S2、S1、S0是运算选择控制端,由它们决定运算器执行哪一种运算(16种算术运算或16种逻辑运算)。

5.M是算术/逻辑运算选择,M=0时,执行算术运算,M=1时,执行逻辑运算。

6.Cn是算术运算的进位控制端,Cn=0(低电平),表示有进位,运算时相当于在最低位上加进位1,Cn=1(高电平),表示无进位。

逻辑运算与进位无关。

7.ALU-B是输出三态门的控制端,控制运算器的运算结果是否送到数据总线BUS上。

低电平有效。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

计算机组成原理实验(一)

实验项目名: 实验台基本模块认识实验

实验要求:

学习使用计算机组成原理教学实验系统的,认识组成原理实验台上的各个组成部件模块,熟悉各模块的功能、数据通路和使用方法,为后续实验做准备。

实验内容:

(1)了解计算机组成原理硬件实验台各模块的组成和功能

✶运算器单元- 74LS181(4位并行运算器),输入端74LS373(锁存器),

输出端74LS245(三态缓冲器),74LS74(双D触发器)。

✶寄存器组单元– 3片74LS374 作为三个通用寄存器使用,R0、R1、R2 与总线相连。

✶地址寄存器单元– 2片地址锁存器74LS273锁存地址,通过总线将地址送入到该地址寄存器单元,而该地址寄存器与存储器接口相连,用于访问存储器。

✶数据总线单元–显示当前数据总线输出的内容。

✶主存储器单元–由6116 SRAM(4片)存储器作为主存储器,存储实验用机器指令,连接到数据和地址总线上。

✶程序计数器PC– 8位指令地址,使用2片74LS163构成,通过控制信号,可实现PC内容与总线间的交换。

✶指令寄存器单元—使用1片74LS273锁存器锁存当前执行的指令,IR寄存器的一端连接到数据总线上,另一端则连接到微地址单元的地址输入接口,用于寻址控存。

✶时序启停单元—通过输入系统脉冲源,可产生T1~T4四个标准的周期性信号,并且通过按键控制,可产生单次脉冲。

✶微程序电路单元—模拟微程序结构的CU,根据指令的操作码译码后得到的微程序地址,访问系统中的控存6116,取出微指令后,发出相应的微操作控制信号,控制系统中数据的流动及功能器件的动作。

该实验台各模块共有26个微控制信号,其中有7个(BUS-111,BUS-110,Rd-BUS,Rs-BUS,299-BUS,ALU-BUS,PC-BUS)采用译码输出的方式,而剩余的采用直接

控制方式输出。

下一条微指令的地址由微指令的低地址(每条微指令长度为32位,其中(26-7)+3(译码)为微操作控制位,其余的为下地址)部分决定。

✶逻辑译码单元—其实可以算作微程序单元的一部分,两块逻辑,分别是下地址部分需要译码条件位,从而进行分支,以及7个微控制信号需要译码产生。

✶输入设备单元– 8个拨动开关,向总线输入数据。

✶输出设备单元–输出数据进入锁存器后由8位发光二极管显示。

(2)了解计算机组成原理实验环境软/硬件的使用方法

✶实验台键盘和数码管显示的使用

dY –N P. –正常开机/复位状态;

①按[增址]键,工作方式切换,手动方式–L,自动方式–H,动态跟踪操作–n

②按任意数字键,进入待命状态0,此时按下的数字可作为存储器地址,寄存器号,微程序地址等,根据后续按键[存储]、[寄存]、[读],决定操作对象不同,此后可使用[增址]、[减址]键操作相连单元。

✶实验环境的使用

①连接检测功能:PC与实验台是否连接上的检测,看工具栏,有一个

“连接”图标,灰色说明已连上。

②实验指导:

图2 集成环境提供的实验指导功能下拉菜单

集成实验环境,菜单栏中有“实验指导”一项,通过下拉,能够看到提供的主要指导功能,包括每个实验的实验目的、实验内容、实验电路和实验连线等等。

使用时,首先根据实验单元,分别选中“单元手动实验”中的某一项实验,或者“模型机实验”中的某一项,然后再重新打开下拉菜单,点击实验指导内容中想要查看的地方,就可以了。

③实验系统连线诊断程序:

图3 “诊断测试”菜单图4 “诊断测试”窗口集成实验环境提供实验连线的诊断测试功能,在完成实验连线之后,可以通过点击菜单中的“调试”-〉“诊断测试”,打开“诊断测试”窗口,进行实验台实验连线的诊断测试。

④虚拟示波器

图5 “逻辑示波器”菜单图6 “逻辑示波器”窗口

实验台有两个示波器的表笔插孔,集成实验环境支持“虚拟示波器”功能,通过“视图”-〉“逻辑示波器”,打开“逻辑示波器”窗口,点击“开始”后,可以看到表笔接触位置的信号波形情况。

(3)通用寄存器模块实验

硬件结构:参考(1)中描述。

使用模块:①通用寄存器组

②输入设备单元

③输出设备单元

④数据总线单元

⑤时序启停单元

控制信号:

通用寄存器– R0-B、R1-B、R2-B 寄存器送总线;

LDR0、LDR1、LDR2 总线送寄存器;

输入设备单元– SW-B 开关输入送总线

输出设备单元– LDED 总线数据送LED显示

数据总线单元–无控制信号

硬件连线:

实验涉及模块的总线接口连线,8芯扁缆;

实验涉及模块所有的控制信号;

实验台的时钟信号输入;

操作过程:

二进制开关–控制相应的控制信号有效,按下单步键运行。