(完整word版)24小时数字钟VHDL语言

VHDL 语言设计数字时钟

数字时钟DIGITAL CLOCK电子信息科学与技术专业关键词:VHDL,设计,数字钟,应用电路英文关键词:VHDL; design; digital clock; application electro circuits摘要:以一款数字钟设计为例,较详细的介绍了如何用VHDL语言设计数字电路,并给出了部分程序、仿真波形图,并在MAX+plusII中进行编译、仿真、下载。

由此说明利用VHDL开发数字电路的优点。

英文摘要:By showing some program codes and emulational wave charts,the paper introduces the way to designdigital electro circuits with VHDL in details andgives us an example of designing a digital clock.Andit compiles,emulates and downloads them inMAX+plusII,which elucidates the advantages ofdeveloping digital electro circuits with VHDL引言20世纪末,数字电子技术得到了飞速发展,有力地推动和促进了社会生产力的发展和社会信息化的提高,数字电子技术的应用已经渗透到人类生活的各个方面。

从计算机到手机,从数字电话到数字电视,从家用电器到军用设备,从工业自动化到航天技术,都尽可能采用了数字电子技术。

现代电子设计技术的核心是EDA技术。

EDA(电子设计自动化)技术就是以计算机为工具,在EDA软件平台上,对硬件语言HDL为系统逻辑描述手段完成的设计文件,自动的完成逻辑编译、逻辑化简、逻辑综合及优化、逻辑仿真,直至对特定目标芯片的适配编译、逻辑映射和编程下载等工作(文本选用的开发工具为Altera公司的MAX+PLUSII)。

VHDL数字钟

课程设计报告设计题目:用VHDL语言实现数字钟的设计班级:学号:姓名:指导老师:设计时间:摘要本设计是基于VHDL语言的数字钟,硬件平台是Xilinx的Virtex2系列FPGA 开发板。

该数字钟具备预置年月日时分秒的功能,通过按键还可以改变数字钟显示的内容和进入不同的设置状态,并通过加减按键调整系统时间。

在整个VHDl数字电路系统中,采用层次化设计方法,自顶向下进行设计。

设计中根据系统的功能要求合理划分出层次,进行分级设计和仿真验证,将较为复杂的数字系统逻辑简化为基本的模型从而降低实现的难度。

工程中底层实体实现了年月日、时分秒的双向计数器功能,另外还单独设计了系统的时钟模块,用来生成周期为125Hz的按键扫描时钟和周期为1Hz单位脉冲时钟。

为了消除按键的抖动,为此设计了按键消抖模块,采用了状态机来对按键进行消抖。

为了实现根据年份和月份对当前月的天数的判断逻辑,采用了函数对该逻辑进行分析,给出正确的判断结果。

为了提高利用率,在工程中建立了一个包集文件,对底层实体进行了统一封装,方便顶层的调用。

底层的所有实体系统的顶层主要完成了底层的元件例化,主控状态机对系统的状态转换进行控制,按键响应和时钟重新分配电路则完成了整个系统的控制逻辑。

关键词:层次化设计,元件例化,函数,状态机目录摘要 (2)一、课程设计目的 (4)二、课程设计内容及其要求 (4)三、VHDL程序设计 (5)1.设计方案论证 (5)2.设计思路与方法 (6)3.VHDL源代码及其仿真结果 (7)1、六进制可逆计数器 (7)2、十进制可逆计数器, (9)3、十二进制可逆计数器, (11)4、二十四进制可逆计数器 (13)5、天数计数器 (16)6、判断闰年和月份 (18)7、时钟分频模块 (22)8、按键消抖模块 (24)9、程序包 (27)10、顶层实体(主控状态机) (29)四、编程下载 (38)五、课程设计总结 (38)六、参考文献 (38)一、课程设计目的诞生于1983年的VHDL语言,在1987年被美国国防部和IEEE指定为标准硬件描述语言。

VHDL编程--数字钟

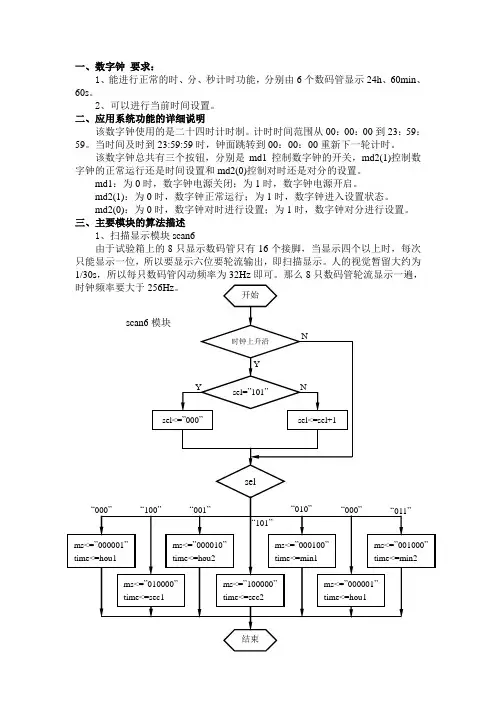

一、数字钟要求:1、能进行正常的时、分、秒计时功能,分别由6个数码管显示24h、60min、60s。

2、可以进行当前时间设置。

二、应用系统功能的详细说明该数字钟使用的是二十四时计时制。

计时时间范围从00:00:00到23:59:59。

当时间及时到23:59:59时,钟面跳转到00:00:00重新下一轮计时。

该数字钟总共有三个按钮,分别是md1控制数字钟的开关,md2(1)控制数字钟的正常运行还是时间设置和md2(0)控制对时还是对分的设置。

md1:为0时,数字钟电源关闭;为1时,数字钟电源开启。

md2(1):为0时,数字钟正常运行;为1时,数字钟进入设置状态。

md2(0):为0时,数字钟对时进行设置;为1时,数字钟对分进行设置。

三、主要模块的算法描述1、扫描显示模块scan6由于试验箱上的8只显示数码管只有16个接脚,当显示四个以上时,每次只能显示一位,所以要显示六位要轮流输出,即扫描显示。

人的视觉暂留大约为1/30s,所以每只数码管闪动频率为32Hz即可。

那么8只数码管轮流显示一遍,2、计时模块hourten,huoroen,minten,minone,secten,secone计时模块共分为6个部分,分别是时、分、秒的十位和个位。

由每位之间的逻辑关系以及md1和md2来控制正常计数、进位和对小时分钟的设置。

3、译码模块dec7s把计时模块输出的时、分、秒各位的二进制数翻译成能在七段数码管上显示的七位二进制码,能够显示0~9各个数字。

四、程序的源代码清单library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity digital_clock isport(clk:in std_logic; --扫描频率,>=256Hz clk1:in std_logic; --计时频率,1Hzmd1:in std_logic; --开关,0时有效md2:in std_logic_vector(1 downto 0); --时间设置dout:out std_logic_vector(6 downto 0); --译码显示ms:out std_logic_vector(5 downto 0)); --扫描控制end digital_clock;architecture one of digital_clock issignal sel:std_logic_vector(2 downto 0);signal hou1,hou2,min1,min2,sec1,sec2:std_logic_vector(3 downto 0);signal time:std_logic_vector(3 downto 0);begin---------------------------------------------scan6scan6:process(clk1,hou1,hou2,min1,min2,sec1,sec2)beginif clk1'event and clk1='1' thenif sel="101" thensel<="000";elsesel<=sel+1;end if;end if;case sel iswhen "000"=>ms<="000001";time<=hou1;when "001"=>ms<="000010";time<=hou2;when "010"=>ms<="000100";time<=min1;when "011"=>ms<="001000";time<=min2;when "100"=>ms<="010000";time<=sec1;when "101"=>ms<="100000";time<=sec2;when others=>ms<="100000";time1=sec2;end case;end process scan6;---------------------------------------------hourtenhourten:process(clk,hou2,min1,min2,sec1,sec2,md1,md2)beginif clk'event and clk='1' thenif (hou1&hou2&min1&min2&sec1&sec2="001000110101100101011001") then hou1<="0000"; --当23:59:59时,时十位归0elsif (hou1&hou2="00100011"and md1&md2="001") thenhou1<="0000"; --当设置小时,时位是23时,时十位归0elsif ((hou2&min1&min2&sec1&sec2="10010101100101011001")or(hou2="1001"and md1&md2="001")) thenhou1<=hou1+1; --当正常计时,时间是x9:59:59时,或设置小时,end if; --时位是x9时,时十位加1end if;end process hourten;---------------------------------------------houronehourone:process(clk,min1,min2,sec1,sec2,md1,md2,hou1)beginif clk'event and clk='1' thenif (hou1&hou2&min1&min2&sec1&sec2="001000110101100101011001") then hou2<="0000"; --当23:59:59时,时个位归0elsif (hou2&min1&min2&sec1&sec2="001000110101100101011001") thenhou2<="0000"; --当x9:59:59时,时个位归0elsif ((hou2="1001"or hou1&hou2="00100011")and(md1&md2="001")) thenhou2<="0000"; --当设置小时,时位是x9或23时,时个位归0 elsif (min1&min2&sec1&sec2="0101100101011001)or(md1&md2="001")then hou2<=hou2+1; --当正常计时,时间是xx:59:59时,或设置小时,时个位加1 end if;end if;end process hourone;---------------------------------------------mintenminten:process(clk,min2,sec1,sec2,md1,md2)beginif clk'event and clk='1' thenif (min1&min2&sec1&sec2="0101100101011001") thenmin1<="0000"; --当xx:59:59时,分十位归0elsif (min1&min2="01011001"and md1&md2="000")thenmin1<="0000"; --当设置分钟,分位是59时,分十位归0elsif (min2&sec1&sec2="100101011001")or --正常计时,时间是xx:x9:59时,或(min2="1001"and md1&md2="000") then --设置分钟,时间是x9,分十位加1min1<=min1+1;end if;end if;end process minten;---------------------------------------------minoneminone:process(clk,sec1,sec2,md1,md2)beginif clk'event and clk='1' thenif (min2&sec1&sec2="100101011001") thenmin2<="0000"; --当xx:x9:59时,分个位归0elsif (min2="1001"and md1&md2="000") thenmin2<="0000"; --当设置分钟,分位是x9时分个位归0elsif (sec1&sec2="01011001")or(md1&md2="000") thenmin2<=min2+1; --正常计时,时间是xx:xx:59时,或设置分钟,分个位加1 end if;end if;end process minone;---------------------------------------------sectensecten:process(clk)beginif clk'event and clk='1' thenif (sec1&sec2="01011001") then --当时间是xx:xx:59时,秒十位归0sec1<="0000";elsif sec2="1001"then --当秒位是x9时,秒十位加1sec1<=sec1+1;end if;end if;end process secten;--------------------------------------------seconesecone:process(clk)beginif clk'event and clk='1' thenif sec2="1001" then --当秒位是x9时,秒个位归0sec2<="0000";else sec2<=sec2+1; --否则加1end if;end if;end process secone;------------------------------------------dec7sdec7s:process(time)begincase time iswhen "0000"=>dout<="0111111";when "0001"=>dout<="0000110";when "0010"=>dout<="1011011";when "0011"=>dout<="1001111";when "0100"=>dout<="1100110";when "0101"=>dout<="1101101";when "0110"=>dout<="1111101";when "0111"=>dout<="0000111";when "1000"=>dout<="1111111";when "1001"=>dout<="1101111";when others=>dout<="0111111";end case;end process dec7s;end one;。

基于VHDL语言的数字钟设计

信息与通信工程学院数字电路与逻辑设计实验题目:基于VHDL语言的数字钟设计班级:姓名:学号:日期:指导教师:一.摘要数字钟是一个将“时”、“分”、“秒”显示于人的视觉器官的计时装置。

它的基本功能是计时,计时周期为24小时,显示满刻度23时59分59秒;或者计时周期为12小时并配有上下午指示,显示满刻度为11时59分59秒,通过六个七段数码管显示出来。

本实验主要在理论分析和具体的软硬件实现上,基于VHDL语言编写源代码,使用软件Quartus II 进行处理,再配合具体电路连接,实现一个多功能的数字钟。

关键词:数字钟;VHDL语言;七段数码管二.设计任务要求设计实现一个数字钟。

1.24小时制,显示刻度从0:0:0到23:59:59 。

2.12小时制,显示刻度从0:0:0到11:59:59 。

3.12/24小时制可切换,12小时制下上下午有不同显示(上午发光二极管不亮,下午发光二极管亮)。

4.可手动校对时间,能对时和分进行校正。

5.整点报时功能。

6.闹铃功能,可设置闹铃时间,当计时到预定时间时,蜂鸣器发出闹铃信号,闹铃时间为5秒,可提前终止闹铃。

7.可认为设置时间为倒计时模式8.可切到屏保模式,六个数码管显示为“supper”字样。

三.设计思路和总体设计框图1.设计思路程序设计主要分为四个模块,第一部分,做分频器,分出一秒的时钟用来计数,再分出一个中频时钟用来扫描显示数码管,我选择的频率是50kHZ;第二部分,做计数器,秒随时钟沿计数进1,分钟随着秒计数60次进一,而小时,由于有12/24小时制的切换,时的计数有两个信号来进行,一个信号hour1是分60进一在0到23循环计数,另一个信号hour2是分60进一在0到11循环计数;第三部分,做扫描显示六个七段数码管,通过选通信号6矢量cat来依次使六个数码管亮,数码管每两位对应相应的时分秒;第四部分,其他输入输出单元,比如数字钟的时间修正,闹铃等,这些都是基于前三个部分,做起来难度不大。

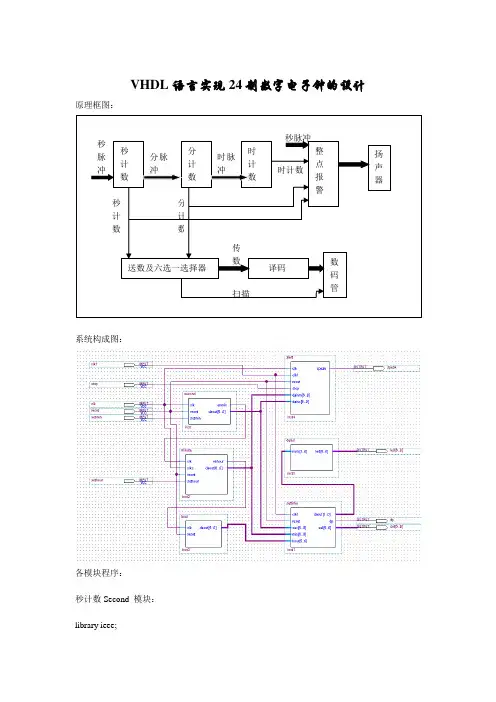

VHDL语言实现24制数字电子钟的设计程序

VHDL 语言实现24制数字电子钟的设计原理框图:系统构成图:各模块程序:秒计数Second 模块:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity second isport(clk: in std_logic;reset: in std_logic;setmin: in std_logic;enmin: out std_logic;daout: out integer range 0 to 59);end entity second;architecture art of second issignal count:integer range 0 to 59;signal enmin_1,enmin_2:std_logic;begindaout<=count;enmin_2<=(setmin and clk);enmin<=(enmin_1 or enmin_2);process(clk,reset,setmin)beginif(reset='0')thencount<=0;enmin_1<='0';elsif(clk'event and clk='1')thenif(count<59) thencount<=count+1; enmin_1<='0';elsecount<=0;enmin_1<='1';end if;end if;end process;end art;分计数minute模块:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity minute isport(clk: in std_logic;clks: in std_logic;reset: in std_logic;sethour:in std_logic;enhour: out std_logic;daout: out integer range 0 to 59);end entity minute;architecture art of minute issignal count:integer range 0 to 59;signal enhour_1,enhour_2:std_logic;begindaout<=count;enhour_2<=(sethour and clks);enhour<=(enhour_1 or enhour_2);process(clk,reset,sethour)beginif(reset='0')thencount<=0;enhour_1<='0';elsif(clk'event and clk='1')thenif(count<59) thencount<=count+1; enhour_1<='0';elsecount<=0;enhour_1<='1';end if;end if;end process;end art;时计数hour模块:LIBRARY IEEE;USE IEEE.std_logic_1164.all;USE IEEE.std_logic_unsigned.all;entity hour isport ( clk : in std_logic;reset: in std_logic;daout: out integer range 0 to 11);end entity hour;architecture zrt of hour issignal count:integer range 0 to 11;begindaout<=count;process(clk,reset)beginif(reset='0') thencount<=0;elsif (clk'event and clk='1') thenif(count<11) thencount<=count+1;elsecount<=0;end if;end if;end process;end zrt;时间调整及多路选择settime模块;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity settime isport(clk1: in std_logic;reset: in std_logic;sec,min:in integer range 0 to 59;hour: in integer range 0 to 11;daout: out integer range 0 to 9;dp: out std_logic;sel: out std_logic_vector(5 downto 0)); end settime;architecture art of settime issignal count:std_logic_vector(2 downto 0); beginprocess(clk1,reset)beginif(reset='0')thencount<="000";elsif(clk1'event and clk1='1')thenif(count>="101")thencount<="000";elsecount<=count+1;end if;end if;end process;process(clk1,reset)variable a ,b:integer range 0 to 9;beginif(reset='0')thendaout<=0;dp<='0';sel<="111111";elsif(clk1'event and clk1='1')thencase count iswhen"000"=>a:=sec rem 10;daout<=a;dp<='0';sel<="000001";when"001"=>b:=sec /10;daout<=b;dp<='0';sel<="000010";when"010"=>a:=min rem 10;daout<=a;dp<='1';sel<="000100";when"011"=>b:=min / 10;daout<=b;dp<='0';sel<="001000";when"100"=>a:=hour rem 10;daout<=a;dp<='1';sel<="010000";when"101"=>b:=hour / 10;daout<=b;dp<='0';sel<="100000";when others=>null;end case;end if;end process;end art;报时alert模块:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity alert isport ( clk,clk1,reset,stop:in std_logic;dainm:in integer range 0 to 59;dains:in integer range 0 to 59;speak:out std_logic);end alert;architecture art of alert issignal s_speak,enspeak:std_logic;beginspeak<=enspeak and s_speak;process(clk1,reset)beginif(reset='0')thens_speak<='0';elsif(clk1'event and clk1='1')thenif(dainm=0)thenif(dains>10)thens_speak<='0';elses_speak<=clk;end if;elses_speak<='0';end if;end if;end process;process(stop,reset,dains)beginif(reset='0' or dains>10)thenenspeak<='1';elsif(stop'event and stop='1')thenenspeak<='0';end if;end process;end art;译码deled模块:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity deled isport(num: in integer range 0 to 9;led: out std_logic_vector(6 downto 0)); end entity deled;architecture art of deled isbeginled<="1111110"when num=0 else"0110000"when num=1 else"1101101"when num=2 else"1111001"when num=3 else"0110011"when num=4 else"1011011"when num=5 else"1011111"when num=6 else"1110000"when num=7 else"1111111"when num=8 else"1111011"when num=9 else"0000000";end art;顶层文件clock:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity clock isport (clk1,stop,clk,reset,setmin,sethour:in std_logic;dp,speak:out std_logic;led:out std_logic_vector(6 downto 0);sel:out std_logic_vector(5 downto 0));end entity clock;architecture one of clock iscomponent second isport(clk: in std_logic;reset: in std_logic;setmin: in std_logic;enmin: out std_logic;daout: out integer range 0 to 59);end component second;component minute isport(clk: in std_logic;clks: in std_logic;reset: in std_logic;sethour:in std_logic;enhour: out std_logic;daout: out integer range 0 to 59);end component minute;component hour isport ( clk : in std_logic;reset: in std_logic;daout: out integer range 0 to 11);end component hour;component alert isport ( clk,clk1,reset,stop:in std_logic;dainm:in integer range 0 to 59;dains:in integer range 0 to 59;speak:out std_logic);end component alert;component settime isport(clk1: in std_logic;reset: in std_logic;sec,min:in integer range 0 to 59;hour: in integer range 0 to 11;daout: out integer range 0 to 9;dp: out std_logic;sel: out std_logic_vector(5 downto 0));end component settime;component deled isport(num: in integer range 0 to 9;led: out std_logic_vector(6 downto 0));end component deled;signal min:std_logic;signal secondout:integer range 0 to 59;signal hour1:std_logic;signal minuteout:integer range 0 to 59;signal hourout:integer range 0 to 11;signal settimeout:integer range 0 to 9;beginu1:second port map(clk=>clk,reset=>reset,setmin=>setmin,enmin=>min,daout=>secondout);u2:minute port map(clk=>min,clks=>clk,reset=>reset,sethour=>sethour,enhour=>hour1,daout=>minuteout);u3:hour port map(clk=>hour1,reset=>reset,daout=>hourout);u4:alert port map(clk=>clk,clk1=>clk1,reset=>reset,stop=>stop,dainm=>minuteout,dains=>secondout,speak=> speak);u5:settime port map(clk1=>clk1,reset=>reset,sec=>secondout,min=>minuteout,hour=>hourout,daout=>settimeou t,dp=>dp,sel=>sel);u6:deled port map(num=>settimeout,led=>led);end architecture one;。

(完整word版)24小时数字钟VHDL语言

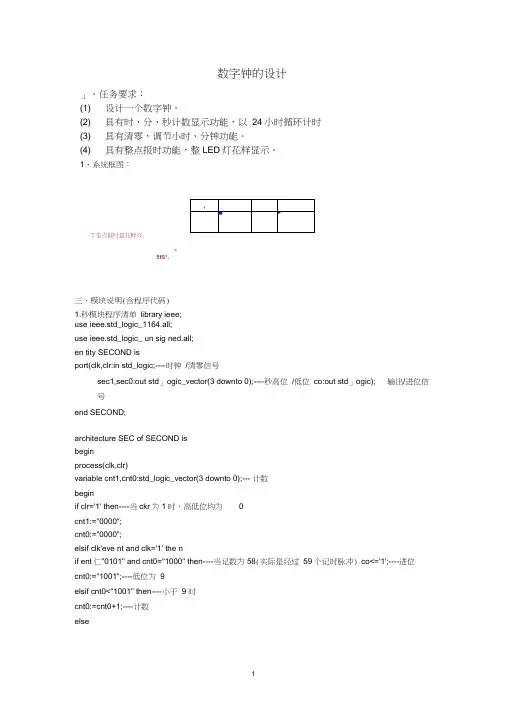

数字钟的设计」、任务要求:(1) 设计一个数字钟。

(2) 具有时,分,秒计数显示功能,以24小时循环计时(3) 具有清零,调节小时、分钟功能。

(4) 具有整点报时功能,整LED灯花样显示。

1、系统框图:T荃点捱吋盘花畔亦,*5fS*.三、模块说明(含程序代码)1.秒模块程序清单library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_ un sig ned.all;en tity SECOND isport(clk,clr:in std_logic;----时钟/清零信号sec1,sec0:out std」ogic_vector(3 downto 0);----秒高位/低位co:out std」ogic); 输出/进位信号end SECOND;architecture SEC of SECOND isbeginprocess(clk,clr)variable cnt1,cnt0:std_logic_vector(3 downto 0);--- 计数beginif clr='1' then----当ckr为1时,高低位均为0cnt1:="0000";cnt0:="0000";elsif clk'eve nt and clk='1' the nif ent仁"0101" and cnt0="1000" then----当记数为58(实际是经过59个记时脉冲) co<='1';----进位cnt0:="1001";----低位为9elsif cnt0<"1001" then----小于9 时cnt0:=cnt0+1;----计数elsecntO:="OOOO";if cnt1<"0101" then----高位小于 5 时 cnt1:=cnt1+1; elsecnt1:="0000"; co<='0'; end if; end if; end if; sec1<=c ntl; sec0<=c ntO; end process; end SEC;秒模块仿真波形mwmnnmuuuumjumnmnnnnnmmjuuuuumnR秒模块原理图Ei i 1Jsecip. 0J «oD[3.4]coi insti. . 1 B 1. .iVW 召当clr=1时,秒的高低位清零;当 clr=0时,来一个时钟信号 sec0加1,当sec0加到九时清零,co=1, secl 加1。

vhdl实验报告--数字钟

VHDL实验报告一、实验目的1、设计一个24小时制数字钟,要求能显示时,分,秒,并且可以手动调整时和分。

2、通过复杂实验,进一步加深对VHDL语言的掌握程度。

二、实验原理数字钟的主体是计数器,它记录并显示接收到的秒脉冲个数,其中秒和分为模60计数器,小时是模24计数器,分别产生3位BCD码。

BCD码经译码,驱动后接数码管显示电路。

秒模60计数器的进位作为分模60计数器的时钟,分模60计数器的进位作为模24计数器的时钟。

为了实现手动调整时间,在外部增加了setm(调整分),seth(调整时)按键,当这两个按键为低电平时,电路正常计时,当为高电平时,分别调整分,时。

同时在外部还增加了一个清零按键clr.和消抖动电路。

三、实验步骤1、单元模块设计部分1)消抖动电路关键部分signal key_in1,key_in2:std_logic:='0';beginprocess(clk,key_in)beginif clk'event and clk='1' thenkey_in1<=key_in;key_in2<=key_in1;if key_in='1' and key_in1='1' and key_in2='1' then key_out<='1';else key_out<='0';end if;2) 模60计数器程序关键部分:signal md_temp,mg_temp:std_logic_vector(3 downto 0);beginprocess(clk,clr)beginif clr='1' thenmd_temp<="0000"; mg_temp<="0000";elsif set='1' thenmd_temp<=setl; mg_temp<=seth;elsif clk'event and clk='1' thenif md_temp="1001" thenmd_temp<="0000";mg_temp<=mg_temp+'1';else md_temp<=md_temp+'1';if md_temp="1001" and mg_temp="0101" thenmd_temp<="0000";mg_temp<="0000";2、模24计数器程序关键部分signal hd_temp,hg_temp:std_logic_vector(3 downto 0);beginprocess(clk,clr,set,setl,seth)isbeginif set='1' then hd_temp<=setl; hg_temp<=seth;elsif clr='1' then hd_temp<="0000"; hg_temp<="0000";elsif clk'event and clk='1' thenif hg_temp="0010" and hd_temp="0011" thenhd_temp<="0000"; hg_temp<="0000";elsif hd_temp="1001" thenhg_temp<=hg_temp+'1' hd_temp<="0000";else hd_temp<=hd_temp+'1';end if;end if;end process ;3、清零和调时部分显示部分关键程序process (sd,sg,md,mg,hd,hg)begincase sd iswhen "0000" =>sl<="1111110";when "0001" =>sl<="0110000";when "0010" =>sl<="1101101";when "0011" =>sl<="1111001";when "0100" =>sl<="0110011";when "0101" =>sl<="1011011";when "0110" =>sl<="1011111";when "0111" =>sl<="1110000";when "1000" =>sl<="1111111";when "1001" =>sl<="1111011";when others =>sl<="0000000";end case;if clk_g'event and clk_g='1' thenif sel="101" thensel<="000";else sel<=sel+'1';end if;end if;process(sel,sd,sl,sg,sh,md,ml,mg,mh,hd,hl,hg,hh)begincase sel iswhen"000"=>led<=sl;led_which<=sd;when"001"=>led<=sh;led_which<=sg;when"010"=>led<=ml;led_which<=md;when"011"=>led<=mh;led_which<=mg;when"100"=>led<=hl;led_which<=hd;when"101"=>led<=hh;led_which<=hg;when others=>led<="0000000";led_which<="0000";end case;4、顶层文件关键程序port(clk,clk_g:in std_logic;-----clk_g是用在数码管显示里面的信号clr: in std_logic;------clr=1时清零setm,seth:in std_logic;---------setm为1时调分,seth为1时调时setd,setg:in std_logic_vector(3 downto 0);----调整时间的时候,setd调整的是低位setg 调整高位led:out std_logic_vector(6 downto 0);sel_out: out std_logic_vector(2 downto 0);led_which: out std_logic_vector(3 downto 0));---输出的是秒分时的哪一个beginu1:de_shake port map (clk=>clk,key_in=>clr,key_out=>clro);u2:de_shake port map (clk=>clk,key_in=>setm,key_out=>setmo);u3:de_shake port map (clk=>clk,key_in=>seth,key_out=>setho);u4:s60 port map (clk=>clk,clr=>clro,sd=>sdl,sg=>sgh,fenmaichong=>fenmaichong o);u5:m60 port map (clk=>fenmaichongo,clr=>clro,md=>mdl,mg=>mgh,xiaoshimaichong=> xiaoshimaichongo,setl=>setd,seth=>setg,set=>setmo);u6:h24 port map (clk=>xiaoshimaichongo,clr=>clro,hd=>hdl,hg=>hgh,set=>setho,se tl=>setd,seth=>setg);u7:led_xs port map (clk_g=>clk_g,sd=>sdl,sg=>sgh,md=>mdl,mg=>mgh,hd=>hdl, hg=>hgh,led=>led,sel_out=>sel_out,led_which=>led_which);四、实验结果及分析本设计,满足了本次试验设计的任务要求,能显示时分秒,并且可以手动调节分和时。

数字钟VHDL

VHDL实验报告:数字钟一:数字钟的功能1:具有以二十四小时计时、显示、整点报时、时间设置和闹钟的功能。

设计精度要求为1S。

二.功能描述1 . 系统输入:系统状态及校时、定时转换的控制信号为k、trans、set;时钟信号clk,采用1024Hz;系统复位信号reset。

输入信号均由按键产生。

系统输出:LED显示输出,蜂鸣器声音信号输出。

2. 计时:正常工作状态下,每日按24h计时制计时并显示,蜂鸣器无声,逢整点报时。

3. 校时:在计时状态显示下,按下“set键”,进入“小时”校准状态,之后按下“k键”则进入“分”校准状态,继续按下“k 键”则进入“秒复零”状态,第三次按下“k 键”又恢复到正常计时显示状态。

A:“小时”校准状态:在“小时”校准状态下,显示“小时”数码管以1Hz的频率递增计数。

B:“分”校准状态:在“分”校准状态下,显示“分”的数码管以1Hz的频率递增计数。

C:“秒”复零状态:在“秒复零”状态下,显示“秒”的数码管复零。

4. 整点报时:蜂鸣器在“59”分钟的第“51”、“53”、“55”、“57‘秒发频率为512Hz的低音,在“59”分钟的第“59”秒发频率为1024Hz的高音,结束时为整点。

5. 显示:要求采用扫描显示方式驱动6个LED数码管显示小时、分、秒。

闹钟:闹钟定时时间到,蜂鸣器发出周期为1s的“滴”、“滴”声,持续时间为10s;闹钟定时显示。

6. 闹钟定时设置:在闹钟定时显示状态下,按下“set键”,进入闹钟的“时”设置状态,之后按下“k键”进入闹钟的“分”设置状态,继续按下“k 键”则进入“秒”设置状态,第三次按下“k键”又恢复到闹钟定时显示状态。

A:闹钟“小时”设置状态:在闹钟“小时”设置状态下,显示“小时”的数码管以1Hz的频率递增计数。

B:闹钟:“分”设置状态:在闹钟“分”设置状态下,显示“分”的数码管以1Hz的频率递增计数。

三:仿真。

分主控模块、计时校时模块、闹钟设定模块、选择显示模块、整点报时及闹铃模块、分频模块、动态显示模块。

24小时数字时钟的VHDL程序 2012

24小时数字时钟的VHDL程序2012-4-20 23:24阅读(37)先编辑一个74LS161十进制计数器:Library ieee;Use ieee.std_logic_1164.all;Use ieee.std_logic_unsigned.all;Entity court161 isport( clk,CTT,CTP,LD,CR:in std_logic;D3,D2,D1,D0: in std_logic;Q:out std_logic_VECTOR(3 DOWNTO 0);Co: out std_logic);end court161;architecture court of court161 issignal a,b,c: std_logic ;signal D,CQI:std_logic_vector(3 downto 0);beginD<=D3&D2&D1&D0;a<=CTT and CTP;b<=(not (CQI(3) and CQI(0)))and LD; process(clk,CTT,CTP,LD,CR,D3,D2,D1,D0) beginif a='1' thenif clk'event and clk='1' thenif b='0' then CQI<=D;else CQI<=CQI+1;end if;end if;if CQI=9 then c<='1';else c<='0';end if;end if;if clk'event and clk='1' then Co<=c;end if;if CR='0' then CQI<="0000";end if;Q<=CQI ;end process; end ;再编辑一个7段数码管(共阴极)显示驱动程序:Library ieee;Use ieee.std_logic_1164.all;Entity QDLED7 isPORT(DATA:IN STD_LOGIC_VECTOR(3 DOWNTO 0);a,b,c,d,e,f,g:out std_logic);end QDLED7;Architecture LED of QDLED7 issignal y: STD_LOGIC_VECTOR(6 DOWNTO 0); beginprocess(DATA)begincase DATA iswhen "0000"=>y<="1111110" ;when "0001"=>y<="0110000" ;when "0010"=>y<="1101101" ;when "0011"=>y<="1111001" ;when "0100"=>y<="0110011" ;when "0101"=>y<="1011011" ;when "0110"=>y<="1011111" ;when "0111"=>y<="1110000" ;when "1000"=>y<="1111111" ;when "1001"=>y<="1111011" ;when others=>null;end case;a<=y(6);b<=y(5);c<=y(4);d<=y(3);e<=y(2);f<=y(1);g<=y(0);end process;end;然后在编写时钟描述语言Library ieee;Use ieee.std_logic_1164.all;Use ieee.std_logic_unsigned.all;Entity timer24 isport(CP,CR:IN STD_LOGIC;AS0,BS0,CS0,DS0,ES0,FS0,GS0,AS1,BS1,CS1,DS1,ES1,FS1 ,GS1:OUT STD_LOGIC;AM0,BM0,CM0,DM0,EM0,FM0,GM0,AM1,BM1,CM1,DM1,EM1,FM1 ,GM1:OUT STD_LOGIC;AH0,BH0,CH0,DH0,EH0,FH0,GH0,AH1,BH1,CH1,DH1,EH1,FH1 ,GH1:OUT STD_LOGIC);END TIMER24;architecture TIMER of TIMER24 issignal H1,H0,M1,M0,S1,S0:std_logic_vector(3 downto 0); SIGNAL C0,C1,C2,C3,C4,C5: std_logic ;COMPONENT court161 IS port( clk,CTT,CTP,LD,CR:in std_logic;D3,D2,D1,D0:in std_logic;Q:out std_logic_VECTOR(3 DOWNTO 0);Co: out std_logic);end COMPONENT;COMPONENT QDLED7 ISPORT(DATA:IN STD_LOGIC_VECTOR(3 DOWNTO 0);a,b,c,d,e,f,g:out std_logic);end COMPONENT;beginU0:court161 PORTMAP(CP,'1','1','1',CR,'0','0','0','0',S0,C0);U1:court161 PORT MAP(C0,'1','1',(NOT(S1(2)ANDS1(0))),CR,'0','0','0','0',S1,C1);U2:court161 PORT MAP((NOT(S1(2)ANDS1(0))),'1','1','1',CR,'0','0','0','0',M0,C2);U3:court161 PORT MAP(C2,'1','1',(NOT(M1(2)ANDM1(0))),CR,'0','0','0','0',M1,C3);U4:court161 PORT MAP(C3,'1','1','1',(CR AND(NOT(H1(1) AND H0(2)))),'0','0','0','0',H0,C4);U5:court161 PORT MAP(C4,'1','1',(NOT H1(1)),(CRAND(NOT(H1(1) AND H0(2)))),'0','0','0','0',H1,C5);U6:QDLED7 PORT MAP(S0,AS0,BS0,CS0,DS0,ES0,FS0,GS0);U7:QDLED7 PORT MAP(S1,AS1,BS1,CS1,DS1,ES1,FS1,GS1);U8:QDLED7 PORT MAP(M0,AM0,BM0,CM0,DM0,EM0,FM0,GM0);U9:QDLED7 PORT MAP(M1,AM1,BM1,CM1,DM1,EM1,FM1,GM1);U10:QDLED7 PORT MAP(H0,AH0,BH0,CH0,DH0,EH0,FH0,GH0);U11:QDLED7 PORT MAP(H1,AH1,BH1,CH1,DH1,EH1,FH1,GH1);END;接上数码管,和脉冲信号发生器,必要时要分频,分成脉冲周期为1秒的脉冲周期方可。

基于vhdl语言数字时钟设计说明书

一、设计要求 (1)二、设计原理及框图 (1)1、设计原理 (1)2、结构框图 (1)三、设计过程 (2)1、模块化设计 (2)2、顶层文件生成 (3)四、仿真调试过程 (3)1、各模块时序仿真图 (3)2、仿真过程中遇到的问题 (4)五、设计体会及收获 (4)一、设计要求1、稳定的显示时、分、秒。

2、当电路发生走时误差时,要求电路有校时功能。

3、电路有整点报时功能。

报时声响为四低一高,最后一响高音正好为整点。

二、设计原理及框图1、设计原理系统框图由六个模块组成,分别为:秒、分、时计数模块,整点报时模块,LED动态显示扫描模块,调时控制模块组成。

其工作原理是:基准脉冲输入信号同时加到秒、分、时、分隔符的脉冲输入端,采用并行计数的方式,秒的进位接到分的使能端上,秒的使能借到分隔符的使能上,分得接到时的使能端上,完成秒、分、时和分隔符的循环计数。

整点报时是根据分的A、B输出同时为0时,整点报时模块输出高电平控制报时。

LED显示扫描模块根据输入的扫描信号CKDSP轮流选通秒、分、时、分隔符的8位八段数码管,LED显示译码器完成计数器输出的BCD的译码。

2、结构框图三、设计过程1、模块化设计(1)秒计时模块秒计时模块由一个60位计数器为主体构成,其输入输出端口组成为:Clk:计时时钟信号Reset:异步清零信号Setmin:分钟设置信号Enmin:使能输出信号Daout[6:0]:BCD码输出(2)分计时模块分计时模块由一个60位计数器为主体构成,其输入输出端口组成为:Clk、clk1:计时时钟信号Reset:异步清零信号Sethour:小时设置信号Enmin:使能输出信号Daout[6:0]:BCD码输出(3)时计时模块时计时模块由24位计数器为主体构成,其输入输出端口组成为:Clk:计时时钟信号Reset:异步清零信号Daout[6:0]:BCD码输出(4)显示模块系统时间输出由六个七段数码管显示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字钟的设计一、任务要求:(1)设计一个数字钟。

(2)具有时,分,秒计数显示功能,以24小时循环计时。

(3)具有清零,调节小时、分钟功能。

(4)具有整点报时功能,整LED灯花样显示。

二、系统框图:三、模块说明(含程序代码)1. 秒模块程序清单library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity SECOND isport(clk,clr:in std_logic;----时钟/清零信号sec1,sec0:out std_logic_vector(3 downto 0);----秒高位/低位co:out std_logic);-------输出/进位信号end SECOND;architecture SEC of SECOND isbeginprocess(clk,clr)variable cnt1,cnt0:std_logic_vector(3 downto 0);---计数beginif clr='1' then----当ckr为1时,高低位均为0cnt1:="0000";cnt0:="0000";elsif clk'event and clk='1' thenif cnt1="0101" and cnt0="1000" then----当记数为58(实际是经过59个记时脉冲)co<='1';----进位cnt0:="1001";----低位为9elsif cnt0<"1001" then----小于9时cnt0:=cnt0+1;----计数elsecnt0:="0000";if cnt1<"0101" then----高位小于5时cnt1:=cnt1+1;elsecnt1:="0000";co<='0';end if;end if;end if;sec1<=cnt1;sec0<=cnt0;end process;end SEC;秒模块仿真波形秒模块原理图当clr=1时,秒的高低位清零;当clr=0时,来一个时钟信号sec0加1,当sec0加到九时清零,co=1,sec1加1。

2. 分模块程序清单library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity MINUTE isport(clk,en:in std_logic;min1,min0:out std_logic_vector(3 downto 0);co:out std_logic);end MINUTE;architecture MIN of MINUTE isbeginprocess(clk)variable cnt1,cnt0:std_logic_vector(3 downto 0);beginif clk'event and clk='1' thenif en='1' thenif cnt1="0101" and cnt0="1000" thenco<='1';cnt0:="1001";elsif cnt0<"1001" thencnt0:=cnt0+1;elsecnt0:="0000";if cnt1<"0101" thencnt1:=cnt1+1;elsecnt1:="0000";co<='0';end if;end if;end if;end if;min1<=cnt1;min0<=cnt0;end process;end MIN;分模块仿真波形分模块原理图当en=0时,分的高低位清零;当en=1时,来一个时钟信号min0加1,当min0加到九时清零,co=1,min1加1。

3. 时模块程序清单library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity HOUR isport(clk,en:in std_logic;----输入时钟/高电平有效的使能信号h1,h0:out std_logic_vector(3 downto 0));----时高位/低位end HOUR;architecture hour_arc of HOUR isbeginprocess(clk)variable cnt1,cnt0:std_logic_vector(3 downto 0);----记数beginif clk'event and clk='1' then---上升沿触发if en='1' then---同时“使能”为1if cnt1="0010" and cnt0="0011" thencnt1:="0000";----高位/低位同时为0时cnt0:="0000";elsif cnt0<"1001" then----低位小于9时,低位记数累加cnt0:=cnt0+1;elsecnt0:="0000";cnt1:=cnt1+1;-----高位记数累加end if;end if;end if;h1<=cnt1;h0<=cnt0;end process;end hour_arc;分模块仿真波形分模块原理图当en=0时,时的高低位清零;当en=1并且时钟信号到来时,当时达到23时,时的高低位清零,否则h0加1 ,当h0加到9时h0清零h1加1。

4. 动态扫描模块library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity seltome_v2 isport(clk:in std_logic;------扫描时钟sec1,sec0,min1,min0,h1,h0:in std_logic_vector(3 downto 0);-----分别为秒个位/时位;分个位时位;分别为时个位/时位daout:out std_logic_vector(3 downto 0);----------------输出sel:out std_logic_vector(2 downto 0));-----位选信号end seltome_v2;architecture fun of seltome_v2 issignal count:std_logic_vector(2 downto 0);----计数信号beginsel<=count;process(clk)beginif(clk'event and clk='1') thenif(count>="101") thencount<="000";elsecount<=count+1;end if;end if;case count iswhen"101"=>daout<= sec0;----秒个位when"100"=>daout<= sec1;----秒十位when"011"=>daout<=min0; ----分个位when"010"=>daout<=min1;---分十位when"001"=>daout<=h0; ----时个位when others =>daout<=h1;----时十位end case;end process;end fun;分模块仿真波形分模块原理图5. 报时模块library ieee;use ieee.std_logic_1164.all;entity ALERT isport(m1,m0,s1,s0:in std_logic_vector(3 downto 0);------输入秒、分高/低位信号clk:in std_logic;------高频声控制q500,qlk:out std_logic);----低频声控制end ALERT;architecture sss_arc of ALERT isbeginprocess(clk)beginif clk'event and clk='1' thenif m1="0101" and m0="1001" and s1="0101" then----当秒高位为5,低位为9时且分高位为5if s0="0001" or s0="0011" or s0="0101" or s0="0111" then---当分的低位为1或3或5或7时q500<='1';----低频输出为1elseq500<='0';----否则输出为0end if;end if;if m1="0101" and m0="1001" and s1="0101" and s0="1001" then---当秒高位为5,低位为9时且分高位为5,----分低位为9时,也就是“59分59秒”的时候“报时”qlk<='1';-----高频输出为1elseqlk<='0';end if;end if;end process;end sss_arc;报时模块仿真波形报时模块原理图6. 显示模块library ieee;use ieee.std_logic_1164.all;entity DISPLAY isport(d:in std_logic_vector(3 downto 0);----连接seltime扫描部分d信号q:out std_logic_vector(6 downto 0));----输出段选信号(电平)end DISPLAY;architecture disp_are of DISPLAY isbeginprocess(d)begincase d iswhen"0000" =>q<="0111111";--显示0when"0001" =>q<="0000110";--显示1when"0010" =>q<="1011011";--显示2when"0011" =>q<="1001111";--显示3when"0100" =>q<="1100110";--显示4when"0101" =>q<="1101101";--显示5when"0110" =>q<="1111101";--显示6when"0111" =>q<="0100111";--显示7when"1000" =>q<="1111111";--显示8when others =>q<="1101111";--显示9end case;end process;end disp_are;显示模块仿真波形显示模块原理图数字时钟原理图:数字时钟波形仿真图:。