CY7C1350G-133AXC中文资料

CY7C1352F-133AC中文资料

4.5

ns

205

mA

40

mA

Pin Configuration

100-Pin TQFP

NC

NC

81 A

82 A

85 ADV/LD

86 OE

87 CEN

WE

89 CLK

VSS

VDD

CE3

BWA

BWB

95 NC

96 NC

CE2

CE1

99 A

A

83

84

88

90

91

92

93

94

97

98

100

NC

1

NC

2

NC

• Internally self-timed output buffer control to eliminate the need to use OE

• Byte Write capability • 256K x 18 common I/O architecture • Single 3.3V power supply • 2.5V / 3.3V I/O Operation • Fast clock-to-output times

NC

77

VDDQ

76

VSS

75

NC

74

DQPA

73

DQA

72

DQA

71

VSS

70

VDDQ

69

DQA

68

DQA

67

VSS

BYTE A

66

NC

65

VDD

64

ZZ

63

DQA

62

DQA

61

CY7C1338G-133AXC资料

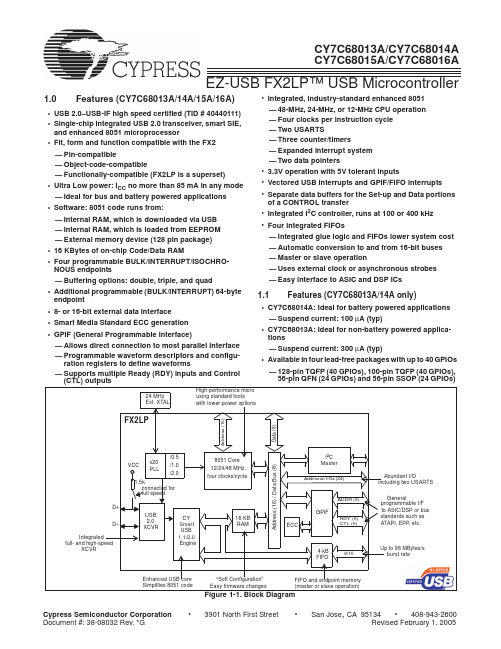

PRELIMINARY4-Mbit (128K x 32) Flow-Through Sync SRAMCY7C1338GFeatures•128K X 32 common I/O•3.3V –5% and +10% core power supply (V DD)•2.5V or 3.3V I/O supply (V DDQ)•Fast clock-to-output times—6.5 ns (133-MHz version)—7.5 ns (117-MHz version)—8.0 ns (100-MHz version)•Provide high-performance 2-1-1-1 access rate •User-selectable burst counter supporting Intel®Pentium® interleaved or linear burst sequences •Separate processor and controller address strobes •Synchronous self-timed write•Asynchronous output enable•Lead-Free 100-pin TQFP and 119-ball BGA packages •“ZZ” Sleep Mode option Functional Description[1]The CY7C1338G is a 131,072 x 32 synchronous cache RAM designed to interface with high-speed microprocessors with minimum glue logic. Maximum access delay from clock rise is 6.5 ns (133-MHz version). A 2-bit on-chip counter captures the first address in a burst and increments the address automati-cally for the rest of the burst access. All synchronous inputs are gated by registers controlled by a positive-edge-triggered Clock Input (CLK). The synchronous inputs include all addresses, all data inputs, address-pipelining Chip Enable (CE1), depth-expansion Chip Enables (CE2 and CE3), Burst Control inputs (ADSC, ADSP, and ADV), Write Enables(BW[A:D], and BWE), and Global Write (GW). Asynchronous i nputs include the Output Enable (OE) and the ZZ pin.The CY7C1338G allows either interleaved or linear burst sequences, selected by the MODE input pin. A HIGH selects an interleaved burst sequence, while a LOW selects a linear burst sequence. Burst accesses can be initiated with the Processor Address Strobe (ADSP) or the cache Controller Address Strobe (ADSC) inputs. Address advancement is controlled by the Address Advancement (ADV) input. Addresses and chip enables are registered at rising edge of clock when either Address Strobe Processor (ADSP) or Address Strobe Controller (ADSC) are active. Subsequent burst addresses can be internally generated as controlled by the Advance pin (ADV).The CY7C1338G operates from a +3.3V core power supply while all outputs may operate with either a +2.5 or +3.3V supply. All inputs and outputs are JEDEC-standard JESD8-5-compatible.Note:1.For best–practices recommendations, please refer to the Cypress application note System Design Guidelines on .Selection Guide133 MHz 117 MHz 100 MHz Unit Maximum Access Time6.57.58.0ns Maximum Operating Current 225220205mA Maximum Standby Current404040mAShaded areas contain advance information. Please contact your local Cypress sales representative for availability of these parts.Pin Configurations100-Pin TQFPAAAAA 1A 0N C N CV S SV D DN C A AAAA ANC DQ B V DDQ V SSQ DQ B DQ B DQ B DQ B V SSQ V DDQ DQ B DQ B V SS NC V DD DQ A DQ A V DDQ V SSQ DQ A DQ A DQ A DQ A V SSQ V DDQ DQ A DQ A NCNC DQ C DQ C V DDQ V SSQ DQ C DQ CDQ C DQ C V SSQ V DDQ DQ C DQ C NC V DD NC V SS DQ D DQ D V DDQ V SSQ DQ D DQ D DQ D DQ D V SSQ V DDQ DQ D DQ D NCAAC E 1C E 2B W DB W CB W BB W AC E 3V D DV S SC L KG WB W EO E A D S P A A123456789101112131415161718192021222324252627282930313233343536373839404142434445464748495080797877767574737271706968676665646362616059585756555453525110099989796959493929190898887868584838281BYTE ABYTE CAA D V A D S C ZZ M O D E N C BYTE BDQ B BYTE DCY7C1338GPin DefinitionsName I/O DescriptionA0, A1, A Input-Synchronous Address Inputs used to select one of the 128K address location s. Sampled at the rising edge of the CLK if ADSP or ADSC is active LOW, and CE1,CE2, and CE3 are sampled active. A[1:0] feed the 2-bit counter.BW A,BW B BW C,BW DInput-SynchronousByte Write Select Inputs, active LOW. Qualified with BWE to conduct byte writes to the SRAM.Sampled on the rising edge of CLK.GW Input-Synchronous Global Write Enable Input, active LOW. When asserted LOW on the rising edge of CLK, a global write is conducted (ALL bytes are written, regardless of the values on BW[A:D] and BWE).BWE Input-Synchronous Byte Write Enable Input, active LOW. Sampled on the rising edge of CLK. This signal must be asserted LOW to conduct a byte write.CLK Input-Clock Clock Input. Used to capture all synchronous inputs to the device. Also used to increment the burst counter when ADV is asserted LOW, during a burst operation.CE1Input-Synchronous Chip Enable 1 Input, active LOW. Sampled on the rising edge of CLK. Used in conjunction with CE2 and CE3 to select/deselect the device. ADSP is ignored if CE1 is HIGH.CE1 is sampled only when a new external address is loaded.CE2Input-Synchronous Chip Enable 2 Input, active HIGH. Sampled on the rising edge of CLK. Used in conjunction with CE1 and CE3 to select/deselect the device. CE2 is sampled only when a new external address is loaded.CE3Input-Synchronous Chip Enable 3 Input, active LOW. Sampled on the rising edge of CLK. Used in conjunction with CE1 and CE2 to select/deselect the device. CE3 is sampled only when a new external address is loaded.OE Input-Asynchronous Output Enable, asynchronous input, active LOW. Controls the direction of the I/O pins. When LOW, the I/O pins behave as outputs. When deasserted HIGH, I/O pins are tri-stated, and act as input data pins. OE is masked during the first clock of a read cycle when emerging from a deselected state.ADV Input-Synchronous Advance Input signal, sampled on the rising edge of CLK. When asserted, it automatically increments the address in a burst cycle.Pin Configurations (continued)2345671A B C D E F G H J K L M N P R T U V DDQNCNCNCDQ CDQ DDQ CDQ DA A A AADSP V DDQ CE2ADQ CV DDQDQ CV DDQV DDQV DDQDQ DDQ DNCNCV DDQV DDCLKV DDV SSV SSV SSV SSV SSV SSV SSV SSNCNCNCNCNCNCNCNCNCNCNCV DDQV DDQV DDQA A AANCAAAAAAA0A1DQ A DQ CDQ ADQ ADQ ADQ BDQ BDQ BDQ BDQ BDQ BDQ BDQ ADQ ADQ ADQ ADQ BV DDDQ CDQ CDQ CV DDDQ DDQ DDQ DDQ DADSCNCCE1OEADVGWV SSV SSV SSV SSV SSV SSV SSV SS NCMODENCNCBW BBW CNC V DD NCBW ANCBWEBW DZZ119-Ball BGAFunctional OverviewAll synchronous inputs pass through input registers controlled by the rising edge of the clock. Maximum access delay from the clock rise (t C0) is 6.5 ns (133-MHz device).The CY7C1338G supports secondary cache in systems utilizing either a linear or interleaved burst sequence. The interleaved burst order supports Pentium ® and i486™processors. The linear burst sequence is suited for processors that utilize a linear burst sequence. The burst order is user-selectable, and is determined by sampling the MODE input. Accesses can be initiated with either the Processor Address Strobe (ADSP) or the Controller Address Strobe (ADSC). Address advancement through the burst sequence is controlled by the ADV input. A two-bit on-chip wraparound burst counter captures the first address in a burst sequence and automatically increments the address for the rest of the burst access.Byte write operations are qualified with the Byte Write Enable (BWE) and Byte Write Select (BW [A:D]) inputs. A Global Write Enable (GW) overrides all byte write inputs and writes data to all four bytes. All writes are simplified with on-chip synchronous self-timed write circuitry.Three synchronous Chip Selects (CE 1, CE 2, CE 3) and an asynchronous Output Enable (OE) provide for easy bank selection and output tri-state control. ADSP is ignored if CE 1is HIGH.Single Read AccessesA single read access is initiated when the following conditions are satisfied at clock rise: (1) CE 1, CE 2, and CE 3 are all asserted active, and (2) ADSP or ADSC is asserted LOW (if the access is initiated by ADSC, the write inputs must be deasserted during this first cycle). The address presented to the address inputs is latched into the address register and the burst counter/control logic and presented to the memory core.If the OE input is asserted LOW, the requested data will be available at the data outputs a maximum to t CDV after clock rise. ADSP is ignored if CE 1 is HIGH.Single Write Accesses Initiated by ADSPThis access is initiated when the following conditions are satisfied at clock rise: (1) CE 1, CE 2, CE 3 are all asserted active, and (2) ADSP is asserted LOW. The addresses presented are loaded into the address register and the burst inputs (GW, BWE, and BW[A:D ])are ignored during this first clock cycle. If the write inputs are asserted active (see Write Cycle Descriptions table for appropriate states that indicate a write) on the next clock rise, the appropriate data will be latched and written into the device. Byte writes are allowed.During byte writes, BW A controls DQ A and BWB controls DQ B .BWC controls DQ C , and BW D controls DQ D . All I/Os are tri-stated during a byte write.Since this is a common I/O device, the asynchronous OE input signal must be deasserted and the I/Os must be tri-stated prior to the presentation of data to DQs. As a safety precaution, the data lines are tri-stated once a write cycle is detected, regardless of the state of OE.ADSPInput-Synchronous Address Strobe from Processor, sampled on the rising edge of CLK, active LOW . Whenasserted LOW, addresses presented to the device are captured in the address registers. A [1:0] arealso loaded into the burst counter. When ADSP and ADSC are both asserted, only ADSP is recog-nized. ASDP is ignored when CE 1 is deasserted HIGHADSC Input-Synchronous Address Strobe from Controller, sampled on the rising edge of CLK, active LOW . When assertedLOW, addresses presented to the device are captured in the address registers. A [1:0] are also loadedinto the burst counter. When ADSP and ADSC are both asserted, only ADSP is recognized.ZZInput-Asynchronous ZZ “sleep” Input, active HIGH . When asserted HIGH places the device in a non-time-critical “sleep”condition with data integrity preserved. For normal operation, this pin has to be LOW or left floating.ZZ pin has an internal pull-down.DQsI/O-Synchronous Bidirectional Data I/O lines . As inputs, they feed into an on-chip data register that is triggered bythe rising edge of CLK. As outputs, they deliver the data contained in the memory location specifiedby the addresses presented during the previous clock rise of the read cycle. The direction of the pins is controlled by OE . When OE is asserted LOW, the pins behave as outputs. When HIGH, DQs are placed in a tri-state condition.V DD Power Supply Power supply inputs to the core of the device .V SS GroundGround for the core of the device .V DDQ I/O Power SupplyPower supply for the I/O circuitry . V SSQ I/O Ground Ground for the I/O circuitry . MODEInput-StaticSelects Burst Order . When tied to GND selects linear burst sequence. When tied to V DD or left floating selects interleaved burst sequence. This is a strap pin and should remain static during device operation. Mode Pin has an internal pull-up.NCNo Connects . Not Internally connected to the die.Pin Definitions (continued)Name I/ODescriptionSingle Write Accesses Initiated by ADSCThis write access is initiated when the following conditions are satisfied at clock rise: (1) CE1, CE2, and CE3 are all asserted active, (2) ADSC is asserted LOW, (3) ADSP is deasserted HIGH, and (4) the write input signals (GW, BWE, and BW[A:D]) indicate a write access. ADSC is ignored if ADSP is active LOW.The addresses presented are loaded into the address register and the burst counter/control logic and delivered to the memory core. The information presented to DQ[A:D] will be written into the specified address location. Byte writes are allowed. During byte writes, BW A controls DQ A, BW B controls DQ B, BW C controls DQ C, and BW D controls DQ D. All I/Os are tri-stated when a write is detected, even a byte write. Since this is a common I/O device, the asynchronous OE input signal must be deasserted and the I/Os must be tri-stated prior to the presentation of data to DQs. As a safety precaution, the data lines are tri-stated once a write cycle is detected, regardless of the state of OE.Burst SequencesThe CY7C1338G provides an on-chip two-bit wraparound burst counter inside the SRAM. The burst counter is fed by A[1:0], and can follow either a linear or interleaved burst order. The burst order is determined by the state of the MODE input.A LOW on MODE will select a linear burst sequence. A HIGH on MODE will select an interleaved burst order. Leaving MODE unconnected will cause the device to default to a inter-leaved burst sequence.Sleep ModeThe ZZ input pin is an asynchronous input. Asserting ZZ places the SRAM in a power conservation “sleep” mode. Two clock cycles are required to enter into or exit from this “sleep”mode. While in this mode, data integrity is guaranteed. Accesses pending when entering the “sleep” mode are not considered valid nor is the completion of the operation guaranteed. The device must be deselected prior to entering the “sleep” mode. CEs, ADSP, and ADSC must remain inactive for the duration of t ZZREC after the ZZ input returns LOW.Interleaved Burst Address Table(MODE = Floating or V DD)FirstAddressA1, A0SecondAddressA1, A0ThirdAddressA1, A0FourthAddressA1, A0 00011011010011101011000111100100 Linear Burst Address Table (MODE = GND) FirstAddressA1,A0SecondAddressA1,A0ThirdAddressA1,A0FourthAddressA1,A0 00011011011011001011000111000110ZZ Mode Electrical CharacteristicsParameter Description Test Conditions Min.Max.Unit I DDZZ Snooze mode standby current ZZ > V DD– 0.2V40mA t ZZS Device operation to ZZ ZZ > V DD – 0.2V2t CYC ns t ZZREC ZZ recovery time ZZ < 0.2V2t CYC ns t ZZI ZZ active to snooze current This parameter is sampled2t CYC ns t RZZI ZZ Inactive to exit snooze current This parameter is sampled0nsTruth Table[2, 3, 4, 5, 6]Cycle Description AddressUsed CE1CE2CE3ZZ ADSP ADSC ADV WRITE OE CLK DQDeselected Cycle, Power-down None H X X L X L X X X L-H tri-state Deselected Cycle, Power-down None L L X L L X X X X L-H tri-state Deselected Cycle, Power-down None L X H L L X X X X L-H tri-state Deselected Cycle, Power-down None L L X L H L X X X L-H tri-state Deselected Cycle, Power-down None X X X L H L X X X L-H tri-state Snooze Mode, Power-down None X X X H X X X X X X tri-state Read Cycle, Begin Burst External L H L L L X X X L L-H QRead Cycle, Begin Burst External L H L L L X X X H L-H tri-state Write Cycle, Begin Burst External L H L L H L X L X L-H DRead Cycle, Begin Burst External L H L L H L X H L L-H QRead Cycle, Begin Burst External L H L L H L X H H L-H tri-state Read Cycle, Continue Burst Next X X X L H H L H L L-H QRead Cycle, Continue Burst Next X X X L H H L H H L-H tri-state Read Cycle, Continue Burst Next H X X L X H L H L L-H QRead Cycle, Continue Burst Next H X X L X H L H H L-H tri-state Write Cycle, Continue Burst Next X X X L H H L L X L-H DWrite Cycle, Continue Burst Next H X X L X H L L X L-H DRead Cycle, Suspend Burst Current X X X L H H H H L L-H QRead Cycle, Suspend Burst Current X X X L H H H H H L-H tri-state Read Cycle, Suspend Burst Current H X X L X H H H L L-H QRead Cycle, Suspend Burst Current H X X L X H H H H L-H tri-state Write Cycle, Suspend Burst Current X X X L H H H L X L-H DWrite Cycle, Suspend Burst Current H X X L X H H L X L-H D Notes:2.X = “Don't Care.” H = Logic HIGH, L = Logic LOW.3.WRITE = L when any one or more Byte Write enable signals (BW A, BW B, BW C, BW D) and BWE = L or GW= L. WRITE = H when all Byte write enable signalsA B C D4.The DQ pins are controlled by the current cycle and the OE signal. OE is asynchronous and is not sampled with the clock.5.The SRAM always initiates a read cycle when ADSP is asserted, regardless of the state of GW, BWE, or BW X. Writes may occur only on subsequent clocksafter the or with the assertion of ADSC. As a result, OE must be driven HIGH prior to the start of the write cycle to allow the outputs to tri-state. OE is a don't care for the remainder of the write cycle.6.OE is asynchronous and is not sampled with the clock rise. It is masked internally during write cycles. During a read cycle all data bits are tri-state when OE isinactive or when the device is deselected, and all data bits behave as output when OE is active (LOW).Partial Truth Table for Read/Write[2, 7]Function GW BWE BW D BW C BW B BW A Read H H X X X X Read H L H H H H Write Byte A H L H H H L Write Byte B H L H H L H Write Bytes B, A H L H H L L Write Byte C H L H L H H Write Bytes C, A H L H L H L Write Bytes C, B H L H L L H Write Bytes C, B, A H L H L L L Write Byte D H L L H H H Write Bytes D, A H L L H H L Write Bytes D, B H L L H L H Write Bytes D, B, A H L L H L L Write Bytes D, B H L L L H H Write Bytes D, B, A H L L L H L Write Bytes D,C,A H L L L L H Write All Bytes H L L L L L Write All Bytes L X X X X X Note:7.Table only lists a partial listing of the byte write combinations. Any combination of BW X is valid. Appropriate write will be done based on which byte write is active.Maximum Ratings(Above which the useful life may be impaired. For user guide-lines, not tested.)Storage Temperature .................................–65°C to +150°C Ambient Temperature withPower Applied.............................................–55°C to +125°C Supply Voltage on V DD Relative to GND........–0.5V to +4.6V DC Voltage Applied to Outputsin tri-state............................................–0.5V to V DDQ + 0.5V DC Input Voltage....................................–0.5V to V DD + 0.5V Current into Outputs (LOW).........................................20 mA Static Discharge Voltage........................................... >2001V (per MIL-STD-883, Method 3015)Latch-up Current..................................................... >200 mA Operating RangeRangeAmbientTemperature]V DD V DDQ Commercial0°C to +70°C 3.3V −5%/+10% 2.5V –5%to V DD Industrial–40°C to +85°CElectrical Characteristics Over the Operating Range[8, 9]Parameter Description Test ConditionsCY7C1338GUnit Min.Max.V DD Power Supply Voltage 3.135 3.6V V DDQ I/O Supply Voltage 2.375V DD V V OH Output HIGH Voltage V DDQ = 3.3V, V DD = Min., I OH = –4.0 mA 2.4VV DDQ = 2.5V, V DD = Min., I OH = –1.0 mA 2.0V V OL Output LOW Voltage V DDQ = 3.3V, V DD = Min., I OL = 8.0 mA0.4VV DDQ = 2.5V, V DD = Min., I OL = 1.0 mA0.4V V IH Input HIGH Voltage V DDQ = 3.3V 2.0V DD + 0.3V VV DDQ = 2.5V 1.7V DD + 0.3V V V IL Input LOW Voltage[8]V DDQ = 3.3V–0.30.8VV DDQ = 2.5V–0.30.7V I X Input Load Current (except ZZ andMODE)GND ≤ V I≤ V DDQ−55µA Input Current of MODE Input = V SS–30µAInput = V DD5µA Input Current of ZZ Input = V SS–5µAInput = V DD30µA I OZ Output Leakage Current GND ≤ V I≤ V DD, Output Disabled–55µA I OS Output Short Circuit Current V DD = Max., V OUT = GND–300µAI DD V DD Operating Supply Current V DD = Max., I OUT = 0 mA,f = f MAX= 1/t CYC 7.5-ns cycle, 133 MHz225mA8.0-ns cycle, 117 MHz220mA 10-ns cycle, 100 MHz205mAI SB1Automatic CE Power-DownCurrent—TTL Inputs Max. V DD, Device Deselected,V IN≥ V IH or V IN≤ V IL, f = f MAX,inputs switching7.5-ns cycle, 133 MHz90mA8.0-ns cycle, 117 MHz85mA10-ns cycle, 100 MHz80mAI SB2Automatic CE Power-DownCurrent—CMOS Inputs Max. V DD, Device Deselected,V IN≥ V DD – 0.3V or V IN≤ 0.3V,f = 0, inputs staticAll speeds40mAI SB3Automatic CE Power-DownCurrent—CMOS Inputs Max. V DD, Device Deselected,V IN≥V DDQ – 0.3V or V IN≤ 0.3V,f = f MAX, inputs switching7.5-ns cycle, 133 MHz75mA8.0-ns cycle, 117 MHz70mA10-ns cycle, 100 MHz65mAI SB4Automatic CE Power-DownCurrent—TTL Inputs Max. V DD, Device Deselected,V IN≥ V DD – 0.3V or V IN≤ 0.3V,f=0, inputs staticAll speeds45mAShaded areas contain advance information.Notes:8.Overshoot: V IH(AC) < V DD +1.5V (Pulse width less than t CYC/2), undershoot: V IL(AC) > -2V (Pulse width less than t CYC/2).9.TPower-up: Assumes a linear ramp from 0v to V DD(min.) within 200ms. During this time V IH < V DD and V DDQ < V DD.Thermal Resistance [10]Parameter DescriptionTest ConditionsTQFP PackageBGA PackageUnit ΘJAThermal Resistance (Junction to Ambient)Test conditions follow standard test methods and procedures formeasuring thermal impedance, per EIA / JESD51.TBD TBD °C/W ΘJC Thermal Resistance(Junction to Case)TBDTBD°C/WCapacitance [10]Parameter DescriptionTest Conditions TQFP PackageBGA Package UnitC IN Input Capacitance T A = 25°C, f = 1 MHz,V DD = 3.3V. V DDQ = 3.3V55pF C CLK Clock Input Capacitance 55pF C I/OInput/Output Capacitance57pFAC Test Loads and WaveformsSwitching Characteristics Over the Operating Range [11, 12, 13, 14, 15, 16]Parameter Description133 MHz117 MHz 100 MHz Unit Min.Max.Min.Max.Min.Max.t POWER V DD (Typical) to the first Access [11]111msClock t CYC Clock Cycle Time 7.58.510ns t CH Clock HIGH 2.5 3.0 4.0ns t CLClock LOW2.53.04.0nsOutput Times t CDV Data Output Valid After CLK Rise 6.57.58.0ns t DOHData Output Hold After CLK Rise2.02.02.0nsShaded areas contain advance information.Notes:10.Tested initially and after any design or process change that may affect these parameters.11.This part has a voltage regulator internally; t POWER is the time that the power needs to be supplied above V DD (minimum) initially before a read or write operationcan be initiated.12.t CHZ , t CLZ ,t OELZ , and t OEHZ are specified with AC test conditions shown in part (b) of AC Test Loads. Transition is measured ± 200 mV from steady-state voltage.13.At any given voltage and temperature, t OEHZ is less than t OELZ and t CHZ is less than t CLZ to eliminate bus contention between SRAMs when sharing the samedata bus. These specifications do not imply a bus contention condition, but reflect parameters guaranteed over worst case user conditions. Device is designed to achieve High-Z prior to Low-Z under the same system conditions.14.This parameter is sampled and not 100% tested.15.Timing reference level is 1.5V when V DDQ = 3.3V and is 1.25V when V DDQ = 2.5V.16.Test conditions shown in (a) of AC Test Loads unless otherwise noted.OUTPUTR = 317ΩR = 351Ω5pFINCLUDING JIG AND SCOPE (a)(b)OUTPUTR L = 50ΩZ 0= 50ΩV T = 1.5V3.3VALL INPUT PULSESV DDQ GND90%10%90%10%≤1ns≤1ns(c)OUTPUTR = 1667ΩR =1538Ω5pFINCLUDING JIG AND SCOPE(a)(b)OUTPUTR L = 50ΩZ 0= 50ΩV T = 1.25V2.5VALL INPUT PULSES V DDQGND90%10%90%10%≤1ns≤1ns(c)3.3V I/O Test Load2.5V I/O Test Loadt CLZ Clock to Low-Z [12, 13, 14]0ns t CHZ Clock to High-Z [12, 13, 14] 3.5 3.5 3.5ns t OEV OE LOW to Output Valid3.53.5 3.5ns t OELZ OE LOW to Output Low-Z [12, 13, 14]0ns t OEHZOE HIGH to Output High-Z [12, 13, 14]3.53.53.5ns Setup Times t AS Address Set-up Before CLK Rise 1.5 2.0 2.0ns t ADS ADSP , ADSC Set-up Before CLK Rise 1.5 2.0 2.0ns t ADVS ADV Set-up Before CLK Rise1.52.0 2.0ns t WES GW, BWE, BW X Set-up Before CLK Rise 1.5 2.0 2.0ns t DS Data Input Set-up Before CLK Rise 1.5 1.5 1.5ns t CESChip Enable Set-up1.52.02.0ns Hold Times t AH Address Hold After CLK Rise 0.50.50.5ns t ADH ADSP , ADSC Hold After CLK Rise 0.50.50.5ns t WEH GW ,BWE , BW X Hold After CLK Rise 0.50.50.5ns t ADVH ADV Hold After CLK Rise 0.50.50.5ns t DH Data Input Hold After CLK Rise 0.50.50.5ns t CEHChip Enable Hold After CLK Rise0.50.50.5nsSwitching Characteristics Over the Operating Range (continued)[11, 12, 13, 14, 15, 16]Parameter Description133 MHz117 MHz 100 MHz Unit Min.Max.Min.Max.Min.Max.Timing Diagrams[17]Timing Diagrams (continued)[17, 18]Timing Diagrams (continued)[17, 19, 20]ZZ Mode Timing [21, 22]Ordering InformationSpeed (MHz)Ordering Code Package Name Package TypeOperating Range 133CY7C1338G-133AXC A101Lead-Free 100-Lead Thin Quad Flat Pack (14 x 20 x 1.4mm)CommercialCY7C1338G-133BGC BG119119-Ball PBGA (14 x 22 x 2.4mm)CY7C1338G-133BGXC BG119Lead-Free 119-Ball PBGA (14 x 22 x 2.4mm)CY7C1338G-133AXI A101Lead-Free 100-Lead Thin Quad Flat Pack (14 x 20 x 1.4mm)Industrial CY7C1338G-133BGI BG119119-Ball PBGA (14 x 22 x 2.4mm)CY7C1338G-133BGXIBG119Lead-Free 119-Ball PBGA (14 x 22 x 2.4mm)117CY7C1338G-117AXC A101Lead-Free 100-Lead Thin Quad Flat Pack (14 x 20 x 1.4mm)Commercial CY7C1338G-117BGC BG119119-Ball PBGA (14 x 22 x 2.4mm)CY7C1338G-117BGXCBG119Lead-Free 119-Ball PBGA (14 x 22 x 2.4mm)CY7C1338G-117AXI A101Lead-Free 100-Lead Thin Quad Flat Pack (14 x 20 x 1.4mm)Industrial CY7C1338G-117BGI BG119119-Ball PBGA (14 x 22 x 2.4mm)CY7C1338G-117BGXIBG119Lead-Free 119-Ball PBGA (14 x 22 x 2.4mm)100CY7C1338G-100AXC A101Lead-Free 100-Lead Thin Quad Flat Pack (14 x 20 x 1.4mm)Commercial CY7C1338G-100BGC BG119119-Ball PBGA (14 x 22 x 2.4mm)CY7C1338G-100BGXC BG119Lead-Free 119-Ball PBGA (14 x 22 x 2.4mm)CY7C1338G-100AXI A101Lead-Free 100-Lead Thin Quad Flat Pack (14 x 20 x 1.4mm)Industrial CY7C1338G-100BGI BG119119-Ball PBGA (14 x 22 x 2.4mm)CY7C1338G-100BGXIBG119Lead-Free 119-Ball PBGA (14 x 22 x 2.4mm)Shaded areas contain advance information. Please contact your local Cypress sales representative for availability of these parts. Lead-Free BGX package will be available in 2005.Notes:21.Device must be deselected when entering ZZ mode. See Cycle Descriptions table for all possible signal conditions to deselect the device.22.DQs are in high-Z when exiting ZZ sleep mode.Timing Diagrams (continued)Package DiagramsDocument #: 38-05521 Rev. *A Page 16 of 17Intel and Pentium are registered trademarks of Intel Corporation. All product and company names mentioned in this document may be the trademarks of their respective holders.Package Diagrams(continued)Document History PageDocument Title: CY7C1338G 4-Mbit (128K x 32) Flow-Through Sync SRAM Document Number: 38-05521REV.ECN NO.Issue Date Orig. ofChange Description of Change**224369See ECN RKF New data sheet*A278513See ECN VBL Deleted 66 MHzChanged TQFP to PB-Free TQFP in Ordering Info sectionAdded PB-Free BG package。

CY7C63723-PC中文资料

元器件交易网CY7C63743CY7C63722/23CY7C63743enCoRe™ USBCombination Low-Speed USB & PS/2Peripheral ControllerTABLE OF CONTENTS1.0 FEATURES (5)2.0 FUNCTIONAL OVERVIEW (6)2.1 enCoRe USB - The New USB Standard (6)3.0 LOGIC BLOCK DIAGRAM (7)4.0 PIN CONFIGURATIONS (7)5.0 PIN ASSIGNMENTS (7)6.0 PROGRAMMING MODEL (8)6.1 Program Counter (PC) (8)6.2 8-bit Accumulator (A) (8)6.3 8-bit Index Register (X) (8)6.4 8-bit Program Stack Pointer (PSP) (8)6.5 8-bit Data Stack Pointer (DSP) (9)6.6 Address Modes (9)6.6.1 Data (9)6.6.2 Direct (9)6.6.3 Indexed (9)7.0 INSTRUCTION SET SUMMARY (10)8.0 MEMORY ORGANIZATION (11)8.1 Program Memory Organization (11)8.2 Data Memory Organization (12)8.3 I/O Register Summary (13)9.0 CLOCKING (14)9.1 Internal/External Oscillator Operation (15)9.2 External Oscillator (16)10.0 RESET (16)10.1 Low-voltage Reset (LVR) (16)10.2 Brown Out Reset (BOR) (16)10.3 Watchdog Reset (WDR) (17)11.0 SUSPEND MODE (17)11.1 Clocking Mode on Wake-up from Suspend (18)11.2 Wake-up Timer (18)12.0 GENERAL PURPOSE I/O PORTS (18)12.1 Auxiliary Input Port (21)13.0 USB SERIAL INTERFACE ENGINE (SIE) (22)13.1 USB Enumeration (22)13.2 USB Port Status and Control (22)14.0 USB DEVICE (24)14.1 USB Address Register (24)14.2 USB Control Endpoint (24)14.3 USB Non-control Endpoints (25)14.4 USB Endpoint Counter Registers (26)15.0 USB REGULATOR OUTPUT (27)16.0 PS/2 OPERATION (27)17.0 SERIAL PERIPHERAL INTERFACE (SPI) (28)17.1 Operation as an SPI Master (29)17.2 Master SCK Selection (29)17.3 Operation as an SPI Slave (29)17.4 SPI Status and Control (30)17.5 SPI Interrupt (31)17.6 SPI Modes for GPIO Pins (31)18.0 12-BIT FREE-RUNNING TIMER (31)19.0 TIMER CAPTURE REGISTERS (32)20.0 PROCESSOR STATUS AND CONTROL REGISTER (35)21.0 INTERRUPTS (36)21.1 Interrupt Vectors (37)21.2 Interrupt Latency (37)21.3 Interrupt Sources (37)22.0 USB MODE TABLES (42)23.0 REGISTER SUMMARY (47)24.0 ABSOLUTE MAXIMUM RATINGS (48)25.0 DC CHARACTERISTICS (48)26.0 SWITCHING CHARACTERISTICS (50)27.0 ORDERING INFORMATION (55)28.0 PACKAGE DIAGRAMS (55)LIST OF FIGURESFigure 8-1. Program Memory Space with Interrupt Vector Table (11)Figure 8-2. Data Memory Organization (12)Figure 9-1. Clock Oscillator On-chip Circuit (14)Figure 9-2. Clock Configuration Register (Address 0xF8) (14)Figure 10-1. Watchdog Reset (WDR, Address 0x26) (17)Figure 12-1. Block Diagram of GPIO Port (one pin shown) (19)Figure 12-2. Port 0 Data (Address 0x00) (19)Figure 12-3. Port 1 Data (Address 0x01) (19)Figure 12-4. GPIO Port 0 Mode0 Register (Address 0x0A) (20)Figure 12-5. GPIO Port 0 Mode1 Register (Address 0x0B) (20)Figure 12-6. GPIO Port 1 Mode0 Register (Address 0x0C) (20)Figure 12-7. GPIO Port 1 Mode1 Register (Address 0x0D) (20)Figure 12-8. Port 2 Data Register (Address 0x02) (21)Figure 13-1. USB Status and Control Register (Address 0x1F) (23)Figure 14-1. USB Device Address Register (Address 0x10) (24)Figure 14-2. Endpoint 0 Mode Register (Address 0x12) (25)Figure 14-3. USB Endpoint EP1, EP2 Mode Registers (Addresses 0x14 and 0x16) (26)Figure 14-4. Endpoint 0,1,2 Counter Registers (Addresses 0x11, 0x13 and 0x15) (26)Figure 17-1. SPI Block Diagram (28)Figure 16-1. Diagram of USB-PS/2 System Connections (28)Figure 17-2. SPI Data Register (Address 0x60) (29)Figure 17-3. SPI Control Register (Address 0x61) (30)Figure 17-4. SPI Data Timing (31)Figure 18-1. Timer LSB Register (Address 0x24) (31)Figure 18-2. Timer MSB Register (Address 0x25) (32)Figure 18-3. Timer Block Diagram (32)Figure 19-1. Capture Timers Block Diagram (33)Figure 19-2. Capture Timer A-Rising, Data Register (Address 0x40) (33)Figure 19-3. Capture Timer A-Falling, Data Register (Address 0x41) (34)Figure 19-4. Capture Timer B-Rising, Data Register (Address 0x42) (34)Figure 19-5. Capture Timer B-Falling, Data Register (Address 0x43) (34)Figure 19-6. Capture Timer Status Register (Address 0x45) (34)Figure 19-7. Capture Timer Configuration Register (Address 0x44) (34)Figure 20-1. Processor Status and Control Register (Address 0xFF) (35)Figure 21-1. Global Interrupt Enable Register (Address 0x20) (38)Figure 21-2. Endpoint Interrupt Enable Register (Address 0x21) (39)Figure 21-3. Interrupt Controller Logic Block Diagram (40)Figure 21-4. Port 0 Interrupt Enable Register (Address 0x04) (40)Figure 21-5. Port 1 Interrupt Enable Register (Address 0x05) (40)Figure 21-6. Port 0 Interrupt Polarity Register (Address 0x06) (41)Figure 21-7. Port 1 Interrupt Polarity Register (Address 0x07) (41)Figure 21-8. GPIO Interrupt Diagram (41)Figure 26-1. Clock Timing (51)Figure 26-2. USB Data Signal Timing (51)Figure 26-3. Receiver Jitter Tolerance (52)Figure 26-4. Differential to EOP Transition Skew and EOP Width (52)Figure 26-5. Differential Data Jitter (52)Figure 26-7. SPI Slave Timing, CPHA = 0 (53)Figure 26-6. SPI Master Timing, CPHA = 0 (53)Figure 26-8. SPI Master Timing, CPHA = 1 (54)Figure 26-9. SPI Slave Timing, CPHA = 1 (54)LIST OF TABLESTable 8-1. I/O Register Summary (13)Table 11-1. Wake-up Timer Adjust Settings (18)Table 12-1. Ports 0 and 1 Output Control Truth Table (21)Table 13-1. Control Modes to Force D+/D– Outputs (24)Table 17-1. SPI Pin Assignments (31)Table 19-1. Capture Timer Prescalar Settings (Step size and range for FCLK = 6 MHz) (35)Table 21-1. Interrupt Vector Assignments (37)Table 22-1. USB Register Mode Encoding for Control and Non-Control Endpoints (42)Table 22-2. Decode table for Table 22-3: “Details of Modes for Differing Traffic Conditions” (44)Table 22-3. Details of Modes for Differing Traffic Conditions (45)Table 28-1. CY7C63722-XC Probe Pad Coordinates in microns ((0,0) to bond pad centers) (57)1.0 Features•enCoRe™ USB - enhanced Component Reduction—Internal oscillator eliminates the need for an external crystal or resonator—Interface can auto-configure to operate as PS/2 or USB without the need for external components to switch between modes (no GPIO pins needed to manage dual mode capability)—Internal 3.3V regulator for USB pull-up resistor—Configurable GPIO for real-world interface without external components•Flexible, cost-effective solution for applications that combine PS/2 and low-speed USB, such as mice, gamepads, joysticks, and many others.•USB Specification Compliance—Conforms to USB Specification, Version 2.0—Conforms to USB HID Specification, Version 1.1—Supports 1 Low-Speed USB device address and 3 data endpoints—Integrated USB transceiver—3.3V regulated output for USB pull-up resistor•8-bit RISC microcontroller—Harvard architecture—6-MHz external ceramic resonator or internal clock mode—12-MHz internal CPU clock—Internal memory—256 bytes of RAM—8 Kbytes of EPROM—Interface can auto-configure to operate as PS/2 or USB—No external components for switching between PS/2 and USB modes—No GPIO pins needed to manage dual mode capability•I/O ports—Up to 16 versatile General Purpose I/O (GPIO) pins, individually configurable—High current drive on any GPIO pin: 50 mA/pin current sink—Each GPIO pin supports high-impedance inputs, internal pull-ups, open drain outputs or traditional CMOS outputs —Maskable interrupts on all I/O pins•SPI serial communication block—Master or slave operation—2 Mbit/s transfers•Four 8-bit Input Capture registers—Two registers each for two input pins—Capture timer setting with 5 prescaler settings—Separate registers for rising and falling edge capture—Simplifies interface to RF inputs for wireless applications•Internal low-power wake-up timer during suspend mode—Periodic wake-up with no external components•Optional 6-MHz internal oscillator mode—Allows fast start-up from suspend mode•Watchdog Reset (WDR)•Low-voltage Reset at 3.75V•Internal brown-out reset for suspend mode•Improved output drivers to reduce EMI•Operating voltage from 4.0V to 5.5VDC•Operating temperature from 0 to 70 degrees Celsius•CY7C63723 available in 18-pin SOIC, 18-pin PDIP•CY7C63743 available in 24-pin SOIC, 24-pin PDIP•CY7C63722 available in DIE form•Industry standard programmer support2.0 Functional Overview2.1enCoRe USB - The New USB StandardCypress has re-invented its leadership position in the low-speed USB market with a new family of innovative microcontrollers. Introducing...enCoRe USB—“enhanced Component Reduction.” Cypress has leveraged its design expertise in USB solutions to create a new family of low-speed USB microcontrollers that enables peripheral developers to design new products with a minimum number of components. At the heart of the enCoRe USB technology is the breakthrough design of a crystal-less oscillator. By integrating the oscillator into our chip, an external crystal or resonator is no longer needed. We have also integrated other external components commonly found in low-speed USB applications such as pull-up resistors, wake-up circuitry, and a 3.3V regulator. All of this adds up to a lower system cost.The CY7C637xx is an 8-bit RISC One Time Programmable (OTP) microcontroller. The instruction set has been optimized specif-ically for USB and PS/2 operations, although the microcontrollers can be used for a variety of other embedded applications. The CY7C637xx features up to 16 general purpose I/O (GPIO) pins to support USB, PS/2 and other applications. The I/O pins are grouped into two ports (Port 0 to 1) where each pin can be individually configured as inputs with internal pull-ups, open drain outputs, or traditional CMOS outputs with programmable drive strength of up to 50 mA output drive. Additionally, each I/O pin can be used to generate a GPIO interrupt to the microcontroller. Note the GPIO interrupts all share the same “GPIO” interrupt vector. The CY7C637xx microcontrollers feature an internal oscillator. With the presence of USB traffic, the internal oscillator can be set to precisely tune to USB timing requirements (6 MHz ±1.5%). Optionally, an external 6-MHz ceramic resonator can be used to provide a higher precision reference for USB operation. This clock generator reduces the clock-related noise emissions (EMI). The clock generator provides the 6- and 12-MHz clocks that remain internal to the microcontroller.The CY7C637xx has 8 Kbytes of EPROM and 256 bytes of data RAM for stack space, user variables, and USB FIFOs.These parts include low-voltage reset logic, a watchdog timer, a vectored interrupt controller, a 12-bit free-running timer, and capture timers. The low-voltage reset (LVR) logic detects when power is applied to the device, resets the logic to a known state, and begins executing instructions at EPROM address 0x0000. LVR will also reset the part when V CC drops below the operating voltage range. The watchdog timer can be used to ensure the firmware never gets stalled for more than approximately 8 ms. The microcontroller supports 10 maskable interrupts in the vectored interrupt controller. Interrupt sources include the USB Bus-Reset, the 128-µs and 1.024-ms outputs from the free-running timer, three USB endpoints, two capture timers, an internal wake-up timer and the GPIO ports. The timers bits cause periodic interrupts when enabled. The USB endpoints interrupt after USB transactions complete on the bus. The capture timers interrupt whenever a new timer value is saved due to a selected GPIO edge event. The GPIO ports have a level of masking to select which GPIO inputs can cause a GPIO interrupt. For additional flexibility, the input transition polarity that causes an interrupt is programmable for each GPIO pin. The interrupt polarity can be either rising or falling edge.The free-running 12-bit timer clocked at 1 MHz provides two interrupt sources as noted above (128 µs and 1.024 ms). The timer can be used to measure the duration of an event under firmware control by reading the timer at the start and end of an event, and subtracting the two values. The four capture timers save a programmable 8 bit range of the free-running timer when a GPIO edge occurs on the two capture pins (P0.0, P0.1).The CY7C637xx includes an integrated USB serial interface engine (SIE) that supports the integrated peripherals. The hardware supports one USB device address with three endpoints. The SIE allows the USB host to communicate with the function integrated into the microcontroller. A 3.3V regulated output pin provides a pull-up source for the external USB resistor on the D– pin.The USB D+ and D– USB pins can alternately be used as PS/2 SCLK and SDATA signals, so that products can be designed to respond to either USB or PS/2 modes of operation. PS/2 operation is supported with internal pull-up resistors on SCLK and SDATA, the ability to disable the regulator output pin, and an interrupt to signal the start of PS/2 activity. No external components are necessary for dual USB and PS/2 systems, and no GPIO pins need to be dedicated to switching between modes. Slow edge rates operate in both modes to reduce EMI.3.0 Logic Block Diagram4.0 Pin Configurations5.0 Pin AssignmentsNameI/O CY7C63723CY7C63743CY7C63722Description18-Pin 24-Pin 25-Pad D–/SDATA,D+/SCLK I/O 121315161617USB differential data lines (D– and D+), or PS/2 clock and data signals (SDATA and SCLK)P0[7:0]I/O1, 2, 3, 4,15, 16, 17, 181, 2, 3, 4,21, 22, 23, 241, 2, 3, 4,22, 23, 24, 25GPIO Port 0 capable of sinking up to 50 mA/pin, or sinking controlled low or high programmable current.Can also source 2 mA current, provide a resistive pull-up, or serve as a high-impedance input. P0.0 and P0.1 provide inputs to Capture Timers A and B, respec-tively.P1[7:0]I/O5, 145, 6, 7, 8,17, 18, 19, 205, 6, 7, 8,18, 19, 20, 21IO Port 1 capable of sinking up to 50 mA/pin, or sinking controlled low or high programmable current. Can alsosource 2 mA current, provide a resistive pull-up, or serve as a high-impedance input.Wake-Up 12-bit Timer USB &D+,D–P1.0–P1.7Interrupt ControllerPort 0P0.0–P0.7GPIO8-bit RISC Xtal RAM 256 Byte EPROM 8K ByteCoreBrown-out Reset XcvrWatch Timer Dog 3.3V Port 1GPIO Capture TimersUSB Engine PS/2Internal Oscillator Oscillator Low ResetVoltage RegulatorTimerSPIXTALOUTXTALIN/P2.1VREG/P2.01234569111516171819202221P0.0P0.1P0.2P0.3P1.0P1.2VSS VREG/P2.0P0.6P1.5P1.1P1.3D+/SCLK P1.7D–/SDATA VCC14P0.710VPPXTALIN/P2.1XTALOUT121378P1.4P1.62423P0.4P0.524-pin SOIC/PDIPCY7C6374312346781011121315161817P0.0P0.1P0.2P0.3VSS VREG/P2.0P0.4P0.6P0.7D+/SCLK D–/SDATA VCC18-pin SOIC/PDIPP0.59VPPXTALIN/P2.1XTALOUTCY7C63723514P1.0P1.1Top View4 5 6 7 8 93 P 0.21 P 0.0 2 P 0.125 P 0.4 24 P 0.523 P 0.622 21 20 19 1811121314151617P0.3P1.0P1.2P1.4P1.6 VSS VSS V P P X T A L I N /P 2.1V R E G X T A L O U T V C C D -/S D A T A D+/SCLK P0.7P1.1P1.3P1.5P1.7CY7C63722-XCDIE106.0 Programming ModelRefer to the CYASM Assembler User’s Guide for more details on firmware operation with the CY7C637xx microcontrollers.6.1Program Counter (PC)The 14-bit program counter (PC) allows access for up to 8 Kbytes of EPROM using the CY7C637xx architecture. The program counter is cleared during reset, such that the first instruction executed after a reset is at address 0x0000. This instruction is typically a jump instruction to a reset handler that initializes the application.The lower 8 bits of the program counter are incremented as instructions are loaded and executed. The upper 6 bits of the program counter are incremented by executing an XPAGE instruction. As a result, the last instruction executed within a 256-byte “page”of sequential code should be an XPAGE instruction. The assembler directive “XPAGEON” will cause the assembler to insert XPAGE instructions automatically. As instructions can be either one or two bytes long, the assembler may occasionally need to insert a NOP followed by an XPAGE for correct execution.The program counter of the next instruction to be executed, carry flag, and zero flag are saved as two bytes on the program stack during an interrupt acknowledge or a CALL instruction. The program counter, carry flag, and zero flag are restored from the program stack only during a RETI instruction.Please note the program counter cannot be accessed directly by the firmware. The program stack can be examined by reading SRAM from location 0x00 and up.6.28-bit Accumulator (A)The accumulator is the general-purpose, do everything register in the architecture where results are usually calculated.6.38-bit Index Register (X)The index register “X” is available to the firmware as an auxiliary accumulator. The X register also allows the processor to perform indexed operations by loading an index value into X.6.48-bit Program Stack Pointer (PSP)During a reset, the program stack pointer (PSP) is set to zero. This means the program “stack” starts at RAM address 0x00 and “grows” upward from there. Note that the program stack pointer is directly addressable under firmware control, using the MOV PSP ,A instruction. The PSP supports interrupt service under hardware control and CALL, RET, and RETI instructions under firmware control.During an interrupt acknowledge, interrupts are disabled and the program counter, carry flag, and zero flag are written as two bytes of data memory. The first byte is stored in the memory addressed by the program stack pointer, then the PSP is incremented.The second byte is stored in memory addressed by the program stack pointer and the PSP is incremented again. The net effect is to store the program counter and flags on the program “stack” and increment the program stack pointer by two.The return from interrupt (RETI) instruction decrements the program stack pointer, then restores the second byte from memory addressed by the PSP . The program stack pointer is decremented again and the first byte is restored from memory addressed by the PSP . After the program counter and flags have been restored from stack, the interrupts are enabled. The effect is to restore the program counter and flags from the program stack, decrement the program stack pointer by two, and re-enable interrupts.The call subroutine (CALL) instruction stores the program counter and flags on the program stack and increments the PSP by two.XTALIN/P2.1IN 912136-MHz ceramic resonator or external clock input, or P2.1 inputXTALOUT OUT1013146-MHz ceramic resonator return pin or internal oscillator outputV PP 71011Programming voltage supply, ground for normal operation V CC111415Voltage supplyVREG/P2.0 81112Voltage supply for 1.3-k Ω USB pull-up resistor (3.3V nominal). Also serves as P2.0 input.V SS699, 10Ground5.0 Pin Assignments (continued)NameI/O CY7C63723CY7C63743CY7C63722Description18-Pin 24-Pin 25-PadThe return from subroutine (RET) instruction restores the program counter, but not the flags, from program stack and decrements the PSP by two.Note that there are restrictions in using the JMP, CALL, and INDEX instructions across the 4-KB boundary of the program memory. Refer to the CYASM Assembler User’s Guide for a detailed description.6.58-bit Data Stack Pointer (DSP)The data stack pointer (DSP) supports PUSH and POP instructions that use the data stack for temporary storage. A PUSH instruction will pre-decrement the DSP, then write data to the memory location addressed by the DSP. A POP instruction will read data from the memory location addressed by the DSP, then post-increment the DSP.During a reset, the Data Stack Pointer will be set to zero. A PUSH instruction when DSP equals zero will write data at the top of the data RAM (address 0xFF). This would write data to the memory area reserved for a FIFO for USB endpoint 0. In non-USB applications, this works fine and is not a problem.For USB applications, the firmware should set the DSP to an appropriate location to avoid a memory conflict with RAM dedicated to USB FIFOs. The memory requirements for the USB endpoints are shown in Section 8.2. For example, assembly instructions to set the DSP to 20h (giving 32 bytes for program and data stack combined) are shown below:MOV A,20h; Move 20 hex into Accumulator (must be D8h or less to avoid USB FIFOs)SWAP A,DSP; swap accumulator value into DSP register6.6Address ModesThe CY7C637xx microcontrollers support three addressing modes for instructions that require data operands: data, direct, and indexed.6.6.1DataThe “Data” address mode refers to a data operand that is actually a constant encoded in the instruction. As an example, consider the instruction that loads A with the constant 0x30:•MOV A, 30hThis instruction will require two bytes of code where the first byte identifies the “MOV A” instruction with a data operand as the second byte. The second byte of the instruction will be the constant “0xE8h”. A constant may be referred to by name if a prior “EQU” statement assigns the constant value to the name. For example, the following code is equivalent to the example shown above:•DSPINIT: EQU 30h•MOV A,DSPINIT6.6.2Direct“Direct” address mode is used when the data operand is a variable stored in SRAM. In that case, the one byte address of the variable is encoded in the instruction. As an example, consider an instruction that loads A with the contents of memory address location 0x10h:•MOV A, [10h]In normal usage, variable names are assigned to variable addresses using “EQU” statements to improve the readability of the assembler source code. As an example, the following code is equivalent to the example shown above:•buttons: EQU 10h•MOV A,[buttons]6.6.3Indexed“Indexed” address mode allows the firmware to manipulate arrays of data stored in SRAM. The address of the data operand is the sum of a constant encoded in the instruction and the contents of the “X” register. In normal usage, the constant will be the “base” address of an array of data and the X register will contain an index that indicates which element of the array is actually addressed:•array: EQU 10h•MOV X,3•MOV A,[x+array]This would have the effect of loading A with the fourth element of the SRAM “array” that begins at address 0x10h. The fourth element would be at address 0x13h.7.0 Instruction Set SummaryRefer to the CYASM Assembler User’s Guide for detailed information on these instructions. Note that conditional jump instructions (i.e., JC, JNC, JZ, JNZ) take 5 cycles if jump is taken, 4 cycles if no jump.MNEMONIC Operand Opcode Cycles MNEMONIC Operand Opcode Cycles HALT 007NOP 204ADD A,expr data014INC A acc214ADD A,[expr] direct026INC X x224ADD A,[X+expr] index037INC [expr] direct237ADC A,expr data044INC [X+expr] index248ADC A,[expr] direct056DEC A acc254ADC A,[X+expr] index067DEC X x264SUB A,expr data074DEC [expr] direct277SUB A,[expr] direct086DEC [X+expr] index288SUB A,[X+expr] index097IORD expr address295SBB A,expr data0A4IOWR expr address2A5SBB A,[expr] direct0B6POP A2B4SBB A,[X+expr] index0C7POP X2C4OR A,expr data0D4PUSH A2D5OR A,[expr] direct0E6PUSH X2E5OR A,[X+expr] index0F7SWAP A,X2F5AND A,expr data104SWAP A,DSP305AND A,[expr] direct116MOV [expr],A direct315AND A,[X+expr] index127MOV [X+expr],A index326XOR A,expr data134OR [expr],A direct337XOR A,[expr] direct146OR [X+expr],A index348XOR A,[X+expr] index157AND [expr],A direct357CMP A,expr data165AND [X+expr],A index368CMP A,[expr] direct177XOR [expr],A direct377CMP A,[X+expr] index188XOR [X+expr],A index388MOV A,expr data194IOWX [X+expr] index396MOV A,[expr] direct1A5CPL 3A4MOV A,[X+expr] index1B6ASL 3B4MOV X,expr data1C4ASR 3C4MOV X,[expr] direct1D5RLC 3D4reserved 1E RRC 3E4XPAGE 1F4RET 3F8MOV A,X404DI 704MOV X,A414EI 724MOV PSP,A604RETI 738CALL addr50 - 5F10JMP addr80-8F5JC addr C0-CF 5 (or 4) CALL addr90-9F10JNC addr D0-DF 5 (or 4)JZ addr A0-AF 5 (or 4)JACC addr E0-EF7JNZ addr B0-BF 5 (or 4)INDEX addr F0-FF148.0 Memory Organization8.1Program Memory Organization[1]After reset Address14 -bit PC0x0000Program execution begins here after a reset.0x0002USB Bus Reset interrupt vector0x0004128-µs timer interrupt vector0x0006 1.024-ms timer interrupt vector0x0008USB endpoint 0 interrupt vector0x000A USB endpoint 1 interrupt vector0x000C USB endpoint 2 interrupt vector0x000E SPI interrupt vector0x0010Capture timer A interrupt Vector0x0012Capture timer B interrupt vector0x0014GPIO interrupt vector0x0016Wake-up interrupt vector0x0018Program Memory begins here0x1FDF8 KB PROM ends here (8K - 32 bytes). See Note below Figure 8-1. Program Memory Space with Interrupt Vector TableNote:1.The upper 32 bytes of the 8K PROM are reserved. Therefore, the user’s program must not overwrite this space.8.2Data Memory OrganizationThe CY7C637xx microcontrollers provide 256 bytes of data RAM. In normal usage, the SRAM is partitioned into four areas: program stack, data stack, user variables and USB endpoint FIFOs as shown below:After reset Address8-bit DSP8-bit PSP0x00Program Stack Growth(User’s firmware movesDSP)8-bit DSP User Selected Data Stack GrowthUser Variables0xE8USB FIFO for Address A endpoint 20xF0USB FIFO for Address A endpoint 10xF8USB FIFO for Address A endpoint 0Top of RAM Memory0xFFFigure 8-2. Data Memory Organization8.3I/O Register SummaryI/O registers are accessed via the I/O Read (IORD) and I/O Write (IOWR, IOWX) instructions. IORD reads the selected port into the accumulator. IOWR writes data from the accumulator to the selected port. Indexed I/O Write (IOWX) adds the contents of X to the address in the instruction to form the port address and writes data from the accumulator to the specified port. Note that specifying address 0 with IOWX (e.g., IOWX 0h) means the I/O port is selected solely by the contents of X.Note:All bits of all registers are cleared to all zeros on reset, except the Processor Status and Control Register (Figure20-1). All registers not listed are reserved, and should never be written by firmware. All bits marked as reserved should always be written as 0 and be treated as undefined by reads.Table 8-1. I/O Register SummaryRegister Name I/O Address Read/Write Function Fig. Port 0 Data0x00R/W GPIO Port 012-2 Port 1 Data0x01R/W GPIO Port 112-3 Port 2 Data0x02R Auxiliary input register for D+, D–, VREG, XTALIN 12-8 Port 0 Interrupt Enable0x04W Interrupt enable for pins in Port 021-4 Port 1 Interrupt Enable0x05W Interrupt enable for pins in Port 121-5 Port 0 Interrupt Polarity 0x06W Interrupt polarity for pins in Port 021-6 Port 1 Interrupt Polarity 0x07W Interrupt polarity for pins in Port 121-7 Port 0 Mode0 0x0A W Controls output configuration for Port 012-4 Port 0 Mode10x0B W12-5 Port 1 Mode00x0C W Controls output configuration for Port 112-6 Port 1 Mode10x0D W12-7 USB Device Address0x10R/W USB Device Address register14-1 EP0 Counter Register0x11R/W USB Endpoint 0 counter register14-4 EP0 Mode Register0x12R/W USB Endpoint 0 configuration register14-2 EP1 Counter Register0x13R/W USB Endpoint 1 counter register14-4 EP1 Mode Register0x14R/W USB Endpoint 1 configuration register14-3 EP2 Counter Register0x15R/W USB Endpoint 2 counter register14-4 EP2 Mode Register0x16R/W USB Endpoint 2 configuration register14-3 USB Status & Control0x1F R/W USB status and control register13-1 Global Interrupt Enable0x20R/W Global interrupt enable register21-1 Endpoint Interrupt Enable0x21R/W USB endpoint interrupt enables21-2 Timer (LSB)0x24R Lower 8 bits of free-running timer (1 MHz)18-1 Timer (MSB)0x25R Upper 4 bits of free-running timer18-2 WDR Clear0x26W Watchdog Reset clear-Capture Timer A Rising0x40R Rising edge Capture Timer A data register19-2 Capture Timer A Falling0x41R Falling edge Capture Timer A data register19-3 Capture Timer B Rising0x42R Rising edge Capture Timer B data register19-4 Capture Timer B Falling0x43R Falling edge Capture Timer B data register19-5 Capture TImer Configuration0x44R/W Capture Timer configuration register19-7 Capture Timer Status0x45R Capture Timer status register19-6 SPI Data0x60R/W SPI read and write data register17-2 SPI Control0x61R/W SPI status and control register17-3 Clock Configuration0xF8R/W Internal / External Clock configuration register9-2 Processor Status & Control0xFF R/W Processor status and control20-1。

AC1350中文资料

ADI Home > Market Solutions > IOS Subsystems > 3B SeriesCurrent Conversion ResistorThe Model AC1342 100 ohms, 0.1%, 1/4 watt, 20 ppm/°C resistor is supplied with each 3B32 current input module to convert input current to a voltage; an additional AC1342 can be optionally ordered as a spare.AC1342Order Now ModelAC1342back to topInterface Board for Analog I/OThe Model AC1324 optional universal interface board includes a 26-pin I/O connector and 26 I/O screw terminals. The 26-pin connector accepts the AC1315 or CAB-01 cables from a 3B Series Model 3B01, 3B02 or 3B03 backplane and provides 26 screw terminals for interconnecting to any analog I/O subsystem, such as a programmable controller. It can be mounted either at the back of the AC1330 rack-mount kit (standoffs are included and should be used) or in a snap track.AC1324Order Now ModelAC1324back to topPower Supply JumpersThe optional Model AC1344 spare set of 10 jumpers can be used on the 3B01, 3B02 and 3B03 backplanes to configure the W1, W2, W3 and W4 power supply and grounding options. W1 and W3 force Pin 25 to power supply common; W2 provides external voltage sensing to enable the 3B Series Subsystem, with Analog Devices' RTI boards, to increase noise rejection by measuring in pseudo-differential mode.W4 ties the ±15 V DC power supply common to the +24 V DC power supply common, required when a +24 V DC power supply is used.AC1344Order Now ModelAC1344back to topKits for User-Designed ModulesThe optional Model AC1350 kit contains an individual blank case, connectors and PC vector board to enable the construction of a user-designed 3B-type module. The Model AC1351 kit includes only a case and connectors.AC1350Order Now Model AC1350AC1351Order Now Model AC1351back to topMounting Kits - Rack-MountThe optional Model AC1330 is a two-piece metal optional mounting to enable Models 3B01, 3B02 or 3B03 backplanes to be fitted into a 19-inch rack, requiring a 19-inch x 4.7-inch area. The bottom plate has threaded inserts for mounting any of the three backplanes using four screws that are shipped with each backplane. The AC1330 top piece provides a rigid module hold-down and is secured to the bottom piece with two quarter-turn fasteners.AC1330Order Now ModelAC1330back to topMounting Kits - Surface-MountThe Models AC1331, AC1332 and AC1333 optional surface-mount kits enable any of the backplanes, Models 3B01, 3B02 or 3B03, respectively, to be easily mounted in a panel or NEMA enclosure.AC1331 Order Now ModelAC1331AC1332Order Now Model AC1332AC1333Order Now ModelAC1333back to topPower Supplies and Power CordsThe 3B Series Subsystem requires either an optional AC/DC power supply or an optional DC/DC converter mounted on the backplane. External ±15 V DC and +24 V DC power supplies can also be used.The Models AC1300 and AC1301 plug-in, modular, encapsulated AC/DC, regulated, ±15 V DC power supplies can be directly mounted on the 3B Series backplanes, with the supplied retainer clip and hardware. This mounting features the ability for each power supply to be asily removed from the backplane.The Model AC1302 plug-in modular DC/DC converter, accepts a+24 V DC input and provides a regulated ±15 V DC output to enable an external +24 V current loop source to supply all power to the backplane, such as in a factory data collection environment. The external +24 V DC supply must be capable of handling the desired number of current loop outputs as well as powering the AC1302.AC1300Order Now Model AC1300AC1301Order Now Model AC1301AC1302Order Now Model AC1302。

CC1350 LaunchPad 无线微控制器开发板快速原型说明书

CC1350 LaunchPad™// wireless microcontroller development kit for rapid prototyping. LAUNCHXL-CC1350LAUNCHYOUR DESIGNSTART @/launchxl-cc1350CC1350 LaunchPad// wireless microcontroller development kit for rapid prototyping.LAUNCHXL-CC1350Launch Your Design @ /launchxl-cc1350The platform bar, MSP430, SimpleLink and LaunchPad are trademarks of Texas Instruments. © 2018 Texas Instruments Incorporated. SWRU478bIMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCESTexas Instruments Incorporated(‘TI”)technical,application or other design advice,services or information,including,but not limited to, reference designs and materials relating to evaluation modules,(collectively,“TI Resources”)are intended to assist designers who are developing applications that incorporate TI products;by downloading,accessing or using any particular TI Resource in any way,you (individually or,if you are acting on behalf of a company,your company)agree to use it solely for this purpose and subject to the terms of this Notice.TI’s provision of TI Resources does not expand or otherwise alter TI’s applicable published warranties or warranty disclaimers for TI products,and no additional obligations or liabilities arise from TI providing such TI Resources.TI reserves the right to make corrections, enhancements,improvements and other changes to its TI Resources.You understand and agree that you remain responsible for using your independent analysis,evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications)with all applicable regulations,laws and other applicable requirements.You represent that,with respect to your applications,you have all the necessary expertise to create and implement safeguards that(1) anticipate dangerous consequences of failures,(2)monitor failures and their consequences,and(3)lessen the likelihood of failures that might cause harm and take appropriate actions.You agree that prior to using or distributing any applications that include TI products,you will thoroughly test such applications and the functionality of such TI products as used in such applications.TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.You are authorized to use,copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s)identified in such TI Resource.NO OTHER LICENSE,EXPRESS OR IMPLIED,BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT,AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN,including but not limited to any patent right,copyright,mask work right,or other intellectual property right relating to any combination,machine,or process in which TI products or services are rmation regarding or referencing third-party products or services does not constitute a license to use such products or services,or a warranty or endorsement e of TI Resources may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.TI RESOURCES ARE PROVIDED“AS IS”AND WITH ALL FAULTS.TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS,EXPRESS OR IMPLIED,REGARDING TI RESOURCES OR USE THEREOF,INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS,TITLE,ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY,FITNESS FOR A PARTICULAR PURPOSE,AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM,INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE.IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL,DIRECT,SPECIAL, COLLATERAL,INDIRECT,PUNITIVE,INCIDENTAL,CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF,AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.You agree to fully indemnify TI and its representatives against any damages,costs,losses,and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.This Notice applies to TI Resources.Additional terms apply to the use and purchase of certain types of materials,TI products and services. These include;without limitation,TI’s standard terms for semiconductor products /sc/docs/stdterms.htm),evaluation modules,and samples(/sc/docs/sampterms.htm).Mailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2018,Texas Instruments Incorporated。

CY7C131中文资料