采用_2_1_7_卷积码_QPSK的中频调制解调系统的FPGA实现

中频数字化接收及QPSK高速解调的FPGA实现

138电路与系统学报第15卷择m=1,即,.f=80MHz,这样经正交采样零中频化后,数字部分的处理速率为40Mbps,每个信息符号内约有4个采样点,本文所设计的零中频解调算法完全可以达到较好的误码性能。

本文ADC选用AD公司的AD6645(14bit),FPGA选用Aitera公司的StratixII.2s60c4。

采用正交采样技术(.f=80MHz)采集到信号的频谱(使用逻辑分析仪采集ADC采样后的数据存储到PC机并用MATLAB绘制频谱)如图9所示。

由图9可以看出,正交采样后,信号频谱被搬移到.疋/4=20MHz处,再经过基于多相滤波的正交变换,信号将变换为零中频信号进入零中频解调模块进行解调。

基于多相滤波正交变换后的零中频信号频谱如图10所示。

由信号分析仪测得的零中频解调模块解调信号的星座图如图ll所示。

本文设计并实现了一种基于多相滤波的宽带中频正交采样数字零中频接收机以及高速QPSK零中频解调算法,采用了适中的采样速率,即降低了系统采样速率以及数字部分的处理速率,又满足了系统对数据传输速率和低误码的性能要求。

图9正交采样得到的频谱图图lO正交变换后的零中频信号频谱参考文献。

图11零中频解调星座图【1】杨小牛,楼才义,徐建良,著.软件无线电原理与应用【M】.电子工业出版社,2001,1:53・56.【2】2LErup,FMGardner,RAHarris.InterpolationinDigitalModems-Partl:Fundamentals【J】.IEEETrans.OnCommun.,1993,4l(3):501・507【3】FMGardner.ABPSK/QPSKtiming—errordetectorforsampledreceivers[J】.IEEETrans.OnComm・,1986,34(3):423-429.作者简介t赵国栋(1977一),男,博士,・主要从事通信系统设计及通信信号处理研究;徐建良(1969-),男,研究员,主要从事通信与电子对抗研究。

QPSK的调制与解调课程设计

注意事项: a. 信号的相位要保持稳定 b. 接收信号的强度要足够大 c. 解调过程中要避免干扰信号的影响

实验结果分析

实验目的:验证QPSK调制与解调的原理和性能

实验设备:信号源、调制器、解调器、示波器等

实验步骤:设置参数、调制信号、解调信号、观察波形等

实验结果:调制信号的频谱、解调信号的波形、误码率等

03

QPSK信号的生成

信号调制:将信息比特转换为QPSK信号

信号生成:通过I/Q调制器生成QPSK信号

信号频率:QPSK信号的频率为载波频率的4倍

信号相位:QPSK信号的相位有4种可能,对应4种信息比特

QPSK信号的解调

解调原理:利用相位差进行解调

解调方法:采用相位检测器进行解调

解调过程:首先进行相位检测,然后进行信号恢复

QPSK调制与解调在遥感系统中的应用

添加标题

添加标题

添加标题

添加标题

QPSK调制:将遥感数据调制到载波上,提高传输效率

遥感系统:通过卫星、飞机等平台获取地球表面信息

QPSK解调:接收端对载波进行解调,恢复遥感数据

应用优势:抗干扰能力强,传输距离远,数据传输速率高

QPSK调制与解调在其他领域的应用

添加标题

实验过程:包括信号产生、调制、解调、接收等步骤

添加标题

实验不足:在实验过程中遇到了一些困难,如信号干扰、设备故障等

QPSK调制与解调的应用

05

QPSK调制与解调在通信系统中的应用

提高传输速率:QPSK调制可以提高传输速率,满足高速数据传输的需求。

提高抗干扰能力:QPSK调制可以提高系统的抗干扰能力,保证通信质量。

QPSK调制信号的波形

每个相位对应一个比特,0度对应0,180度对应1

采用(2,1,7)卷积码+QPSK的中频调制解调系统的FPGA实现

采用(2,1,7)卷积码+QPSK的中频调制解调系统的FPGA实

现

罗常青;安建平;沈业兵

【期刊名称】《电子技术应用》

【年(卷),期】2005(31)10

【摘要】提出了一个采用(2,1,7)卷积码+QPSK的中频调制解调方案,并在Xilinx 公司的100万门FPGA芯片上实现了该系统.该系统在信噪比SNR为6dB左右时可实现速率超过1Mbit/s、误码率小于10-5的数据传输.

【总页数】3页(P78-80)

【作者】罗常青;安建平;沈业兵

【作者单位】北京理工大学,电子工程系,北京,100081;北京理工大学,电子工程系,北京,100081;北京理工大学,电子工程系,北京,100081

【正文语种】中文

【中图分类】TN4

【相关文献】

1.QPSK调制解调系统设计及FPGA实现 [J], 钟钧波;章坚武;包建荣

2.一种串行结构的2,1,7卷积码维特比译码器的FPGA实现 [J], 黄华柱;刘荣科;王闰昕

3.基于FPGA的全数字低中频QPSK调制解调器实现 [J], 彭飞;赵继勇

4.(2,1,7)卷积码Viterbi译码器FPGA实现方案 [J], 韩可;邓中亮;施乐宁

5.QPSK信号调制解调系统设计与FPGA实现 [J], 马劲松

因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA的软件无线电的宽带中频QPSK调制实现

图1 总体方案图

图2 FPGA内部模块图期

图3 SRRC滤波器具体实现结构图图4 移位寄存器组的结构Z-1

图5 查表和加法模块结构图

图6 FPGA实现DDS的程序结构图

三路,其中两路被作为地址送往两个

ROM,一路反馈到累加器的输入端。

在本系统中累加器必然会发生数

据溢出,当溢出发生后,累加器能否

回到正确的状态重新开始计数,对于

DDS的正常工作是非常重要的。

假设

一个累加器的位数是3,在取步长为

(011)2的情况下,时序图如图7所示。

图8 分频器的内部结构

图10 调制后信号的波形图

由40MHz晶振的二次谐波引起的,

这主要是因为用30MHz和40MHz混

70MHz的混频方案不太合理,两个频图9 FPGA中各功能模块连接图。

卷积编码及Viterbi译码的低时延FPGA设计实现

卷积编码及Viterbi译码的低时延FPGA设计实现张健,吴倩文,高泽峰,周志刚(杭州电子科技大学电子信息学院袁浙江杭州310018)摘要:针对毫米波通信的高速率和低时延设计要求,设计实现1/2码率(2,1,7)卷积码的低时延译码。

采用高度并行优化实现框架、低延时的最小值选择方式,获得Viterbi硬判决译码算法的输出遥利用基于Xilinx公司的Artix7-xc7a200t芯片综合后,译码器的数据输出延时约89个时钟周期,最高工作频率可达203.92MHz遥结果表明,该译码器可支持吉比特级的数据传输速率,实现了低延时、高速率的编译码器遥关键词:毫米波通信;卷积码;Viterbi译码;system generator中图分类号:TN911.22文献标识码:A DOI:10.16157/j.issn.0258-7998.201025中文引用格式:张健袁吴倩文,高泽峰袁等.卷积编码及Viterbi译码的低时延FPGA设计实现[J].电子技术应用,2021,47 (6):96-99.英文弓I用格式:Zhang Jian,Wu Qianwen,Gao Zefeng,et al.Low-latency FPGA design and implementation of convolutional coding and Viterbi decoding[J].Application of Electronic Technique,2021,47(6):96-99.Low-latency FPGA design and implementation of convolutionalcoding and Viterbi decodingZhang Jian,Wu Qianwen,Gao Zefeng,Zhou Zhigang(School of Electronic Information,Hangzhou Dianzi University,Hangzhou310018,China)Abstract:Aiming at the high-speed and low-delay design requirements of millimeter wave communications,this paper designs low-delay decoding of convolutional codes with1/2code rate(2,1,7).A highly parallel optimization implementation framework and a low-latency minimum selection method are adopted to obtain the output of the Viterbi hard decision decoding algorithm.After synthesis using the Artix7-xc7a200t chip based on Xilinx,the data output delay of the decoder is about89clock cycles,and the highest operating frequency can reach203.92MHz.The results show that the decoder can support gigabit-level data transmission rates,and realizes a low-latency,high-rate codec.Key words:millimeter wave communication;convolutional code;Viterbi decoding;system generator0引言近年来,5G移动通信技术的发展受到人们的广泛关注,高速率、高可靠、低时延的高能效通信成为毫米波通信中的重要因素[1-2」。

基于FPGA的QPSK高速数字调制系统的研究与实现

基于FPGA的QPSK高速数字调制系统的研究与实现摘要:介绍了一种基于FPGA的QPSK的高速数字调制系统的实现方案。

先从调制系统的基本框图入手,简要介绍其实现原理及流程;然后着重介绍FPGA功能模块的软件编程、优化及整个系统的性能。

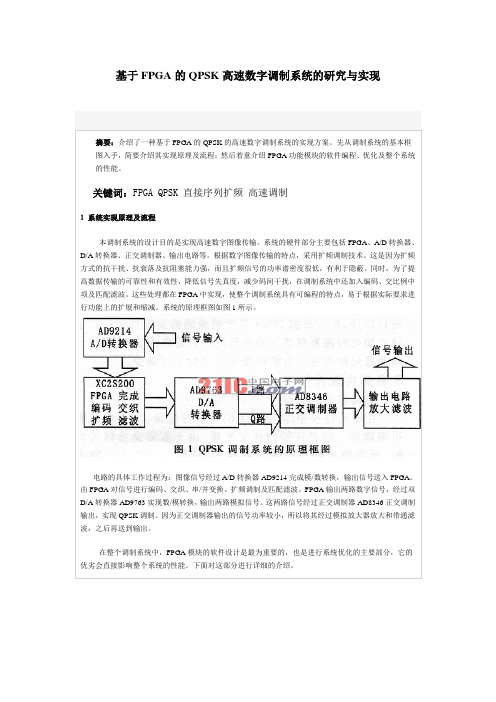

关键词:FPGA QPSK 直接序列扩频高速调制1 系统实现原理及流程本调制系统的设计目的是实现高速数字图像传输。

系统的硬件部分主要包括FPGA、A/D转换器、D/A转换器、正交调制器、输出电路等。

根据数字图像传输的特点,采用扩频调制技术。

这是因为扩频方式的抗干扰、抗衰落及抗阻塞能力强,而且扩频信号的功率谱密度很低,有利于隐蔽。

同时,为了提高数据传输的可靠性和有效性,降低信号失真度,减少码间干扰,在调制系统中还加入编码、交比例中项及匹配滤波。

这些处理都在FPGA中实现,使整个调制系统具有可编程的特点,易于根据实际要求进行功能上的扩展和缩减。

系统的原理框图如图1所示。

电路的具体工作过程为:图像信号经过A/D转换器AD9214完成模/数转换,输出信号送入FPGA。

由FPGA对信号进行编码、交织、串/并变换、扩频调制及匹配滤波。

FPGA输出两路数字信号,经过双D/A转换器AD9763实现数/模转换,输出两路模拟信号。

这两路信号经过正交调制器AD8346正交调制输出,实现QPSK调制。

因为正交调制器输出的信号功率较小,所以将其经过模拟放大器放大和带通滤波,之后再送到输出。

在整个调制系统中,FPGA模块的软件设计是最为重要的,也是进行系统优化的主要部分,它的优劣会直接影响整个系统的性能。

下面对这部分进行详细的介绍。

2 软件部分实现原理FPGA模块的软件设计部分包括以下几个方面:编码、交织、串并变换、扩频、匹配滤波以及复位和时钟。

2.1 编码和交织数字通信中经常使用信道编码加交织模块来提高数据传输的可靠性和有效性。

为了达到一定的增益要求,选择卷积码中纯编码增益为3.01的(1,1,6)码(在大信噪比下),并对其进行增信删余。

QPSK调制解调技术的设计与仿真

摘要本文主要阐述的是QPSK调制与解调电路的设计。

数字调制解调技术在数字通信中占有非常重要的地位。

为了使数字信号在带通信道中传输,必须用数字信号对载波进行调制。

根据所处理的基带信号的进制不同分为二进制和多进制调制(M进制)。

多进制数字调制与二进制相比,其频谱利用率更高,在有限的信道频带内,能够传输高速数据。

数字通信技术与FPGA的结合是现代通信系统发展的一个必然趋势。

多进制数字调制技术与FPGA的结合使得通信系统的性能得到了迅速的提高。

文中介绍了QPSK调制解调的原理,并基于FPGA实现了QPSK调制解调电路。

MUXPLUSⅡ环境下进行编译、综合仿真,验证了设计的正确性。

此外,本方案采用了相位选择法,与常用的调相解调法相比,设计更简单,更适合于FPGA实现,系统的可靠性也更高。

通过对仿真波形的分析可知,该方案很好的实现了QPSK调制与解调功能。

关键词:PSK FPGA QPSK调制解调AbstractThis article mainly deals with the design of QPSK modulation and demodulation circuit. Technology of digital modulation and demodulation plays an important role in digital communication system.In order to transmit digital signal in band-pass channel,digital signal must be used on the carrier modulation..According to the different bands of digital signal that is handled,there are binary and multi-band pared with binary modulation ,multi-band modulation has higher specrum utilization rate,and it could transmit high-speed data in limited-band channel.The combination of digital communication technology and FPGA is a certainly trend of the development of modern communication system.The combination of multi-band modulation and FPGA makes the performance of communication system a rapid increase.The paper introduces the principle of QPSK modulation and demodulation, the circuits are also be realized based on FPGA. The complier and simulation under MAX+PLUSII environment provides the correction of the design..In addition, this design employs phase selection ,compared with the PM demodulation method,phase selection is simpler,more suitable for FPGA implementation,the reliability of the system is higher.The analysis of simulation waveform indicates that the programme achieves QPSK modulation and demodulation functions well.Keywords:PSK FPGA QPSK modulation demodulation目录摘要 (I)ABSTRACT.................................................... I I 前言 (1)1.绪论 (2)1.1QPSK的简介 (2)1.2FPGA和CPLD简介 (2)1.3VHDL简介 (3)1.4MAX+PLUS II简介 (3)2.调制与解调电路的基本设计原理 (4)2.1QPSK调制的电路原理图 (5)2.2QPSK解调的电路原理图 (5)3.QPSK调制与解调电路的设计 (6)3.1调制电路的设计 (6)3.1.1 设计思路 (6)3.1.2 调制电路的程序 (7)3.1.3 调制电路仿真结果 (8)3.2解调电路的设计 (9)3.2.1 设计思路 (9)3.2.2 解调电路的程序 (10)3.2.3 解调电路的仿真结果 (10)3.3仿真分析 (11)3.3.1 BPSK调制解调的实现及其仿真波形 (11)3.3.2 BPSK和QPSK的区别 (16)3.3.3 QPSK仿真波形的分析 (18)4.总结 (20)参考文献 (21)附录 (22)前言现代通信系统要求通信距离远、通信容量大、传输质量好。

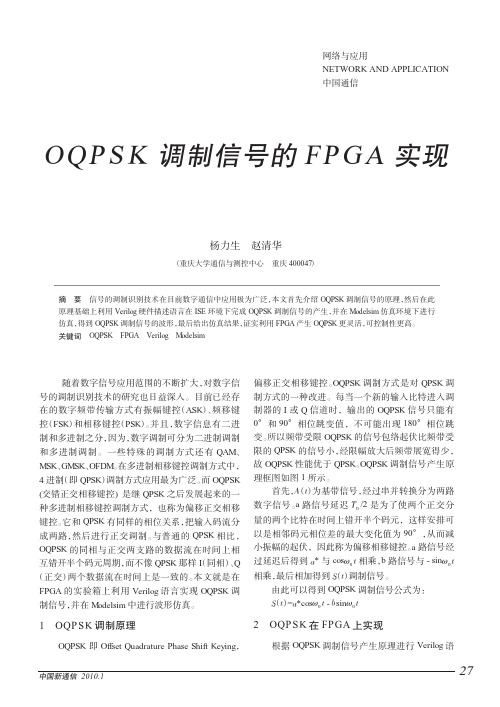

OQPSK调制信号的FPGA实现

相加 S(t) 电路

言编程,需要具体实现三个部分:串并转换电路的实 现、双极性码变换电路的实现以及载波产生电路的 实现。

首先,串并转换电路可以看作将一个序列第一 个码元延迟半个码元周期赋值给 a,第二个码元延迟 半个码元周期赋值给 b,以此类推。其实现 verilog 关 键语句为程序(1)。

always@(posedge clk) begin

首先,A(t)为基带信号,经过串并转换分为两路 数字信号。a 路信号延迟 Tb /2 是为了使两个正交分

量的两个比特在时间上错开半个码元,这样安排可 以是相邻码元相位差的最大变化值为 90°,从而减 小振幅的起伏,因此称为偏移相移键控。a 路信号经 过延迟后得到 a* 与 cosω0 t 相乘,b 路信号与 - sinω0 t

最后,载波电路的实现采用 DDS 原理,通过查

[4]

找表的方法实现正交的两路正弦和余弦信号 。正弦 和余弦信号的产生可以利用 always 语句进行地址累 加,通过 case 语句选择相应地址对应的存储波形数 据。本试验中对一个周期的正弦波形进行 64 个采样 点,8bit 波形数据。

然后按照原理图中的流程,将 a 路信号与余弦 信号相乘,b 路信号同正弦信号相乘,最后将乘得的 两路信号相加,得到 OQPSK 调制信号。

余弦波形,使单路信号和产生的正弦余弦电路相乘, 速数字通信中,利用 FPGA 实现数字信号调制解调

在 Modelsim 中可以得到如图 3 所示仿真波形。

的方法在军事和民用方面都有很高的应用价值,值

可以看出,此时得到的 a 路信号和余弦信号相 得我们再深入细致的研究。

参考文献

[1] 樊昌信,曹丽娜. 通信原理. 北京:国防工业出版社,2007.1 [2] 杨大柱. 基于 FPGA 的 QPSK 调制解调电路设计与实现. 微计算机信息,2007 [3] 高雪平,官伯然,汪海勇. QPSK 调制解调的系统仿真实验. 杭州电子科技大学学报,2006,26(5) [4] 周维龙,姚晓玲. 基于 FPGA 的 QPSK 调制器的设计与实现. 湖南冶金职业技术学院学报,2008,8(4) [5] 刘秀兰,王淑敏. 基于软件无线电的 QPSK 调制的设计. 计算机仿真. 2008,25(11) [6] 金小萍,洪波,钱勤,胡博. 大型全数字 QPSK 调制技术的实验方案设计. 电子工程师,2008,34(4)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《电子技术应用》2005年第10期欢迎网上投稿www.aetnet.cnwww.aetnet.com.cn(接上页)ALU控制模块在译码阶段产生的,在指令执行阶段起始段就输出到数据通道,所以它不在关键路径上)。

对于C31与C30,有C31=C30P31+G31,所以C30⊕C31=C30C31+C30C31=(C27G28G29G30G31+C27P28P29P30P31G31)(1)+(P28G28G29G30G31+G28P29P30P31G31)+P29G29G30G31+P30G30G31+G29P30P31G31+G30P31G31)(2)显然,分式(1)是和进位链无关的一部分,可以在每一个流水线的指令执行阶段起始段很快得到,而分式(2)则是和进位链有关的部分,其具体逻辑值将取决于进位C27的值。

分式(1)中高位的Gi和Pi都可以在进位C27到来之前预先得到,只要C27一到就可以进行逻辑判断,得到相应的逻辑。

所以令P1=G28G29G30G31+C27P28P29P30P31G31P2=P28P29P30P31G31Gtotal=式(2)则Overflow=(C30⊕C31)·Overflag=(C27P1+C27P2+Gtotal)·Overflag(3)②溢出逻辑电路实现根据式(3)的逻辑表达式,可设计出加法器溢出逻辑产生电路,如图7所示。

设计得到的32位加法器在SMIC流片后,经测试,运算速度在400MHz以上,满足设计要求,为后续浮点加法器的设计提供了很好的铺垫。

参考文献1JohnLHennessy.DavidAPatterson.ComputerOrganization&Design———TheHardware/SoftwareInterface(SecondEdition).北京:机械工业出版社,19982JanMRabaey.DigitalIntegratedCircuits.PersonEducationInc.2003,ISBN0-13-0909963Weste.NeILH.E.,K.Eshraghian.PrinciplesofCMOSVLSIDesign.AddisonWeley,19934KorenI.ComputerArithmeticAlgorithms.PrenticeHall,1993(收稿日期2005-03-28)在无线数据传输中,由于信道中的噪声干扰,在接收端会引入一定量的误码率(BitErrorRate,BER)。

高质量的数据业务要求较低的BER。

为了达到较低的BER,经常采用信道编码技术。

卷积编码和Viterbi译码是广泛使用的信道编码技术,具有一定的克服突发错误的能力,可以降低信道的误码率,带来很高的编码增益。

信道编码的引入在提供纠错能力的同时,还扩展了信号的带宽。

为了保证频带的利用率,本文采用QPSK调制方式,使数据调制在中频载波上,实现数据的可靠传输。

本文所述的中频调制解调系统具有以下特点:(1)所有算法(编码、调制、解调和译码)都是在Xilinx公司的FPGA芯片中实现的,结构简单,体积小,功耗低。

(2)具有很好的实时性。

对于1Mbit/s以上的数据速率,译码延迟不超过0.1ms。

(3)模块化的设计使得系统具有一定的兼容性,只需要修改少量程序,即可实现各种卷积编码和不同的调制中频。

(4)与浮点算法的仿真性能相比较,采用定点算法采用(2,1,7)卷积码+QPSK的中频调制解调系统的FPGA实现罗常青,安建平,沈业兵(北京理工大学电子工程系,北京100081)摘要:提出了一个采用(2,1,7)卷积码+QPSK的中频调制解调方案,并在Xilinx公司的100万门FPGA芯片上实现了该系统。

该系统在信噪比SNR为6dB左右时可实现速率超过1Mbit/s、误码率小于10-5的数据传输。

关键词:卷积编码Viterbi译码QPSKFPGA!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!78《电子技术应用》2005年第10期本刊邮箱#eta@ncse.com.cnA/D卷积编码QPSK调制D/A信道A/DQPSK解调Viterbi译码D/A图1中频调制解调系统工作流程图的系统性能损失不大,并能以较低的信噪比提供可靠的数据传输。

1系统总体结构及硬件设计图1是中频调制解调系统的工作流程图。

在发端,数据通过A/D转换器采样后进入FPGA,在其中完成(2,1,7)卷积编码和QPSK调制后通过D/A转换器输出。

在收端,接收到的信号通过A/D转换器采样后进入FPGA,在其中完成QPSK解调和Viterbi译码后通过D/A转换器输出。

2系统的FPGA实现系统主要分为编译码和调制解调两大部分,下面分别叙述这两部分的原理及设计。

2.1卷积编码与Viterbi译码的FPGA实现2.1.1(2,1,7)卷积编码典型的(n,m,k)卷积码编码器是指输入位数为m、输出位数为n、约束长度为k的卷积码编码器,其编码速率为m/n。

一个(2,1,7)的卷积码编码器如图2所示,可用六个移位寄存器实现。

2.1.2Viterbi译码Viterbi译码算法是Viterbi于1967年提出的一种概率译码算法。

其主要思想就是最大似然译码[1]。

译码时,将接收序列与根据编码产生的网格图上面的所有路径进行比较,求出其汉明距离或欧式距离,选出具有最小距离的路径,那么这条路径上的序列与发送序列相同的可能性最大。

在AWGN信道中,当使用欧式距离时,Viterbi算法的性能最好。

因此,这种算法是最优最大似然译码算法[2]。

Viterbi译码器分为硬判决译码器和软判决译码器,软判决译码器与硬判决译码器相比有2 ̄3dB的增益,而译码器结构复杂度增加不大[1]。

由Viterbi算法的基本原理可得典型的Viterbi译码器,如图3所示。

分支路径度量产生单元BMG(BranchMetricGenerate)用于产生接收序列与状态转移分支上编码输出数据之间的距离。

令长度为n的接收信号为R!=("r1,…"rn),与之相应的发送信号为C!=("c1,…"cn)。

因为具有最小欧式距离的路径也就是具有最大相关的路径,所以定义分支路径上的度量为:BM=ni=1#"ri"ci。

由于此分支路径度量没有平方运算,所以可将状态转移分支上的编码输出数据存储在查找表内,这样只需进行加减和查表运算,大大减小了实现的复杂程度。

以上计算公式中数值为连续值,而本设计采用的是软判决译码器,故只需对输入的接收信号进行均匀量化即可(量化比特数为q)。

加比选单元ACS(Add-Compare-Select)模块包括若干个单个状态加比选模块ACSU,一个ACSU模块执行一个状态的路径度量升级。

ACSU模块的具体个数根据译码器的速率要求而定。

对于低速的译码器,为了节约芯片的面积,可以使用较少的ACSU模块进行时分复用;而在高速Viterbi译码器的设计中,则采用全并行的结构,ACSU模块的个数等于网格图上的状态数N=2k-1。

译码器开始工作时,给路径度量设定一个初始化正值。

在度量升级过程中,路径度量的不断累加会造成溢出。

因为在度量升级时只是比较大小,所以在每次度量升级之后,所有的路径度量值减去路径度量值中的最小值,而不会影响路径度量间的大小关系。

同时,为了下次路径度量升级不出现负值,需要对所有的度量值加上一个恒定常数。

经过归一化处理后的路径度量,其最大值与最小值相差不超过2q(k-1)。

所以,对于q比特而软判决编码长度为k的Viterbi译码器,其路径度量长度为q+log2(k-1)比特[3]。

MLD(Most-Likelihood-Decision)模块用于在所有状态的路径度量中找出最大值,具有最大路径度量的幸存路径便是最大似然路径。

在时刻L时,MLD电路判决最大似然路径,将其末端节点状态送至TB模块。

同时为了保证下次的路径度量升级不出现负值,还要找出最小值送79《电子技术应用》2005年第10期欢迎网上投稿www.aetnet.cnwww.aetnet.com.cn表1FPGA芯片资源利用率表选用的芯片:2V1000fg456-4内部资源占用数总数占用率slice块4366512085%触发器56491024054%四输入查找表54961024053%I/O6632420%块状RAM304075%专用乘法器64015%全局时钟1166%到PMMI模块,在其中进行归一化处理。

PMMI模块和SPMI模块分别是ACS模块与路径度量存储器PMM(PathMetricMemory)之间和幸存路径存储器SPM(SurvivorPathMemory)与MLD模块之间的接口模块。

同时,TB(TraceBack)模块也通过SPMI模块读取幸存路径存储器信息。

针对不同的存储方式,SPMI和PMMI的复杂程度也不同。

ACSU模块的复用程度越高,其接口电路越复杂[4]。

TB模块从SPM中读取当前时刻64条路径的幸存信息,根据末端状态可以找到相应的最大似然路径在时刻t的幸存信息,从而找到t-1时刻最大似然路径上的状态。

依此类推,直至找到最大似然路径在t-L+1时刻的状态,状态的最高位即为译码输出。

FPGA可以实现流水线操作,而各个模块可以同时进行工作,所以需要控制模块处理各个模块间的时序关系。

每个子模块都有一个控制信号,使得输入数据可以在各个模块之间进行流水操作。

由于本方案是基于各个功能单元自上至下设计的,灵活性较大,稍加修改子模块,便可以用于实现各种卷积码的Viterbi译码器。

2.2QPSK调制与解调的FPGA实现QPSK调制模块由成形滤波和上变频两部分组成。

成形滤波具有两个功能,即限带和抗码间干扰。

成形滤波采用查表的方式实现,四倍内插,升余弦滚降。

成形后的数据与NCO产生的本地载波进行上变频运算。

QPSK解调的结构框图如图4所示。

解调模块由下变频、低通滤波、根升余弦滤波和载波同步几部分组成。

I、Q两路的调制信号先经过本地载波NCO下变频,再通过低通滤波器LPF得到基带信号。

基带信号需要进行相应的根升余弦滤波。

由于本地载波与发端载频之间有一定的偏差,所以要根据解调后的信号估计频差并修改本地载波NCO的参数,实现载波同步。

数据经过根升余弦滤波后进行差分解码,解调后送入译码器单元。

3系统性能分析与结论综上所述,系统主要功能都是在FPGA内完成的。

本文选择Xilinx公司的100万门FPGA芯片XC2V1000,在ISE6.2i环境下进行编程开发。

系统的资源占用情况如表1所示。

为了测试系统在噪声下的误码率性能,在发端和收端之间引入噪声源,在70MHz中频上进行数据传输。