暴风影音去广告

MPC564MZP40中文资料

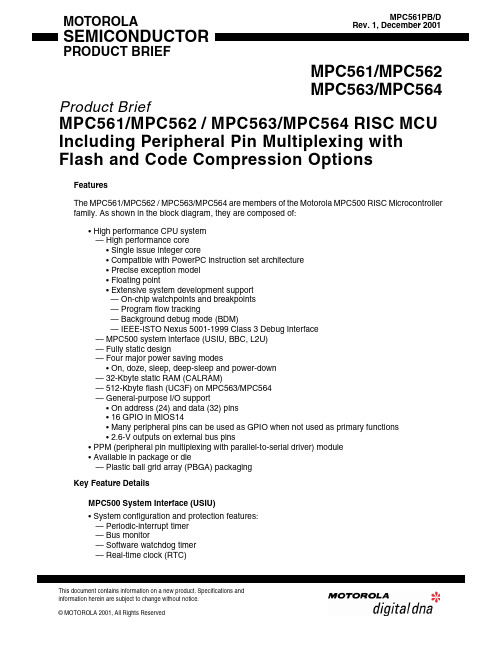

MOTOROLA SEMICONDUCTOR PRODUCT BRIEFThis document contains information on a new product. Specifications and information herein are subject to change without notice.MPC561PB/DRev. 1, December 2001MPC561/MPC562 MPC563/MPC564Product BriefMPC561/MPC562 / MPC563/MPC564 RISC MCUIncluding Peripheral Pin Multiplexing withFlash and Code Compression OptionsFeaturesThe MPC561/MPC562 / MPC563/MPC564 are members of the Motorola MPC500 RISC Microcontrollerfamily. As shown in the block diagram, they are composed of:• High performance CPU system— High performance core• Single issue integer core• Compatible with PowerPC instruction set architecture• Precise exception model• Floating point• Extensive system development support— On-chip watchpoints and breakpoints— Program flow tracking— Background debug mode (BDM)— IEEE-ISTO Nexus 5001-1999 Class 3 Debug Interface— MPC500 system interface (USIU, BBC, L2U)— Fully static design— Four major power saving modes• On, doze, sleep, deep-sleep and power-down— 32-Kbyte static RAM (CALRAM)— 512-Kbyte flash (UC3F) on MPC563/MPC564— General-purpose I/O support• On address (24) and data (32) pins• 16 GPIO in MIOS14• Many peripheral pins can be used as GPIO when not used as primary functions• 2.6-V outputs on external bus pins• PPM (peripheral pin multiplexing with parallel-to-serial driver) module• Available in package or die— Plastic ball grid array (PBGA) packagingKey Feature DetailsMPC500 System Interface (USIU)• System configuration and protection features:— Periodic-interrupt timer— Bus monitor— Software watchdog timer— Real-time clock (RTC)元器件交易网— Decrementer— Time base• Clock synthesizer• Power management• Reset controller• External bus interface that tolerates 5-V inputs, provides 2.6-V outputs and supports multiple-mas-ter designs• Enhanced interrupt controller that supports up to eight external and 40 internal interrupts, simpli-fies the interrupt structure and decreases interrupt processing time• USIU supports dual mapping to map part of one internal/external memory to another external memory• USIU supports dual mapping of flash on MPC563 and MPC564 to move part of internal flash mem-ory to external bus for development• External bus, supporting non-wraparound burst for instruction fetches, with up to 8 instructions per memory cycleBurst Buffer Controller (BBC) Module• Support for enhanced interrupt controller (EIC)• Support for enhanced exception table relocation feature• Branch target buffer• Contains 2-Kbytes of decompression RAM (DECRAM) for code compression. This RAM may also be used as general-purpose RAM when code compression feature not used.Flexible Memory Protection Unit• Flexible memory protection units (MPU) in BBC and L2U• Default attributes available in one global entry• Attribute support for speculative accesses• Up to eight memory regions are supported, four for data and four for instructionsMemory Controller• Four flexible chip selects via memory controller• 24-bit address and 32-bit data buses• 4-Kbyte to one 16-Mbyte (data) or four-Gbyte (instruction) region size support• Supports enhanced external burst• Up to eight-beat transfer bursts, two-clock minimum bus transactions• Use with SRAM, EPROM, flash and other peripherals• Byte selects or write enables• 32-bit address decodes with bit masks• Four regions512-Kbytes of CDR3 Flash EEPROM Memory (UC3F) – MPC563 Only• One 512-Kbyte module• Page read mode• Block (64 Kbytes) erasable• External 4.75- to 5.25-V VFLASH power supply for program, erase, and read operations32-Kbyte static RAM (CALRAM)• Composed of one 32-Kbyte CALRAM module— 28-Kbyte static RAM— 4-Kbyte calibration (overlay) RAM feature that allows calibration of flash-based constants • Eight 512-byte overlay regions• One clock fast accesses• Two-clock cycle access option for power saving• Keep-alive power (VDDSRAM) for data retentionGeneral-Purpose I/O Support• 24 Address pins and 32 data pins can be used for general-purpose I/O in single-chip mode • 16 GPIO in MIOS14• Many peripheral pins can be used as GPIO when not used as primary functions• 2.6-V outputs on external bus pins• 5-V outputs with slew rate controlNEXUS Debug Port (Class 3)• Compliant with Class 3 of the IEEE-ISTO Nexus 5001-1999• Program trace via branch trace messaging (BTM)• Data trace via data write messaging (DWM) and data read messaging (DRM)• Ownership trace via ownership trace messaging (OTM)• Run-time access to on-chip memory map and MPC5xx special purpose registers (SPRs) via the READI read/write access protocol• Watchpoint messaging via the auxiliary port• Reduced-port mode (1 MDI, 2 MDO) or full-port mode (2 MDI. 8 MDO)• All features configurable and controllable via the auxiliary port• Security features for production environment• Supports the RCPU debug mode via the auxiliary port• READI module can be reset independent of system resetIntegrated I/O SystemTwo Time Processor Units (TPU3)• True 5-V I/O• Two time processing units (TPU3) with16 channels each• Each TPU3 is a micro-coded timer subsystem• Eight-Kbytes of dual port TPU RAM (DPTRAM) shared by two TPU3 modules for TPU micro-code22-Channel Modular I/O System (MIOS14)• Six modulus counter sub-modules (MCSM)• 10 double-action sub-modules (DASM)• 12 dedicated PWM sub-modules (PWMSM)• One MIOS14 16-bit parallel port I/O sub-modules (MPIOSM)Two Enhanced Queued Analog-to-Digital Converter Modules (QADC64E)• Two queued analog-to-digital converter modules (QADC64_A, QADC64_B) providing a total of 32 analog channels• 16 analog input channels on each QADC64E module using internal multiplexing• Directly supports up to four external multiplexers• Up to 41 total input channels on the two QADC64E modules with external multiplexing• Software configurable to operate in Enhanced or Legacy (MPC555 compatible) mode• Unused analog channels can be used as digital input/output pins— GPIO on all channels in Enhanced mode• 10-bit A/D converter with internal sample/hold• Typical conversion time of less than 5 µs (>200 K samples/second)• Two conversion command queues of variable length• Automated queue modes initiated by:— External edge trigger— Software command— Periodic/interval timer within QADC64E module, that can be assigned to both queue 1 and 2— External Gated trigger (queue 1only)• 64 result registers— Output data is right- or left-justified, signed or unsigned• Alternate reference input (ALTREF), with control in the conversion command word (CCW)Three CAN 2.0B Controller (TouCAN) Modules• Three TouCAN modules (TOUCAN_A, TOUCAN_B, TOUCAN_C)• Each TouCAN provides the following features:— 16 message buffers each, programmable I/O modes— Maskable interrupts— Independent of the transmission medium (external transceiver is assumed)— Open network architecture, multi-master concept— High immunity to EMI— Short latency time for high-priority messages— Low-power sleep mode, with programmable wake-up on bus activity— TOUCAN_C pins are shared with MIOS14 GPIO or QSMCMQueued Serial Multi-Channel Module (QSMCM)• One queued serial module with one queued SPI and two SCIs (QSMCM)• QSMCM matches full MPC555 QSMCM functionality• Queued SPI— Provides full-duplex communication port for peripheral expansion or inter-processor commu-nication— Up to 32 preprogrammed transfers, reducing overhead— Synchronous serial interface with baud rate of up to system clock / 4— Four programmable peripheral-selects pins:— Support up to 16 devices with external decoding— Support up to eight devices with internal decoding— Special wrap-around mode allows continuous sampling of a serial peripheral for efficient inter-facing to serial analog-to-digital (A/D) converters• SCI— UART mode provides NRZ format and half- or full-duplex interface— 16 register receive buffers and 16 register transmit buffers on one SCI— Advanced error detection and optional parity generation and detection— Word-length programmable as eight or nine bits— Separate transmitter and receiver enable bits, and double buffering of data— Wake-up functions allow the CPU to run uninterrupted until either a true idle line is detected, or a new address byte is receivedPeripheral Pin Multiplexing (PPM) PPM• Synchronous serial interface between the microprocessor and an external device• Four internal parallel data sources can be multiplexed through the PPM— TPU3_A: 16 channels— TPU3_B: 16 channels— MIOS14: 12 PWM channels, 4 MDA channels— Internal GPIO: 16 general-purpose inputs, 16 general-purpose outputs• Software configurable stream size• Software configurable clock (TCLK) based on system clock• Software selectable clock modes (SPI mode and TDM mode)• Software selectable operation modes— Continuous mode— Start-transmit-receive (STR) mode• Software configurable internal modules interconnect (shorting)MPC561/MPC562 / MPC563/MPC564 Optional FeaturesThe following are optional features of the MPC561/MPC562 / MPC563/MPC564:• 56-MHz operation (40 MHz is default)• Code compression supported on the MPC562 and the MPC564— Compression reduces instruction memory requirements by 40-50%— Compression optimized for automotive (non-cached) applications • 512 Kbytes flash (available on the MPC563/MPC564 only)— Single array— Page mode read— Block (64 Kbytes) erasable— External 4.75- to 5.25-V VFLASH program, erase, and read power supplyFigure 1 MPC561/MPC562 / MPC563/MPC564 Block DiagramE-BUSMPC5xx Core L-BUSU-BUSIMB3+FPUSIUBuffer Burst Int.L2U I/FUIMB QSMCM MIOS14DPTRAM8-Kbyte READIQADC64JTAGTPU3QADC64TPU332-Kbyte CALRAM 28-Kbyte (No Overlay)4-Kbyte OverlayTou CAN Tou CANPPMSRAM Tou CAN Controller512 Kbytes Flash (on MPC563/MPC564 only)Figure 2 MPC561 / MPC563 Internal Memory Map4-Kbyte Overlay Section0x30 7FFF 0x2F FFFF 0x30 00000x00 00000x38 00000x38 3FFF 0x3F FFFF0x2F C0000x2F BFFF 0x30 80000x37 FFFF 0x38 40000x07 FFFF 0x3F 7FFF 0x3F 80000x08 00000x38 00FF 0x38 01000x2F 80000x2F 7FFF UC3F Flash*512 KbytesReserved for Flash 2,605 KbytesBBC DECRAM 2 Kbytes USIU & Flash Control16 KbytesUIMB I/F & IMB Modules 32 KbytesReserved for IMB 491 Kbytes CALRAM/READI Control 256 bytes Reserved (L-bus Control)~32 KbytesReserved (L-bus Mem)464 KbytesCALRAM 32 Kbytes*NOTE: Only available on MPC563/MPC564.0x3F F0000x30 00000x30 7FFFDPTRAM (8 Kbytes)QSMCM (1 Kbyte)MIOS14 (4 Kbytes)TOUCAN_A (1 Kbyte)TOUCAN_B (1 Kbyte)UIMB Registers (128 bytes)TPU3_A (1 Kbyte)TPU3_B (1 Kbyte)QADC64_A (1 Kbyte)QADC64_B (1 Kbyte)DPTRAM Control (32 bytes)USIU Control Registers0x2F C0000x30 7C000x30 70000x30 60000x30 54000x30 50000x30 4C000x30 48000x30 44000x30 40000x30 20000x30 7400Reserved (8160 bytes)Reserved (2 Kbytes)Reserved (896 bytes)0x30 78000x2F C8000x30 7F80TOUCAN_C (1 Kbyte)0x30 5C00PPM (64 bytes)0x30 5C80Reserved (960 bytes) 0x30 0020UC3F Control Registers*0x2F 8800 Reserved for BBC 0x2F A000 BBC CONTROLFigure 3 MPC561 / MPC563 Ball Map1234567891011121314151617181920212223242526AVDDVSSVSSVSSA_TPUCH3A_TPUCH7A_TPUCH11A_TPUCH15VSSAVRLA_AN3_A NZ_PQB3A_AN51_P QB7A_AN55_PQA3A_AN56_P QA4B_AN0_AN W_PQB0B_AN48_PQB4B_AN52_M A0_PQA0B_AN56_P QA4VSSETRIG2_PCS7MDA13MDA28VSSVSSVDDVSSAB VSS VDD VSS VSS A_TPUCH2A_TPUCH6A_TPUCH10A_TPUCH14VSSA ALTREF A_AN2_A NY_PQB2A_AN50_P QB6A_AN54_MA2_PQ A2A_AN58_P QA6B_AN1_AN X_PQB1B_AN49_PQB5B_AN53_M A1_PQA1B_AN57_P QA5VSSETRIG1_PCS6MDA14MDA29VSSVDDVSSQVDDLBC VSS VSS VDD VSS A_TPUCH1A_TPUCH4A_TPUCH8A_TPUCH12NVDDL VRH A_AN0_A NW_PQB 0A_AN48_P QB4A_AN52_MA0_PQ A0A_AN59_P QA7B_AN2_AN Y_PQB2B_AN50_PQB6B_AN54_M A2_PQA2B_AN58_P QA6VDDH MDA11MDA15VDDH VDD VSS QVDDL VSS CD VSS VSS VSS VDD VSS A_TPUCH5A_TPUCH9A_TPUCH13NVDDL VDDA A_AN1_A NX_PQB1A_AN49_P QB5A_AN53_MA1_PQ A1A_AN57_P QA5B_AN3_AN Z_PQB3B_AN51_PQB7B_AN55_P QA3B_AN59_P QA7VDDH MDA12MDA27VDD VSS QVDDL VSS VSS DE VDDH VSS VSS VSS QVDDL VSS VSS VSS EF B_T2CLK_P CS4A_T2CLK_PCS5A_TPUCH 0QVDDL VDDH MDA30MDA31MPWM0_MDI1F GB_TPUCH12B_TPUCH13B_TPUCH 14B_TPUCH15MPWM1_MDO2MPWM16MPWM3_PP M_RX1MPWM2_PP M_TX1GH B_TPUCH8B_TPUCH9B_TPUCH 10B_TPUCH11MPWM17_M DO3MPWM18_MD O6MPWM19_MDO7MPIO32B5_MDO5HJ B_TPUCH4B_TPUCH5B_TPUCH6B_TPUCH7MPIO32B6_MPWM4_MDO6MPIO32B7_MP WM5MPIO32B8_MPWM20MPIO32B9_MPWM21JK B_TPUCH0B_TPUCH1B_TPUCH2B_TPUCH3MPIO32B12_C_CNTX0MPIO32B11_C _CNRX0MPIO32B10_PPM_TSYNC MPIO32B13_PPM_TCLK KLJCOMP_RS TI_B TCK_DSCK_MCKI B_CNRX0B_CNTX0VSS VSS VSS VSS VSS VSS VF0_MPIO32B0_MDO1VF1_MPIO32B 1_MCKO MPIO32B15_PPM_TX0MPIO32B14_PPM_RX0LM TDI_DSDI_MDI0TMS_EVTI _B VDDSRA MTDO_DSDO_MDO0VSS VSS VSS VSS VSS VSS A_CNTX0VF2_MPIO32B2_MSEI_B VFLS0_MPIO32B3_MSEO_BVFLS1_MPIO 32B4M N IRQ3_B_KR_B_RETRY _B_SGPIO C3IWP0_VFL S0IWP1_VFL S1SGPIOC6_FRZ_PTR_BVSS VSS VSS VSS VSS VSSPCS2_QGPI O2PCS1_QGPIO1PCS0_SS_B_QGPIO0A_CNRX0NP IRQ4_B_AT 2_SGPIOC4IRQ2_B_CR_B_SGPIOC2_MDO5_MTSIRQ0_B_S GPIOC0_MDO4IRQ1_B_RSV_B_SGPIOC1VSS VSS VSS VSS VSS VSSSCK_QGPIO 6MOSI_QGPIO5MISO_QGPIO4PCS3_QGPIO3PR SGPIOC7_IRQOUT_B_LWP0BB_B_VF2_IWP3BG_B_VF 0_LWP1BR_B_VF1_IWP2VSS VSS VSS VSS VSS VSSRXD1_QGPI 1TXD2_QGPO2_C_CNTX0TXD1_QGPO1PULL-SEL RTWE_B_AT0WE_B_AT1WE_B_AT 2WE_B_AT 3VSS VSS VSS VSS VSS VSS EPEE BOEPEE VDDHRXD2_QGPI2_C_CNRX0TU CS0_B CS1_B CS2_BCS3_BCLKOUT VSSF VDDF VFLASH UV RD_WR_B OE_B TEA_B TSIZ0VDD EXTCLK VSS ENGCLK_BUCLK VW TSIZ1TS_B TA_B BDIP_B HRESET_B SRESET_B PORESET_B _TRST_BKAPWRWY BURST_BBI_B_STS_B ADDR_SG PIOA12ADDR_SG PIOA11NVDDLIRQ7_B_MODC K3RSTCONF_B_TEXPVDDSYN YAA VSS VSS VSS QVDDL VSS VSS VSS XFC AA ABVSSVSSQVDDLVSSQVDDLVSSVSSVSSSYNABAC VSS QVDDL VSS NVDDL VSS ADDR_SGP IOA10ADDR_SG PIOA18ADDR_SGPI OA20ADDR_SGPIOA23NVDDL ADDR_S GPIOA26DATA_SG PIOD1DATA_SG PIOD5DATA_SGPIOD7NVDDL DATA_SG PIOD9DATA_SGP IOD11DATA_SGPIOD12NVDDL DATA_SGPIOD14VSS VDD VSS QVDDL VSS EXTAL ACAD QVDDL VSS NVDDL VSS VSS QVDDLADDR_SG PIOA13ADDR_SGPI OA16ADDR_SG PIOA19ADDR_SGP IOA21ADDR_S GPIOA24ADDR_SG PIOA25DATA_SG PIOD0DATA_SG PIOD28DATA_SGP IOD26DATA_SG PIOD24DATA_SGP IOD22DATA_SG PIOD13DATA_SGPI OD15DATA_SGPIOD16IRQ5_B_SGPIOC5_MODCK1VSS VDD VSS QVDDL XTAL ADAE VSS NVDDL VSS VSS VSS QVDDL ADDR_SG PIOA14ADDR_SGPI OA17ADDR_SG PIOA31ADDR_SGP IOA30ADDR_S GPIOA28ADDR_SG PIOA29DATA_SG PIOD30DATA_SG PIOD29DATA_SGP IOD27DATA_SG PIOD25DATA_SGP IOD23DATA_SG PIOD21DATA_SGPI OD19DATA_SGPIOD17IRQ6_B_MODCK2VSS VSS VDD VSS QVDDL AEAF NVDDL VSS VSS VSS VDDH VSS ADDR_SG PIOA15ADDR_SGPI OA9ADDR_SG PIOA8ADDR_SGP IOA22ADDR_S GPIOA27DATA_SG PIOD31DATA_SG PIOD3DATA_SG PIOD2DATA_SGP IOD4DATA_SG PIOD6DATA_SGP IOD8DATA_SG PIOD10DATA_SGPI OD20DATA_S GPIOD18VDDH VSS VSS VSS VDD VSS AF1234567891011121314151617181920212223242526MPC561 / MPC563 Ball Map(As viewed from top, through the package and silicon)NOTE: The flash balls are only available on the MPC563 and MPC564. These are no connect balls onthe MPC561 and MPC562. Flash supplies and inputs are located on the following balls: T23, T24, U24, U25. U26.Ordering InformationTable 2 lists the documents that provide a complete description of the MPC561/563 and are required to design properly with the part. Documentation is available from a local Motorola distributor, a Motorola semiconductor sales office, a Motorola Literature Distribution Center, or through the Motorola Semicon-ductor documentation page on the Internet (the source for the latest information).Table 1 MPC561/562 / MPC563/564Device Name Order Part Number 1NOTES:1. Add R2 suffix for parts shipped in tape and reel media.Package Info Temperature Range Maximum Frequency Code CompressionMPC561MPC561MZP40388 PBGA -40 – 125° C 40 MHz No MPC561MPC561CZP40388 PBGA -40 – 85° C 40 MHz No MPC561MPC561MZP56388 PBGA -40 – 125° C 56 MHz No MPC561MPC561CZP56388 PBGA -40 – 85° C 56 MHz No MPC562MPC562MZP40388 PBGA -40 – 125° C 40 MHz Yes MPC562MPC562CZP40388 PBGA -40 – 85° C 40 MHz Yes MPC562MPC562MZP56388 PBGA -40 – 125° C 56 MHz Yes MPC562MPC562CZP56388 PBGA -40 – 85° C 56 MHz Yes MPC563MPC563MZP40388 PBGA -40 – 125° C 40 MHz No MPC563MPC563CZP40388 PBGA -40 – 85° C 40 MHz No MPC563MPC563MZP56388 PBGA -40 – 125° C 56 MHz No MPC563MPC563CZP56388 PBGA -40 – 85° C 56 MHz No MPC564MPC564MZP40388 PBGA -40 – 125° C 40 MHz Yes MPC564MPC564CZP40388 PBGA -40 – 85° C 40 MHz Yes MPC564MPC564MZP56388 PBGA -40 – 125° C 56 MHz Yes MPC564MPC564CZP56388 PBGA-40 – 85° C56 MHzYesTable 2 Available DocumentationDocument Number TitleMPC561_3RM/ADMPC561/MPC563 Reference ManualAN1821/D Exception Table Relocation and Multi-Processor Address Mapping in the Embedded MPC5XX Family AN2109/D MPC555 Interrupts.AN2127/DEMC Guidelines for MPC500-Based Automotive Powertrain SystemsMPC561/MPC563 PRODUCTBRIEF MOTOROLA11Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty,representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. “Typical” parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers,employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.OnCE, DigitalDNA, and the DigitalDNA logo are trademarks of Motorola, Inc.Order Number MPC561PB/DHow to reach us:USA/EUROPEMotorola Literature DistributionP.O. Box 5405Denver, Colorado 802171-303-675-21401-800-441-2447Technical Information Center1-800-521-6274JAPAN Motorola Japan Ltd.SPS, Technical Information Center 3-20-1, Minami-Azabu, Minato-ku Tokyo 106-8573 Japan 81-3-3440-3569ASIA/PACIFICMotorola Semiconductors H.K. Ltd.Silicon Harbour Centre2 Dai King StreetTai Po Industrial EstateTai Po, N.T., Hong Kong852-********Home Page /semiconductors。

广告关闭操作方法

广告关闭操作方法

关闭广告的操作方法有以下几种:

1. 点击广告上的'关闭' 或'X' 按钮:广告上通常会有一个明显的关闭按钮或'X'按钮,点击这个按钮即可关闭广告。

2. 找到广告所在页面上的关闭选项:有些广告可能没有关闭按钮,但是页面上可能会有其他关闭选项,比如在广告旁边可以找到一个叉叉按钮,点击这个按钮即可关闭广告。

3. 通过广告设置关闭:有些广告会提供设置选项,允许用户自定义广告的显示设置。

在设置中可以找到关闭广告的选项,选择关闭后,广告就会停止显示。

4. 使用广告拦截器或广告屏蔽插件:安装广告拦截器或广告屏蔽插件可以有效地屏蔽网页上的广告,使其无法显示。

通过这种方式,你可以避免看到广告。

5. 卸载或停用与广告相关的应用程序:有些应用程序可能会在手机或电脑上显示广告。

通过卸载或停用这些应用程序,可以避免看到这些广告。

请注意,有些广告可能无法通过上述方法关闭,这些广告可能是强制性的或浮窗式的广告,可能需要通过其他方式来关闭,比如通过关闭网页或应用程序。

用暴风影音看电影字幕文件的使用方法

字幕请到射手网或TLF字幕网下载

一、下载字幕文件

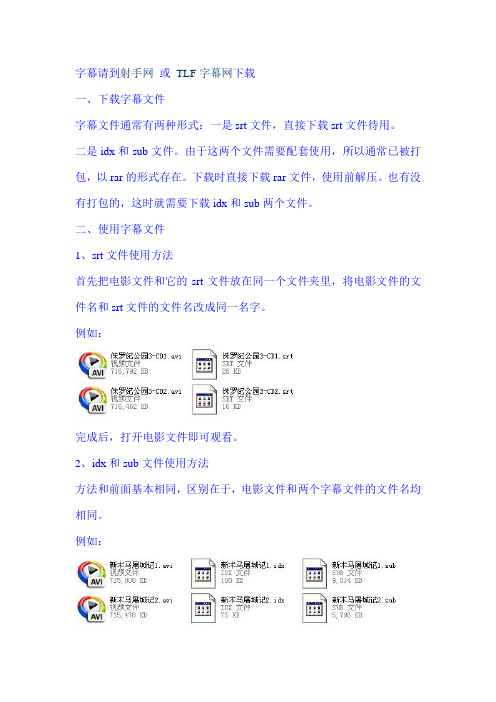

字幕文件通常有两种形式:一是srt文件,直接下载srt文件待用。

二是idx和sub文件。

由于这两个文件需要配套使用,所以通常已被打包,以rar的形式存在。

下载时直接下载rar文件,使用前解压。

也有没有打包的,这时就需要下载idx和sub两个文件。

二、使用字幕文件

1、srt文件使用方法

首先把电影文件和它的srt文件放在同一个文件夹里,将电影文件的文件名和srt文件的文件名改成同一名字。

例如:

完成后,打开电影文件即可观看。

2、idx和sub文件使用方法

方法和前面基本相同,区别在于,电影文件和两个字幕文件的文件名均相同。

例如:

完成后,打开电影文件即可观看。

三、注意事项

1、下载的如果是rar文件,使用前请解压。

并使得电影文件和idx和sub 这三个文件都处于同一目录。

2、有的电影是单本,有的是双CD,所以,要注意cd1和cd2分别对应好各自的字幕文件。

3、改名随意,并无规则,但是让名字尽量简单,如“cd1”、“cd2”等,可以减少出错的几率。

tvbox去广告规则 -回复

tvbox去广告规则-回复探讨:TVBox去广告规则引言:在互联网发展迅速的今天,电视已经成为家庭娱乐的重要组成部分。

而网络电视盒子(TV Box)的出现使得电视观看更加丰富多样。

然而,广告垃圾的泛滥却成为影响观看体验的突出问题。

为了解决这一问题,许多用户希望能够找到去广告的解决方案。

本文将逐步探讨TVBox去广告的规则,并提供一些可行的解决方案。

第一部分:广告垃圾的困扰1.1 广告垃圾的定义与特点广告垃圾指的是过多、过双眼的商业广告信息,其在传播过程中会给用户带来骚扰,而不是满足其需求。

1.2 广告带来的问题广告直接影响到用户的观影体验和观看质量,限制了用户对电视内容的真正享受。

除此之外,广告也是许多惹人厌烦的恶意软件和病毒传播的重要渠道。

第二部分:TVBox去广告的需求2.1 用户对去广告的期待用户希望通过某种方式,可以过滤广告并远离广告垃圾,以获得更加高品质的观看体验。

2.2 去广告的技术挑战去广告的技术挑战主要体现在广告的形式与多样性,以及如何精确识别和屏蔽广告。

第三部分:常见的TVBox去广告解决方案3.1 广告屏蔽软件广告屏蔽软件是一种常见的去广告解决方案。

通过拦截广告请求、过滤页面元素或屏蔽广告域名,来实现去广告效果。

常见的广告屏蔽软件包括AdGuard、Pi-hole等。

3.2 主题定制与插件扩展通过定制TVBox的主题布局或者添加插件扩展,可以去除或屏蔽广告。

例如,通过自定义主题、更换桌面壁纸等方式,可以让用户在观看电视时不再看到烦人的广告。

3.3 DNS过滤与黑名单通过设置DNS过滤规则或黑名单,可以屏蔽一些常见广告域名,从而降低广告出现的频率和数量。

例如,通过设置路由器级别的DNS过滤规则,可以让所有通过该路由器上网的设备都享受去广告的效果。

第四部分:TVBox去广告规则的限制与挑战4.1 宣传方式的改变带来新的问题随着传播方式的变化,广告形式也在不断更新。

很多广告采用了狡猾的手段,如隐形广告和文字链接广告,这给去广告的规则制定带来了一定的挑战。

使用“暴风影音”播放韩文字幕方法及设置

使用“暴风影音”播放韩文字幕方法及设置。

1,当然还是得下载“暴风影音”当作播放器来使用,(暴风5.1以上的版本都带上vobsub插件,老版本就没有的,此处的vobsub插件也很重要,后面将讲解)注:大家常用的RealPlayer或windows media player的常用播放器是不能显示“外挂字幕”的(如srt格式之类的外挂字幕),建议使用“暴风影音“或"KMPlayer"播放.下载地址:/soft/25918.htm ;2,下载好安装"暴风"到你的电脑上。

安装好后一般是蓝白色的图标,这样才能直接双击打开的就是“暴风”,如果不是此图标,那就右键“打开方式”选择“暴风影音”来播放3,下载字幕,下载后是个压缩包,把压缩包中的字幕文件解压出来。

(如何解压就不在说了)把字幕文件“复制”或“剪切”,“粘贴”到你的片子所在处置,并将其名称改为一样(很重要)!!!!!具体说下:很多人在这块会出错。

名称改为一样,并不是全一样的。

而是名称一样,后辍名千万不可改掉哟,不然就错了。

举例:如果你有个片名称为“01”或“01.rmvb",而下载后的字幕解压出来是“对不起我爱你01.srt" 后面的.rmvb和.srt都是文件的后辍名代表了文件是何种类型。

改了就不是这种文件了嘛,所以改名只能改后辍名前面的就行,后辍名保持原有的就行,改为“对不起我爱你01”或“对不起我爱你01.rmvb",和“对不起我爱你01.srt",这样的改名才是真正的名称一样哟。

4,设置方面。

首先我们要明白字幕的特性:外挂字幕在暴风中是可以有“两种方式”来实现显示韩文的。

(切记,看你使用哪种,这里贴出来的是两种都教你如何设置出来)一种是通过对”暴风“选项”的“字幕选项”调整来实现“暴风显示韩文”,二种是直接打开的。

你打开电影的同时就会自动加载,如果你第3步方面的名称改为一样成功的话,在我们的“桌面右下角任务栏”会有个“绿色小标头”而此时你会发现你的暴风中有很多小格子(是不是呀???)这就是vobsub 显示韩文,但此时字幕设置都是中文字体,显示韩文当然是乱码之类的嘛,所以才是“小格子”,5,明白了这些,我们来开始具体设置了。

openwrt去电视广告规则

openwrt去电视广告规则广告是当今社会中无处不在的,而电视广告更是我们日常生活中经常接触到的一种形式。

然而,并不是所有的电视广告都是我们希望看到的,有时候它们会打断我们正在观看的节目,给我们带来不必要的干扰。

为了解决这个问题,许多用户选择使用OpenWrt,这是一种基于Linux的自由和开放源代码的操作系统,用于路由器和嵌入式设备。

通过OpenWrt,我们可以设置去广告规则,从而屏蔽电视广告,提供更加纯净的观看体验。

为了实施去电视广告规则,以下是一些方法供您参考:1. 使用Pi-hole: Pi-hole是一款广告过滤软件,可以在OpenWrt上安装和配置。

它通过将广告服务器的域名指向无效IP地址,阻断广告网络连接,从而实现去广告效果。

您可以通过OpenWrt的软件包管理器安装Pi-hole,并按照其官方文档进行配置。

2. 使用AdGuard Home: AdGuard Home是另一款广告拦截软件,也可以在OpenWrt上安装和配置。

它使用类似的机制来屏蔽广告,但具有更多的个性化选项和高级功能。

您可以从OpenWrt的软件包管理器安装AdGuard Home,并按照其官方文档进行设置。

3. 使用OpenWrt的iptables规则: 如果您熟悉iptables和网络规则设置,您可以手动配置OpenWrt的iptables规则来拦截广告流量。

这需要更多的技术知识和时间投入,但可以提供更高的灵活性和定制性。

无论您选择哪种方法,都需要注意以下几点:- 定期更新去广告软件或规则,以确保其有效性和适应新的广告网络。

- 有些广告可能会通过其他域名或协议传输,因此完全去除所有广告可能是不可能的。

但通过使用去广告规则,您可以大大减少广告数量。

- 去广告规则可能会对某些网站或应用程序的功能产生影响。

如果您发现某些网站或应用程序无法正常运行,请尝试禁用去广告规则。

总之,使用OpenWrt可以帮助我们屏蔽广告,提供更加纯净的电视观看体验。

去除小广告的方法

去除小广告的方法

去除小广告的方法有以下几种:

1. 勿点击小广告:小广告往往会通过诱人的内容吸引用户点击,从而获取收益。

为避免被小广告骚扰,用户可以在使用电脑或移动设备时,不要轻易点击或关注小广告。

2. 使用广告拦截软件:用户可以安装广告拦截软件,如Adblock Plus、uBlock Origin等,来屏蔽小广告的显示。

这些软件能够识别网页上的广告内容,并将其过滤掉,提升用户浏览网页的体验。

3. 定期清理浏览器缓存:小广告信息可能会存储在浏览器的缓存中,定期清理浏览器的缓存可以有效去除小广告。

4. 更新操作系统和应用程序:及时更新操作系统和应用程序可以修复漏洞,提升系统和应用的安全性,减少小广告的出现。

5. 谨慎使用不安全的网站和应用:尽量避免使用不安全或没有信誉的网站和应用,这些网站和应用可能将用户信息泄露给小广告发布者,并导致更多的小广告出现。

需要注意的是,尽管采取以上措施可以减少小广告的出现,但小广告层出不穷,

总会有新的方式绕过防御。

因此,在日常使用电脑和移动设备时,用户还应提高对小广告的识别能力,并保持警惕,避免点击或关注这些小广告。

如何让暴风影音不自动升级

strormliv.exe是暴风的自动升级程序

你要是把它关闭了,暴风会提示出现损坏,要求升级,让它在进程里,会占用一定的内存

完全把stormliv.exe取消的方法(不会要求升级)

到设置-控制面板-管理工具-服务-找到

Contrl Center of Storm Media ,双击它,启动类型-禁用,

服务状态-停止,

到storm的安装文件中找到

Media2.dll ,删除它

然后在暴风的安装文件夹中,找到stormliv.exe删除,新建一个文件夹,命名为stormliv.exe

在防火墙里把暴风影音的主程序的网络访问规则设置为禁止

(两个:storm.exe stormliv.exe)

这样暴风不会访问网络,也就不会自动升级了。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

暴风影音去广告

打开文件夹C:\Documents and Settings\All Users\Application

Data\Baofeng\StormPlayer\Profiles\md\link

里面有两个文件st1.xml和st2.xml,用记事本打开删除里面

一切内容,保存,设定文件属性为只读。

打开文件夹C:\Documents and Settings\All Users\Application

Data\Baofeng\StormPlayer\Profiles\vod

将此文件夹中的loading和tips文件夹删除,新建同名文件(不

要后缀),设属性为只读。

打开文件夹C:\Documents and Settings\All Users\Application

Data\Baofeng\StormPlayer\Profiles\md\

将此文件夹中的mat文件夹删除,新建同名文件(不要后缀),

设属性为只读。