基于FPGA的DDR2 SDRAM存储器用户接口设计

基于DDR2 SDRAM乒乓双缓冲的高速数据收发系统设计

基于DDR2 SDRAM乒乓双缓冲的高速数据收发系统设计刘杰;赛景波【摘要】在高速数据收发系统设计中,首先需要解决的问题是实时数据的高速缓存,然而FPGA内部有限的存储资源无法满足海量数据缓存的要求。

为了解决系统中海量数据的缓存问题,系统创新提出了一种基于DDR2 SDRAM的乒乓双缓冲设计方案。

方案设计了两路基于DDR2 SDRAM的大容量异步FIFO,通过FPGA内部选择逻辑实现两条通路间的乒乓操作,从而实现数据的高速缓存。

实验结果表明,基于DDR2 SDRAM的数据收发系统实现了每路512 Mbit的缓存空间和200 MHz的总线速率,解决了海量数据的高速缓存问题。

%In the high-speed data transceiver system design, the first problem to be solved is the real-time data cache,However,the limited memory resources of FPGA can not meet the requirements of massive data cache,To solve the problem of system cache huge amounts of data,the system proposed ping-pong double buffering innovative design based on the DDR2 SDRAM. Design of two-way high-capacity asynchronous FIFO based on DDR2 SDRAM, selection logic operations to achieve a ping-pong between the two paths through the FPGA to achieve the cached da-ta . Experimental results show that the Data transceiver system based on DDR2 SDRAM realized every road 512 Mbit cache space and 200 MHz of the bus rate and solved the problem of the huge amounts of data cache.【期刊名称】《电子器件》【年(卷),期】2015(000)003【总页数】5页(P650-654)【关键词】高速数据收发;乒乓双缓冲;DDR2 SDRAM技术;异步FIFO【作者】刘杰;赛景波【作者单位】北京工业大学电控学院,北京100022;北京工业大学电控学院,北京100022【正文语种】中文【中图分类】TN919.6高速数据传输是现代信号处理的基础,在雷达、通信、遥测遥感等技术应用领域得到了广泛的应用。

网络处理器中的DDRSDRAM控制器的设计与实现的开题报告

网络处理器中的DDRSDRAM控制器的设计与实现的开题报告1.课题背景随着网络技术的不断发展,网络设备的处理能力和稳定性要求越来越高。

网络处理器是一类专用于网络应用的高性能处理器。

网络处理器的核心是其内置的DDR SDRAM控制器。

DDR SDRAM控制器是网络处理器内部的一个重要模块,它完成了在处理器与外部存储器之间的数据传输、存储和读取等功能。

2.研究内容和目标本项目旨在探究基于FPGA的网络处理器中DDR SDRAM控制器的设计与实现方法。

主要研究内容包括:(1)DDR SDRAM控制器的架构和原理(2)DDR SDRAM控制器的时序控制和数据传输(3)FPGA中DDR SDRAM控制器的实现方法(4)性能测试和验证研究目标是实现一个高效的DDR SDRAM控制器,能够满足网络处理器的数据传输要求,并具有较高的性能。

3.研究方法和步骤本项目将采用以下研究方法和步骤:(1)阅读相关文献,了解DDR SDRAM控制器的基本原理和FPGA 中DDR SDRAM控制器的实现方法。

(2)根据DDR SDRAM的时序和数据传输要求,设计DDR SDRAM 控制器的架构和接口。

(3)使用Verilog语言实现DDR SDRAM控制器的模块。

(4)在FPGA上进行验证和性能测试。

(5)对实现的DDR SDRAM控制器进行性能测试和优化,以达到更高的性能。

4.研究意义和预期成果本项目的意义在于探究网络处理器中DDR SDRAM控制器的设计和实现方法,并且实现一个高效的DDR SDRAM控制器。

该控制器可用于各种网络设备中,提高网络设备的运行效率和稳定性。

预期成果包括:(1)DDR SDRAM控制器的设计与实现文档(2)基于 FPGA 的网络处理器中 DDR SDRAM 控制器模块的Verilog 代码(3)DDR SDRAM 控制器在 FPGA 上的验证和性能测试报告(4)论文发表和技术报告5.存在的问题和风险存在的问题:(1)DDR SDRAM控制器的设计和实现需要充分考虑时序和数据传输的要求,因此需要仔细分析和设计。

altera-ddr2-sdram-ip核参数设置及读写时序

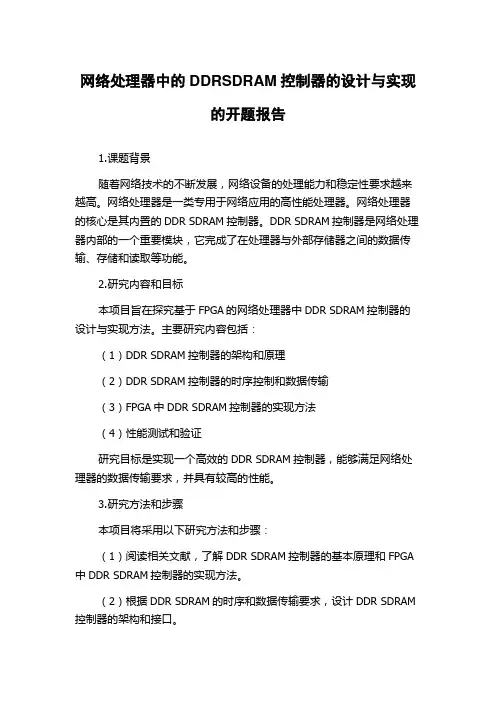

1、Uniphy 整体框图:2、存储控制器连接图PHY的时钟与复位信号1、pll_ref_clk:PLL参考时钟输入。

2、global_reset_n:全局复位信号,对PLL和PHY里的所有逻辑单元进行复位。

3、soft_reset_n:软复位信号,对phy复位,不对PLL复位。

当soft_reset_n为低时,输出的afi_reset_n信号也为低。

3、各个模块间的接口信号3、1控制器与用户接口间使用的Avalon相关信号线:下表是本地接口信号,在altera例化的IP核里,本地用户接口使用的是avalon总线➢Local_addr:指的是用户接口端的地址线,位宽计算方法如下:1)当只使用1pcs 外部存储器时:位宽=bank位宽+行位宽+列位宽-1;2)当使用多片片外存储器时:位宽=芯片位宽+bank位宽+行位宽+列位宽-1;计算位宽时减1 是因为用户数据接口宽度是memory侧数据宽度的两倍(memory侧是在时钟的上升和下降沿都收发数据,而用户侧只在时钟的上升沿收发数据,假如用户读写数据的时钟频率与memory侧的数据频率相同,那么,在时钟上升沿来时,用户侧发送的数据位宽应是memory 侧数据位宽的两倍)。

➢local_be:字节使能信号(用于向控制器写数据时),与memory侧的DM(data mask )信号作用一样,比如,当想使local_data的某8位数据无效,将local_be的对应位置0即可。

➢local_burstbegin:本地突发开始信号,当avalon总线开始突发读写时,将此信号置位‘1’。

(使用条件:本地接口是avalon总线,且memory侧的突发长度大于2)➢local_size:本地突发长度,即连续读或写的local_data个数。

长度不能超过ddr ip核里配置的maximum avalon- mm burst length的长度。

➢local_wdata:本地写数据。

基于FPGA的DDR2 SDRAM存储器用户接口设计

基于FPGA 的DDR2SDRAM 存储器用户接口设计杨斌,段哲民,高峰(西北工业大学电子信息学院,陕西西安710129)摘要:使用功能强大的FPGA 来实现一种DDR2SDRAM 存储器的用户接口。

该用户接口是基于XILINX 公司出产的DDR2SDRAM 的存储控制器,由于该公司出产的这种存储控制器具有很高的效率,使用也很广泛,可知本设计具有很大的使用前景。

本设计通过采用多路高速率数据读写操作仿真验证,可知其完全可以满足时序要求,由综合结果可知其使用逻辑资源很少,运行速率很高,基本可以满足所有设计需要。

关键词:DDR2SDRAM ;FPGA ;用户接口;DDR2SDRAM 存储控制器中图分类号:TN919.8文献标识码:A文章编号:1674-6236(2012)23-0147-03Design of DDR2SDRAM memory user interface based on FPGAYANG Bin ,DUAN Zhe -min ,GAO Feng(School of Electronic Information ,Northwestern Polytechnical University ,Xi ’an 710129,China )Abstract:The user interface of a DDR2SDRAM memory is implemented by using the powerful FPGA .The user interface is based on DDR2SDRAM memory controller produced by the XILINX company .The company produced such memory controllers with high efficiency and used widely .So that this design has great prospects .Through the simulation of multi -channel high -speed data read and write operations we can know that it can fully meet the timing requirements .Through the synthesis results we can know that the use of logic resources is very little ,run rate is high .It can basically meet all design needs.Key words:DDR2SDRAM ;FPGA ;user interface ;DDR2SDRAM memory controller收稿日期:2012-08-06稿件编号:201208014作者简介:杨斌(1981—),男,陕西佳县人,硕士研究生。

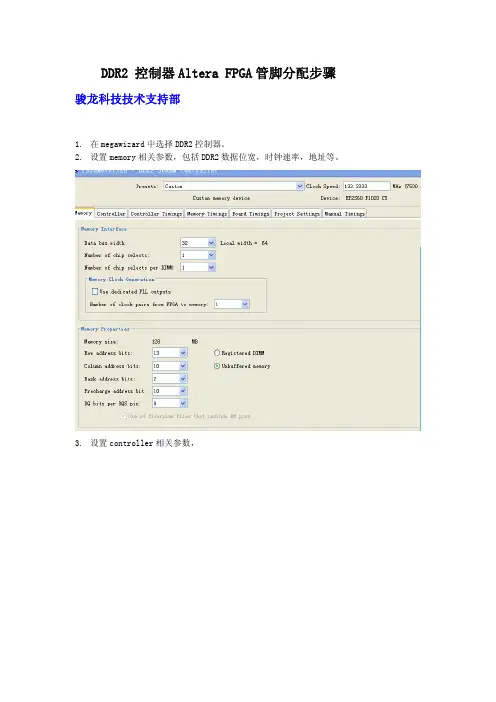

DDR2 控制器Altera FPGA 管脚分配步骤

DDR2 控制器Altera FPGA管脚分配步骤 骏龙科技技术支持部1.在megawizard中选择DDR2控制器。

2.设置memory相关参数,包括DDR2数据位宽,时钟速率,地址等。

3.设置controller相关参数,册。

5.设置board timing,这里的参数与PCB走线有关。

6.仿真模型设置,如果需要对生成的IP进行功能仿真,选上Generate Simulation Model。

7.生成DDR2控制器IP,在工程目录下可以查看到Altera 提供一个自测程序文件(_example_top.v),把_example_top.v设置为top level file。

8.在settings下的timequest timing analyzer处添加DDR2的时序约束文件SDC文件,如下图。

9.综合工程和管脚约束:综合完成后运行tcl scripts(在tools菜单下):选中_pin_assignments.tcl,然后点击RUN。

10.运行打开pin planner :assignments/pin planner11.分配dqs信号到想要的DQS管脚上,注意DQS group有X8/X9mode,X4/X5mode,X16/X18mode.12.指定DQ,ADDRESS和命令信号等到相应的IO bank,但DQ是跟随DQS的。

如图,只需把location指定到bank位置,不需指定到某个IO号。

13.位置指定完成后,全编译!14.全编译后查看是否有时序不满足,主要看信息栏,是否有报关键警告。

15.16.编译完成,时序也满足要求后运行:assignments/back-annotate assignments将之前指定到IObank的管脚反标到特定的IO管脚上。

再查看pin planner时,你将会发现上图变为下图所示:17.在assignments下选择Pin planner,倒出管脚文件,文件名后缀为*.csv.18.。

FPGA与DDR2SDRAM互联的信号完整性分析

Ke wo d : sg a itg i I p t tu Bufr no main p cf ain(BI ) mo e;hg —p e P itd y r s in l ne ry; n u/ p t t Ou f If r t S e i c t e o i o I S d l ih s e d r e Cic i n rut Bo r ad

联 。4 D 2 S AM共享地址线和控制 命令线 。数据线是 片 DR DR 点对点连接方 式 , 拓扑结构 简单。地址线和控制命令线的连接 存在一个拓扑结构 的选择问题。树形拓扑结构和菊花链式拓扑 结构 是两 种常见 的拓 扑结 构一 章从 仿真 的 角度 分析 上面 。文 两种不 同拓扑结 构下不同的端接方式对信 号完整性的影响 。

S DRAM. mp tr En i e rn n p ia in , 0 1 4 ( 9 : 5 — 6 . Co u e gn e i g a d Ap l to s 2 1 , 7 2 ) 1 8 1 0 c

Ab t a t Ths p p r d s r e h r be o in l ne r y b t e r x 5 n sr c : i a e e ci s t e p o lm f sg a itg i ewe n Vi e - a d DDR2 S b t t DRAM ne c n e t n I a ay e t i tro n ci . n lz s i o t s

o f PCB ouig. e e ul oft s o ott e a hie e nsr ts t a u h t e r s e e t i e d sg o i —p e ic i. r t Th rs t e t n pr oyp m c n d mo tae h ts c o y i f ci n h ve n t e in f hgh s e d cr ut h

基于FPGA的Verilog语言描述的SDRAM接口电路设计

基于FPGA的SDRAM存储器接口实现摘要随着信息科学的飞速发展,人们面临的信号处理任务越来越繁重,对数据采集处理系统的要求也越来越高。

单片机、DSP等微处理器内部RAM 有限,这就需要在微处理器的外部扩展存储器。

同步动态随机访问存储器具有价格低廉、密度高、数据读写速度快的优点,从而成为数据缓存的首选存储介质,在数据采集系统和图像处理系统等方面中有着重要和广泛的应用。

SDRAM 的读写逻辑复杂,最高时钟频率达100MHz 以上,普通单片机无法实现复杂的SDRAM 控制操作。

复杂可编程逻辑器件CPLD具有编程方便,集成度高,速度快,价格低等优点。

因此选用CPLD 设计SDRAM 接口控制模块, 简化主机对SDRAM 的读写控制。

通过设计基于CPLD 的SDRAM 控制器接口,可以在STM系列、ARM系列、STC系列等单片机和DSP等微处理器的外部连接SDRAM,增加系统的存储空间。

论文开始介绍了SDRAM接口设计研究的背景和研究的目的及意义,引出对SDRAM的研究,详细介绍了SDRAM的基本原理、内部结构、基本操作和工作时序,以及设计的重点及难点。

在这些理论基础上对SDRAM 接口进行模块化设计,了解设计中所使用的硬件和软件。

最后用Verilog语言在软件QuartusⅡ设计CPLD芯片,通过在硬件和软件上的调试基本实现了SDRAM接口的设计。

关键词SDRAM;接口;Verilog;CPLDThe Implementation of SDRAM MemoryInterface Based on the EPM570AbstractWith the rapid development of information science, people face more and more onerous task of signal processing, the requirements of data acquisition and processing system are getting higher and higher. Microprocessor such as single-chip microprocessor, DSP etc, their RAM is limited, which requires external expansion in the microprocessor memory. Synchronous Dynamic Random Access Memory has a low cost, high density, fast read and write data on the merits, thereby becoming the first choice for data cache storage medium, which paly an important role and widely used in the data acquisition system and image processing systems.SDRAM read and write logic is complex, the maximum clock frequency reaches above 100MHz, the ordinary microcontroller can not achieve complex SDRAM control operation. Complex programmable logic device has advantages such as programming convenience, high integrity, high speed and low cost etc. Therefore select CPLD to design control module of SDRAM interface , to simplify the host to read and write control of the SDRAM. Through the design of SDRAM controller interface based on CPLD, you can connect SDRAM in the external of STM series, ARM series, STC series single chip microprocessor and the DSP, increase system storage space.At the beginning of paper introduces the research background, research purpose and significance of the study of SDRAM interface design, leads to the study of SDRAM, detailed introduces information of SDRAM about the basic principles, the internal structure, the basic operation and timing of work, and the design emphasis and difficulty. Based on these theories, modularing the designof SDRAM interface, understanding hardware and software used in the design. Finally, it uses Verilog language in Quartus Ⅱsoftware to design CPLD chip, Through the hardware and the software realization SDRAM the commissioning of the basic design of the interface.Keywords SDRAM; Interface; Verilog; CPLD目录摘要 (I)Abstract (II)第1章绪论 (1)1.1 课题背景 (1)1.2 课题研究的目的及意义 (1)1.3 同步动态随机存储器简介 (2)1.4 论文的结构和框架 (3)第2章SDRAM的工作原理 (4)2.1 存储器的概述 (4)2.1.1 存储器的分类 (4)2.1.2 存储器的技术指标 (5)2.1.3 存储器的比较 (5)2.2 SDRAM的工作原理 (6)2.2.1 SDRAM存储的基本原理 (6)2.2.2 SDRAM的内部结构 (7)2.3 本章小结 (8)第3章SDRAM的基本操作 (9)3.1 SDRAM的基本操作 (9)3.1.1 芯片初始化 (9)3.1.2 行有效 (9)3.1.3 列读写 (10)3.1.4 读操作 (11)3.1.5 写操作 (12)3.2 SDRAM的工作特性 (13)3.2.1 模式寄存器的设置 (13)3.2.2 预充电 (14)3.2.3 刷新 (15)3.3 SDRAM接口设计的要求 (16)3.3.1 存储器接口解决数据存取的难点 (17)3.3.2 存储器接口在工作方式上的初步优化 (17)3.4 本章小结 (18)第4章系统结构及硬件设计 (19)4.1 SDRAM接口设计的整体结构 (19)4.1.1 控制接口模块 (19)4.1.2 CAS延迟模块 (20)4.1.3 突发长度模块 (22)4.1.4 地址转换模块 (22)4.2 EPM570芯片简介 (23)4.2.1 MAXⅡ系列芯片功能简介 (24)4.2.2 逻辑阵列 (25)4.2.3 全局时钟 (25)4.2.4 I/O端口结构 (26)4.3 MT48LC系列芯片简介 (26)4.4 本章小结 (28)第5章软件设计与实现 (30)5.1 利用QuartusⅡ进行设计的流程 (30)5.2 软件的设计 (31)5.2.1 Verilog语言的特点 (31)5.2.2 采用Verilog设计综合的过程 (32)5.2.3 SDRAM接口设计的仿真 (34)5.3 本章小结 (36)结论 (37)致谢 (38)参考文献 (39)附录A (41)附录B (46)附录C (51)第1章绪论1.1课题背景数据采集处理技术是现代信号处理的基础,广泛应用于雷达、声纳、软件无线电、瞬态信号测试等领域。

基于FPGA的DDR2 SDRAM控制器设计

基于FPGA的DDR2SDRAM控制器设计钱素琴,刘晶华(东华大学信息科学与技术学院,上海,201600)摘要:基于高速数据传输与存储的数据釆集记录仪对缓存模块高性能的需求,选择了读写速度快、低成本、大容量、运行稳定的DDR2SDRAM作为本地存储器,在其存储寻址原理和IP核的读写控制逻辑的基础上,借助硬件描述语言设计了一个DDR2存储控制器方案。

在Intel的FPGA Cyclone IV系列开发板上进行了整体方案的功能验证,完成了用户接口和控制器之间的多数据宽度、多突发长度的高效数据传输和读写操作,在166.7MHz时钟频率下实现了稳定读写的目标。

关键词:FPGA;DDR2SDRAM;IP核Design of DDR2SDRAM controller based on FPGAQian Suqin,Liu Jinghua(College of information science and technology,Donghua University,Shanghai,201600) Abstract;Based on the requirement of high-speed data transmission and storage data acquisition recorder for high performance of cache module,DDR2SDRAM with high read-write speed,low cost, large capacity and stable operation is selected as the local memory.Based on its storage addressing principle and the read-write control logic of IP core,a DDR2storage controller scheme is designed with the help of hardware description language.The functional verifiestion of the overall scheme is carried out on the FPGA cyclone IV series development board of Intel.The efficient datQ transmission and read-write operation of multipie data widths and burst lengths between the user interface and the cont r oller are comple t ed.The st a ble read-wr ite t a rge t is achieved a/t166.7MHz clock frequency. Keywords:FPGA;DDR2SDRAM;IP coreo引言随着数据采集系统的发展,应用于图像采集和数据传输等领域的产品对存储器的速度要求越来越高。

基于FPGA的DDR2存储器控制器设计_河北科技大学.

毕业设计学生姓名:洪雷学号: 09xxxxxxxx 专业:电子科学与技术题目:基于FPGA的DDR2存储器控制器设计指导教师:安国臣(讲师评阅教师:武瑞红(副教授2013年6月毕业设计中文摘要随着消费电类电子产品以及便携式通讯产品向多功能、高性能和低功耗方向的飞快发展,而随之带来的是对大量的数据处理,而产品的系统对其主要的存储设备的要求也越来越高。

目前,DDR2凭着其及其高的数据传输速率和低廉的成本则越来越多的被用到一些高档类的消费类电子和便携式产品中。

对DDR2 SDRAM的控制器处理的设计变得也就非常有必要。

使用FPGA技术设计数字电路,不仅可以简化设计过程,而且还可以减低整个系统的体积和成本,增加系统的可靠性。

本次设计则使用Altear公司的Cyclone V 代器件,经行开发的最小系统。

本次设计使用的是Mircon公司的MT47系列的芯片,借助Altera公司提供的IP 核所自动生成PHY接口。

由于DDR2的读写驱动的要求,多次设计了电压的要求。

本文对DDR2 SDRAM基本结构和原理进行了简单的介绍。

并且阐述基于FIFO和PHY接口的DDR2设计方法。

关键词DDR2 FPGA 存储器控制器 FIFO毕业设计外文摘要Title DDR2 Memory Controller Design based on FPGAAbstractAs consumer electric class electronic products and portable communication products to multi-functional, high performance and low power consumption direction of rapid development, and then brings about a lot of data processing, the product of the system to the main storage device requirements more and more higher. At present, the DDR2 with its and high data transfer rate and low cost are more and more used in some high-end consumer electronics and portable products. Processing of DDR2 SDRAM controller design becomes and is very necessary.Digital circuit design using FPGA technology, not only can simplify the design process, but also can reduce the size and cost of the whole system, increase the reliability of the system. This design USES Altear company Cyclone V generation device, the smallest system development. This design USES the Mircon MT47 series chips, and IP core provided by Altera corporation how can automatically generate the PHY interface. Driven requirements due to DDR2, speaking, reading and writing, and design the voltage requirements for many times.in this paper, the basic structure and principle of DDR2 SDRAM has carried on the simple introduction. And in this paper, the DDR2 design method based on FIFO and PHY interfaceKey Words DDR2 FPGA memory controlle FIFO目录1 绪论 (12 动态随机存储器 (32.1 同步动态随机存储器原理与结构 (32.2 双倍动态随机存储器原理与特点 (32.3 DDR2随机存储器的简介 (43 可编程逻辑器件原理 (73.1 FPGA原理 (73.2 FPGA结构 (73.3 FPGA器件开发的优点 (94 外围电路设计 (114.1芯片的选择和介绍 (114.2 FPGA电源设计 (154.3 FPGA时钟和复位设计 (164.4 FPGA的配置设计 (175 软件设计与仿真 (185.1 FPGA的设计开发流程 (18 5.2 系统设计软件介绍 (195.3 VHDL语言的介绍 (195.4 系统设计 (20结论 (29致谢 (30参考文献 (311 绪论随着大规模、甚大规模的集成电路的设计技术的飞速发展,科技的日益更新,跟随而来的是各种的芯片的弄能不段的变复杂,而同时,数字产品例如掌上电脑、网络设备、音频设备、高清电视等,对高性能的内存的需求也越来越高。

基于FPGA的DDR2 SDRAM数据存储研究

21 D R . D 2系统 架构 功能定 义

1 D R D A 概 述 D 2S R M

D R ( obeD t R t 2 S R M 器 件 是 由 D 2 D u l a ae ) D A a JD C 电子设备 工程 联 合 委员 会 ) 行 开发 的新 EE( 进

摘

要: D 2S R M具有存取速度快, D R D A 容量大等特点, 它在 内存、 显存及数据暂存方面有着广

泛 的应 用。本 文基 于 X l xV n x x0 P A对 D R D A 数 据存 取 做 了较 为 详 细的探 in ie5 F 7 T F G i D 2S R M

沿 同时进行数 据传输 的基本 方式 , D R 但 D 2内存 却

拥有两倍于上一代 D R内存预读取能力( i数 D 4b t 据读预取) 。即 D R D 2内存每个时钟能够以4 倍外

收 稿 日期 : 09一l 4 20 2—1

同而不同 ,ie Vrx t 5内部是 F O形式的接 口。 I F () 2 控制逻辑层

第2 7卷 第 2期

21 年 00 4月

贵州大学学报( 自然科 学版)

Ju a uzo n esy( a rl c ne) or l f i uU i r t N t a Si cs n oG h v i u e

Vo.2 o 1 7 N .2 A r 00 p .2 1

准, 与用于 写入 的数据 中心 对准 。 对 D R D A 器 件 的读 取 和写 入 访 问 为 D 2S R M

4 l) F G 0n ,P A芯片的集成度成倍提高 , n 时钟频率

已经达 到数吉 赫兹 。 数 据 采集 系统 采样 频 率 的不 断 提高 对数 据 存 储也提 出 了越 来越高 的要求 , 高速 采样 和大容量 持 续存储 已经成 为存储 领域 的一个发展 方 向 , 并且 已

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA的DDR2 SDRAM存储器用户接口设计

现如今,随着电子技术和通信技术的飞速发展,电路设计对存储器的要求也越来越高,其主要体现在对存储器的容量和存储操作速度两个方面。

鉴于此,JEEDEC定义了DDR2SDRAM技术标准,其以低能耗、低发热量、高密度以及高频率成为了现代存储技术的核心器件。

DDR2自身的工作频率可以达到677 MHz,几乎可以满足所有电路设计的要求。

而这也就使得整个电路设计的频率瓶颈出现在了用户设计部分与DDR2存储器之间的逻辑上,主要是因为DDR2本身的结构特性使得DDR2的操作时序很复杂苛刻。

而这之间的部分又主要分为DDR2存储控制器和用户接口部分。

现如今已经有了很多的厂家在生产DDR2存储控制器,其中以XILINX公司设计的DDR2存储控制器效率最高使用最为广泛,该存储控制器的单独操作频率非常高,完全不会影响DDR2存储器的操作,因此这又将整个电路系统的频率瓶颈缩小到了用户接口部分。

用户接口的设计有很多种方案,而FPGA以其高速度、丰富的片上资源、灵活的设计以及简单方便的调试特性成为了用户接口设计的必然选择。

1 DDR2存储器应用的一般模式

DDR2存储器一般作为片上系统的辅助器件,其应用的一般模式如图1所示。

本文引用地址:/article/189601.htm

用户设计部分是整个片上系统的核心,主要是完成系统要实现的所有任务,对整个系统进行整体的调度和控制。

用户接口部分主要是接收用户设计部分传送的操作数据,以及与这些操作数据相对应的控制指令,之后将这些数据进行整理,然后按照一定的时序要求发出。

如果操作的是多路不同种类的数据时,则还要将这多路数据进行仲裁,保证所有数据都不会被发错或者丢失。

DDR2存储控制器主要是接收用户接口部分发给的特定的读写操作控制指令和已经整理好的数据,将这些指令进行进一步的解析,最后将经过解析产生的那些DDR2存储器硬件可以识别的信号以及与读写

有效信号有关的写数据输出给DDR2,读数据从DDR2存储器中读回。

DDR2存储器主要是按照读写有效信号将要处理的数据进行读出和写入操作。

2 用户接口设计

用户接口设计的原理如图2所示。

其主要包括写数据通路、读数据通路以及接口控制3大模块。

写数据通路按照输入存储器路数的不同分为以下两种:只有一路数据输入时只有控制模块和地址计算模块;当有多路数据输入时,不仅有控制模块和地址计算模块还有仲裁模块。

控制模块主要是将输入的数据进行一次2乒乓操作的缓存,再将缓存后的数据拼接成64位数据,之后在仲裁模块允许该路数据写操作时将这些数据发送给仲裁模块。

地址计算模块主要是计算每路信号的每个数据的存储地址,由于每路数据都是不同数据类型的,因此必须要将每路地址的计算与其数据严格地对应起来,要正确的保存好每次写数据操作的地址,以便产生下次操作的正确地址。

仲裁模块主要是保证多路数据对DDR2控制器的访问可以正确进行。

DDR2存储控制器采用的是高效的burst操作(对于本设计采用的是burst为30),也就是在一次读操作或者是写操作的过程中要连续处理burst长度所定义的数据个数(在本设计中每次读写操作要完成30

个64位数据的读出或写入)。

这样在一次请求操作被响应之后,在接下来的15个周期只能传输这路数据,在将这路数据传输完成之前不能再响应其他路数据的操作请求,这样就有可能导致其他多路数据的操作请求在本次操作结束之后同时到来,这样就要求仲裁模块必须要很好地控制每路数据之间的操作顺序,使得多路信号对存储器的访问机率大致相同。

鉴于此,本设计中采用了轮询的机制。

读通路和写通路基本类似,只是读通路不需要对数据进行拼接,相反的需要对数据进行拆分,将DDR2存储器输出的64位数据拆分成原始输入时的数据,并将这些数据存入读操作端的FIFO中。

这样在外部请求数据数据时,若要求的数据已经在FIFO中则直接将数据输出即可,不需要再向DDR2存储控制器请求,若要求的数据还没在FIFO 中则要先向DDB2存储控制器请求数据,将数据存入该FIFO,之后再将FIFO中本次要求读出的数据输出。

接口控制模块主要是接收写通路的写操作请求信号以及它对应的地址信号和数据信号,读通路的读操作请求信号以及它对应的地址信号,并将这些信号按照DDR2存储控制器的时序要求发送给DDR2存储控制器,之后再接收DDR2存储控制器发回的读数据。

DDR2存储控制器的读写操作时序如图3所示。

本文引用地址:/article/189601.htm

3 仿真验证

对本设计的验证采用的是6路8位数据以27 MHz的频率写入读出操作。

对其进行整体读写仿真的时序结果如图4所示。

由该图可知,当将数据写入到DDR2中的数量到达一定程度时,开始向向外读出数据,写入的时序和读出的时序整体上符合设计要求。

对读写操作的具体仿真时序如图5所示。

由该图可知,写操作时的各种控制指令以及地址和数据的发送都是完全正确的;读操作时的各种控制指令以及地址和数据的发送也是完全正确的。

对该设计采用XILINX Spartan6系列的xc6slx16—2ftg256器件进行综合,其结果如图6所示。

由该图可知该设计使用的逻辑资源相当小,其中寄存器还不到总数的百分之一,查找表也只使用了总数的百分之二。

4 改进

在一般情况下,DDR2的硬件存储速率很快,其会等待存储控制器发送下一个操作指令,而DDR2存储控制器的操作指令是由用户接口发

出的,因此可以提出以下改进方案。

可以在存储控制器前端添加多个FIFO,将与操作有关的所有指令、地址以及数据对应起来存入这些FIFO中,这样等到DDR2存储控制器将本次操作完成之后自动将所有FIFO中与下次操作有关的指令和数据读出,直接进行下一次DDR2的操作,与此同时用户接口部分在这些FIFO没满的情况下,还仍然向这些FIFO中写入要操作的所有指令和数据。

5 结论

由以上仿真结果可知,该设计在整个设计读写频率很高时仍然可以保证所有数据的正确操作,不会存在数据的丢失或者错误。

由以上综合结果可知,该设计占用的FPGA片上资源很少,运行频率很高,基本可以满足所有设计的要求。

因此可知,该设计具有很高的工作频率,解决了电路设计中DDR2存储器读写操作频率的瓶颈问题,使得整个设计的工作效率得到很大的提高。