AD转换verilog程序

Verilog中的一些语法和技巧

Verilog中的⼀些语法和技巧1、.2、.3、Reg型的数据类型默认初始值为X。

reg型数据可以赋正值也可以赋负值,但是当⼀个reg型数据是⼀个表达式的操作数的时候,他的值被当做⽆符号数及正值。

4、在数据类型中?和Z均表⽰⾼阻态。

5、Reg型只表⽰被定义的信号将⽤在“always”模块内,并不是说reg型⼀定是寄存器或触发器的输出。

虽然reg型信号常常是寄存器或触发器的输出但是并不⼀定总是这样。

6、Verilog语⾔中没有多维数组的存在。

Memory型数据类型是通过扩展reg型数据的弟⼦和范围来⽣成的。

其格式如下reg[n-1:0]存储器名[m-1:0];7、在除法和取余的运算中结果的符号和第⼀个操作数的符号位是相同的。

8、不同长度的数据进⾏运算:两个长度不同的数据进⾏位运算时,系统会⾃动地将两者按有端对齐,位数少的操作数会在相应的⾼位⽤0填满以便连个操作数安慰进⾏操作。

9、= = =与!= = =和= =与!= =的区别:后者称为逻辑等是运算符,其结果是2个操作数的值决定的。

由于操作书中某些位可能不定值x和⾼阻态z结果可能是不定值x。

⽽ = = =和!= = =运算符对操作数的⽐较时对某些位的⾼阻态z和不定值x也进⾏⽐较,两个操作数必须完全⼀致,其结果才是1,否则是0.10、⾮阻塞和阻塞赋值⽅式:⾮阻塞赋值⽅式(如a<=b)上⾯语句所赋得变量值不能⽴即被下⾯语句所⽤,(2)快结束后才能完成这次赋值操作 3在编写克综合的时序逻辑模块时这是最常⽤的赋值⽅法。

阻塞赋值(如a=b)赋值语句执⾏完后,块才结束 2 b的值在赋值语句完成后⽴即执⾏ 3在时序逻辑使⽤中,可能产⽣意想不到的结果。

11、模块的描述⽅式:(RTL为寄存器传输级描述)“(1)数据流描述⽅式:数据流⾏描述主要⽤来描述组合功能,具体⽤“assign”连续赋值语句来实现。

分为两种a、显式连续赋值语句;连线型变量类型[连线型变量为快]连线型变量名Assign #(延时量)连线型变量名=赋值表达式;显式连续赋值语句包含了两条语句;第⼀条是对连线型变量的进⾏类型说明的说明语句;第⼆句是对这个已得到声明的连线型变量进⾏连续赋值语句。

verilog buf用法

verilog buf用法Verilog中的buf用法Verilog是一种硬件描述语言,用于描述数字电路。

buf是Verilog中的一个重要关键字,用于实现信号的缓冲。

在本文中,我们将深入探讨buf的用法及其在数字电路设计中的作用。

1. buf的基本概念和语法在Verilog中,buf是一个简单的缓冲器,用于驱动信号到其他模块或输出端口。

它可以连接到一个信号源,并将信号传递给目标模块或输出端口,起到一个“信号传递”的作用。

buf的语法如下所示:```verilogbuf <信号名称或端口名称> (<信号或端口>);```其中,信号名称或端口名称是buf要连接的信号源、目标模块或输出端口的名称。

2. buf的工作原理当buf接收到一个输入信号时,它会将信号转发给目标模块或输出端口。

buf不对信号进行任何处理或改变,只是将信号传递给其他地方。

这使得buf成为一个很有用的工具,可以在数字电路中实现信号的传输和连接。

3. buf的应用场景buf在数字电路设计中有多种应用场景,下面是其中几个常见的应用:3.1 输入/输出缓冲buf可以用作输入/输出缓冲器,用于将信号从输入端口传输到输出端口。

例如,在设计中存在一个输入端口A和一个输出端口B,我们可以使用buf来实现从A到B的信号传递。

具体实现如下:```verilogbuf buf_inst (.A (input_signal),.B (output_signal));```其中,input_signal是输入端口A的信号,output_signal是输出端口B的信号。

3.2 信号驱动buf还可以用于信号驱动,帮助实现复杂的电路结构。

例如,在设计中存在一个复杂的模块C,它需要接收来自模块A和模块B的信号,并生成一个输出信号。

我们可以使用buf来分别连接模块A和模块B的输出信号到模块C的输入信号。

具体实现如下:```verilogbuf buf_inst1 (.A (moduleA_output),.B (moduleC_input));buf buf_inst2 (.A (moduleB_output),.B (moduleC_input));```其中,moduleA_output和moduleB_output分别是模块A和模块B的输出信号,moduleC_input是模块C的输入信号。

复杂数字逻辑的VerilogHDL设计方法HDLV

模块C

模 块A1

模 块A2

模 块A3

模 块B1

模 块B2

模 块C1

模 块C2

电路图 设计文件

电路功能 仿真

有问题

没问题

HDL 设计文件

HDL 功能仿真

没问题 HDL 综合

有问题

确定实现电路 的具体库名

与实现逻辑的物 理器件有关的工艺 技术文件

优 化 、布 局 布 线

布线后门级仿真 没问题

电路制造工艺文件 或 FPGA 码 流 文 件

- 软件只能提高系统的灵活性能 - 军用系统的实时、高可靠、低功耗要求 - 系统的功能专一,但对其各种性能要求极高 - 降低系统的设计和制造成本

怎样设计如此复杂的系统?

• 传统的设计方法: - 查用器件手册;

- 选用合适的微处理器和电路芯片; - 设计面包板和线路板; - 调试; - 定型; - 设计复杂的系统(几十万门以上)极其困难。

程就是。

• 常用的编程语言:C、Pascal、Fortran、Basic

或汇编语言。

计算机体系结构和硬线逻辑 的基本概念

• 计算机体统结构:是一门讨论和研究通

用的计算机中央处理器如何提高运算速度 性能的学问。

• 硬线逻辑: 由与门、或门、非门、触发

器、多路器等基本逻辑部件造成的逻辑系 统。

数字信号处理系统的分类

实时数字信号 处理系统实现中存在的技术难点

和解决办法

电路实现的两个方向: • FPGA • 专用集成电路

实时数字信号 处理系统实现中存在的技术难点

和解决办法

用于信号处理的 FPGA 和专用集成 电路(ASIC)设计的方法: Verilog HDL建模、仿真、综合和全

verilog数学函数

verilog数学函数在Verilog中,有一些数学函数可以用于进行数值计算和转换。

以下是一些常见的Verilog数学函数的介绍。

3. $sqrt(x)$ 函数:这个函数返回一个数的平方根。

它接受一个输入参数x,并返回$\sqrt{x}$的结果。

例如,$sqrt(9)$的结果将是34. $pow(x,y)$ 函数:这个函数返回一个数x的y次幂。

它接受两个输入参数x和y,并返回$x^y$的结果。

例如,$pow(2,3)$的结果将是85. $loor(x)$ 函数:这个函数返回一个小于或等于x的最大整数。

它接受一个输入参数x,并返回最大整数值。

例如,$loor(2.8)$的结果将是26. $ceil(x)$ 函数:这个函数返回一个大于或等于x的最小整数。

它接受一个输入参数x,并返回最小整数值。

例如,$ceil(2.1)$的结果将是37. $abs(x)$ 函数:这个函数返回一个数的绝对值。

它接受一个输入参数x,并返回x的绝对值。

例如,$abs(-5)$的结果将是58. $sin(x)$ 函数:这个函数返回一个角度的正弦值。

它接受一个输入参数x,表示以弧度为单位的角度,并返回sin(x)的结果。

例如,$sin(0)$的结果将是0。

9. $cos(x)$ 函数:这个函数返回一个角度的余弦值。

它接受一个输入参数x,表示以弧度为单位的角度,并返回cos(x)的结果。

例如,$cos(\pi)$的结果将是-110. $tan(x)$ 函数:这个函数返回一个角度的正切值。

它接受一个输入参数x,表示以弧度为单位的角度,并返回tan(x)的结果。

例如,$tan(\pi/4)$的结果将是1这些函数在Verilog中可以用于进行数值计算和数值转换。

可以在Verilog代码中直接调用这些函数来进行数学运算,从而简化数学计算的实现。

这些函数通常用于数值处理和模拟电路设计,以及其他需要进行数学运算的应用中。

verilog readmemh使用

verilog readmemh使用Verilog是一种硬件描述语言,用于描述数字电路和系统的行为。

在Verilog中,使用readmemh指令可以从文件中读取十六进制格式的数据并将其加载到内存中。

这篇文章将详细介绍如何在Verilog中使用readmemh指令以及它的作用和用法。

我们需要了解readmemh指令的基本语法和用法。

readmemh指令的语法如下:```verilogreadmemh(filename, memory);```其中,filename是要读取的文件名,memory是要将数据加载到的内存。

readmemh指令将从指定的文件中读取十六进制格式的数据,并将其加载到内存中。

文件中的每一行都包含一个十六进制数,readmemh指令会逐行读取文件,并将每个数值存储到内存中的相应位置。

下面是一个使用readmemh指令的例子:```verilogmodule test;reg [7:0] memory [0:15];initial begin$readmemh("data_file.txt", memory);endendmodule```在上面的例子中,我们定义了一个8位宽的内存数组memory,大小为16。

然后,在initial块中使用readmemh指令,将data_file.txt文件中的数据加载到memory中。

readmemh指令会按照文件中数据的顺序,将每个十六进制数依次存储到memory数组中。

在上面的例子中,data_file.txt文件中的第一个数将存储在memory[0]中,第二个数将存储在memory[1]中,依此类推。

使用readmemh指令可以方便地将大量初始化数据加载到内存中,这在设计复杂的数字电路时非常有用。

通过在文件中存储数据,我们可以轻松地对其进行修改和扩展,而不需要修改Verilog代码。

除了readmemh指令,Verilog还提供了其他读取文件的指令,如readmemb。

verilog的延时赋值语法

verilog的延时赋值语法

Verilog是一种硬件描述语言,通常用于设计数字电路。

在Verilog中,延时赋值语法是一种重要的赋值方式,用于指定不同延迟时间的信号

赋值。

延时赋值语法的基本形式是:

<variable> = #<delay> <value>;

其中,<variable>是要赋值的信号名称,<delay>是延时时间(以仿

真时间为单位),<value>是要赋给信号的值。

举个例子,下面的代码片段演示了延时赋值语法的使用:

wire clk;

reg r = 0;

always begin

#10 clk = ~clk;

end

always@(posedge clk) begin

#5 r = ~r;

end

上述代码中,使用了两个always块来定义模块的行为。

第一个always块通过十个时钟周期交替将时钟信号clk赋值为0和1。

第二个always块在clk信号上升沿触发时,将寄存器r的值取反,并延迟5个时钟周期。

需要注意的是,延迟时间只在仿真时有意义,在实际 FPGA 中运行时不会生效。

因此,延时赋值的使用需要谨慎,需要充分考虑系统的实际响应时间,以避免产生意想不到的结果。

总的来说,Verilog中的延时赋值语法是设计数字电路时极为有用的一种机制,能够准确地指定信号在不同延迟时间内的赋值,从而实现更加复杂的功能。

但需要注意的是,它也容易导致设计出现不可预测的行为,因此需要谨慎使用。

SPI总线接口的verilog的实现

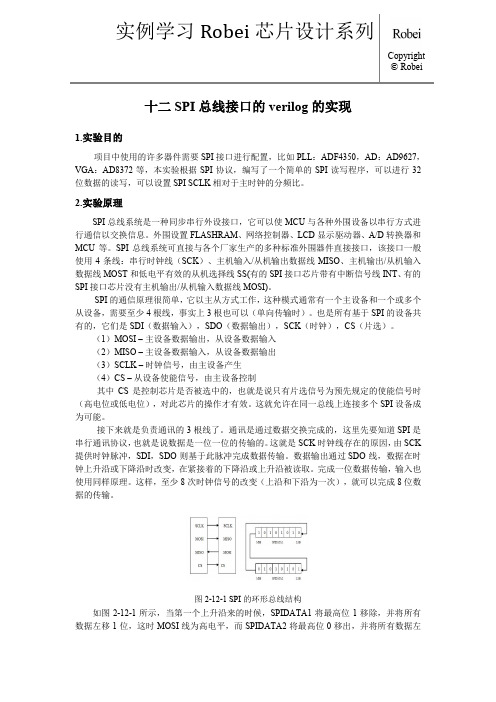

十二SPI总线接口的verilog的实现1.实验目的项目中使用的许多器件需要SPI接口进行配置,比如PLL:ADF4350,AD:AD9627,VGA:AD8372等,本实验根据SPI协议,编写了一个简单的SPI读写程序,可以进行32位数据的读写,可以设置SPI SCLK相对于主时钟的分频比。

2.实验原理SPI总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。

外围设置FLASHRAM、网络控制器、LCD显示驱动器、A/D转换器和MCU等。

SPI总线系统可直接与各个厂家生产的多种标准外围器件直接接口,该接口一般使用4条线:串行时钟线(SCK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOST和低电平有效的从机选择线SS(有的SPI接口芯片带有中断信号线INT、有的SPI接口芯片没有主机输出/从机输入数据线MOSI)。

SPI的通信原理很简单,它以主从方式工作,这种模式通常有一个主设备和一个或多个从设备,需要至少4根线,事实上3根也可以(单向传输时)。

也是所有基于SPI的设备共有的,它们是SDI(数据输入),SDO(数据输出),SCK(时钟),CS(片选)。

(1)MOSI –主设备数据输出,从设备数据输入(2)MISO –主设备数据输入,从设备数据输出(3)SCLK –时钟信号,由主设备产生(4)CS –从设备使能信号,由主设备控制其中CS是控制芯片是否被选中的,也就是说只有片选信号为预先规定的使能信号时(高电位或低电位),对此芯片的操作才有效。

这就允许在同一总线上连接多个SPI设备成为可能。

接下来就是负责通讯的3根线了。

通讯是通过数据交换完成的,这里先要知道SPI是串行通讯协议,也就是说数据是一位一位的传输的。

这就是SCK时钟线存在的原因,由SCK 提供时钟脉冲,SDI,SDO则基于此脉冲完成数据传输。

数据输出通过 SDO线,数据在时钟上升沿或下降沿时改变,在紧接着的下降沿或上升沿被读取。

Verilog HDL数字设计教程(贺敬凯)第7章

图7-2 跑马灯模块端口框图

第7章 Verilog HDL可综合设计举例

4. 代码分析 【例7-1】 设计源码。 module paomadeng(rst,clk,sel,led); input rst,clk; input[1:0] sel; output[7:0] led; reg[7:0] led;

第7章 Verilog HDL可综合设计举例

end end default: ; endcase

end

endmodule

第7章 Verilog HDL可综合设计举例

程序说明:

(1) case语句用于选择三种模式。当case表达式中的sel为

2'b00时选择模式1,为2'b01时选择模式2,为2'b11时选择模式3。

第7章 Verilog HDL可综合设计举例

if(cnt8>=7) cnt8<=0; else cnt8<=cnt8+1; SM_in <= 2*cnt8+1; //生成待显示数据为1, 3, 5, ... SM_B=1<<cnt8; //生成位选信号

end

endmodule 例7-4是扫描显示的顶层模块。其中:clk是扫描时钟; SM_7S为7段控制信号,由高位至低位分别接g、f、e、d、c、b、 a 7个段;SM_B是位选控制信号,接图7-6中的8个选通信号K1、 K2、…、K8。

第7章 Verilog HDL可综合设计举例

2'b11: begin

if(!dir) begin

if(cnt3==0) begin led_r=8'b00000001;led_r1=8'b10000000;end else begin led_r=(led_r<<1)| led_r; led_r1=(led_r1>>1)| led_r1; end led<=led_r | led_r1; if(cnt3==3) begin dir<=~dir; end cnt3<=cnt3+1; end else

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

// 16-bit Analogue-Digital Converter

//

// +-----------------------------+

// | Copyright 1996 DOULOS |

// | designer : Tim Pagden |

// | opened: 7 Jun 1996 |

// +-----------------------------+

`timescale 1 ns / 1 ps

module ADC_16bit (analog_in,digital_out);

parameter conversion_time = 25.0, // conversion_time in ns

// (see `timescale above)

charge_limit = 1000000; // = 1 million

input[63:0] analog_in;

// double-precision representation of a real-valued input port; a fix that enables

// analog wires between modules to be coped with in Verilog.

// Think of input[63:0] <variable> as the equivalent of MAST's electrical. output[15:0] digital_out;

reg[15:0] delayed_digitized_signal;

reg[15:0] old_analog,current_analog;

reg[4:0] changed_bits;

reg[19:0] charge;

reg charge_ovr;

reg reset_charge;

/* SIGNALS:-

analog_in = 64-bit representation of a real-valued signal

analog_signal = real valued signal recovered from analog_in

analog_limited = analog_signal, limited to the real-valued input range of the ADC

digital_out = digitized 16bit 2's complement quantization of

analog_limited

*/

/* function to convert analog_in to digitized_2s_comp_signal.

Takes analog_in values from (+10.0 v - 1LSB) to -10.0 v and converts them to values from +32767 to -32768 respectively */

function[15:0] ADC_16b_10v_bipolar;

parameter max_pos_digital_value = 32767,

max_in_signal = 10.0;

input[63:0] analog_in;

reg[15:0] digitized_2s_comp_signal;

real analog_signal,analog_abs,analog_limited;

integer digitized_signal;

begin

analog_signal = $bitstoreal (analog_in);

if (analog_signal 0.0)

begin

analog_abs = -analog_signal;

if (analog_abs > max_in_signal)

analog_abs = max_in_signal;

analog_limited = -analog_abs;

end

else

begin

analog_abs = analog_signal;

if (analog_abs > max_in_signal)

analog_abs = max_in_signal;

analog_limited = analog_abs;

end

if (analog_limited == max_in_signal)

digitized_signal = max_pos_digital_value;

else

digitized_signal = $rtoi (analog_limited * 3276.8);

if (digitized_signal 0)

digitized_2s_comp_signal = 65536 - digitized_signal;

else

digitized_2s_comp_signal = digitized_signal;

ADC_16b_10v_bipolar = digitized_2s_comp_signal;

end

endfunction

/* This function determines the number of digital bit changes from sample to sample; can be used to determine power consumption if required.

Task power_determine not yet implemented */

function[4:0] bit_changes;

input[15:0] old_analog,current_analog;

reg[4:0] bits_different;

integer i;

begin

bits_different = 0;

for (i=0;i=15;i=i+1)

if (current_analog[i] != old_analog[i])

bits_different = bits_different + 1;

bit_changes = bits_different;

end

endfunction

/* Block to allow power consumption to be measured (kind of). Reset_charge is used to periodically reset the charge accumulated value (which can be used to determine current consumption and thus power consumption) */

always @ (posedge reset_charge)

begin

charge = 0;

charge_ovr = 0;

end

/* This block only triggered when analog_in changes by an amount greater than 1LSB, a crude sort of scheduler */

always @ (ADC_16b_10v_bipolar (analog_in))

begin

current_analog = ADC_16b_10v_bipolar (analog_in); // digitized_signal changed_bits = bit_changes (old_analog,current_analog);

old_analog = current_analog;

charge = charge + (changed_bits * 3);

if (charge > charge_limit)

charge_ovr = 1;

end

/* Block to implement conversion_time tpd; always block use to show difference between block and assign coding style */

always

# conversion_time delayed_digitized_signal = ADC_16b_10v_bipolar (analog_in);

assign digital_out = delayed_digitized_signal;

endmodule。