嵌入式系统讲义4_07

合集下载

嵌入式系统讲课文档

嵌入式系统

第一页,共34页。

What is this?

The Von Neumann Architecture

第二页,共34页。

What is Embedded ?

第三页,共34页。

什么是嵌入式系统?

计算机 ……

,假装自己不是计算机

(Stephen A. Edwards)

第四页,共34页。

为什么要嵌入?

办公设备、建筑物设备、制造和流程控制、医疗、监视、维生设备、交通运输、 通讯业、银行金融业、测试及诊断系统、其他…

Embedded systems in everything

第十页,共34页。

应用范例 LEGO 机器人

• The LEGO Mindstorms® is a robotic building system consisting of

almost twice as fast

Wii

l ATI “Hollywood” processor handles the 遙控

graphics

SYNC. 按鍵

DC in

l Runs at 243 MHz

GFX

數位信號處理 DSP

Hollywood

圖表記憶體 3MB

內部儲存記憶體 24MB

Wi-Fi 區塊

Operating system: MAC OS X GSM: Quad-band Wireless data: WiFi, EDGE, Bluetooth

Camera: 2 Mega pixel Audio and video playback

Talk time: 8 hrs Standby time: 250 hrs

Microprocessor: TI OMAP (ARM+DSP)

第一页,共34页。

What is this?

The Von Neumann Architecture

第二页,共34页。

What is Embedded ?

第三页,共34页。

什么是嵌入式系统?

计算机 ……

,假装自己不是计算机

(Stephen A. Edwards)

第四页,共34页。

为什么要嵌入?

办公设备、建筑物设备、制造和流程控制、医疗、监视、维生设备、交通运输、 通讯业、银行金融业、测试及诊断系统、其他…

Embedded systems in everything

第十页,共34页。

应用范例 LEGO 机器人

• The LEGO Mindstorms® is a robotic building system consisting of

almost twice as fast

Wii

l ATI “Hollywood” processor handles the 遙控

graphics

SYNC. 按鍵

DC in

l Runs at 243 MHz

GFX

數位信號處理 DSP

Hollywood

圖表記憶體 3MB

內部儲存記憶體 24MB

Wi-Fi 區塊

Operating system: MAC OS X GSM: Quad-band Wireless data: WiFi, EDGE, Bluetooth

Camera: 2 Mega pixel Audio and video playback

Talk time: 8 hrs Standby time: 250 hrs

Microprocessor: TI OMAP (ARM+DSP)

嵌入式系统基础知识

8

通用计算机与嵌入式系统对比

特征 形式和类型

•

通用计算机 看得见的计算机。 按其体系结构、运算速度 和结构规模等因素分为大 、中、小型机和微机。 通用处理器、标准总线和 外设。 软件和硬件相对独立。

•

嵌入式系统

看不见的计算机。 形式多样,应用领域广泛 ,按应用来分。

组成

•

•

面向应用的嵌入式微处 理器,总线和外部接口 多集成在处理器内部。 软件与硬件是紧密集成 在一起的。 采用交叉开发方式,开 发平台一般是通用计算 机,运行 平台是嵌入 式系统。 大部分不能再编程

2、Windows CE

17

1.3 嵌入式操作系统举例

1.3.2 开源版嵌入式操作系统 嵌入式Linux(Embedded Linux)

具有低成本、多种硬件平台支持、优异的性能和良好的 网络支持等优点 uCLinux、RT-Linux、Embedix、 XLinux、PoketLinux、红旗嵌入式Linux等

开发方式

•

开发平台和运行平台都是 通用计算机

•

二次开发性

•

应用程序可重新编制

•

1.1 嵌入式系统概述

1.1.3 嵌入式系统的发展 嵌入式系统发展的4个阶段:

① 以单芯片为核心的可编程控制器形式的系统 ② 以嵌入式CPU为基础、以简单操作系统为核心的嵌入式

系统 ③ 以嵌入式操作系统为标志的嵌入式系统 ④ 以Internet为标志的嵌入式系统

3

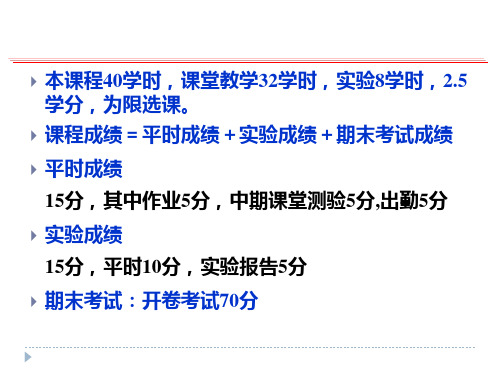

第1章 嵌入式系统基础知识

本章课程:

1.1 嵌入式系统概述 1.2 嵌入式系统的组成 1.3 嵌入式操作系统举例 1.4 嵌入式系统开发概述 1.5 小结

嵌入式系统软硬件可靠性设计讲义

14

5-500R < 0.8v => R>4.2/500=8.4k

15

Vcc

R

VH

Io

Io

200μA

200uA *15K=3V 选 10K 可用。

24V 10Ω±10%

最坏电路情况分析,R 取最不利的数 值 最高的器件环境温度 Ta 最高的电 压 Vmax 降额余量 最大的阻值 误差 R-ΔR

16

1.1 、设计调查表 1.2 、导致问题的常见应力 1.3 、分析方法

3

1.1、设计调查表

1. 环境因素 2. 人的因素 3. 关联设备的因素

4

1.2、常见故障应力

过渡过程应力及超调对输入端器件的影响

5

感性负载、容性负载对驱动电路的影响分析

6

环境条件影响

7

单一故障与系统分析方法

8

1.3、分析方法

工程计算与容差分析

P

95.4%

-2σ

+2σ

U

-σ +σ

68.3%

-3σ

+3σ

99.73 %

9

最坏电路情况分析法

±5%?

±5%?

±10%

10

精度分配方法

1. 得到系统的总精度要求 2. 找出影响总精度的各分模块 3. 推导出系统输出值与各模块测控物理量的工程计算公式 4. 根据工程计算公式,做微分运算,推导出影响总精度的所有要素,然

MT48LC8M16A2 Datasheet.pdf

19

面板复位电路抗干扰电容

1. 面板复位是静电非常敏感电路;处理方式如图

2. 电容典型值 560pF

4. 双向 TVS 管选择结电容较小的 管 子,结电容<1000pF

嵌入式系统基础知识专业知识讲座

嵌入式系统基础知识专业知识讲座

更多级的流水线

ARM10采用了6级流水线。 ARM11采用了8级流水线。

嵌入式系统基础知识专业知识讲座

流水线的数据相关问题

若指令中具有N个阶段,当每个阶段的执行时间是相同的 话,那么在流水线装满的时间内,则在每一个周期就可同时 执行N条指令,性能就可改善N倍。

在当时,IT行业的迅猛发展,Intel、摩托罗拉、TI 等上游厂商都有着不同的数字架构,这使得他们的 CPU等基础器件各有不同。器件不同,软件就不同, 而越来越多不同的指令集、工具和语言,对整个数 字技术的发展非常不利。全球工业价值链基本就是 大包大揽的大公司的天下,象摩托罗拉这样的公司 在测试、制造、系统封装,甚至CPU设计等领域都 是一把抓的。直到80年代末,产业链开始出现分工。 这样一个更有效的办法就是出现一个更上游的厂商 来制定标准,而这个标准的统一,一定是从数字技 术的核心CPU开始。于是ARM诞生的时候就选择了 CPU体系结构设计这个上游厂商的上游。

乘法器一般采用两位乘法并带有加1移位的方法来 实现乘法。内部高速乘法器采用32位的结构,这样 可以降低集成度,完成32*32位的运算需要5个周期。

嵌入式系统基础知识专业知识讲座

4)浮点部件(协处理器)

体系结构设计师们在指令系统层次上提供一种灵活 性的设计方法是利用协处理器,它被附接在CPU上并 能实现部分指令。例如,通过提供实现浮点指令的芯 片,浮点算术运算就能够被引入到嵌入式系统体系结 构中。

但如果当一条指令需要前面指令的执行结果,而这些指令 均在流水线中重叠执行时,就可能会涉及流水线的数据相关, 不得不产生停顿。为了避免结构相关,因而ARM架构采用了 资源重复的方法: 采用分离式指令Cache和数据Cache。该方法是取指和存 储器的数据访问不再发生冲突,同时也解决了相应数据同一 通道的问题。ALU中采用单独的加法器来完成地址计算,该 方法是执行周期的运算不再产生资源冲突。

更多级的流水线

ARM10采用了6级流水线。 ARM11采用了8级流水线。

嵌入式系统基础知识专业知识讲座

流水线的数据相关问题

若指令中具有N个阶段,当每个阶段的执行时间是相同的 话,那么在流水线装满的时间内,则在每一个周期就可同时 执行N条指令,性能就可改善N倍。

在当时,IT行业的迅猛发展,Intel、摩托罗拉、TI 等上游厂商都有着不同的数字架构,这使得他们的 CPU等基础器件各有不同。器件不同,软件就不同, 而越来越多不同的指令集、工具和语言,对整个数 字技术的发展非常不利。全球工业价值链基本就是 大包大揽的大公司的天下,象摩托罗拉这样的公司 在测试、制造、系统封装,甚至CPU设计等领域都 是一把抓的。直到80年代末,产业链开始出现分工。 这样一个更有效的办法就是出现一个更上游的厂商 来制定标准,而这个标准的统一,一定是从数字技 术的核心CPU开始。于是ARM诞生的时候就选择了 CPU体系结构设计这个上游厂商的上游。

乘法器一般采用两位乘法并带有加1移位的方法来 实现乘法。内部高速乘法器采用32位的结构,这样 可以降低集成度,完成32*32位的运算需要5个周期。

嵌入式系统基础知识专业知识讲座

4)浮点部件(协处理器)

体系结构设计师们在指令系统层次上提供一种灵活 性的设计方法是利用协处理器,它被附接在CPU上并 能实现部分指令。例如,通过提供实现浮点指令的芯 片,浮点算术运算就能够被引入到嵌入式系统体系结 构中。

但如果当一条指令需要前面指令的执行结果,而这些指令 均在流水线中重叠执行时,就可能会涉及流水线的数据相关, 不得不产生停顿。为了避免结构相关,因而ARM架构采用了 资源重复的方法: 采用分离式指令Cache和数据Cache。该方法是取指和存 储器的数据访问不再发生冲突,同时也解决了相应数据同一 通道的问题。ALU中采用单独的加法器来完成地址计算,该 方法是执行周期的运算不再产生资源冲突。

嵌入式系统PPT讲解全

三大领域所占比例之和接近60%

消费电子:信息家电,电视机、微波炉、数字电话 通信设备:手机、平板电脑 工业控制:自动化与测控仪器仪表 在工控和仿真领域,几乎所有的计算机控制系统都

采用嵌入式系统.新型的测控仪器仪表无一不是嵌入 式系统

嵌入式系统作为“物联网”的核心,是当前最热门最 有前景的IT应用领域之一。

(软件外包是指软件外包提供商为了集中精力从事核心 竞争力业务,降低项目成本,同时提高项目实施的质量,将 自己的软件项目中的全部或部分工作发包给合适的软件 企业去完成)

嵌入式系统在工业上的应用

嵌入式工控机 嵌入式工控机(Embedded Industrial Computer)是一

种加固的增强型工业计算机,它可以作为一个工业控 制器在工业环境中可靠运行。

工控机对于扩展性的要求也非常高,接口的设计需要 满足特定的外部设备,因此大多数情况下工控机需要 单独定制才能满足需求。

嵌入式工控机的优点 性能可靠 体积小巧 免维护 低功耗、无风扇、宽温设计、适应恶劣工作环境

嵌入式工控机的三大缺点。 一是性能较低; 二是扩展性较差;

三是缺乏标准化。

嵌入式工业触控一体机

工控机(Industrial Personal Computer,IPC)即工业 控制计算机,是一种采用总线结构,对生产过程及 机电设备、工艺装备进行检测与控制的工具总称。 工控机具有重要的计算机属性和特征,如具有计算 机CPU、硬盘、内存、外设及接口,并有操作系统、 控制网络和协议、计算能力、友好的人机界面。

工控机的主要类别有:IPC(PC总线工业电脑)、PLC (可编程控制系统)、DCS(分散型控制系统)、 FCS(现场总线系统)及CNC(数控系统)五种。

嵌入式工控机的优势

嵌入式资料PPT课件

C语言

适用于需要面向对象编程 的应用场景,如GUI开发、 游戏机等。

Python语言

适用于需要快速原型开发 或脚本编程的应用场景。

嵌入式软件设计模式

单片机程序架构

适用于资源受限的微控制器,如8051系列。

ARM Cortex-M系列MCU程序架构

适用于ARM Cortex-M系列MCU,如STM32。

软件设计

根据系统需求和总体设计,设计 软件模块和接口,确定软件架构。

系统实现与测试

编码实现

按照设计要求,编写代 码并实现系统功能。

单元测试

对每个模块进行测试, 确保模块功能正常。

集成测试

将所有模块集成在一起 进行测试,确保系统整

体功能正常。

系统测试

对整个系统进行测试, 确保系统满足需求规格

说明书的要求。

系统部署与维护

系统部署

将系统安装到实际运行环境中,并进 行配置和调试。

系统维护

对系统进行日常维护和升级,确保系 统稳定运行。

05

嵌入式系统应用案例

智能家居系统

智能家居系统

01

通过嵌入式系统技术,将家中的各种设备连接到互联网,实现

智能化控制和管理。

智能家居系统的功能

02

包括远程控制、语音控制、自动化控制等,提高家庭生活的便

传感器和执行器是嵌入式系统 的关键组成部分,用于实现系

统的感知和控制功能。

选择合适的传感器和执行器需 要考虑应用场景、性能要求和

成本等因素。

嵌入式硬件开发工具

嵌入式硬件开发工具包括原理图 设计软件、PCB设计软件、仿真

软件等。

这些工具可以帮助开发人员快速 设计、仿真和调试嵌入式硬件系

嵌入式系统概述整本书课件完整版电子教案(最新)

嵌入式系统原理与应用 2008

3. 嵌入式系统的演变

3.1 计算机用于控制设备或嵌入系统的历史几乎与计算机自身的历史一样长 计算机控制系统 单片机掀起电子化浪潮 微处理器高速发展推动了嵌入式系统

3.2 嵌入式系统的演变 8031/8051单片机系统,自行编写程序; 68360/386EX控制系统,自己编写简单的操作系统; 32位嵌入式处理器+pSoS嵌入式操作系统+tcp/ip协议栈; 各种SoC+嵌入式Linux/VxWorks+嵌入式Web 设备server以及各种复杂网 络协议栈+GUI图形界面+无线模块=现代可移动的网络智能设备

嵌入式系统原理与应用 2008

嵌入式系统的概念

1.4 精确定义:

以应用为中心、以计算机技术为基础、

软件硬件可裁剪、适应应用系统对功能、可靠

性、成本、体积、功耗严格要求的专用计算机

系统

嵌入式系统是将先进的计算机技术、

半导体技术和电子技术和各个行业的具体应用

相结合后的产物,这一点就决定了它必然是一

个技术密集、资金密集、高度分散、不断创新

Automatic toll systems Network switches/routers

Automatic transmission On-board navigation

Avionic systems

Pagers

Battery chargers

Photocopiers

Camcorders

Point-of-sale systems

2.2 嵌入式系统软件的特征: 软件要求固态化存储 软件代码高质量、高可靠性 系统软件(OS)的高实时性是基本要求 多任务操作系统是知识集成的平台和走向工业标准化道路的基础

3. 嵌入式系统的演变

3.1 计算机用于控制设备或嵌入系统的历史几乎与计算机自身的历史一样长 计算机控制系统 单片机掀起电子化浪潮 微处理器高速发展推动了嵌入式系统

3.2 嵌入式系统的演变 8031/8051单片机系统,自行编写程序; 68360/386EX控制系统,自己编写简单的操作系统; 32位嵌入式处理器+pSoS嵌入式操作系统+tcp/ip协议栈; 各种SoC+嵌入式Linux/VxWorks+嵌入式Web 设备server以及各种复杂网 络协议栈+GUI图形界面+无线模块=现代可移动的网络智能设备

嵌入式系统原理与应用 2008

嵌入式系统的概念

1.4 精确定义:

以应用为中心、以计算机技术为基础、

软件硬件可裁剪、适应应用系统对功能、可靠

性、成本、体积、功耗严格要求的专用计算机

系统

嵌入式系统是将先进的计算机技术、

半导体技术和电子技术和各个行业的具体应用

相结合后的产物,这一点就决定了它必然是一

个技术密集、资金密集、高度分散、不断创新

Automatic toll systems Network switches/routers

Automatic transmission On-board navigation

Avionic systems

Pagers

Battery chargers

Photocopiers

Camcorders

Point-of-sale systems

2.2 嵌入式系统软件的特征: 软件要求固态化存储 软件代码高质量、高可靠性 系统软件(OS)的高实时性是基本要求 多任务操作系统是知识集成的平台和走向工业标准化道路的基础

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第四章 存储系统

4.2.3 S3C44B0x的存储分配

一共有8个Bank

Bank0~Bank5可接ROM(Flash)、SRAM存储器 Bank6~Bank7可接FPM/EDO/SDRAM存储器

支持两种端格式的存储器

Big/Little Endian

如何支持多种存储器字宽的引导ROM?

31

t1 t2 t3

5ns t0 10ns tsu 40ns, th 6ns 4.3.4 存储器时序(续)

第四章 存储系统

访 存 时 序 配 合

存控发出的信号要满足存储器的时序要求 2013/4/18 存储器返回的信号要满足存控的时序要求

tsu

th

32

第四章 存储系统

1 满足存储器的时序要求,则时钟周期T

4 所以最小时钟周期T为

T max{65,80} 80ns

2013/4/18 33

第四章 存储系统

本讲小结

目的与要求

掌握常用存储器的特点、分类以及性能指标;标准电 平、建立、保持时间、存储器时序分析 熟悉S3C44B0x的存储器分配 了解存储器时序的基本概念

重点与难点

典型存储器的特点、分类以及性能指标 存储器时序分析

FRAM(铁电存储器)

非挥发 功耗低 读写速度快 接口时序简单 • 类似SRAM接口 成本高

2013/4/18

9

第四章 存储系统

4.1.3 常用的几种存储器(续)

并行接口存储器

引脚数目多——三大总线 • 地址、控制总线 • 数据总线(8/16/32位) 存储容量大 • 适用于大容量存储场合 存取速度快 接口时序复杂,编程透明

第四章 存储系统

4.3.2 时序转换

信号的改变需要时间,阻容充放电效应,信号需要一定时间到达 规定的逻辑电平

状 态 转 换 时 序 转 换

2013/4/18 23

第四章 存储系统

4.3.2 时序转换(续)

状 态 转 换 时 序 转 换

2013/4/18 24

第四章 存储系统

4.3.2 时序转换(续)

第四章 存储系统

2 SRAM的操作时序

读操作

首先将地址送到地址线上,保持不变 然后置片选CE#和读使能OE#有效,此时开始读操作 经过一定的延迟,指定地址的数据将出现在存储芯片 的数据总线上,主机(存控)可以读取该数据

注意:

对于读操作,需要注意的是地址和控制信号必须满足 存储器的时序要求(信号宽度或者建立/保持时间) 读出的数据要满足存控的建立/保持时间

性能指标 只读性 挥发性 存储容量 速度 功耗 可靠性

2013/4/18

4

第四章 存储系统

4.1.3 常用的几种存储器

SRAM(静态随机存储器)

存储密度小 • 6管结构,占用较大芯片面积 价格较高 功耗较高 容量较小 存取速度快 接口时序简单

2013/4/18

阅读章节:第4.1~4.3节 作业:补充作业

34

2013/4/18

第四章 存储系统

4.4 存储器接口

4.4.1 SRAM接口 4.4.2 DRAM接口 4.4.3 Flash接口

2013/4/18

35

第四章 存储系统

4.4.1 SRAM接口

1 概述 2 SRAM的操作时序 3 SRAM存储器芯片 4 应用设计

T t0 t0 t1 10 60 70ns T 70 5 65ns

2 满足存控的建立时间,则时钟周期T

T t0 t2 tsu 10 30 40 80ns

3 满足存控的保持时间

th t0 t3 5 5 10ns 6ns

OM引脚,外部连接决定引导ROM的字宽

如何支持多种存储器字宽的其他存储器?

在引导ROM里对其他存储器进行配置

2013/4/18

16

第四章 存储系统

S3C44B0 微控制器 片内集成 存储控制器

2013/4/18

17

并非所有的组都要使用,但 BANK0必须(启动代码) 第四章 存储系统 S3C44B0

存储空间 分配

2013/4/18

18

第四章 存储系统

4.3 存储器时序

4.3.1 数字信号的三种状态 4.3.2 时序转换 4.3.3 建立/保持时间 4.3.4 存储器时序

2013/4/18

19

第四章 存储系统

4.3.1 数字信号的三种状态

高电平(逻辑1——理论5/3.3V) 低电平(逻辑0——理论0V) 高阻态(三态——断开):引脚悬空所至、三态门 控制,呈现出极大的电阻、用于总线

21

2013/4/18

第四章 存储系统

4.3.1 数字信号的三种状态(续)

标准CMOS电平

发送端 • 高电平:>0.9Vdd • 低电平:<0.1Vdd 接收端 • 高电平:>0.7Vdd • 低电平:<0.3Vdd 特点 • 噪声容限大 • 负载能力强

VO

VI

2013/4/18

22

2013/4/18

43

第四章 存储系统

4 应用设计(续)

读写速度

SRAM速度一般是几个ns至几百个ns,常用40~70ns

操作时序——存储系统设计的一个重点

处理器发出的读写信号时序必须和外接的存储器严格 配合(匹配操作时序) 地址、数据以及各个控制信号必须要满足存储芯片手 册规定的时序要求(信号宽度或者建立/保持时间) 在保证数据读写正确性的前提下,才能对片外总线速 率进行优化

5

第四章 存储系统

4.1.3 常用的几种存储器(续)

DRAM(动态随机存储器)

存储密度大 • 单管结构 单位存储成本较低 功耗较低 容量较大 接口时序复杂 • 需要刷新电路

2013/4/18

6

第四章 存储系统

4.1.3 常用的几种存储器(续)

EEPROM

非挥发 存储密度小 单位存储成本较高 容量小 写入有限制,页写要等待 接口时序简单,一般采用串行接口 小量参数存储

2013/4/18

36

第四章 存储系统

1 概述

特点

速度快、存储密度较小、 成本高、易失性存储器 SRAM的接口和使用简单

Addr Data

总线

数据总线——8/16/32位 地址总线——1k~1M级 控制总线——大多是低电 平有效

SRAM

OE# WE# CE#

37

2013/4/18

第四章 存储系统

4.3.3 建立/保持时间(续)

表征时钟边沿触发时数据需要在锁存器的输入端 持续的时间 建立时间

在时钟信号边沿到来之前,数据信号必须提前一段时 间保持稳定有效

保持时间

在时钟信号边沿到来之后,数据信号必须在随后的一 段时间内保持稳定有效

所有数据信号在时钟信号边沿(触发器采集)前/ 后一段时间内必须满足建立/保持时间的要求

性能和鲁棒性的折中,一定的裕量

28

2013/4/18

第四章 存储系统

4.3.3 建立/保持时间(续)

tsu t h

t0

2013/4/18

29

第四章 存储系统

4.3.4 存储器时序(timing)

时序图

设备之间输入输出信号的表示方法 体现了设备之间输入输出信号的关系

实质

表明什么时候一个信号需要确认,什么时候从设备得 到一个期望的响应

2013/4/18

38

第四章 存储系统

2 SRAM的操作时序(续)

SRAM读操作时序示意图

2013/4/18

39

第四章 存储系统

2 SRAM的操作时序(续)

写操作

首先将地址和数据送到总线上,保持不变 然后置片选CE#和写使能WE#有效,此时开始写操作 经过一定的延迟,数据可靠写入指定地址存储单元

2013/4/18

20

第四章 存储系统

4.3.1 数字信号的三种状态(续)

标准TTL电平

发送端 • 高电平:>2.4V • 低电平:<0.4V 接收端 • 高电平:>2.0V • 低电平:<0.8V 特点 • 噪声容限小 • 负载能力弱

Vdd

2.4V 2.0V

VO VI

0.8V 0.4V 0V

2013/4/18

7

第四章 存储系统

4.1.3 常用的几种存储器(续)

Flash(闪存存储器)

非挥发 存储密度大 单位存储成本较低 容量大 接口时序复杂——需要擦除及Block写 NOR Flash & NAND Flash

2013/4/18

8

第四章 存储系统

4.1.3 常用的几种存储器(续)

要求

时序信号必须兼容,否则需要添加额外的电路

2013/4/18

30

第四章 存储系统

4.3.4 存储器时序(续)

某 存 储 器 时 序 图 示 例

2013/4/18

t1

t2

参考 功能描述 rd持续时间 rd到有效数据输出 data持续时间 5 最小值 60 30 10

t3

最大值 单位 ns ns ns

状 态 转 换 时 序 转 换