VHDL课件

合集下载

VHDL范例PPT课件

第7章 VHDL设计应用实例

B4:IN STD_LOGIC_VECTOR(3 DOWNTO 0); S4:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); CO4:OUT STD_LOGIC); END COMPONENT ADDER4B; SIGNAL SC:STD_LOGIC; --4位加法器的进位标志 BEGIN U1:ADDER4B --例化(安装)一个4位二进制加法器U1 PORT MAP(C4=>C8,A4=>A8(3 DOWNTO 0),

7.3 1秒计时电路的设计 外部输入的频率为1KHz,要求产生一个1S的时钟信号

1Kz ( 1/1000 秒) 10分频 (1/100秒) 10分频 (1/10秒) 10分频 1秒

CLK(1KHz)

10 clk001 10 clk01 10

分

分

分

频

频

频

clk1s

第7章 VHDL设计应用实例

(1)10分频的VHDL语言描述

第7章 VHDL设计应用实例

BEGIN A5<='0'& A4;

--将4位加数矢量扩为5位,为进位提供空间 B5<='0'& B4;

--将4位被加数矢量扩为5位,为进位提供空间 S5<=A5+B5+C4 ; S4<=S5(3 DOWNTO 0);

CO4<=S5(4); END ARCHITECTURE ART;

END ENTITY ADDER8B; ARCHITECTURE ART OF ADDER8B IS COMPONENT ADDER4B IS

--对要调用的元件ADDER4B的界面端口进行定义 PORT(C4:IN STD_LOGIC;

B4:IN STD_LOGIC_VECTOR(3 DOWNTO 0); S4:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); CO4:OUT STD_LOGIC); END COMPONENT ADDER4B; SIGNAL SC:STD_LOGIC; --4位加法器的进位标志 BEGIN U1:ADDER4B --例化(安装)一个4位二进制加法器U1 PORT MAP(C4=>C8,A4=>A8(3 DOWNTO 0),

7.3 1秒计时电路的设计 外部输入的频率为1KHz,要求产生一个1S的时钟信号

1Kz ( 1/1000 秒) 10分频 (1/100秒) 10分频 (1/10秒) 10分频 1秒

CLK(1KHz)

10 clk001 10 clk01 10

分

分

分

频

频

频

clk1s

第7章 VHDL设计应用实例

(1)10分频的VHDL语言描述

第7章 VHDL设计应用实例

BEGIN A5<='0'& A4;

--将4位加数矢量扩为5位,为进位提供空间 B5<='0'& B4;

--将4位被加数矢量扩为5位,为进位提供空间 S5<=A5+B5+C4 ; S4<=S5(3 DOWNTO 0);

CO4<=S5(4); END ARCHITECTURE ART;

END ENTITY ADDER8B; ARCHITECTURE ART OF ADDER8B IS COMPONENT ADDER4B IS

--对要调用的元件ADDER4B的界面端口进行定义 PORT(C4:IN STD_LOGIC;

第四章VHDL设计初步PPT课件

第4页

第四章 VHDL设计初步

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL;

程序包

设计一个2选1 多路通道

ENTITY mux21 IS PORT(a,b,s: IN BIT; q: OUT BIT );

END mux21;

实体

ARCHITECTURE connect OF mux21 IS

第 10 页

第四章 VHDL设计初步

VHDL结构要点

2、Arcthitecture(结构描体)述器件内部逻辑

格式:

功能或电路结构。

Arcthitecture 结构体名 of 实体名 is

[说明语句] 内部信号、常数、元件、数据类 型、函数等的定义

begin [功能描述语句]

并行语句或顺序语 句或它们的混合。

END EALRSCEHITbE; CT条UR件E o判ne;断表达式

第 14 页

第四章 VHDL设计初步

ARCHITECTURE one OF mux21a IS

SIGNAL d,e: BIT;

BEGIN

d<= a AND (NOT s); 逻辑操作符:

e<= b AND s;

BIT,

q<= d OR e; END ARCHITECTURE

end 结构体名;

第 11 页

第四章 VHDL设计初步

VHDL结构要点 说明语句

说明功能描述中用到的 信号(SIGNAL) 数据类型(TYPE) 常数(CONSTANT) 元件(COMPONENT) 函数(FUNCTION) 过程(PROCEDURE)

第 12 页

第四章 VHDL设计初步

VHDL课件VHDL语言及其应用

8

第二部分 VHDL语言的学习基础 (3)

•书写规定与基本句法单元

▲数及表示法

数制: 二进制、十进制、十六进制 书写格式:被表示的数 ::= <基>#<用基表示的整数[.用基表示的整数]>#[<指数>]

<基>为2~16之间的十进制正整数, #号为定界符,<基>为10时可省略

定界符和基。

<指数> ::= E[+]<十进制正整数> | E<–> <十进制正整数> ;

Synthesis Packages, IEEE-1076.4 VITAL, IEEE Standard 1164 Multi-value Logic System

• VHDL语言的优点?

▲人机可读性好 ▲比图形和布尔方程更简洁 ▲方便设计重用 ▲容易实现设计仿真与验证 ▲便于映射为IC芯片的制造工艺

扩展标识符 由VHDL’93,VHDL2001支持,首尾用反斜杠“\”定界, 区分大小写,总与基本标识符不同,字符集:ASCII码, 反斜杠字符要双写,允许任意字符,包括保留字、类型字

▲ 保留字 类型字 专用字

保留字 预留用于专门用途的标识符,VHDL’87,VHDL’93和VHDL2001有差别 类型字 用于表示数据类型的标识符 专用字 用于表示特别信息和常量的标识符

<用基表示的整数> ::= <扩展数字>{[下划线]<扩展数字>};

<扩展数字> ::= <数字> | <字符>

举例:

用字符A~F表示10~15的数字,不分大小写。

2#0001_0111_0010# 8#562# 16#172# 370 3.7E+2 --整数370的表示

第二部分 VHDL语言的学习基础 (3)

•书写规定与基本句法单元

▲数及表示法

数制: 二进制、十进制、十六进制 书写格式:被表示的数 ::= <基>#<用基表示的整数[.用基表示的整数]>#[<指数>]

<基>为2~16之间的十进制正整数, #号为定界符,<基>为10时可省略

定界符和基。

<指数> ::= E[+]<十进制正整数> | E<–> <十进制正整数> ;

Synthesis Packages, IEEE-1076.4 VITAL, IEEE Standard 1164 Multi-value Logic System

• VHDL语言的优点?

▲人机可读性好 ▲比图形和布尔方程更简洁 ▲方便设计重用 ▲容易实现设计仿真与验证 ▲便于映射为IC芯片的制造工艺

扩展标识符 由VHDL’93,VHDL2001支持,首尾用反斜杠“\”定界, 区分大小写,总与基本标识符不同,字符集:ASCII码, 反斜杠字符要双写,允许任意字符,包括保留字、类型字

▲ 保留字 类型字 专用字

保留字 预留用于专门用途的标识符,VHDL’87,VHDL’93和VHDL2001有差别 类型字 用于表示数据类型的标识符 专用字 用于表示特别信息和常量的标识符

<用基表示的整数> ::= <扩展数字>{[下划线]<扩展数字>};

<扩展数字> ::= <数字> | <字符>

举例:

用字符A~F表示10~15的数字,不分大小写。

2#0001_0111_0010# 8#562# 16#172# 370 3.7E+2 --整数370的表示

EDA技术_第二章_VHDL语言ppt课件

❖ 2.熟悉:

▪ VHDL语言的其它数据类型、子程序、包集合及配置

❖ 3.了解:

▪ 标示符:扩展标识符;数据类型转换

2020/4/26

.

2

VHDL语言程序通常包含5部分:

LOGO

实体说明:

entity:

描述所设计系统的外部接口信号,是可见的。

构造体: architecture 配置: configuration

2020/4/26

.

9

§2.2 VHDL的数据类型及运算操作符 LOGO

❖ VHDL语言同其它语言一样有多种数据类型和运算符, 且它们的定义也大多相同。VHDL语言的特点是用户 可以自己定义数据类型。

▪ 如:type count is integer RANGE 0 to 10;

2020/4/26

2020/4/26

.

8

2.1.5 段名

LOGO

❖ 段名是多个下标名的组合,对应数组中某一段的元素

▪ 格式:标示符(表达式 方向 表达式) ▪ 方向:TO 或 DOWNTO

▪ SIGNAL a ,z :BIT_VECTOR(0 TO 7) ;

▪ Signal b:bit_vector(4 downto 0); ▪ z(0 TO 3)<= a(4 TO 7) ;--z(0)<= a(4)、z(1)<= a(5)…

LOGO

VHDL的语言要素包含

客体(或对象) 数据类型 运算操作符

操作数

VHDL规定: (1)不区分大小写(“”和‘’内的字符除外); (2)每条语句以一个分号;结束; (3)不是所有语句前都可以加标号; (4)一条语句后可以加注释,在注释内容前加两个短划线。

▪ VHDL语言的其它数据类型、子程序、包集合及配置

❖ 3.了解:

▪ 标示符:扩展标识符;数据类型转换

2020/4/26

.

2

VHDL语言程序通常包含5部分:

LOGO

实体说明:

entity:

描述所设计系统的外部接口信号,是可见的。

构造体: architecture 配置: configuration

2020/4/26

.

9

§2.2 VHDL的数据类型及运算操作符 LOGO

❖ VHDL语言同其它语言一样有多种数据类型和运算符, 且它们的定义也大多相同。VHDL语言的特点是用户 可以自己定义数据类型。

▪ 如:type count is integer RANGE 0 to 10;

2020/4/26

2020/4/26

.

8

2.1.5 段名

LOGO

❖ 段名是多个下标名的组合,对应数组中某一段的元素

▪ 格式:标示符(表达式 方向 表达式) ▪ 方向:TO 或 DOWNTO

▪ SIGNAL a ,z :BIT_VECTOR(0 TO 7) ;

▪ Signal b:bit_vector(4 downto 0); ▪ z(0 TO 3)<= a(4 TO 7) ;--z(0)<= a(4)、z(1)<= a(5)…

LOGO

VHDL的语言要素包含

客体(或对象) 数据类型 运算操作符

操作数

VHDL规定: (1)不区分大小写(“”和‘’内的字符除外); (2)每条语句以一个分号;结束; (3)不是所有语句前都可以加标号; (4)一条语句后可以加注释,在注释内容前加两个短划线。

VHDL语言基础PPT课件

程序包结构: 程序包说明(包首) 程序包主体(包体)

第36页/共80页

1、程序包说明(包首)

语法: package 程序包名 is { 包说明项 } end 程序包名;

包声明项可由以下语句组成: use 语句(用来包括其它程序包); 类型说明;子类型说明;常量说明; 信号说明;子程序说明;元件说明。

end 配置名;

第21页/共80页

一个与非门不同实现方式的配置

library ieee; use ieee.std_logic_1164.all; entity nand is

port(a: in std_logic; b: in std_logic; c: out std_logic);

end entity nand; architecture art1 of nand is begin

UNSIGNED,SIGNED和SMALL_INT,并为其定 义了相关的算术运算符和转换函数。 Std_logic_signed 和 Std_logic_Unsigned : 重载了可用于INTEGER型和STD_LOGIC及 STD_LOGIC_VECTOR型混合运算的运算符,并定 义了不同数据类型间的转换函数。

UNSIGNED.CONV_INTEGER; 上例表明,要使用IEEE库中STD_LOGIC_1164包 集合中的所有过程和函数,这里项目名为ALL, 表示包集合中的所有项目都要用。

第35页/共80页

五、程序包(包集合)Package

程序包(Package):将已定义的常数、 数据类型、元件语句、子程序等收集起来组成 一个集合,以便被更多的VHDL设计实体进行访 问和共享。

第31页/共80页

WORK库 WORK库:是用户的VHDL设计的现行工作库; 用于存放用户设计和定义的一些设计单元和程序包; 满足VHDL语言标准,在实际调用中不必以显式说明。

第36页/共80页

1、程序包说明(包首)

语法: package 程序包名 is { 包说明项 } end 程序包名;

包声明项可由以下语句组成: use 语句(用来包括其它程序包); 类型说明;子类型说明;常量说明; 信号说明;子程序说明;元件说明。

end 配置名;

第21页/共80页

一个与非门不同实现方式的配置

library ieee; use ieee.std_logic_1164.all; entity nand is

port(a: in std_logic; b: in std_logic; c: out std_logic);

end entity nand; architecture art1 of nand is begin

UNSIGNED,SIGNED和SMALL_INT,并为其定 义了相关的算术运算符和转换函数。 Std_logic_signed 和 Std_logic_Unsigned : 重载了可用于INTEGER型和STD_LOGIC及 STD_LOGIC_VECTOR型混合运算的运算符,并定 义了不同数据类型间的转换函数。

UNSIGNED.CONV_INTEGER; 上例表明,要使用IEEE库中STD_LOGIC_1164包 集合中的所有过程和函数,这里项目名为ALL, 表示包集合中的所有项目都要用。

第35页/共80页

五、程序包(包集合)Package

程序包(Package):将已定义的常数、 数据类型、元件语句、子程序等收集起来组成 一个集合,以便被更多的VHDL设计实体进行访 问和共享。

第31页/共80页

WORK库 WORK库:是用户的VHDL设计的现行工作库; 用于存放用户设计和定义的一些设计单元和程序包; 满足VHDL语言标准,在实际调用中不必以显式说明。

VHDL语言教程ppt课件

信号赋值语句: 目标信号名 <= 表达式;

x<=9; Z<=x after 5 ns; -- 在5ns后将x的值赋予z

9

3.1.2 数据类型

➢ VHDL的预定义数据类型 在VHDL标准程序包STANDARD中定义好,实际使用过程中,已

自动包含进VHDL源文件中,不需要通过USE语句显式调用。

布尔:(Boolean)

来,区分大小写;

VARIABLE string_var: STRING (1 TO 7);

string_var:=“A B C D” ;

-- 通常用“”引起来,区分大小写;

整数:(Integer)

取值范围 -(231-1) ~(231-1),可用32位有符号的二进制数表示

variable a:integer range -63 to 63

在条件语句中,必须要全面考虑Std_Logic的所有可能取值情况,否则综 合器可能会插入不希望的锁存器。

13

➢ 用户自定义

TYPE 数据类型名 IS 数据类型定义 OF 基本数据类型 或 TYPE 数据类型名 IS 数据类型定义

数组:type value_type is array (127 downto 0) of integer; type matrix_type is array (0 to 15, 0 to 31) of std_logic;

L: Weak 0

H: Weak 1

—:Don’t care

标准逻辑位矢量( Std_Logic_vector)

基于Std_Logic类型的数组;

使用Std_Logic和 Std_Logic_Vector要调用IEEE库中的Std_Logic_1164 程序包;就综合而言,能够在数字器件中实现的是“-、0、1、Z”四种状态。

x<=9; Z<=x after 5 ns; -- 在5ns后将x的值赋予z

9

3.1.2 数据类型

➢ VHDL的预定义数据类型 在VHDL标准程序包STANDARD中定义好,实际使用过程中,已

自动包含进VHDL源文件中,不需要通过USE语句显式调用。

布尔:(Boolean)

来,区分大小写;

VARIABLE string_var: STRING (1 TO 7);

string_var:=“A B C D” ;

-- 通常用“”引起来,区分大小写;

整数:(Integer)

取值范围 -(231-1) ~(231-1),可用32位有符号的二进制数表示

variable a:integer range -63 to 63

在条件语句中,必须要全面考虑Std_Logic的所有可能取值情况,否则综 合器可能会插入不希望的锁存器。

13

➢ 用户自定义

TYPE 数据类型名 IS 数据类型定义 OF 基本数据类型 或 TYPE 数据类型名 IS 数据类型定义

数组:type value_type is array (127 downto 0) of integer; type matrix_type is array (0 to 15, 0 to 31) of std_logic;

L: Weak 0

H: Weak 1

—:Don’t care

标准逻辑位矢量( Std_Logic_vector)

基于Std_Logic类型的数组;

使用Std_Logic和 Std_Logic_Vector要调用IEEE库中的Std_Logic_1164 程序包;就综合而言,能够在数字器件中实现的是“-、0、1、Z”四种状态。

第七章VHDL语言简介-PPT课件

位矢量使用双引号括起来的一组位数据,如 “1011”。 使用位矢量时必须注明位宽,即数组中元素个数和 排列,如: SIGNAL S1:BIT_VECTOR(15 DOWNTO 0);

标准数据类型(10种)

• 布尔量 :TRUE,FALSE • 字符(CHARACTER) • 字符串 • 时间 : • 错误等级

3-2 构造体

构造体:确定基本设计单元输入输出关系,即它定义 了设计单元的具体功能。

• 构造体说明

• 构造体的描述方式

行为描述 寄存器传输级描述(RTL描述) 结构描述

构造体的说明

一定要跟在实体的后面 ,书写格式:

behev

可任意取,但一般用描述方式定义 dataflow

ARCHITECTURE 构造体名 OF 实体名 IS

4、VHDL语言标准、规范,易于共享和重复利用。

二、VHDL的基本语法规则

1、词法规则 2、标识符 3、保留字 4、VHDL的数据类型 5、VHDL的运算操作符

2-1 词法规则

2-1-1 注释

• 由两个短线“--”开始的一行文字,如: -- this is a counter

2-1-2 数字

• 十进制整数表示法:012 12_345(=12345) • 以基数表示: 2#1110_1001#, 16#AB0#E1 • 实数:必需带小数点。12.0 3.144 0.0 5.54E-2

加、减、并,关系,逻辑运算符。

❖括号可改变运算次序

下面以加法器为例说明并置运算符的用法:

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL;

标准数据类型(10种)

• 布尔量 :TRUE,FALSE • 字符(CHARACTER) • 字符串 • 时间 : • 错误等级

3-2 构造体

构造体:确定基本设计单元输入输出关系,即它定义 了设计单元的具体功能。

• 构造体说明

• 构造体的描述方式

行为描述 寄存器传输级描述(RTL描述) 结构描述

构造体的说明

一定要跟在实体的后面 ,书写格式:

behev

可任意取,但一般用描述方式定义 dataflow

ARCHITECTURE 构造体名 OF 实体名 IS

4、VHDL语言标准、规范,易于共享和重复利用。

二、VHDL的基本语法规则

1、词法规则 2、标识符 3、保留字 4、VHDL的数据类型 5、VHDL的运算操作符

2-1 词法规则

2-1-1 注释

• 由两个短线“--”开始的一行文字,如: -- this is a counter

2-1-2 数字

• 十进制整数表示法:012 12_345(=12345) • 以基数表示: 2#1110_1001#, 16#AB0#E1 • 实数:必需带小数点。12.0 3.144 0.0 5.54E-2

加、减、并,关系,逻辑运算符。

❖括号可改变运算次序

下面以加法器为例说明并置运算符的用法:

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL;

第4章-VHDL基础PPT课件

PORT(a,b_LOGIC);

实体部分

END and2;

ARCHITECTURE and2x OF and2 IS

BEGIN

y<=a AND b;

结构体部分

END and2x;

4

2库(LIBRARY)

➢ 库是用来放置可编译的设计单元的地方,通过其目录可查询 和调用。 VHDL中的库大致可归纳为5种:IEEE库、STD库、 ASIC矢量库、WORK库和用户定义库。

6

库和程序包的语法:

library <设计库名>; use < 设计库名>.<程序包名>.all ;

一般VHDL代码中库和程序包的调用语句:

library ieee ; use ieee.std_logic_1164.all ;

--最常用

use ieee.std_logic_arith.all;

use ieee.std_logic_signed.all;

END add4;

由实体说明画出四位加法器add4的电路图如下所示。

a[3..0]

Sum[3..0]

b[3..0]

Ci

add4

Co

11

4. 结构体

结构体主要是描述实体的硬件结构、元件之间的 互连关系、实体所完成的逻辑功能以及数据的传输变 换等方面的内容。

结构体的语句格式:

architecture arch_name of e_name is [说明语句]

2

实体

(Entity)

一个完整的 VHDL程序

结构体

(Architecture)

配置

(Configuration)

包集合

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2) 半加器的逻辑描述 LIBRARY IEEE; -- IEEE库的使用说明 USE IEEE.STD_LOGIC_1164.ALL; ENTITY h_adder IS --实体h_adder的说明 PORT(a,b:IN STD_LOGIC; co,so:OUT STD_LOGIC); END ENTITY h_adder; ARCHITECTURE art2 OF h_adder IS -- 实体h_adder的结构体art2的说明 BEGIN so<=(a OR b) AND (a NAND b); co<=NOT (a NAND b); END ARCHITECTURE art2;

(5) 在结构体art3中,COMPONENT→END COMPONENT 语句结构对所要调用的或门和半加器两元件 作了声明(COMPONENT DECLARATION),并由SIGNAL 语句定义了三个信号d、e和f,作为中间信号转存点,以利于 几个器件间的信号连接。 “PORT MAP( )”语句称为元件例化语句(COMPONENT INSTANTIATION)。所谓例化,在电路板上,相当于往上 装配元器件;在逻辑原理图上,相当于从元件库中取了一个 元件符号放在电路原理图上,并对此符号的各引脚进行连线。 例化也可理解为元件映射或元件连接,MAP是映射的意思。 例如,语句“U2:h_adder PORT MAP(a=>e,b=>cin, co=>f,so=>sum)”表示将实体h_adder描述的元件U2的 引脚信号a、b、co和so分别连向外部信号e、cin、f和sum。 符号“=>”表示信号连接。

3.1.3 VHDL程序设计约定 为了便于程序的阅读和调试,对VHDL程序设计特作如下约 定: (1) 语句结构描述中方括号“[ ]”内的内容为可选内容。 (2) 对于VHDL的编译器和综合器来说,程序文字的大小 写是不加区分的。 (3) 程序中的注释使用双横线“--”。在VHDL程序的任何 一行中,双横线“--”后的文字都不参加编译和综合。 (4) 为了便于程序的阅读与调试,书写和输入程序时,使 用层次缩进格式,同一层次的对齐,低层次的较高层次的缩 进两个字符。 (5) 考虑到MAX+plusII要求源程序文件的名字与实体名 必须一致,因此为了使同一个VHDL源程序文件能适应各个 EDA开发软件上的使用要求,建议各个源程序文件的命名均 与其实体名一致。

3.2.3 实体(ENTITY) 实体(ENTITY)是设计实体中的重要组成部 分,是一个完整的、独立的语言模块。它相当于 电路中的一个器件或电路原理图上的一个元件符 号。 实体由实体声明和结构体组成。实体声明部 分指定了设计单元的输入输出端口或引脚,是设 计实体经封装后对外的一个通信界面,是外界可 以看到的部分。 结构体用来描述设计实体的逻辑结构和逻辑 功能。由VHDL语句构成,是外界看不到的部分。 一个实体可以拥有一个或多个结构体。

• • • • •.2 VHDL设计实体的基本结构 通过VHDL描述一个二输入或门的实例,来说明VHDL的基本结构。 例1 一个二输入或门的VHDL程序如下: LIBRARY IEEE; -- IEEE库的使用说明 USE IEEE.STD_LOGIC_1164.ALL; --实体描述器件的输入、输出端口和数 据类型用的程序包 ENTITY OR2 IS --实体OR2的说明 PORT(A,B: STD_LOGIC; ---端口声明,A、B是标准逻辑位类型的输 入端口 C:OUT STD_LOGIC); --声明C是标准逻辑位类型的输出端口 END ENTITY OR2; ARCHITECTURE ONE OF OR2 IS --实体OR2的结构体ONE 的说明 BEGIN C<=A OR B; --二输入或门逻辑功能描述 END ARCHITECTURE ONE;

COMPONENT or2 PORT(a,b:IN STD_LOGIC; c: OUT STD_LOGIC); END COMPONENT or2; SIGNAL d,e,f:STD_LOGIC;

--定义中间信号转存点 BEGIN --元件连接说明 U1:h_adder PORT MAP(a=>ain,b=>bin,co=>d,so=>e); --名称映射法 U2:h_adder PORT MAP(a=>e,b=>cin,co=>f,so=>sum); --名字关联方式 U3:or2 PORT MAP(a=>d,b=>f,c=>cout); END ARCHITECTURE art3;

(6) 实体f_adder引导的逻辑描述也是由三个主要部分构 成的,即库、实体和结构体。从表面上看来,库的部分仅包 含一个IEEE标准库和打开的IEEE.STD_LOGIC_1164.ALL 程序包。但实际上,从结构体的描述中可以看出,其对外部 的逻辑有调用的操作,这类似于对库或程序包中的内容作了 调用。因此,库结构部分还应将上面的或门和半加器的 VHDL描述包括进去,作为工作库中的两个待调用的元件。 由此可见,库结构也是VHDL程序的重要组成部分。

3.2.2 VHDL程序的基本结构

库、程序包使用说明 设 计 实 体 配置 (CONF IGURAT ION) 结构体功能描述 实体 (ENT IT Y) PORT端口说明 结构体说明 GENERIC类属说明

结构体 (ARCHIT ECT URE)

VHDL程序设计基本结构

库、程序包

根据VHDL语法规则,在VHDL程序中使用的文字、数据对象、数 据类型都需要预先定义。为了方便用VHDL编程,IEEE将预定义的数 据类型、元件调用声明(Declaration)及一些常用子程序收集在一起, 形成程序包,供VHDL设计实体共享和调用。 若干个程序包则形成库,常用的库是IEEE标准库。因此,在每 个设计实体开始都有打开库或程序包的语句。例如 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; 表示设计实体中被描述器件的输入、输出端口和数据类型将要用 到IEEE标准库中的STD_LOGIC_1164程序包。

(3) 实体h_adder及对应的结构体art2描述了一个半加器。是 由一个与非门、一个非门、一个或门和一个与门连接而成 的,其逻辑关系来自于半加器真值表。在VHDL中,逻辑 算符NAND、NOT、OR和AND分别代表“与非”、 “非”、“或”和“与”4种逻辑运算关系。 (4) 在全加器接口逻辑VHDL描述中,1位二进制全加器 f_adder的原理图,实体f_adder定义了引脚的端口信号 属性和数据类型。其中,ain和bin分别为两个输入的相加 位,cin为低位进位输入,cout 为进位输出,sum为1位 和输出。其对应的结构体art3的功能是利用 COMPONENT声明语句和COMPONENT例化语句将上面 由两个实体or2和h_adder描述的独立器件,按照图3.2全 加器内部逻辑原理图中的接线方式连接起来。

• 或门程序包含了VHDL的库、程序包、实体说明和结构体几个主要部分。语句 C<=A OR B为或门电路的逻辑描述,其他都作为或门对外部端口的描述,设 计实体定义了或门外部界面后,其他的设计就可以直接调用这个或门实体。

3.2.1 VHDL程序设计举例 1.设计思路 以全加器为例 例2 全加器可以由两个1位的半加器构成。1位半加器的端口 信号A 和B分别是2位相加的二进制输入信号,SO是相加和的 输出信号,CO是进位输出信号,左边的门电路结构构成了右 边的半加器H_ADDER。

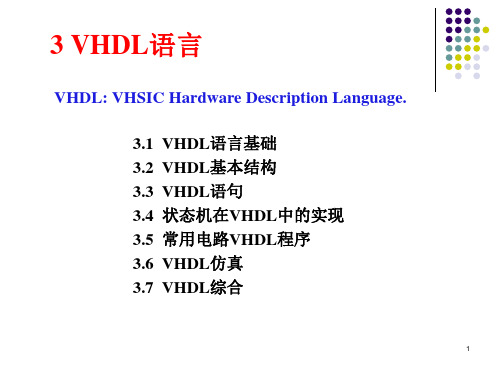

VHDL 编 程 基 础

目

3.1 3.2 3.3 3.4 3.5 3.6 3.7

录

概述 VHDL设计实体的基本结构 VHDL语言要素 VHDL顺序语句 VHDL并行语句 VHDL的库和程序包 VHDL设计流程

3.1 概 述 3.1.1 VHDL语言简介 VHDL是超高速集成电路硬件描述语言(Very High Speed Integrated Circuit Hardware Description language)。是标准化程度最高的硬件描述语言。目前流行 的EDA工具软件全部支持VHDL,VHDL是现代电子设计师必 须掌握的硬件设计计算机语言。 (1) 逻辑描述层次:一般的硬件描述语言可以在三个层次上 进行电路描述,层次由高到低依次可分为行为级、RTL级(寄 存器转换级)和门电路级。VHDL语言是一种高级描述语言, 适用于行为级和RTL级的描述,最适于描述电路的行为; (2) 设计要求:VHDL进行电子系统设计时可以不了解电路的 结构细节,设计者所做的工作较少;Verilog和ABEL语言进 行电子系统设计时需了解电路的结构细节,设计者需做大量 的工作。

3) 全加器的逻辑描述

LIBRARY IEEE; -- IEEE库的使用说明 USE IEEE.STD_LOGIC_1164.ALL; ENTITY f_adder IS --实体f_adder的说明 PORT(ain,bin,cin:IN STD_LOGIC; --端口声明,方向、数据类型名 cout,sum: OUT STD_LOGIC); END ENTITY f_adder; ARCHITECTURE art3 OF f_adder IS --实体F_ADDER的结构体ART3的说明 COMPONENT h_adder --元件调用声明,将h_adder作为元件连接到指定端口 PORT(a,b:IN STD_LOGIC; --端口声明 co,so:OUT STD_LOGIC); END COMPONENT h_adder;

3.2.2 VHDL程序的基本结构

完整的VHDL程序(设计实体)具有固定的结构。应包括三个基本组成部 分:库、程序包使用说明,实体说明和实体对应的结构体说明。 库、程序包使用说明用于打开本设计实体将要用到的库、程序包; 实体说明用于描述该设计实体与外界的接口信号说明,是可视部分; 结构体说明用于描述该设计实体内部工作的逻辑关系。 在一个实体中,可以含有一个或一个以上的结构体,而在每一个结构体 中又可以含有一个或多个进程以及其他的语句。 实体还可以有配置说明语句。配置说明语句主要用于以层次化的方式对 特定的设计实体进行元件例化,或是为实体选定某个特定的结构体。