计算机组成_ 流水线处理器(Pipelined Processor)_

流水线处理器

一、流水线处理器1、流水线原理一条指令的执行可以分为取值、分析和执行3个阶段,这3个阶段的执行分别由控制器内部的取值部件、指令分析部件和指令执行部件3个独立的功能部件完成。

在传统的控制器中,这3个阶段在时间上是分时进行的,即指令的3个阶段在时间上是顺序执行的,指令的这种执行方式又称为串行执行。

在串行执行方式中,n条指令的执行时间为:∑=+ +=niiiitttT1) (执行指令分析指令取指令如果取指令、分析指令和执行指令的3段时间都相等,每段时间都等于t ,则执行n 条指令的时间为:T=3nt采用串行执行指令的方式的优点是控制简单,节省硬件。

缺点是:①执行指令的速度慢。

只有当上一条指令执行完毕后,才能开始下一条指令的执行,即在任何时刻,控制器中只有一条指令在执行。

②功能部件利用率低。

例如,在取指令时,取指部件是“忙”的,而指令分析部件和执行部件是“空闲”的。

因此,串行执行指令并不能充分发挥控制器内各独立功能部件的作用。

为了克服串行执行指令的缺点,提高指令的执行速度和控制器各部件和利用率,指令的执行过程可以采用类似于工厂中的流水线装配形式,使指令的3个执行阶段在控制器各部件实现流水作业,控制器各部件总处于“忙”状态。

如果取指令、分析指令和执行指令的3段时间都相等,且每段时间都等于t,则执行n 条指令的时间为:T=(2+n)t 。

上述分析是针对在一条流水线有3个独立的功能部件而言的。

若一条流水线有m个功能独立的部件S1 ,S2,……,S m,这种流水线控制器的并行程度会显著提高。

为了充分发挥流水线的作用,流水线中的功能部件和任务必须满足以下条件:(1)在流水线中处理的任务必须是连续的,只有连续不断的任务才能充分发挥流水线的效率。

(2)把一个任务(一条指令或一个操作)分解为几个有联系的子任务,每个子任务由一个独立的功能部件来完成。

(3)在流水线中的每一个功能部件的后面都要有一个高速缓冲器用于保存本段的执行结果。

计算机的基本组成部分有哪些

计算机的基本组成部分有哪些计算机是一种高效的信息处理工具,它由多个基本组成部分构成,每个组成部分都发挥着重要的作用。

本文将介绍计算机的基本组成部分及其功能。

一、中央处理器(CPU)中央处理器是计算机的核心部件,主要负责解释和执行计算机程序。

它由控制单元和算术逻辑单元组成,控制单元负责控制数据流和指令的执行流程,算术逻辑单元负责完成各种运算操作。

中央处理器是计算机的大脑,决定了计算机的运算速度和性能。

二、内存(Memory)内存是计算机重要的存储器件,负责临时存储数据和程序。

它被分为主存储器和辅助存储器。

主存储器是计算机与外部世界直接交互的地方,包括随机存取存储器(RAM)和只读存储器(ROM)。

辅助存储器则用于长期存储和备份数据,如硬盘、光盘和闪存。

三、输入设备(Input Devices)输入设备用于将外部信息输入计算机系统,常见的有键盘、鼠标、扫描仪和摄像头等。

键盘和鼠标是最基本的输入设备,用户可以通过键盘输入文字和指令,通过鼠标控制光标和点击操作。

扫描仪和摄像头可以将纸质文件或实物物体转化为数字化的数据。

四、输出设备(Output Devices)输出设备用于将计算机处理的结果呈现给用户,最常见的输出设备是显示器和打印机。

显示器可以将文字和图像以可视化的形式展现出来,而打印机则将数据以纸质形式输出。

其他输出设备还包括音频设备和投影仪等。

五、存储设备(Storage Devices)存储设备用于永久存储和保存数据,以备将来使用。

常见的存储设备包括硬盘、固态硬盘和光盘等。

硬盘可以大容量地存储数据,固态硬盘具有更快的读写速度,而光盘则可以方便地存储、传播和备份数据。

六、总线(Bus)总线是计算机各组件之间进行通信和数据传输的通道。

它负责传递控制信号、地址和数据。

总线通常分为数据总线、地址总线和控制总线三种类型,数据总线用于传输数据,地址总线用于指定内存地址,控制总线用于传递控制信号。

七、操作系统(Operating System)操作系统是计算机的核心软件,负责管理和控制计算机的各种资源,提供良好的用户界面和支持各种应用程序的环境。

计算机体系结构——流水线技术(Pipelining)

单功能流水线:流水线只完成一种固定功能 多功能流水线:流水线可以完成多种功能,如 TI公司的ASC机,8段流水线,能够实现:定点加减 法、定点乘法、浮点加法等功能 3.按同一时间内各段之间的连接方式分 静态多功能流水线 :同一时间内,多功能结构只能按一种功能的连接方式工作。 动态多功能流水线:在同一时间内,可以有多种功能的连接方式同时工作 4.按处理的数据类型 标量流水线 向量流水线 5.按控制方式 同步流水线 异步流水线:当Si功能段要向Si+1段传送数据时,首 先发出就绪信号,Si+1功能段收到信号后,向Si回送 一个回答信号。 6.按任务从输出端的流出顺序 顺序流水方式:指令流出顺序 = 指令流入顺序 乱序流水方式:指令流出顺序 != 指令流入顺序 7. 线性流水线——不带反馈回路的流水线

三、流水线的分类(了解)

四、流水线相关及冲突(重点) 1.流水线相关 2.流水线冲突 3.流水线冲突带来问题 4.数据冲突及其解决方案 5.结构冲突及其解决方案 6.控制冲突及其解决方案

五、流水线性能分析(含例题讲解) 1.流水线的基本参数——吞吐率 2.流水线的基本参数——加速比 3.流水线的基本参数——效率 4.结果分析 5.有关流水线性能的若干问题

整体评估、反馈、再改进

3. 指令周期

单周期处理机模型:一个周期完成一个指令(每个周期是等长的),指令长度可能不一样,会造成很大的浪费 多周期处理机模型:将一个指令的完成划分成若干个周期来实现 流水线模型

二、流水线技术 1. 什么是流水线? 计算机中的流水线是把一个重复的过程分解为若干个子过程,每个子过程与其他子过程并行进行。由于这种工作方式与工厂中的生产 流水线十分相似, 因此称为流水线技术 从本质上讲,流水线技术是一种时间并行技术。

计算机由哪几部分组成

计算机由哪几部分组成计算机是一种能够进行数据处理和执行运算的机器,它由多个部分组成。

这些部分相互配合,共同完成计算机的功能。

下面,我们将介绍计算机由哪几部分组成。

1. 中央处理器(Central Processing Unit,CPU)中央处理器是计算机的“大脑”,负责执行指令、控制和协调各个部件的工作。

它由算术逻辑单元、控制单元和寄存器等组成。

算术逻辑单元负责进行各种运算操作,控制单元负责指挥各部件的工作,而寄存器则用于临时存储数据和指令。

2. 内存(Memory)内存是计算机的临时存储器,用于存储当前运行的程序和数据。

它分为主存储器和辅助存储器两部分。

主存储器通常指的是随机存取存储器(Random Access Memory,RAM),它能够快速地读写数据。

辅助存储器包括硬盘、固态硬盘和U盘等,用于长期存储数据。

3. 输入设备(Input Devices)输入设备用于将外部信息输入计算机。

常见的输入设备有键盘、鼠标、扫描仪和摄像头等。

键盘用于输入文本和命令,鼠标用于控制光标和进行操作,扫描仪和摄像头用于将纸质文档或图像转换成数字化的数据。

4. 输出设备(Output Devices)输出设备用于将计算机处理后的结果显示给用户。

常见的输出设备有显示器、打印机、喇叭和投影仪等。

显示器用于显示图像和文字,打印机可以将数据打印成纸质文档,喇叭用于播放声音,投影仪用于将图像投射到屏幕上。

5. 存储设备(Storage Devices)存储设备用于长期保存数据和程序。

除了辅助存储器外,还包括光盘、磁带和固态硬盘等。

光盘和磁带适用于大容量的数据存储,固态硬盘则以其高速读写和抗震抗摔的特点备受青睐。

6. 总线(Bus)总线是计算机内部各部件之间传输数据和信号的通道。

它分为数据总线、地址总线和控制总线等。

数据总线用于传输数据,地址总线用于指定数据的存储位置,控制总线则用于控制各部件的工作。

通过以上介绍,我们可以看到计算机由中央处理器、内存、输入设备、输出设备、存储设备和总线等几个部分组成。

计算机组成原理基础知识流水线技术和超标量处理器

计算机组成原理基础知识流水线技术和超标量处理器计算机组成原理基础知识:流水线技术和超标量处理器计算机组成原理是指计算机硬件的基本组成和工作原理。

在计算机科学与技术领域,流水线技术和超标量处理器是两个重要的概念。

本文将介绍这两种技术的基本原理和应用。

一、流水线技术流水线技术是指将一个复杂的操作分解成多个简单的子操作,并将这些子操作连续地执行,以提高计算机的指令执行效率。

在传统的自顶向下的设计方法中,计算机硬件主要包括控制器、运算器等单一功能模块,而在流水线技术中,计算机硬件被划分成多个阶段,每个阶段执行一个特定的功能子模块。

经典的流水线包括取指、译码、执行、访存和写回等阶段。

在取指阶段,计算机从存储器中读取指令;在译码阶段,计算机对指令进行解码并读取相应的操作数;在执行阶段,计算机执行相应的操作;在访存阶段,计算机对数据进行读写操作;在写回阶段,计算机将执行结果写回到寄存器或存储器。

流水线技术的优点是可以充分利用计算机硬件资源,提高指令的并行执行程度。

但是,流水线技术也存在一些问题,例如数据的相关性和冒险问题,需要通过一些技术手段来解决。

二、超标量处理器超标量处理器是一种在流水线技术基础上的改进方案。

传统的流水线技术中,每个阶段只能执行一个指令,而超标量处理器允许在同一个时钟周期内执行多个指令,以进一步提高计算机的执行效率。

超标量处理器主要依靠两个关键技术来实现多指令并行执行:乱序执行和动态调度。

乱序执行是指根据指令之间的依赖关系,按照合理的顺序执行指令,而不是按照指令在程序中的顺序执行。

动态调度是指通过硬件对指令进行调度,在不改变程序语义的前提下,尽可能地重排指令的执行顺序,以提高指令的并行度。

超标量处理器的工作原理可以简单描述为:在取指阶段,计算机从存储器中读取多个指令;在译码阶段,计算机对这些指令进行解码;在执行阶段,计算机并行执行多个指令;在访存阶段,计算机同时进行多个数据的读写操作;在写回阶段,计算机将执行结果写回到寄存器或存储器。

了解现代计算机体系结构

了解现代计算机体系结构现代计算机体系结构是指计算机硬件和软件之间的结构组织和交互方式。

了解现代计算机体系结构对于学习和理解计算机的工作原理以及技术发展具有重要意义。

本文将从计算机的组成、层次和关键技术等方面介绍现代计算机体系结构的基本知识。

一、计算机的组成现代计算机由硬件和软件两部分组成。

硬件部分包括中央处理器(CPU)、内存、输入输出设备等,软件部分则包括系统软件和应用软件。

计算机的硬件和软件之间通过总线进行连接和通信。

1. 中央处理器(CPU)中央处理器是计算机的核心部件,负责执行指令并处理数据。

它包括运算器和控制器两个部分。

运算器执行算术和逻辑运算,而控制器则负责指令的解码和执行,以及协调硬件的工作。

2. 内存内存是计算机中用于存储数据和指令的地方。

它分为主存和辅存两部分。

主存是CPU可以直接访问的部分,而辅存则用于长期存储数据和程序。

3. 输入输出设备输入输出设备用于与计算机进行信息交互。

常见的输入设备包括键盘、鼠标和扫描仪等,而输出设备则包括显示器、打印机和音响等。

二、计算机的层次现代计算机按照功能和抽象程度可以划分为多个层次,从下到上分别是硬件层、操作系统层、编程语言层和应用层。

1. 硬件层硬件层是计算机最底层的层次,包括CPU、内存、总线等硬件组件。

它负责执行指令和处理数据,是计算机系统的基础。

2. 操作系统层操作系统层是计算机系统的核心层次,它提供了对硬件的管理和控制。

操作系统负责调度进程、管理内存和文件系统等重要任务,为上层应用提供了统一的接口。

3. 编程语言层编程语言层是介于操作系统和应用层之间的层次。

它将高级语言翻译成计算机可以理解的机器语言,并提供了丰富的库和工具,方便程序员开发和调试应用程序。

4. 应用层应用层是计算机系统最上层的层次,包括游戏、办公软件、网络浏览器等各种应用程序。

应用层使用操作系统和编程语言提供的接口,实现特定的功能和任务。

三、现代计算机体系结构的关键技术现代计算机体系结构涉及多个关键技术,在提升计算机性能和功能方面起到重要作用。

按照流水线的级别来分计算机结构

AB 输入

AB 输入

AB 输入

AB 输入

求阶差

求阶差

求阶差

求阶差

对阶

对阶

对阶

对阶

尾数加

尾数加

尾数加

尾数加

规格化

规格化

规格化

规格化

尾数乘

尾数乘

尾数乘

尾数乘

累加

累加

累加

累加

输出

输出

g= f(A ,B)

(a)功能段间的互连

定点乘 (b)定点乘法

输出

输出

浮点加

浮点点积

(c)浮点加法 (d)浮点点积

4、静态流水线与动态流水线

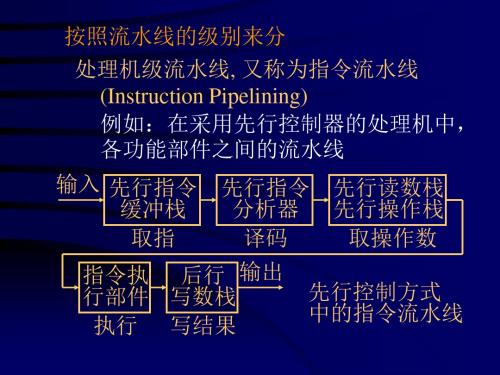

按照流水线的级别来分

处理机级流水线, 又称为指令流水线

(Instruction Pipelining) 例如:在采用先行控制器的处理机中, 各功能部件之间的流水线

输入 先行指令 先行指令 先行读数栈 缓冲栈 分析器 先行操作栈

取指

译码

取操作数

指令执 后行 输出

行部件 写数栈

先行控制方式

执行 写结果

中的指令流水线

静态流水线: 同一段时间内,多功能流水线中的各个 功能段只能按照一种固定的方式连接, 实现一种固定的功能。 只有连续出现同一种运算时,流水线的 效率才能得到充分的发挥。

动态流水线: 在同一段时间内,多功能流水线中的各 段可以按照不同的方式连接,同时执行 多种功能。

空间

浮点加法 定点乘法

输出

1 2 3…n

水线或异步流水线等

输入 就绪 回答

就绪

就绪

S1 回答 S2 回答 S3

输出 就绪 回答

5.2.3 线性流水线的性能分析

流水线(Pipeline)介绍

ID 段 Reg EX 段 MEM 段 DM WB 段 Reg

IF 段 IM

流水线寄存器

13

ALU

2.3 数据冒险

一条指令必须等到另一条指令的完成而造成 的流水线暂停的情况叫做数据冒险。形如: add $s0, $t0, $t0 sub $t2, $s0 $t3 加法指令需要到WB阶段后才写回结果,减法 指令此时才可以继续执行。在不任何干预的 情况下,流水线白白浪费了三个时钟周期。

Can’t happen in MIPS 5 stage pipeline because: - All instructions take 5 stages, and - Writes are always in stage 5

18

读后写冲突(WAR: Write After Read)

在 i 读之前,j 先写。i 读出的内容是错误的! 这对应“反相关” ,寄存器换名技术可以消 除

转发(旁路)方式解决数据冒险

形如:add $s0, $t0, $t0 sub $t2, $s0 $t3,减法指令要等到加 法指令写回寄存器堆时才可以执行指令,浪 费了时间。转发技术:在加法指令在ALU运 算一结束就将结果送给减法指令的输入项。 这样从内部资源中直接提前得到缺少的运算 项的过程叫做转发。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

≈

5分钟

做四道菜

8+分钟

20分钟

连续工作

每1+分钟上一道菜 < 每5分钟上一道菜 ≈5倍

“超级流水线”

“超级流水线”技术 (Super Pipelining)

◦ 将五级流水线细分为更多的阶段,增加流水线的深度

◦ 提升时钟频率,从而提高指令吞吐率

五级流水线 S1

S2

S3

S4

S5

◦ 时钟周期:200ps+50ps=250ps

IMem Reg ALU DMem Reg

instruction 5

IMem Reg ALU DMem Reg

如果指令和数据放在同一个存储器中,则不能同时读存储器 解决方案2:指令和数据放在不同的存储器中

结构冒险(示例2)

时间(ps)0 200 400 600 800 1000 1200 1400 1600 1800 2000 2200 2400

切菜

炒菜

装盘

1分钟

2分钟

1分钟

1分钟

不平衡的流水线 流水线方式

非流水线方式

单独一道菜

8+分钟

>

5分钟

做四道菜

14+分钟

20分钟

连续工作

每2+分钟上一道菜 < 每5分钟上一道菜

≈2.5倍

流水线的调整

时钟周期=1分钟

洗菜

切菜1

切菜2

炒菜

装盘

1分钟

1分钟

1分钟

1分钟

1分钟

平衡的流水线 流水线方式

非流水线方式

本节主题

流水线的优化

北京大学 · 慕课 计算机组成

制作人:陆俊林

流水线的分析

洗菜

时钟周期=1分钟

切菜

炒菜

装盘

1分钟

单独一道菜 做四道菜 连续工作

1分钟

1分钟

1分钟

流水线方式

非流水线方式

4+分钟

≈

4分钟

7+分钟

16分钟

每1+分钟上一道菜 < 每4分钟上一道菜

≈4倍

流水线的平衡性

洗菜

时钟周期=2分钟

IF ID EX MEM WB

lw …

IMem Reg ALU DMem Reg

instruction 1 IMem Reg ALU DMem Reg

instruction 2

IMem Reg ALU DMem Reg

bubble bubble bubble bubble bubble

instruction 3 instruction 4

IF ID EX MEM WB

lw …

IMem Reg ALU DMem Reg

instruction 1 IMem Reg ALU DMem Reg

instruction 2

IMem Reg ALU DMem Reg

IMem Reg ALU DMem Reg IMem Reg ALU DMem Reg

如果指令和数据放在同一个存储器中,则不能同时读存储器 解决方案1:流水线停顿(stall),产生空泡(bubble)

结构冒险(示例1)

时间(ps)0 200 400 600 800 1000 1200 1400 1600 1800 2000 2200 2400

十级流水线 S1 S2 S3 S4 S5 S6 S7 S8 S9 S10

◦ 时钟周期:100ps+50ps=150ps

流水线的深度

流水线的级数是越多越好吗?

◦ 否!

五级流水线 S1

S2

S3

S4

S5

◦ 时钟周期:200ps+50ps=250ps

◦ 单条指令的延迟:1250ps

◦ 流水线寄存器延迟所占比例:50ps / 250ps = 20%

IMem Reg ALU DMem Reg

instruction 5

IMem Reg ALU DMem Reg

如果指令和数据放在同一个存储器中,则不能同时读存储器

结构冒险(示例1)

时间(ps)0 200 400 600 800 1000 1200 1400 1600 1800 2000 2200 2400

IF ID EX MEM WB

IMem Reg ALU DMem Reg

instruction 1 IMem Reg ALU DMem Reg

instruction 2

IMem Reg ALU DMem Reg

instruction 3

IMem Reg ALU DMem Reg

instruction 4

lw …

IF ID EX MEM WB

IMem Reg ALU DMem Reg

instruction 1 IMem Reg ALU DMem Reg

instruction 2

IMem Reg ALU DMem Reg

instruction 3

IMem Reg ALU DMem Reg

instruction 4

1991年,R4000(64位): 8级

1993年,Pentium: 5级 1995年,Pentium Pro: 12级

取指

译码

地址生成

执行

回写

IF1 IF2 IF3 ID1 ID2 RAT ROB DIS EX WB RR RET

1997年,ARM9: 5级 2002年,ARM11: 8级

取指

译码

① 结构冒险

◦ 所需的硬件部件正在为之前的指令工作

② 数据冒险

◦ 需要等待之前的指令完成数据的读写

③ 控制冒险

◦ 需要根据之前指令的结果决定下一步的行为

结构冒险(示例1)

时间(ps)0 200 400 600 800 1000 1200 1400 1600 1800 2000 2200 2400

lw …

十级流水线 S1 S2 S3 S4 S5 S6 S7 S8 S9 S10

◦ 时钟周期:100ps+50ps=150ps

◦ 单条指令的延迟:1500ps

◦ 流水线寄存器延迟所占比例:50ps / 150ps = 33%

处理器流水线深度的变化

1986年,R2000: 5级

1988年,R3000: 5级

2010年,Cortex-A9:11级

2013年,Core i7(Haswell):14级

2013年,Cortex-A57:15级

本节小结

流水线的优化

北京大学 · 慕课 计算机组成

制作人:陆俊林

本节主题

流水线的“冒险”

北京大学 · 慕课 计算机组成

制作人:陆俊林

“冒险”(Hazard)

阻止下一条指令在下一个时钟周期开始执行的情况

取指1 取指2 译码

执行

访存

写回

发射 执行1 执行2 执行3 写回

2004年,Pemtium 4(Prescott):31级

2006年,Core 2 Duo(Merom):14级

2008年,Core i7(Nehalem):16级

2009年,Cortex-A8:13级

2011年,Cortex-A15:15级