第11章运放设计补充精品PPT课件

第11章 集成运算放大器及其应用

上式表明,差动放大电路的差模电压放大倍数和 单管放大电路的电压放大倍数相同。多用一个放大管 后,虽然电压放大倍数没有增加,但是换来了对零漂 的抑制。这正是差动放大电路的优点。

差动放大电路对共模输入信号的放大倍数叫做共 模电压放大倍数,用Auc表示,可以推出,当输入共 模信号时,Auc为

Au c u o u C1 u C 2 0 0 ui c ui1 ui1

由于集成运放的电压放大倍数Ao d和输入电阻Ri d 都非常大(理想情况下,两者约等于∞),于是可以 推得 u u

i i 0

注意:“虚短”和“虚断”是理想运放工作在线 性区时的两个重要特点。这两个特点常常作为今后分 析运放应用电路的出发点,因此必须牢固掌握。

(2)集成运放工作在非线性区的特性 如果运放的工作信号超出了线性放大范围,则输 出电压与输入电压不再满足式(11-1),即uo不再随 差模输入电压(u+ - u -)线性增长,uo将达到饱和。 此时集成运放的输出电压uo只有两种取值:或等于运 放的正向最大输出电压+UOM,或等于其负向最大输 出电压-UOM,具体为 当u + >u - 时,uo = +UOM 当u + <u - 时,uo = -UOM 另外,因为集成运放的输入电阻Ri d很大,故在 非线性区仍满足输入电流等于零,即式(11-3)对非 线性工作区仍然成立。

有时,为了简化起见,常常不把恒流源式差动放 大电路中恒流管T3的具体电路画出,而采用一个简化 的恒流源符号来表示,如图11-7所示。

二、输出级——功率放大电路 集成运放的输出级是向负载提供一定的功率,属 于功率放大,一般采用互补对称的功率放大电路。 1. 功率放大电路的特点 (1)因为信号的幅度放大在前置电路中已经完成, 所以功率放大电路对电压放大倍数并无要求。由于射 极输出器的输出电流较大,能使负载获得较大输出功 率,并且它的输出电阻小,带负载能力强,因此通常 采用射极输出器作为基本的功率放大电路。不过单个 的射极输出器对信号正负半周的跟随能力不同,在实 用的功率放大电路中大多采用双管的互补对称电路形 式。

第十一章运算放大器-PPT精品

愈高,所构成的运算电路越稳定,运算精度也越高。

3. 输入失调电压 UIO 4. 输入失调电流 IIO 愈小愈好 5. 输入偏置电流 IIB 6. 共模输入电压范围 UICM

运放所能承受的共模输入电压最大值。超出此值, 运放的共模抑制性能下降,甚至造成器件损坏。

称反相输入端“虚

输以出后的如另不一加端说均明为,地输()入。、地特”点—uo

因要求静态时u+、 u– 对

地电阻相同, 所以平衡电阻 R2 = R1 // RF

Auf

反相输入的重要

RF R1

ui

uo RF

ui

R1

总目录 章目录 返回 上一页 下一目录 章目录 返回 上一页 下一页

2. 同相比例运算 (1)电路组成

RF

R1 u– –

+

+ ui

R2 u+ +

–

(2)电压放大倍数

因虚断,所以u+ = ui

u

R1 R1 RF

uo

+ 因虚短,所以 u– = ui , uo 反相输入端不“虚地”

–

uo

(1

RF R1

)ui

因要求静态时u+、u对地 电阻相同,

偏置电路是为各级提供合适的工作 电流。

总目录 章目录 返回 上一页 下一页

反相 输入端

u–

u+

同相 输入端

输入级

+UCC 输出端

uo 中间级 输出级 –UEE

总目录 章目录 返回 上一页 下一页

左图所示为μA741集成运算放大器的芯片实物外形图

多级放大器及运算放大器

ɺ Uo

–

– 第二级

负载

总目录 章目录 返回 上一页 下一页

1. 静态分析 RB1

C1

RC1 T1 RE1

+

C2

′ RB1

RC2 T2 RE2

+UCC +

C3

+

+

ɺ + UO1 ′ RB2 C

E1

ɺ RB2 + Ui ɺ ES – –

RS

+

+ + RL

CE2

ɺ Uo

–

–

由于电容有隔直作用, 由于电容有隔直作用,所以每级放大电路的直流 通路互不相通,每级的静态工作点互相独立, 通路互不相通,每级的静态工作点互相独立,互不 影响,可以各级单独计算。 影响,可以各级单独计算。 两级放大电路均为共发射极分压式偏置电路。 两级放大电路均为共发射极分压式偏置电路。

IE1 = (1 + β )IB1 = (1 + 50)× 0.0098= 0 .49mA UCE = UCC − IE1RE1 = 24− 0.49× 27 = 10 .77V

总目录 章目录 返回 上一页 下一页

第二级是分压式偏置电路 【解】

+24V RB1 1MΩ Ω C1 + T1 RE1 27kΩ Ω RC2 Ω 82kΩ 10kΩ Ω C2 + T2

RB1 1MΩ Ω C1 + T1 RE1 27kΩ Ω RC2 Ω 82kΩ 10kΩ Ω C2 + T2

+24V

′ RB1

C3 + +

+

ɺ Ui

–

43kΩ 7.5kΩ Ω Ω

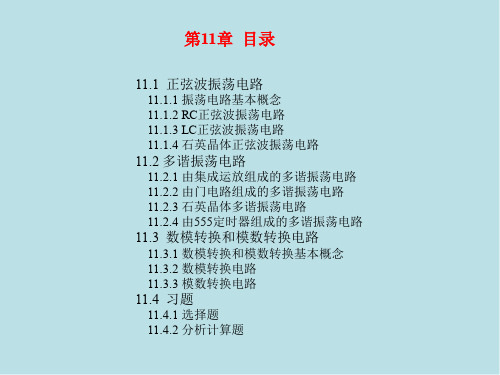

电工与电子技术基础第11章 振荡与信号转换电路

高低阈值电压分别为:+UZR2 和

R1 + R2

-U ZR2 R1 + R2

⒉

振荡周期: T =2Rf C ln (1+

2R2 R1

)

⒊ 矩形波发生器

改变电容C充放电时间常数, 可使方波变为矩形波。

高电平时间ton与周期T的比值

称为占空比,

用q表示:q=

ton T

图11-18

图11-17

11.2.2 由门电路组成的多谐振荡器

解:D=10100000B=160,28=100000000B=256

【例11-9】已知UREF=5V,模拟电压UA=3V, 试求其相应的10位数字电压D。

解:

11.3.2 数模转换电路

⒈ 主要技术指标

⑴ 分辨率

定义: D/A转换器的最小输出电压与最大输出电压之比。 计算公式:1/(2n-1) 例如,对于一个8位D/A转换器,其分辨率为:

tW1 =(R1+R2)C ln2 tW2 =R2C ln2

11.3 数模转换和模数转换电路

11.3.1 数模转换和模数转换基本概念

⒈ 定义

⑴ 数模转换:将数字信号转换为相应的模拟信号称为数模转换 ⑵ 模数转换:将模拟信号转换为相应的数字信号称为模数转换

⒉ 数字信号与相应模拟信号之间的量化关系

【例11-8】已知UREF=10V,8位数字量D=10100000B, 试求其相应模拟电压UA。

11.1.1 正弦振荡基本概念

⒈ 自激振荡的条件 : AF =1

又可分解为振幅平衡条件和相位平衡条件。

振幅平衡条件: | AF |=1

相位平衡条件:φa +φf =2nπ(n=0,1,2,3,…)

第11章集成运算放大器精品PPT课件

结论:反相输入端为 “虚地”。

注意 当反相输入端接地

R1

时, 因为存在负反馈信号, 同

相输入端 不是“虚地”!ui

R2

RF 第11章 11.1

uo

RF

uo

第11章 11.1

运放工作在线性工作状态的必要条件: 运放必须加上深度负反馈,如RF。

3.理想运放非线性工作的分析依据

“虚断路”原则

ii

ii

=

ui rid

(2) “虚短路”原则

ui = u+ – u-= —Au–ouo

–

ui

+ uo

+

对于理想运放 Auo ui 0

u– u+ 相当于两输入端之间(虚)短路

(3) “虚地”的概念

当同相输入端接地时,

ui

R1

由“虚断路”原则 ii = 0 , 有 u+= 0

R2

由“虚短路”原则 u_ u+ = 0

第11章 目录

第11章 集成运算放大器

11.1 运算放大器的简单介绍

11.3 运算放大器在信号运算方面的应用

11.4 运算放大器在信号处理方面的应用

11. 1 运算放大器的简单介绍

集成运放概述

第11章 111

集成运放是具有高开环电压放大倍数,并带有深度负反馈的 的直接耦合放大器。

1. 电路符号

反相 输入端

= 1 + RRF1 R2R+3R3 ui2

R3

uo = u'o + u"o = 1+ RRF1RR2+3R3ui2- RRF1 ui1

第11章 11.3

u o''

运算放大器ppt课件

• 运算放大器是可以对电信号进行运算,一 般具有高增益、高输入阻抗和低输出阻抗 的放大器。

• 运算放大器最早被设计出来的目的是用来 进行加,减,微分,积分的模擬数学运算, 因此被称为“运算放大器” 。同时它也成 为实现模拟计算机(analog computer)的 基本建构单元。

VOLTAGE RANGE LOW INPUT BIAS AND OFFSET CURRENT HIGH INPUT IMPEDANCE J–FET INPUT STAGE INTERNAL FREQUENCY COMPENSATION

• 第一代产品基本沿用了分立元件放大电路的设计思想,采 用集成数字电路的制造工艺,利用了少量横向PNP管,构 成以电流源做偏置电路的三级直接耦合放大电路。

• 第二代产品普遍采用了有源负载,简化了电路的设计,并 使开环增益有了显著提高,各方面性能指标比较均衡,属 于通用型运放。

• 第三代产品的输入级采用了超β管,β值高达1000~5000倍, 而且版图设计上考虑了热效应的影响,从而减小了失调电 压、失调电流以及他们的温漂,增大了共模抑制比和输入 电阻。

2.运算放大器的参数和分类

• 主要有低频增益、单位增益频率、相位边 限移电压、还有噪声等

• 按工作原理可分为电压放大型、电流放大 型、跨导型和互阻型。

• 按性能指标可分为高阻型、高速型、高精 度型和低耗型

3.集成运放的发展概况

• 第四代产品采用了斩波稳零和动态稳零技术,使各性能指 标参数更加理想化。

ST(意法半导体)的运放产品

• LF147 WIDE BANDWIDTH QUAD J-FET

OPERATIONAL AMPLIFIERS

LOW POWER CONSUMPTION WIDE COMMON-MODE (UP TO VCC+) AND DIFFERENTIAL

运算放大器设计.ppt

总的输入噪声: VOUTENTGNBW

输出噪声:

计算例:

运放

LT1028,BW=0-1000Hz,电 阻 值 如 图

E n 0 .9 ( n V / E I = I N ( R 1 / / R

E

R

R / 8(nV /

Hz )

2 )= 1 p A

Hz

Hz ) 1/8

E NT

E N 2 E I2 E R2

3应用技巧调零电路运算放大器性能扩展技术提高输出电压提高输入电阻单电源供电问题三应用举例1信号放大反相放大同相放大差动放大u1alf347nu2alf347nr110kr210kr310kr410kr510kr610kr710kr820ku3alf347nr920kv211121314xsc1xda1thdxfg115仪表放大仪器放大器输人端的屏蔽防护方法2模拟运算反相型加法器基本积分器对数运算器具有温度补偿的指数运算器乘除发器对数逆对数幂运算器电流电压变换器3电流电压转换电荷放大器5滤波电路u1741bal1bal2vsvsr120kr220kr310kc1470nfc2470nfv112v212vovivpk1000hzr410k6电压比较以及波形产生过零比较器741xfg11k1kxsc102bz2250002bz22反相滞回比较器c147nfr220k50220kkeyarw2r451kr520kd102dz47d202dz47u1741bal1bal2vsvsv112v312r120k用反相滞回比较器实现的方波电路其他波形发生电路7低噪声运放电路噪声模型手册已知op的宽带噪声输入电压密度输入电流噪声密度给定电阻阻值

微功耗 仪表放 大器

USD 1.05

0.0 12

250

5+2 12 0/G 0

第11章ADDA转换器

(0 22 1 21 0 20 ) 0.5V 1V

6. A/D转换

将采样保持电路锁存的模拟信号转换成数字信号的器件。

11.3.2 A / D转换器的原理(P401) 按转换方式可分为:直接转换、间接转换。

计算机控制系统方框图如下:

… …

… …

…

被

传 感

滤波 放大

多路转 换开关

A/D

计

器

算

控

机

对

系

象

执行 机构

模拟 开关

功 放

D/A

统

11.2 数/模( D/A )转换器(P391)

定义:数字—模拟转换。把数字信号转换为模拟信号输出的器件 称为数/模转换器(简称D/A转换器)。 11.2.1 D/A转换器的原理

n

V0

V ai

2i

R

i 1

4. 集成化D/A转换器 分类:双极型和CMOS型 电阻网络:离子注入或扩散电阻条、薄膜电阻 离子注入或扩散电阻条:价廉物美,但精度不高; 薄膜电阻:高精度。 特点: 双极型:转换速度快,适合于高速转换的场合。 CMOS型:优点是制造容易、造价低;缺点是转换速度较慢。

JMP T1

HLT

输出三角波(设D/A的口地址为300H)

MOV DX,300H R0:MOV CX,0FFH

MOV AL,00H R1:OUT DX,AL

INC AL LOOP T1 MOV CX,0FFH R2:DEC AL OUT DX,AL LOOP T2 JMP R0 HLT

输出锯齿波(设D/A的口地址为300H) MOV DX,300H MOV AL,00H

第22讲 第十一章放大电路基础(四)及第十二章线性集成运算放大器和运算电路

(2)并联负反馈使输入电阻减少由于基本放大电路与反馈电路在输入回路中并联,如图所示,由于,在相同的V i作用下,因I f的存在而使I i增加,因此,并联负反馈使输入电阻R if=V i/I i减小。

所以,并联负反馈使输入电阻减小倍。

●负反馈对放大电路输出电阻的影响◆电压负反馈使输出电阻减小电压负反馈取样于输出电压,又能维持输出电压稳定,即是说,输入信号一定时,电压负反馈的输出趋于一恒压源,其输出电阻很小。

有电压负反馈时的闭环输出电阻为无反馈时开环输出电阻的1/(1+ )①。

反馈愈深,R of愈小。

◆电流负反馈使输出电阻增加电流反馈取样于输出电流,能维持输出电流稳定,就是说,输入信号一定时,电流负反馈的输出趋于一恒流源,其输出电阻很大。

有电流负反馈时的闭环输出电阻为无反馈时开环输出电阻的1/(1+ )倍。

反馈愈深,R of愈大11.2.5 深度负反馈放大电路近似计算的一般方法● 近似计算的根据 根据和的定义 ,在 中,若 , 则 即 所以有此式表明,当 时,反馈信号 与输入信号 相差甚微,净输入信号 甚小,因而有对于串联负反馈有 (虚短), ;对于并联负反馈有 、, (虚断)。

利用“虚短”、“虚断”的概念可以以快速方便地估算出负反馈放大电路的闭环增益 或闭环电压增益。

● 近似计算的方法1.判别反馈类型,正确识别并画出反馈网络。

注意电压取样时不要把直接并在输出口的电阻计入反馈网络;电流求和时不要把并在输入口的电阻计入反馈网络。

2.在反馈网络输入口标出反馈信号:电压求和为开路电压fv ,电流求和时为短路电流fi ,再由反馈网络求出反馈系数F 。

要注意标fv 时在反馈网络入口标上正下负;标fi 时必须在反馈网络入口以上端流入为参考方向。

3.求闭环增益 ,注意不同的反馈类型fA 的量纲不同。

4.由fA 求闭环源电压增益vsfA 。

电压取样电压求和时:s f vsf v v A A 0==电压取样电流求和时:00f vsf s s s sA v vA v i R R ===电流取样电压求和时:00L vsf f Ls sv i R A A R v v ''⋅'===电流取样电流求和时:00f L L vsfs s s sA R v i R A v i R R '''⋅===⋅其中:0i '是输出管的管端输出电流,即取样电流。

运算放大器ppt 介绍共55页

▪

27、只有把抱怨环境的心情,化为上进的力量,才是成功的保证。——罗曼·罗兰

▪

28、知之者不如好之者,好之者不如乐之者。——孔子

▪

29、勇猛、大胆和坚定的决心能够抵得上武器的精良。——达·芬奇

▪

30、意志是一个强壮的盲人,倚靠在明眼的跛子肩上。——叔本华

Hale Waihona Puke 谢谢!5539、没有不老的誓言,没有不变的承 诺,踏 上旅途 ,义无 反顾。 40、对时间的价值没有没有深切认识 的人, 决不会 坚韧勤 勉。

▪

26、要使整个人生都过得舒适、愉快,这是不可能的,因为人类必须具备一种能应付逆境的态度。——卢梭

运算放大器ppt 介绍

36、“不可能”这个字(法语是一个字 ),只 在愚人 的字典 中找得 到。--拿 破仑。 37、不要生气要争气,不要看破要突 破,不 要嫉妒 要欣赏 ,不要 托延要 积极, 不要心 动要行 动。 38、勤奋,机会,乐观是成功的三要 素。(注 意:传 统观念 认为勤 奋和机 会是成 功的要 素,但 是经过 统计学 和成功 人士的 分析得 出,乐 观是成 功的第 三要素 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

37

Lmin

0.5,NMOS

: Vdsat

0.2V,fT

3 2

20 109 0.2 6.28 0.25

Hz

3.8GHz

4

北大微电子:模拟集成电路原理

高增益vs高速

5

北大微电子:模拟集成电路原理

非主极点的极限频率(1)

6

北大微电子:模拟集成电路原理

非主极点的极限频率(2)

7

北大微电子:模拟集成电路原理

28

北大微电子:模拟集成电路原理

最小包围(enclosure)

• 如N扩散区应被N注 入区包围

• Cantact应被Poly或 者Metal1包围

• 在被包围图形周围留 够余量

29

北大微电子:模拟集成电路原理

最小延伸(extension)

• Poly在有源区外延伸

– 工艺偏差 – 确保边缘部分正常

北大微电子:模拟集成电路原理

• 运放的带宽极限 • 常见的运放结构 • 偏置电路的设计 • 版图设计

– 设计规则 – 天线效应 – 减小栅电阻与漏寄生电容 – 对称性设计

25

设计规则

北大微电子:模拟集成电路原理

• 设计规则分类

– 最小宽度(width) – 最小间距(spacing) – 最小包围(enclosure) – 最小延伸(extension)

26

北大微电子:模拟集成电路原理

最小宽度(width)

• 掩模版定义的几何图 形,其宽度必须大于 某个值

• 偏差:取决于光刻和 工艺水平

• 层厚度越小,该层允 许的最小宽度也越小

27

北大微电子:模拟集成电路原理

最小间距(spacing)

• 同层图形:

– 金属短路

• 不同层图形:

– 扩散区与多晶硅

1

L1

设 Vdsat0 Vdsat ,则Vdsat5 Vdsat ,Vdsat45

Vb3 Vb4 M 1 1 Vdsat

Vb4 Vb3 Vdsat,所以M 3 通常M的取值为4 ~ 6

M 1 Vdsat

23

北大微电子:模拟集成电路原理

Vb1~Vb4的产生

24

本讲内容

• 运放的带宽极限 • 常见的运放结构 • 偏置电路的设计 • 版图设计

11

北大微电子:模拟集成电路原理

五MOSFET运放

12

北大微电子:模拟集成电路原理

套筒式共源共栅运放

13

北大微电子:模拟集成电路原理

对称结构运放

14

北大微电子:模拟集成电路原理

对称结构运放

15

北大微电子:模拟集成电路原理

折叠共源共栅运放

16

北大微电子:模拟集成电路原理

两级Miller运放

17

北大微电子:模拟集成电路原理

两级Miller运放

18

北大微电子:模拟集成电路原理

两级Miller运放

19

本讲内容

北大微电子:模拟集成电路原理

• 运放的带宽极限 • 常见的运放结构 • 偏置电路的设计 • 版图设计

20

北大微电子:模拟集成电路原理

偏置电路(PMOS)

W2/L2 W2/ML2 W2/L2

Vb4 Vdd VGS0 Vdd Vth0 Vdsat0 M 4、M 5串联后的晶体管M 45

VGS 45、Vdsat45

Vb3 Vb4 VGS45 VGS5

若M 0、M 5均取 W2 L2

而M

2取

W2 M L2

,因此M

45的等效沟长 M

而M

2取

W1 ,因此M N L1

23的等效沟长 N

1

L1

设Vdsat1 Vdsat,则Vdsat 3 Vdsat,Vdsat 23

Vb2 Vb1 N 1 1 Vdsat

Vb2 Vb1 Vdsat,所以N 3

通常N的取值为4 ~ 6

N 1 Vdsat

22

北大微电子:模拟集成电路原理

30

北大微电子:模拟集成电路原理

设计规则与版图

31

本讲内容

北大微电子:模拟集成电路原理

• 运放的带宽极限 • 偏置电路的设计 • 版图设计

– 设计规则 – 天线效应 – 减小栅电阻与漏寄生电容 – 对称性设计

32

天线效应

北大微电子:模拟集成电路原理

• 刻蚀第一层金属时,这层金属就像一根天线, 会收集离子。

• 图a:简单折叠,减小漏端电容 • 图b:减小栅电阻Rg,使Rg<1/gm • 低噪声应用:Rg为1/gm的1/5~1/10。 • 以上Rg、gm为单个叉指管的参数

35

北大微电子:模拟集成电路原理

叉指数目:奇数vs偶数

叉指数目为偶数时 漏区面积最小 通常叉指数目为偶数

36

北大微电子:模拟集成电路原理

• 面积越大,收集的离子越多,击穿栅氧。图(a) • 解决方法:通过Metal2过渡。图(b)

33

本讲内容

北大微电子:模拟集成电路原理

• 运放的带宽极限 • 偏置电路的设计 • 版图设计

– 设计规则 – 天线效应 – 减小栅电阻与漏寄生电容 – 对称性设计

34

北大微电子:模拟集成电路原理

叉指晶体管

MOSFET的截至频率fT

CGS

2 3

WLCox,而gm

nCox

W L

Vdsat,Cox

3 fF

/2

iGS

iDS时,MOSFET的截至频率fT

gm 2CGS

3 2

Vdsat 2L2

nCox

60A /V

2, pCox

30A /V

2, 反推得n

20 109

m2 V

Hz, p

10 109

m2 V

Hz

高速Miller运放的设计(1)

8

北大微电子:模拟集成电路原理

高速Miller运放的设计(2)

L 1

1

2CGS 6

1

1

fT

1 1

fT 8

GBW fT 16

9

北大微电子:模拟集成电路原理

GBW最大值与L的关系

10

本讲内容

北大微电子:模拟集成电路原理

折叠共源共栅运放

Vb4 Vb3

Vb2 Vb1

21

北大微电子:模拟集成电路原理

偏置电路(NMOS)

W1/L1 W1/NL1 W1/L1

Vb1 VGS1 Vth1 Vdsat1 M 2、M 3串联后的晶体管M 23

VGS 23、Vdsat 23

Vb2 Vb1 VGS 23 VGS 2

若M1、M 3均取 W1 L1

北大微电子:模拟集成电路原理

第11章 运放设计补充

授课教师:鲁文高 Email:

2008年5月19日、22日

1

本讲内容

北大微电子:模拟集成电路原理

• 运放的带宽极限 • 常见的运放结构 • 偏置电路的设计 • 版图设计

2

北大微电子:模拟集成电路原理

MOSFET的寄生电容

3

北大微电子:模拟集成电路原理