PCB画图笔记

Allegro16.3—PCB设计笔记详解

Allegro16.3—PCB设计笔记详解打开PCB Editor。

一般选择第一项操作选择显示内容View——Customize Toolbar可以设置软件的菜单栏显示模块Commands是可以自定义工具查看各种层Display——Color/Visibility封装的制作在Pad Designer中操作此项首先制作贴片式焊盘的做法Candence制作封装需要先制作焊盘打开制作焊盘的软件开始>程序>candence>release 16.3>PCB Editer Utilities>Pad Designer表贴焊盘就不用填写Themal Relief(散热焊盘)和Anti Pad(绝缘层焊盘)了这是建立好的焊盘文件然后打开PCB Editor——File——New——设置图纸大小Setup——Design Parameter Editor——Design User Unist(单位)选择Extents项中Left X和Lower Y为原点的坐标定义,Width和Heigh 为做封装时图纸的大小>Type项不变,仍为Package(封装)。

都改为0.0254(最小步进值)开始加入焊盘>Layout>Pin>>Option中如下设置创建一个零件库必须的几个条件:1至少一个引脚。

2每个零件必须有图形边框,即轮廓线,线路板上丝印层白漆所画的轮廓。

3参考编号。

4要有Place_bound,即安装区,防止元器件之间的叠加。

做通孔类焊盘的时候要求焊盘过孔镀锡后要比元件引脚直径大0.2或0.3毫米最好。

这样有利于波峰焊是焊锡往上走。

同时也利于排气。

如果孔太小,气体跑不出来,会夹杂在焊锡里,孔太大,元件会发生偏斜。

元件孔包括镀层(铜色的约0.1毫米),镀锡1)首先添加Assembly_T op2)然后设置丝印层边框3)放置Add——Rectangle4)放置参考编号Layout——Labels Ref Des继续放置丝印层,并且放在第一个引脚的边上。

PCB笔记

主要讲述pcb设计部分,以此弥补博客上altium designer pcb设计部分的空缺,由于本人能力有限,还望大家指正。

--- 瑟伊雨

(2)选择右下角的pcb---board insight—可以察看放大的鼠标移动到得区域快捷键f2, 在description中可以查看元器件的属性

(3)当然也可以用pgup pgDn

(4) 在右边有一栏pcb ,主要是用来查看pcb的, 选net 、再选 mask 、再在下面一栏、 选择一些东西可以查看pcb图中的组件 。按住 shift+c 可以清除,可以点击右下方的clear也可以清除。在clear左边有个mask level 可以调节屏蔽的亮度 。下面的小图也可以查看pcb。

(7)按快捷建j 中可以让鼠标跳转到你想到找到的器件或者连接等

12. 在栏的上角有个针状的箭头,点击它可以锁定在哪个面板也可以解除锁定

13. 左右面板上的信息栏全部在下方的system中找到

14. pcb设计中slice tracks的作用是切线

15. 在pcb环境下设置参考点(也就是和schematic中reference一样):edit---origin—set

(2)元器件的对齐方法:选中元器件后右击选择align,这里面有一些对齐的操作,快捷键为a

(3)元器件在底层和顶层之间的切换;选择器件在拖动的过程中按L(而不是单击);或者双击打开属性 对话框,在那里面设计也可

(4)五种走线模式:(a)45度走线;按下空格可以改变是出发处45度还是终点处

(b)圆弧行:按下shift+空格,会切换到该走线模式

(1). 丝印文字层:(Topoverlay或Bottomoverlay层)即上图我们看到的白色字符层。颜色也可为其它颜色,如果省成本或保密,做PCB时也可不把这层印出来。

PCB高级绘图知识

5)制定设计规则

Routing布线规则设置:主要用于自动布线,包括:Width导 线宽度设置、Routing Topology布线拓扑规则设置、 Routing Priority:布线优先级设置、Routing Layers布线 层设置、Routing Coners导线拐角模式设置、Routing Vias过孔设置、Fanout Control导线散开方式设置:

6)PCB布线 自动布线: 设计自动布线策略:单击菜单“自动布 线”→“设定”,会弹出“Situs布线策略” 对话框

6)PCB布线 单击“追加”按钮将弹出“Situs策略编辑器” 对话框,可进行布线策略设置:

6)PCB布线 自动布线:单击“自动布线”,选择相应子菜单

6)PCB布线

全部对象:将弹出布线策略对话框,进行布线前布线策略 的选择,选择好自动布线策略后单击“Route All”,系统根 据布线规则和布线策略对PCB进行全局布线,布线过程中 会弹出“Messages”面板显示自动布线状态信息:

5)制定设计规则 Plane内电层规则设置:包括Power Plane Connect Style内电层连接方式设置,Power Plane Clearence内电层安全间距设置,Polygon Connect Style多边形覆铜连接方式设置:

5)制定设计规则 Testpoint测试点规则设置:用于信号仿真调试 时测试点的设置,包括Testpoint Style测试点 样式设置,Testpoint Usage测试点使用规则 设置:

5)制定设计规则 SMT表面贴装技术规则设置:针对表贴式工艺走线 设置,包括SMD To Corner表贴式元件焊盘与拐 角最小间距设置、SMD To Plane表贴式元件焊 盘与内电层过孔间距设置、SMD Neck-Down表 贴式元件焊盘引线宽度设置:

PCB画图笔记

原理图1 1 File-new-design workspace创建一个工作空间。

2 File-new-project-pcb project创建一个pcb项目。

3 保存工作空间到一个文件夹。

4 file-new-schematic创建原理图。

5 保存schematic和project. 2 Project-option可以进行规则设置 warming、error、no report、fatal error 3 点击 set snap grid 可以调节鼠标每移动一次走过的栅格。

4 点击design-document options可以设置原理图纸的大小等等。

5 模拟地和数字地名字要改成不一样 用0Ω电阻连接。

6 总线的设置 假如 databus[0..7] 中间 ,databus0 databus1,…,databus7(两方都有) 7 对原件标号 tools-annotate-update change list-accept change list –validate changes-execute changes 8 找器件 edit-find text 9 替换 edit-replace text 全替换和部分替换 可以根据下面的选项选择 。

10. 只要不经过管脚线 连线时有交叉不会自动放置节点。

若有节点 不想要 则把管脚外面延长一根线 再交叉就不会有节点了。

11. 芯片的推荐电路图 可以到芯片的公司去看 有样片评估。

PCB 1. tools---component wizard--- 焊盘长和宽都取最大值,长加50mil-- 焊盘与焊盘之间 宽一样 长为 总长平均值+50mil-焊盘长平均值。

2. 然后检查看对不对。

Ctrl+m进行测距 焊盘之间的中心距离和两个横向焊盘之间的边界距离。

中心距离比最大距离长 横向边界距离比原件横向距离短就行。

3. Ctrl+q 英制和米制之间的切换。

ADSPCB板图仿真学习笔记(过孔设定,差分仿真,差分眼图仿真等)

ADSPCB板图仿真学习笔记(过孔设定,差分仿真,差分眼图仿真等)ADS PCB 板图仿真学习笔记⽅法⼀:1.打开Cadence:Allegro PCB Designer 16.5,载⼊需要的PCB⽂件。

1.1File----->Change Editor,在弹出窗⼝选择Allegro PCB DesignXL(Legacy),选中Analog/RF,点击确定。

1.2Setup----->Cross-section 设置叠层厚度,介电常数等信息。

1.31.3.1RF-PCB----->IFF Interface----->Export,在弹出窗⼝选择Export Selection,然后点击PCB上需要导出仿真的线段等,点击OK.(也可以选择Export All等其它选项,根据需要选择)。

1.3.2在弹出窗⼝:RF IFF Export,选择⽂件存放的路径,然后点击layer map。

1.3.3在出现的窗⼝选择转换到ADS对应的层(我习惯4层板依次放在PC1~PC4),点击OK。

1.3.4回到RF IFF Export窗⼝,点击OK,⽣成⽂件。

在产⽣的报告中,Types of viasexported 后给出了过孔输出对应的层。

2打开ADS 20092.1新建⼀个PCB(可在Option----->Preferences 弹出窗⼝中选择layout units 设定layout 单位,也可以在layout 界⾯单机右键,选择Preferences。

另单击右键选择Grid Spaction 可设置栅格⼤⼩;选择Measure可⽤来测量长度)2.2File----->Export 在弹出的Export窗⼝中,File Type选择IFF;Destination file选择刚才⽣成的layout.IFF⽂件(备注:⽂件夹命名不能有空格等⾮法字符)。

2.3Momentum----->Substrate----->open 选择刚才⽣成的xxxx.slm⽂件,载⼊叠层设置。

PCB学习笔记

PROTEL学习1、rules布线设置后不要重新载入网络表及封装,否则新的设置会无效。

2、PCB中有个sheet1的红色填充方框-------应该放置在规划范围以内,好像也可以删除,但是不能放在规划电路图之外------Bounding Region。

3、PCB信号线、电源线、特别是地线的线宽最好是设定范围(max、min、优先设置三个值大小不同),从而尽量避免Width错误。

4、单位换算:mil---千分之一英寸:1mil=0.0254mm;100mil=2.54mm ;1000mil=25.4mm;4000mil=101.6mm=10.16cm---------一般的电路板都在1000mil以上,10000mil以下。

5、原理图网络标号:具有电气特性------具有相同网络标号的导线及元器件引脚是连在一起的----------在复杂电路图中用网络标号代替导线,方便画图并且使得电路图清晰。

6、层次电路图绘制---------实际的Stm32f103系列电路图需要使用层次电路图和网络标号。

7、扩大PCB文件绘图区域(黑色区域)的面积:Design→Board ship→redefine board shape→绘制新的绘图区即可。

8、解决封装不合适的问题:按1:1打印PCB,然后把元件实物放到图纸上比对即可。

9、方块图种错误:Duplicate Net Names Element→在总线上添加一个网络标号即可。

10、Duplicate net names bus slice N000-1:重复的网络总线名片。

Duplicate Net Names wire:重复名称线网。

原因:使用了总线,并且yk、yx和key&led三个电路复用总线,此类错误可能无须在意,因为线路连接正常。

11、总线使用方法:(1)画45度角:英文状态下,使用shift+空格键即可。

(2)总线上要有网络标号,各个线路上也要有网络标号。

Cadence学习笔记4PCB板设计

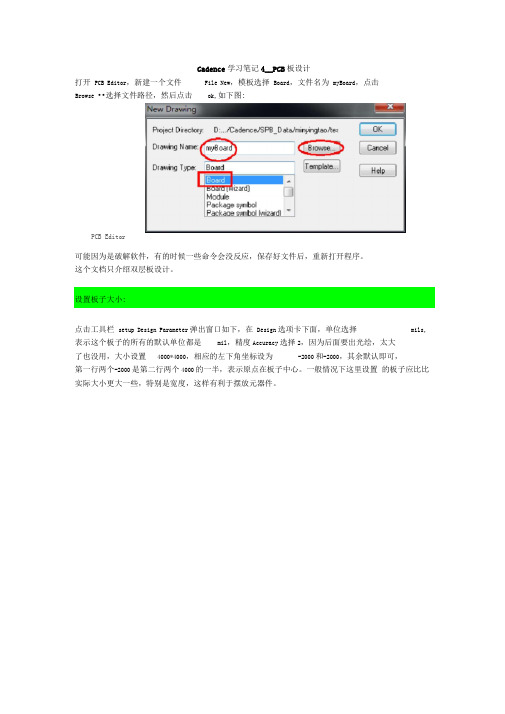

Cadence 学习笔记4__PCB 板设计打开 PCB Editor ,新建一个文件File New ,模板选择 Board ,文件名为 myBoard ,点击 PCB Editor可能因为是破解软件,有的时候一些命令会没反应,保存好文件后,重新打开程序。

这个文档只介绍双层板设计。

设置板子大小:点击工具栏 setup Design Parameter 弹出窗口如下,在 Design 选项卡下面,单位选择 mils ,表示这个板子的所有的默认单位都是 mil ,精度Accuracy 选择2,因为后面要出光绘,太大了也没用,大小设置4000*4000,相应的左下角坐标设为-2000和-2000,其余默认即可,第一行两个-2000是第二行两个4000的一半,表示原点在板子中心。

一般情况下这里设置 的板子应比比实际大小更大一些,特别是宽度,这样有利于摆放元器件。

Browse ••选择文件路径,然后点击ok ,如下图:〕D 『曲电T jQrMLMrrjiParaTiEtiTi dewiphcn pecim Ifie T sn上二号1 t-iiD_gh a pup •中 ireu tlplcns sie^v L. C. D_. aid Oll^. [he 厲店1 由匕 d-emng 阳畝 ii liw LI 丹i Uh 补■・ Miv a Indi 祸 4 v A, M 匚 or 口怙L Fir 匚山*,冯 $UVL ,「I O Utw Unit; k Milrriuivit cr 匚爭* tjmmg 传 ai 辜 A' A3..A4. or QthmrIf png 口fE *百Uh 辜或E 黄 i$ dics eti th$ 甸十才 miimatiMl 卩 h 旳目臍I he cCnV-s hr the SZE.亡r t -e C wg Exterts sectcriOK Cincd -p <接着设置栅格点大小,点击工具栏 setup Grids ,勾选“ GridsOn'显示栅格点,在非电气属性区域Non-Etch 设置为25mil ,表示布局 <摆放元件)时的最小栅格点为 25mil ,在电气属性区域All Etch 及下面的TOP 和BOTTOM 设为5mil ,表示布线时的最小栅格点为5mil ,在 All Etch 这里的 Spaceing x 和y 可以设置所有层的电气属性栅格点,在下面的TOP 和BOTTOM 可以单独设置各个层,这里默认的是两层,如果还有更多的层,都会在这里显示。

PCB设计 笔记(一)

PCB设计笔记(一)本文所述操作均是基于Altium Designer10,为本人整理,仅供学习交流之用。

一、简单原理图设计技巧1、修改原理图文档右下角的文件信息(1)重新选择原理图模板(因默认模板无法修改) Design->General Templates(2)修改文档选项Design->Document Options->Parameters或者直接右键Options->Document Options->Parameters2、原理图走任意角度线shift+space即可切换(此时一定要切换到系统默认的英文输入法状态。

3、添加规则集place->directive->Paramate Set/PCB可以设置tedingdebuxianguize4、放置当前时间place->Test->table键->输入格式=CurrentTime5、智能粘贴word中的图表edited->Smart past->复制word中的表格->复制到原理图也可从word 复制到原理图(需先设置Edit->Smart Past)6、查找,替换用法与word相同Ctrl+F、Ctrl+H7、查找相似对象右键或者快捷键Shift+F(背景被屏蔽)Shift+C 清除查找相似后的选择过滤后全选相似对象Edit->Select->all,选中后在修改其参数,即可修改全部相似对象参数8、封装管理器修改封装Tool->Footprint Manager9、由原理图生成原理图库Deign->Make Schematic Library10、创建联合体选中要联合的部分->youjian ->Unions11、取消联合体右键->Unions->Break12、讲几个元件作为设计整体(以备以后您使用)选中->右键->Snippets,使用时System->Snippets13、生成报表Reports->Bill of Mertarils->Export(导出)用模板格式导出Reports->Bill of Mertarils->Templates->选择安装目录下的Templates中的模板->Export(导出)14、查找相似实现批量更改属性(zhuyi:更改前一定要先选中!)右键->find similar objects(选中复选框Select Matching)->右下角SCH->SCH Inspector->更改属性即可15、查看当前文件中元件的封装封装管理库tools->Parameter Management。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

尽量采用地平面作为电流回路;将模拟地平面和数字地平面分开;如果地平面被信号走线隔断,为降低对地电流回路的干扰,应使信号走线与地平面垂直;模拟电路尽量靠近电路板边缘放置,数字电路尽量靠近电源连接端放置,这样做可以降低由数字开关引起的di/dt (电流随时间的变化)效应。

将地平面布在电路板顶层,以降低电磁干扰。

同一网络的两根线交叉时,不要交叉成直角或锐角。

当一线与直线交叉时切忌不要走锐角,可以走直角。

旁路电容到IC的走线宽度>25mil,并尽量避免使用过孔,模拟信号宽(12-15mil)其它走

线>5mil(10mil)元器件间连线尽量短。

清除地线环路。

PCB上的接地连接如要考虑走线时,设计应将走线尽量加粗。

DC-DC电源屏蔽

在供电电源处或有源器件的电源引脚处施加旁路(或去耦)电容是较好的做法。

电源线和地线要布在一起

电源线和地线的位置良好配合,可以降低电磁干扰的可能性。

如果电源线和地线配合不当,会设计出系统环路,并很可能会产生噪声。

对于模拟电路,还有另外一点需要注意,就是要将数字信号线和地平面中的回路尽量远离模拟电路。

这一点可以通过如下做法来实现:将模拟地平面单独连接到系统地连接端,或者将模拟电路放置在电路板的最远端,也就是线路的末端。

意:为降低电源线的感抗,电源线要比信号线宽很多。

旁路电容

可在电路板上的如下两个位置放置旁路电容:一个电容(10mF至100mF)放置在电源侧,另一个电容放置在每个有源器件(包括数字和模拟器件)旁边。

加在器件上旁路电容的值取决于使用的器件。

如果器件的带宽小于或等于1MHz,那么采用1mF的电容可以显著降低引入的噪声。

如果器件的带宽大于10MHz,0.1mF的电容可能比较合适。

如果带宽在这两个频率之间,可同时使用这两种容值的电容,或使用其一。

电路板上的每个有源器件都需要一个旁路电容。

旁路电容必须尽可能靠近器件的电源引脚放置,

对于同一个电路来说,旁路(bypass)电容是把输入信号中的高频噪声作为滤除对象,把前级携带的高频杂波滤除,而去耦(decoupling,也称退耦)电容是把输出信号的干扰作为滤除对象。