2019年计算机组成原理期末考试题共8页文档

(完整版)计算机组成原理期末考试试题及答案

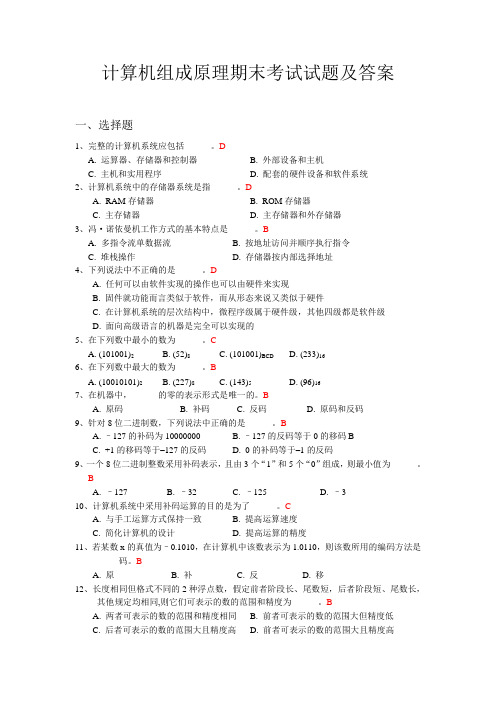

计算机组成原理期末考试试题及答案一、选择题1、完整的计算机系统应包括______。

DA. 运算器、存储器和控制器B. 外部设备和主机C. 主机和实用程序D. 配套的硬件设备和软件系统2、计算机系统中的存储器系统是指______。

DA.RAM存储器B.ROM存储器C. 主存储器D. 主存储器和外存储器3、冯·诺依曼机工作方式的基本特点是______。

BA. 多指令流单数据流B. 按地址访问并顺序执行指令C. 堆栈操作D. 存储器按内部选择地址4、下列说法中不正确的是______。

DA. 任何可以由软件实现的操作也可以由硬件来实现B. 固件就功能而言类似于软件,而从形态来说又类似于硬件C. 在计算机系统的层次结构中,微程序级属于硬件级,其他四级都是软件级D. 面向高级语言的机器是完全可以实现的5、在下列数中最小的数为______。

CA. (101001)2B. (52)8C. (101001)BCDD. (233)166、在下列数中最大的数为______。

BA. (10010101)2B. (227)8C. (143)5D. (96)167、在机器中,______的零的表示形式是唯一的。

BA. 原码B. 补码C. 反码D. 原码和反码9、针对8位二进制数,下列说法中正确的是______。

BA.–127的补码为10000000B.–127的反码等于0的移码BC.+1的移码等于–127的反码D.0的补码等于–1的反码9、一个8位二进制整数采用补码表示,且由3个“1”和5个“0”组成,则最小值为______。

BA. –127B. –32C. –125D. –310、计算机系统中采用补码运算的目的是为了______。

CA. 与手工运算方式保持一致B. 提高运算速度C. 简化计算机的设计D. 提高运算的精度11、若某数x的真值为–0.1010,在计算机中该数表示为1.0110,则该数所用的编码方法是______码。

(完整word版)计算机组成原理期末考试试题及答案

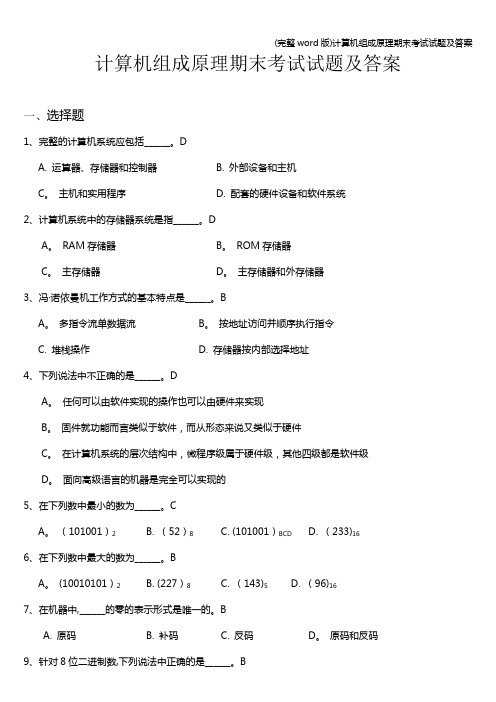

计算机组成原理期末考试试题及答案一、选择题1、完整的计算机系统应包括______。

DA. 运算器、存储器和控制器B. 外部设备和主机C。

主机和实用程序 D. 配套的硬件设备和软件系统2、计算机系统中的存储器系统是指______。

DA。

RAM存储器B。

ROM存储器C。

主存储器D。

主存储器和外存储器3、冯·诺依曼机工作方式的基本特点是______。

BA。

多指令流单数据流B。

按地址访问并顺序执行指令C. 堆栈操作D. 存储器按内部选择地址4、下列说法中不正确的是______。

DA。

任何可以由软件实现的操作也可以由硬件来实现B。

固件就功能而言类似于软件,而从形态来说又类似于硬件C。

在计算机系统的层次结构中,微程序级属于硬件级,其他四级都是软件级D。

面向高级语言的机器是完全可以实现的5、在下列数中最小的数为______。

CA。

(101001)2 B. (52)8 C. (101001)BCD D. (233)166、在下列数中最大的数为______。

BA。

(10010101)2 B. (227)8 C. (143)5 D. (96)167、在机器中,______的零的表示形式是唯一的。

BA. 原码B. 补码C. 反码D。

原码和反码9、针对8位二进制数,下列说法中正确的是______。

BA.–127的补码为10000000B.–127的反码等于0的移码BC. +1的移码等于–127的反码D。

0的补码等于–1的反码9、一个8位二进制整数采用补码表示,且由3个“1”和5个“0”组成,则最小值为______.BA. –127 B。

–32 C. –125 D。

–310、计算机系统中采用补码运算的目的是为了______.CA. 与手工运算方式保持一致B. 提高运算速度C. 简化计算机的设计D. 提高运算的精度11、若某数x的真值为–0。

1010,在计算机中该数表示为1.0110,则该数所用的编码方法是______码。

2019年电大《计算机组成原理》期末考试试题及答案

答: Cl)CPU 内部的通用寄存器。此时应在指令字中给出用到的寄存器编号(寄存器名),

通用寄存器的数量一般为几个、十几个,故在指令字中须为其分配 2 、 3 、上 5 或更多一点的位数

来表示一个寄存器。

(2) 外围设备(接口)中的一个寄存器?通常用设备编号、或设备入出喘口地址、或设备映

像地址(与内存储器地址统一编址的一个设备地址编号)来表示。

c. 符号位都是 0, 符号位都是 1

B. 符号位不同,符号位相同 D. 符号位都是 1, 符号位都是 0

3. 在定点二进制运算器中,加法运算一般通过(

)来实现。

A. 原码运算的二进制加法器

c. 补码运算的十进制加法器

B. 反码运算的二进制加法器 D. 补码运算的二进制加法器

4. 定点运算器用来进行(

D. 虚存技术

12. 在采用 DMA 方式高速传输数据时,数据传送是(

)。

A. 在总线控制器发出的控制信号控制下完成的

B. 在 DMA 控制器本身发出的控制信号控制下完成的

C. 由 CPU 执行的程序完成的

D. 由 CPU 响应硬中断处理完成的

三

二、判断题(将判断结果填在括弧内,正确打 J 号,错误打 X 号。每小 题 3 分,共 15 分)

13. 定点数的表示范围有限,如果运算结果超出表示范围,称为溢出。(

)

14. 基地址寻址方式中,操作数的有效地址等于基址寄存器内容加上形式地址。(

)

15. 计算机中的流水线是把若干个子过程合成为一个过程,使每个子过程实现串行运行。

16. 引入虚拟存储系统的目的,是为了加快外存的存取速度。(

)

17. 按数据传送方式的不同,计算机的外部接口可分为串行接口和并行接口两大类。(

计算机组成原理期末考试试卷及答案

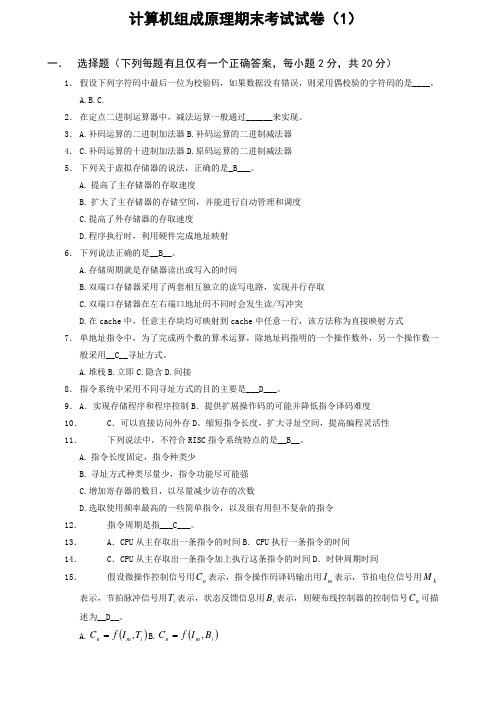

计算机组成原理期末考试试卷(1)一.选择题(下列每题有且仅有一个正确答案,每小题2分,共20分)1.假设下列字符码中最后一位为校验码,如果数据没有错误,则采用偶校验的字符码的是____。

A. B. C. D。

2.在定点二进制运算器中,减法运算一般通过______ 来实现。

3. A.补码运算的二进制加法器 B. 补码运算的二进制减法器4.C. 补码运算的十进制加法器 D. 原码运算的二进制减法器5.下列关于虚拟存储器的说法,正确的是_B___。

A.提高了主存储器的存取速度B.扩大了主存储器的存储空间,并能进行自动管理和调度C. 提高了外存储器的存取速度D. 程序执行时,利用硬件完成地址映射6.下列说法正确的是__B__。

A. 存储周期就是存储器读出或写入的时间B. 双端口存储器采用了两套相互独立的读写电路,实现并行存取C. 双端口存储器在左右端口地址码不同时会发生读/写冲突D. 在cache中,任意主存块均可映射到cache中任意一行,该方法称为直接映射方式7.单地址指令中,为了完成两个数的算术运算,除地址码指明的一个操作数外,另一个操作数一般采用__C__寻址方式。

A. 堆栈B. 立即C.隐含D. 间接8.指令系统中采用不同寻址方式的目的主要是___D___ 。

9.A.实现存储程序和程序控制 B.提供扩展操作码的可能并降低指令译码难度10.C.可以直接访问外存 D。

缩短指令长度,扩大寻址空间,提高编程灵活性11.下列说法中,不符合RISC指令系统特点的是__B__。

A.指令长度固定,指令种类少B.寻址方式种类尽量少,指令功能尽可能强C. 增加寄存器的数目,以尽量减少访存的次数D. 选取使用频率最高的一些简单指令,以及很有用但不复杂的指令 12. 指令周期是指___C___。

13. A .CPU 从主存取出一条指令的时间 B .CPU 执行一条指令的时间 14. C .CPU 从主存取出一条指令加上执行这条指令的时间 D .时钟周期时间 15.假设微操作控制信号用n C 表示,指令操作码译码输出用m I 表示,节拍电位信号用k M 表示,节拍脉冲信号用i T 表示,状态反馈信息用i B 表示,则硬布线控制器的控制信号n C 可描述为__D__。

(完整word版)计算机组成原理期末考试习题及答案

《计算机组成原理》练习题一、单项选择题1.CPU响应中断的时间是__C____。

A.中断源提出请求;B.取指周期结束;C.执行周期结束;D.间址周期结束。

2.下列说法中___C___是正确的。

A.加法指令的执行周期一定要访存;B.加法指令的执行周期一定不访存;C.指令的地址码给出存储器地址的加法指令,在执行周期一定访存;D.指令的地址码给出存储器地址的加法指令,在执行周期不一定访存。

3.垂直型微指令的特点是__C____。

A.微指令格式垂直表示;B.控制信号经过编码产生;C.采用微操作码;D.采用微指令码。

4.基址寻址方式中,操作数的有效地址是___A___。

A.基址寄存器内容加上形式地址(位移量);B.程序计数器内容加上形式地址;C.变址寄存器内容加上形式地址;D.寄存器内容加上形式地址。

5.常用的虚拟存储器寻址系统由___A___两级存储器组成。

A.主存-辅存;B.Cache-主存;C.Cache-辅存;D.主存—硬盘。

6.DMA访问主存时,让CPU处于等待状态,等DMA的一批数据访问结束后,CPU再恢复工作,这种情况称作___A___。

A.停止CPU访问主存;B.周期挪用;C.DMA与CPU交替访问;D.DMA。

7.在运算器中不包含____D__。

A.状态寄存器;B.数据总线;C.ALU;D.地址寄存器。

8.计算机操作的最小单位时间是__A____。

A.时钟周期;B.指令周期;C.CPU周期;D.中断周期。

9.用以指定待执行指令所在地址的是__C____。

A.指令寄存器;B.数据计数器;C.程序计数器;D.累加器。

10.下列描述中___B___是正确的。

A.控制器能理解、解释并执行所有的指令及存储结果;B.一台计算机包括输入、输出、控制、存储及算逻运算五个单元;C.所有的数据运算都在CPU的控制器中完成;D.以上答案都正确。

11.总线通信中的同步控制是___B___。

A.只适合于CPU控制的方式;B.由统一时序控制的方式;C.只适合于外围设备控制的方式;D.只适合于主存。

计算机组成原理期末考试试卷及答案

计算机组成原理期末考试试卷(1)一. 选择题(下列每题有且仅有一个正确答案,每小题2分,共20分)1. 假设下列字符码中最后一位为校验码,如果数据没有错误,则采用偶校验的字符码的是____。

A.B.C.2. 在定点二进制运算器中,减法运算一般通过______来实现。

3. A.补码运算的二进制加法器B.补码运算的二进制减法器 4. C.补码运算的十进制加法器D.原码运算的二进制减法器 5. 下列关于虚拟存储器的说法,正确的是_B___。

A. 提高了主存储器的存取速度B. 扩大了主存储器的存储空间,并能进行自动管理和调度C.提高了外存储器的存取速度D.程序执行时,利用硬件完成地址映射 6. 下列说法正确的是__B__。

A.存储周期就是存储器读出或写入的时间B.双端口存储器采用了两套相互独立的读写电路,实现并行存取C.双端口存储器在左右端口地址码不同时会发生读/写冲突D.在cache 中,任意主存块均可映射到cache 中任意一行,该方法称为直接映射方式 7. 单地址指令中,为了完成两个数的算术运算,除地址码指明的一个操作数外,另一个操作数一般采用__C__寻址方式。

A.堆栈B.立即C.隐含D.间接8. 指令系统中采用不同寻址方式的目的主要是___D___。

9. A .实现存储程序和程序控制B .提供扩展操作码的可能并降低指令译码难度 10. C .可以直接访问外存D 。

缩短指令长度,扩大寻址空间,提高编程灵活性 11.下列说法中,不符合RISC 指令系统特点的是__B__。

A. 指令长度固定,指令种类少B. 寻址方式种类尽量少,指令功能尽可能强C.增加寄存器的数目,以尽量减少访存的次数D.选取使用频率最高的一些简单指令,以及很有用但不复杂的指令 12. 指令周期是指___C___。

13. A .CPU 从主存取出一条指令的时间B .CPU 执行一条指令的时间 14. C .CPU 从主存取出一条指令加上执行这条指令的时间D .时钟周期时间15.假设微操作控制信号用n C 表示,指令操作码译码输出用m I 表示,节拍电位信号用kM 表示,节拍脉冲信号用i T 表示,状态反馈信息用i B 表示,则硬布线控制器的控制信号n C 可描述为__D__。

计算机组成原理期末考试试卷及答案

计算机组成原理期末考试试卷(1)一.选择题(下列每题有且仅有一个正确答案,每小题2分,共20分)1.假设下列字符码中最后一位为校验码,如果数据没有错误,则采用偶校验的字符码的是____。

A. 11001011 B。

11010110 C。

11000001 D。

110010012.在定点二进制运算器中,减法运算一般通过______ 来实现。

A。

补码运算的二进制加法器 B。

补码运算的二进制减法器C。

补码运算的十进制加法器 D. 原码运算的二进制减法器3.下列关于虚拟存储器的说法,正确的是_B___。

A.提高了主存储器的存取速度B.扩大了主存储器的存储空间,并能进行自动管理和调度C。

提高了外存储器的存取速度D。

程序执行时,利用硬件完成地址映射4.下列说法正确的是__B__。

A。

存储周期就是存储器读出或写入的时间B. 双端口存储器采用了两套相互独立的读写电路,实现并行存取C. 双端口存储器在左右端口地址码不同时会发生读/写冲突D。

在cache中,任意主存块均可映射到cache中任意一行,该方法称为直接映射方式5.单地址指令中,为了完成两个数的算术运算,除地址码指明的一个操作数外,另一个操作数一般采用__C__寻址方式。

A。

堆栈 B。

立即 C。

隐含 D. 间接6.指令系统中采用不同寻址方式的目的主要是___D___ 。

A.实现存储程序和程序控制B.提供扩展操作码的可能并降低指令译码难度C.可以直接访问外存 D。

缩短指令长度,扩大寻址空间,提高编程灵活性7.下列说法中,不符合RISC指令系统特点的是__B__。

A.指令长度固定,指令种类少B.寻址方式种类尽量少,指令功能尽可能强C. 增加寄存器的数目,以尽量减少访存的次数D。

选取使用频率最高的一些简单指令,以及很有用但不复杂的指令8. 指令周期是指___C___。

A .CPU 从主存取出一条指令的时间 B .CPU 执行一条指令的时间 C .CPU 从主存取出一条指令加上执行这条指令的时间 D .时钟周期时间 9. 假设微操作控制信号用n C 表示,指令操作码译码输出用m I 表示,节拍电位信号用k M 表示,节拍脉冲信号用i T 表示,状态反馈信息用i B 表示,则硬布线控制器的控制信号n C 可描述为__D__。

计算机组成原理期末考试试题(含答案)

计算组成原理期末考试1、图中所示的寻址方式是() (单选)A、基址寻址B、寄存器寻址C、间接寻址D、寄存器间接寻址2、设存储字长为64位,对于单字长指令而言,PC顺序寻址时应该增加的常量是( )(单选)A、1B、2C、4D、83、在小数定点机中,下列关于原码、反码、补码的描述中正确的是A、只有补码能表示-1B、只有反码能表示-1C、只有原码能表示-1D、三种机器数都能表示-14、移位运算对计算机来说的实用价值是A、可以采用移位和加法相结合,实现乘(除)运算B、采用移位运算可以防止数据溢出C、只采用移位运算就可以实现除法D、只采用移位运算就可以实现乘法5、float型数据通常用IEEE754单精度浮点数格式表示。

若编译器将float型变量x分配在一个32位浮点寄存器FR1中,且x= -8.25,则FR1的内容是()A、C104 0000HB、C184 0000HC、C1C2 0000H`D、C242 0000H6、用海明码对长度为8位的数据进行检纠错时,若只要求纠正一位错,则检验位数至少需要()位。

A、5位B、4位C、3位D、2位7、存储器中地址号分别为1000#、1001#、1002#、1003的4个存储单元,分别保存的字节数据是1A、2B、3C、4D,如果数据字长为32位,存储器采用的是小端对齐模式,则这4个存储单元存储的数据值应被解析为()A、4D3C2B1AB、1A2B2C3DC、2B1A4D3CD、3C4D1A2B8、某型MIPS32指令架构的单周期CPU,其数据通路结构如下图执行指令sub rd, rs, rt 时,应由控制器产生的控制信号PCSrc、regDst、aluSrc、memtoReg、RegWrite分别是( )A、1、0、1、0、1B、1、1、0、0、0C、0、1、0、0、1D、0、1、0、1、09、下列关于MIPS32指令系统中,与基址寻址相关的指令是()A、addi $rt, $rs, immB、lw $rt, $rs, immC、add $rd, $rs, $rtD、add $rd, $rs, $rt10、单周期MIPS在一个时钟周期中不能完成( )A、从数据存储器读数据和向数据存储器写数据B、ALU运算和向寄存器堆写数据C、更新PC内容和向数据存储器写数据D、寄存器堆读数据,ALU运算和数据存储器写数据11、下列按内容寻址,而不是按地址码寻址的存储器是( )A、双端口存储器B、相联存储器C、并行储器D、虚拟存储器12、某半导体14KB,按字节编址,其中0000H-1FFFH为ROM区,2000H-37FFH为RAM区,地址总线A15-A0(低),双向数据总线D7-D0(低),读写控制线R/W。

(完整word版)计算机组成原理期末试题及答案

第一章计算机系统概论计算机的硬件是由有形的电子器件等构成的,它包括运算器、存储器、控制器、适配器、输入输出设备。

早起将运算器和控制器合在一起称为CPU(中央处理器)。

目前的CPU包含了存储器,因此称为中央处理器。

存储程序并按地址顺序执行,这是冯·诺依曼型计算机的工作原理,也是CPU自动工作的关键。

计算机系统是一个有硬件、软件组成的多级层次结构,它通常由微程序级、一般程序级、操作系统级、汇编语言级、高级语言级组成,每一级上都能进行程序设计,且得到下面各级的支持。

习题:4冯·诺依曼型计算机的主要设计思想是什么?它包括那些主要组成部分?主要设计思想是:存储程序通用电子计算机方案,主要组成部分有:运算器、逻辑控制装置、存储器、输入和输出设备5什么是存储容量?什么是单元地址?什么是数据字?什么是指令字?存储器所有存储单元的总数称为存储器的存储容量。

每个存储单元都有编号,称为单元地址。

如果某字代表要处理的数据,称为数据字。

如果某字为一条指令,称为指令字7指令和数据均存放在内存中,计算机如何区分它们是指令还是数据?每一个基本操作称为一条指令,而解算某一问题的一串指令序列,称为程序第二章运算方法和运算器按对阶操作。

直接使用西文标准键盘输入汉字,进行处理,并显示打印汉字,是一项重大成就。

为此要解决汉字的输入编码、汉字内码、子模码等三种不同用途的编码。

1第三章 内部存储器CPU 能直接访问内存(cache 、主存)双端口存储器和多模块交叉存储器属于并行存储器结构。

cache 是一种高速缓冲存储器,是为了解决CPU 和主存之间速度不匹配而采用的一项重要的硬件技术,并且发展为多级cache 体系,指令cache 与数据cache 分设体系。

要求cache 的命中率接近于1适度地兼顾了二者的优点又尽量避免其缺点,从灵活性、命中率、硬件投资来说较为理想,因而得到了普遍采用。

习题: 1设有一个具有20位地址和32位字长的存储器,问:(1)该存储器能存储多少个字节的信息?(2)如果存储器由512K ×8位SRAM 芯片组成,需要多少片;(3)需要多少位地址做芯片选择?(1)字节M 4832*220= (2)片84*28*51232*1024==K K (3)1位地址作芯片选择 2 已知某64位机主存采用半导体存储器,其地址码为26位,若使用4M ×8位DRAM 芯片组成该机所允许的最大主存空间,并选用内存条结构形式,问:(1) 若每个内存条16M ×64位,共需几个内存条?(2)每个内存条共有多少DRAM 芯片? (3)主存共需多少DRAM 芯片?CPU 如何选择各内存条?(1). 共需模块板数为m :m=÷2^24=4(块)(2). 每个模块板内有DRAM 芯片数为32 (片)(3) 主存共需DRAM 芯片为:4*32=128 (片)每个模块板有32片DRAM 芯片,容量为16M ×64位,需24根地址线(A23~A0) 完成模块板内存储单元寻址。

计算机组成原理期末考试试题及答案,DOC

计算机组成原理期末考试试题及答案一、选择题1、完整的计算机系统应包括______。

DA.运算器、存储器和控制器B.外部设备和主机C.主机和实用程序D.配套的硬件设备和软件系统2、计算机系统中的存储器系统是指______。

DA.RAM存储器B.ROM存储器C.主存储器D.主存储器和外存储器3、冯·诺依曼机工作方式的基本特点是______。

BA.多指令流单数据流B.按地址访问并顺序执行指令C.堆栈操作D.存储器按内部选择地址4、下列说法中不正确的是______。

DA.任何可以由软件实现的操作也可以由硬件来实现B.固件就功能而言类似于软件,而从形态来说又类似于硬件C.在计算机系统的层次结构中,微程序级属于硬件级,其他四级都是软件级D.面向高级语言的机器是完全可以实现的5、在下列数中最小的数为______。

CA.(101001)2B.(52)8C.(101001)BCDD.(233)166、在下列数中最大的数为______。

BA.()2B.(227)8C.(143)5D.(96)167、在机器中,______的零的表示形式是唯一的。

BA.原码B.补码C.反码D.原码和反码9、针对8位二进制数,下列说法中正确的是______。

BA.–127的补码为B.–127的反码等于0的移码BC.+1的移码等于–127的反码D.0的补码等于–1的反码9、一个8位二进制整数采用补码表示,且由3个“1”和5个“0”组成,则最小值为______。

BA.–127B.–32C.–125D.–310、计算机系统中采用补码运算的目的是为了______。

CA.与手工运算方式保持一致B.提高运算速度C.简化计算机的设计D.提高运算的精度11、若某数x的真值为–0.1010,在计算机中该数表示为1.0110,则该数所用的编码方法是______码。

BA.原B.补C.反D.移12、长度相同但格式不同的2种浮点数,假定前者阶段长、尾数短,后者阶段短、尾数长,其他规定均相同,则它们可表示的数的范围和精度为______。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一、填空题:

1.若浮点数用补码表示,则判断运算结果是否为规格化数的方法是______。

A 阶符与数符相同为规格化数

B 阶符与数符相异为规格化数

C 数符与尾数小数点后第一位数字相异为规格化数

D数符与尾数小数点后第一位数字相同为规格化数

2.定点16位字长的字,采用2的补码形式表示时,一个字所能表示的整数范围是______。

A -215 ~ +(215 -1)

B -(215 –1)~ +(215 –1)

C -(215 +1)~ +215

D -215 ~ +215

3.某SRAM芯片,存储容量为64K×16位,该芯片的地址线和数据线数目为______。

A 64,16

B 16,64

C 64,8

D 16,16 。

4.交叉存贮器实质上是一种______存贮器,它能_____执行______独立的读写操作。

A 模块式,并行,多个

B 模块式,串行,多个

C 整体式,并行,一个

D 整体式,串行,多个5.冯·诺依曼机工作的基本方式的特点是______。

A 多指令流单数据流

B 按地址访问并顺序执行指令

C 堆栈操作

D 存贮器按内容选择地址

6.在机器数______中,零的表示形式是唯一的。

A 原码

B 补码

C 移码

D 反码

7.在定点二进制运算器中,减法运算一般通过______来实现。

A 原码运算的二进制减法器

B 补码运算的二进制减法器

C 原码运算的十进制加法器

D 补码运算的二进制加法器

8.某计算机字长32位,其存储容量为4MB,若按半字编址,它的寻址范围是______。

A 4M

B B 2MB

C 2M

D 1M

9.主存贮器和CPU之间增加cache的目的是______。

A 解决CPU和主存之间的速度匹配问题

B 扩大主存贮器容量

C 扩大CPU中通用寄存器的数量

D 既扩大主存贮器容量,又扩大CPU中通用寄存器的数量

10.下面浮点运算器的描述中正确的句子是:______。

A. 浮点运算器可用阶码部件和尾数部件实现

B. 阶码部件可实现加、减、乘、除四种运算

C. 阶码部件只进行阶码相加、相减和比较操作

D. 尾数部件只进行乘法和减法运算

11.某计算机字长16位,它的存贮容量是64KB,若按字编址,那么它的

寻址范围是______

A. 64K

B. 32K

C. 64KB

D. 32 KB

12. 双端口存储器在______情况下会发生读/写冲突。

A. 左端口与右端口的地址码不同

B. 左端口与右端口的地址码相同

C. 左端口与右端口的数据码不同

D. 左端口与右端口的数据码相同

13.假定下列字符码中有奇偶校验位,但没有数据错误,采用偶校验的字符码是______。

A 11001011

B 11010110

C 11000001

D 11001001

14.完整的计算机应包括______。

A 运算器、存储器、控制器;

B 外部设备和主机;

C 主机和实用程序;

D 配套的硬件设备和软件系统;

15.某一RAM芯片,其容量为512×8位,包括电源和接地端,该芯片引出线的最小数目应是______。

A 23

B 25

C 50

D 19

16.至今为止,计算机中的所有信息仍以二进制方式表示的理由是______。

A.节约元件; B 运算速度快; C 物理器件的性能决定; D 信息处理方便;

17.已知X为整数,且[X]

= 10011011,则X的十进制数值是______。

补

A +155

B –101

C –155

D +101

18.主存储器是计算机系统的记忆设备,它主要用来______。

A 存放数据

B 存放程序

C 存放数据和程序

D 存放微程序19.在定点运算器中,无论采用双符号位还是单符号位,必须有______,它一般用______来实现。

A 译码电路,与非门;

B 编码电路,或非门;

C 溢出判断电路,异或门;

D 移位电路,与或非门;

20、采用虚拟存贮器的主要目的是______。

A 提高主存贮器的存取速度;

B 扩大主存贮器的存贮空间,并能进行自动管理和调度;

C 提高外存贮器的存取速度;

D 扩大外存贮器的存贮空间;

21.定点计算机用来进行_______。

A 十进制数加法运算;

B 定点数运算;

C 浮点数运算;

D 既进行定点数运算也进行浮点数运算;

22.双端口存储器所以能高速进行读 / 写,是因为采用______。

A 高速芯片

B 两套相互独立的读写电路

C 流水技术

D 新型

器件

23.冯·诺伊曼机工作方式的基本特点是______。

A.多指令流单数据流;

B.按地址访问并顺序执行指令;

C.堆栈操作;

D.存储器按内容选择地址。

24.程序控制类指令的功能是______。

A.进行主存和CPU之间的数据传送;

B.进行CPU和设备之间的数据传送;

C.改变程序执行的顺序;

D.一定是自动加+1。

25.直接、间接、立即三种寻址方式指令的执行速度,由快至慢的排序是______。

A.直接、立即、间接;

B.直接、间接、立即;

C.立即、直接、间接;

D.立即、间接、直接。

26.采用变址寻址可扩大寻址范围,且______。

A.变址寄存器内容由用户确定,在程序执行过程中不可变;

B.变址寄存器内容由操作系统确定,在程序执行过程中可变;

C.变址寄存器内容由用户确定,在程序执行过程中可变;

D.变址寄存器内容由操作系统确定,在程序执行过程中不可变;27.在一地址格式的指令中,下列是正确的。

A.仅有一个操作数,其地址由指令的地址码提供;

B.可能有一个操作数,也可能有两个操作数;

C.一定有两个操作数,另一个是隐含的。

28.寻址便于处理数组问题。

A.间接寻址;

B.变址寻址;

C.相对寻址。

29.直接寻址的无条件转移指令功能是将指令中的地址码送入______。

A.PC;

B.地址寄存器;

C.累加器;

D.ALU。

30.寻址对于实现程序浮动提供了较好的支持。

A.间接寻址;

B.变址寻址;

C.相对寻址;

D.直接寻址。

二、填空题:(每空2分,共22分)

1.数的真值变成机器码可采用______表示法, ______表示法,______表示法,移码表示法。

2.对存储器的要求是______, ______, ______。

为了解决这三方面的矛盾,计算机采用多级存储体系结构。

3.按IEEE754标准,一个浮点数由______,,三部分组成。

其中阶码E的值等于指数的______加上一个固定______。

三.计算题:

(1) x = - 0.01111 ,y = +0.11001,求 [ x ]

补,[ -x ]

补

,[ y ]

补,[ -y ]

补

,x + y = ?,x – y = ?

(2)设存储器容量为64M,字长为64位,模块数m=4,分别用顺序和交叉方式进行组织。

存储周期T=100ns,数据总线宽度为64位,总

线传送周期s=50ns,若连续读出8个字,问顺序和交叉存储器的带

宽各是多少?

(3)已知某8位机的主存采用半导体存贮器,地址码为18位,若使用4K ×4位RAM芯片组成该机所允许的最大主存空间,并选用模块条的形式,问:

(1)若每个模条为32K×8位,共需几个模块条?

(2)每个模块内共有多少片RAM芯片?

(3)主存共需多少RAM芯片?CPU如何选择各模块条?

四、简答题

一条双字长的取数指令(LDA)存于存储器的100和101单元,其中第一个字为操作码和寻址特征M,第二个字为形式地址。

假设PC当前值为100,变址寄存器XR的内容为100,基址寄存器的内容为200,存储器各单元的内容如下图所示。

写出在下列寻址方式中,取数指令执行结束后,累加器AC的内容。

希望以上资料对你有所帮助,附励志名言3条:

1、理想的路总是为有信心的人预备着。

2、最可怕的敌人,就是没有坚强的信念。

——罗曼·罗兰

3、人生就像爬坡,要一步一步来。

——丁玲。