东南大学soc课件12 低功耗设计(3学时)

SOC的低功耗设计

SOC的低功耗设计低功耗设计在当前电子设备发展的大背景下,变得越来越重要。

对于拥有电池限制的移动设备,如智能手机、平板电脑和笔记本电脑,延长电池寿命是用户和制造商的共同需求。

此外,对于一些无线传感器、IoT设备和可穿戴设备,低功耗设计可以实现长时间的无线连接和持久的运行。

SOC(System on Chip)是一种集成了处理器核心、内存、输入/输出接口和其他相关的电子元件的微电子芯片。

在SOC的低功耗设计中,主要考虑以下几个方面:首先是处理器核心的设计。

低功耗的处理器核心通常采用精简指令集(RISC)架构,因为RISC架构相比复杂指令集(CISC)架构具有更高的能效。

此外,延迟插槽、流水线优化和缓存优化等技术也可以降低处理器核心的功耗。

其次是内存的设计。

内存代表着SOC中存储和访问数据的组件。

低功耗设计中,采用低功耗的内存类型,如低功耗SDRAM(LPDDR),可以大大降低功耗。

此外,考虑到内存访问的局部性原理,优化数据结构和算法,减少内存访问次数也是提高能效的关键。

再次是输入/输出接口的设计。

在SOC中,输入/输出接口通常涉及与外部设备的通信和数据传输。

使用低功耗的通信协议,如低功耗蓝牙(Bluetooth Low Energy,BLE)和Zigbee,可以减少功耗。

此外,采用可变频率电压调节器(DVFS)和功耗管理单元(PMU)等技术,根据实际需求动态调整输入/输出接口的功耗,也可以提高整体的能效。

最后是系统级的设计。

系统级的设计考虑了整个SOC中各个组件之间的协调和优化。

例如,通过合理的功耗分配和任务调度,平衡各个组件的工作负载,可以避免单个组件过度消耗能量。

此外,采用低功耗时钟源、电源管理和睡眠模式等策略,使得SOC在非活动状态下能够进入低功耗模式,从而延长电池的使用寿命。

综上所述,SOC的低功耗设计需要从处理器核心、内存、输入/输出接口和系统级等多个方面进行优化。

通过采用低功耗的技术和策略,可以降低功耗,延长电池寿命,从而提高电子设备的能效和用户体验。

SoC系统的低功耗设计

SoC系统的低功耗设计摘要:功耗问题正日益变成VLSI系统实现的一个限制因素。

对便携式应用来说,其主要原因在于电池寿命,对固定应用则在于最高工作温度。

由于电子系统设计的复杂度在日益提高,导致系统的功耗得到其主要功耗成分。

其次,以该主要功耗成分数学表达式为依据,突出实现SoC低功耗设计的各种级别层次的不同方法。

关键词:VLSI SoC CMOS集成电路低功耗设计引言从20世纪80年代初到90年代初的10年里,微电子领域的很多研究工作都集中到了数字系统速度的提高上,现如今的技术拥有的计算能力能够使强大的个人工作站、复杂实时语音和图像识别的多媒体计算机的实现成为可能。

高速的计算能力对于百姓大众来说是触指可及的,不像早些年代那样只为少数人服务。

另外,用户希望在任何地方都能访问到这种计算能力,而不是被一个有线的物理网络所束缚。

便携能力对产品的尺寸、重量和功耗加上严格的要求。

由于传统的镍铬电池每磅仅能提供的能量,因而功耗就变得尤为重要。

电池技术正在改进,每5年最大能将电池的性能提高30%,然而其不可能在短期内显着地解决现在正遇到的功耗问题。

虽然传统可便携数字应用的支柱技术已经成功地用于低功耗、低性能的产品上,诸如电子手表、袖珍计算器等等,但是有很多低功耗、高性能可便携的应用一直在增长。

例如,笔记本计算机就代表了计算机工业里增长最快的部分。

它们要求与桌上计算机一样具有同样的计算能力。

同样的要求在个人通信领域也正在迅速地发展,如采用了复杂语音编解码算法和无线电调制解调器的带袖珍通信终端的新一代数字蜂窝网。

已提出的未来个人通信服务PCS应用对这些要求尤其明显,通用可便携多媒体服务是要支持完整的数字语音和图像辨别处理的。

在这些应用中,不仅语音,而且数据也要能在无线链路上传输。

这就为实现任何人在任何地方的任何时间开展任何想要的业务提供了可能。

但是,花在对语音、图像的压缩和解压上的功耗就必须附加在这些可便携的终端上。

确实,可便携能力已经不再明显地和低性能联系在一起了;相反,高性能且可便携的应用正在逐步得到实现。

精选东南大学电子信息工程之微机学第1章12学时资料

教学参考书:

郁慧娣,微机系统及其接口技术, 东南大学出版社

吴宁,80X86/Pentium微型计算机原理及应用, 电子工业出版社;

戴梅萼,微型计算机技术及应用, 清华大学出版社

张怀莲,IBM-PC宏汇编语言程序设计, 电子工业出版社

8

第1章 微机系统概述

教学重点

微处理器的发展简史 微型计算机的系统组成 IBM PC系列机的主机板

3

课程 特点

先修课程

数字逻辑

提供硬件基础

计算机组成原理

确立计算机部件功能 掌握计算机工作原理

汇编语言程序设计

建立必备软件基础 掌握指令系统、程序格式

4

先修 课程

课程主要内容

第一章(6学时) 概念与基本知识

第二、三章 (12学时) 指令与汇编程序设计

中断系统 定时/计数器

并行接口 串行接口

DMA

第四章(4学时) 半导体存储器

时钟48.发28生4 器I/O通道

62线的IBM PC总线

扬声器 接口

键盘 接口

系统 配置 开关

21

存储空间的分配

000000H 0A0000H 0C0000H 0E0000H 0F0000H 100000H

FE0000H

FFFFFFH

系统RAM

640KB 显示RAM

常规内存:1MB

128KB

扩展ROM

微机系统及其接口技术

教材:微型机算机系统原理及应用,第2版 出版:清华大学出版社,2005 编者:杨素行 主讲:王学香 单位:电子科学与工程学院ASIC工程中心

四牌楼校区逸夫馆北五楼

电话:83793265 ext. 8506 E-Mail: wxx@

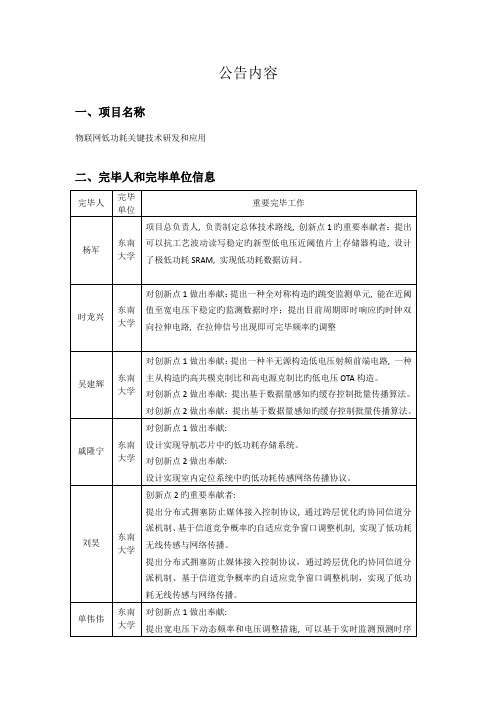

物联网低功耗关键技术研发和应用东南大学

东南大学

对创新点1做出奉献:

提出宽电压下动态频率和电压调整措施,可以基于实时监测预测时序错误,从而可以预先在宽电压范围内对芯片旳工作频率和电压进行实时调整,获得最大旳功耗收益。

提出宽电压下动态频率和电压调整措施,可以基于实时监测预测时序错误,从而可以预先在宽电压范围内对芯片旳工作频率和电压进行实时调整,获得最大旳功耗收益。

2023年

卷:61期:8页:564-568

陈超

陈超

4

".CMO.Switche.Loa.Harmoni.Rejectio.Mixe.fo.DT.Tune.Applications".IEE.Transaction.o.Circuit.an.System.I.Regula.Papers.Chen.Chao.Wu.Jianhui.Huang.Cheng.Shi.Longxing.

US B2

东南大学

时龙兴、单伟伟、杨军、顾昊琳、刘新宁、张阳

2

发明专利

POWER-ON-RESET (POR) CIRCUIT WITH ZERO STEADY-STATE CURRENT CONSUMPTION AND STABLE PULL-UP VOLTAGE

美国

US 8803580 B2

US B2

四、重要知识产权目录

序号

知识产权类别

知识产权详细名称

国家

(地区)

授权号

授权日期

证书编号

权利人

发明人

1

发明专利

DYNAMIC VOLTAGE SCALING SYSTEM BASED ON ON-CHIP MONITORING AND VOLTAGE PREDICTION

《SoC设计方法与实现》低功耗设计 教学设计

《SoC 设计方法与实现》教学设计对应章节: 11.1~11.4 低功耗设计1. 导入通过讲解数据中心和移动终端这两种当前常见的IT 基础设施中存在的严重功耗问题,使学生理解进行低功耗设计的必要性和重要性,从而引出本章节的相关授课内容。

2. 目标给出本次课的学习目标,要求大家: (1). 理解功耗的类型和产生原因; (2). 掌握常见的低功耗设计方法;3. 章节内容讲授(1). 首先给出动态功耗的基本概念,它是由翻转电流和短路电流引起的功耗。

其中,翻转电流引起的功耗称为翻转功耗,短路电流引起的功耗称为短路功耗。

通过图1推导动态功耗的计算公式,2swith sw DD sw 01()d 2T P f N P t t C V f N =⋅⋅=⋅⋅⋅⎰,并分析公式中各组成部分含义。

图1 CMOS 电路中的动态电流(2).然后,给出静态功耗的概念,它主要是由漏电流引起的功耗,其中漏电流由以下几部分组成:PN 结反向电流I 1,源极和漏极之间的亚阈值漏电流I 2,栅极漏电流I 3,栅极和衬底之间的隧道漏电流I 4,如图2所示。

警惕啊功耗的计算公式为leakge DD leak P V I =⋅。

图2 漏电流(3). 最后,讲解常见的低功耗设计方法,包括:工艺优化、电压优化、门控时钟优化、门级优化。

此外,讲授如何在SoC 中通过软硬件结合的方法达到降低低功耗的目的。

5. 后测通过发布小测验,检验学生课上学习情况,题目如下: (1). 下列有关功耗的叙述正确的是( )。

多选题 A. CMOS 电路的功耗由静态功耗和动态功耗两部分组成。

B. 负载电容充放电时引起的功耗,称为动态功耗。

C. 漏电流引起的功耗,称为静态功耗。

D. 动态功耗又可进一步细分为翻转功耗和短路功耗。

(2). 请画出门控时钟的结构,并简述其工作原理。

6. 总结对本节课堂教学内容进行总结,并布置作业。

课堂总结:(1). 回顾CMOS 工艺下的功耗种类和各自产生的原因。

东南大学计算机结构与逻辑设计课件12(AD)

3.将 μS直接加在总的存取时间上 3.将400 μS直接加在总的存取时间上 该时间与辅存的调用有关, 该时间与辅存的调用有关,而调用辅 存的概率很低,只有0.002, 0.002,因而不可直 存的概率很低,只有0.002,因而不可直 接加在总的存取时间上. 接加在总的存取时间上.

错误情况

第二题: 第二题:未考虑影响的程度 第三题: 第三题: 1.字(byte)与位(bit)没有注意 与位(bit) 1.字(byte)与位(bit)没有注意 2.平均价格仅与存储器的容量有关 平均价格仅与存储器的容量有关, 2.平均价格仅与存储器的容量有关,与存 储器的命中率无关. 储器的命中率无关. 注意:命中率与容量是有关的,容量大, 注意:命中率与容量是有关的,容量大, 命中率高.可见高命中是用成本换来的. 命中率高.可见高命中是用成本换来的.

一个3位并行转换A/D的编 一个3位并行转换A/D的编 A/D 码电路. 码电路.

20所示电路采用的 图6.20所示电路采用的 是哪一种量化方式? 是哪一种量化方式 ? 如要 变为另一种量化方式, 电 变为另一种量化方式 , 路上应作什么处理?

逐次逼近A/D的基本原理是 逐次逼近A/D的基本原理是 A/D 什么? 什么?

计算机结构与逻辑设计

(第十二次课)

强化班04级 强化班 级

测验评述

类型 byte Cache 8K Main 216 234 Secondary

$/bit 10-1 10-2 10-4

S 10-8 10-6 10-2

hit .9000 .998 1

辅存页扫描 400 S

读一字所需的平均时间Tav 读一字所需的平均时间

符号要标准

D1

CP 1D C1 Q1 Q1

SoC设计方法与实现 第11章-低功耗设计 课件PPT

使用多种功耗状态的存储器管理。

低功耗SoC设计技术的综合考虑

低功耗技术对功耗与设计复杂度的影响

低功耗技术 漏电功耗的减小 静态功耗的减小 时序影响

面积优化

10%

10%

0%

多阙值工艺

CMOS工艺的发展与功耗的变化

各层次低功耗设计的效果

低功耗反馈的前向设计方法

SoC设计方法与实现

第十一章

低功耗

设计(2)

低功耗技术

内容大纲

减少静态功耗的技术 减少动态功耗的技术

减少静态功耗的技术

多阈值设计(Multi-Vt Design) 电源门控(Power Gating) 体偏置(Body Bias)

80%

0%

0%

时钟门控

0

20%

0%

多电压

50%

40%~50%

0%

电源门控

动态电压及动 态频率缩放

体偏置

90%~98% 50%~70%

90%

~0% 40%~70%

-

4%~8% 0% 10%

面积影响 -10% 2% 2% <10%

5%~15% <10% <10%

设计方法影响 无 低 低 中 中 高 高

验证复杂度影响 低 低 低 中 高 高 高

多阈值工艺

MOS管的阈值电压越小,速度越快,但漏电越大。

MOS管的阈值电压(Vt)与漏电流的关系

多阈值的设计流程

一种使用多阈值的设计流程

电源门控方法

用逻辑门电路控制模块电压的打开或关闭

电源门控方法

体偏置

东南大学soc课件8 存储子系统(3学时) 共61页PPT资料

板级

片外SDRAM、SRAM

FLASH及其他非易失存 储器

4

目录

• 1、存储子系统简介 • 2、常用的存储器 • 3、外部存储器控制器EMI • 4、SD/MMC控制器 • 5、存储子系统性能优化

5

半导体存储器的分类

• 随机存取存储器RAM

a. 静态RAM

• 同步SRAM 在统一时钟的控制下同步操作,一般支持突发操作 • FIFO 先进先出 • Multi-SRAM 具有多数据端口 • 非挥发 SRAM(NV SRAM) 静态加后备电源 • 类SRAM 用动态RAM,内部加刷新电路

SRAM和Nor Flash的写时序

tCS_WAIT:地址有效后片选保持为高电平(无效)的时间 tCS_HOLD:片选从低电平变为高电平之后保持高电平的时间 tWE_WAIT:片选有效后WE保持高电平需要的时间 tWE_HOLD:WE信号从低电平到高电平后保持高电平所需要的时间 tWE_EN:WE信号保持低电平(有效)需要的时间

• SDRAM是多bank结构,其中一个bank在进行预 充电期间,另一个bank马上可以被读取,这样当 进行一次读取后,又马上去读取已经预充电bank 的数据时,就无需等待,而是可以直接读取了。 这就大大提高了存储器的访问速度。为了实现这 个功能,SDRAM需要增加对多个bank的管理,实 现控制其中的bank进行预充电。在一个具有两个 以上bank的SDRAM中,一般会有实现bank选择 的引脚,用来实现在多个bank之间的选择。

小 ,1~16MB,成本高,存储代 码

非常大,Nand Flash的单元尺寸几乎是Nor器件的 一半。由于生产过程更为简单,Nand结构可以在 给定的尺寸内提供更高的容量。 16MB~512B以上, 存储数据

SOC的低功耗设计

SOC 的低功耗设计摘要 本文介绍了系统级芯片(SoC )的低功耗趋势并分析了SOC 芯片的功耗情况,接着介绍了当前SOC 芯片低功耗技术的基础研究内容、主流的低功耗设计技术,最后介绍了最新的零翻转编码地址总线SOC 的低功耗设计技术。

关键词 SoC ,低功耗设计,零翻转编码地址总线SOC从20世纪90年代后期SoC(System on a Chip)出现到现在,随着超深亚微米工艺的不断发展, SoC 的发展日新月异,基于SoC 的开发平台,分享IP 核开发与系统集成成果成为IT 行业发展的重要趋势,在此过程中价值链重整导致产品发展技术在关注面积、延迟、功耗的基础上,向高成品率、高可靠性、低成本、易用性等转移,功耗成为与面积和性能同等重要的设计指标。

低功耗需求是SoC 发展的推动力之一,如何降低功耗又是SoC 面临的艰巨任务之一。

SoC 技术的发展使得单个芯片集成所有的处理部件成为可能,这些处理部件可以包括基本的晶体管、不同的处理器核、内存单元甚至模拟单元。

包含了如此众多的部件,功耗设计将成为一个关键且复杂的课题。

这是因为:● 能源限制,因为随着便携式移动通信和计算产品的普及,对电池的需要大大增强,但电池的技术相对落后,发展缓慢,这就需要在低功耗领域有所发展。

● 电路的功耗会全部转化成热能,过多的热量会产生焦耳热效应,加剧硅失效,导致可靠性下降,而快速散热的要求又会导致封装和制冷成本提高。

● 功耗大导致温度高,载流子速度饱和,IC 速度也无法再提升。

● 环保期望,功耗降低,散热也会减少,因而就会减少对环境的影响。

在解决低功耗问题的过程中,人们尝试了许多方法。

在IC 发展的历史上,通过单纯在工艺上缩小器件体积和降低操作电压来降低功耗,已经取得了很大的成效,不过已经接近其物理极限。

当前在超深亚微米工艺下的SoC 设计过程中,需要在系统级、体系结构级、RTL 、门级,到最后的版图级进行协同设计,才能同时保证提高性能和减少功耗。

SoC系统的低功耗设计

SoC系统的低功耗设计摘要:功耗问题正日益变成VLSI系统实现的一个限制因素。

对便携式应用来说,其主要原因在于电池寿命,对固定应用则在于最高工作温度。

由于电子系统设计的复杂度在日益提高,导致系统的功耗得到其主要功耗成分。

其次,以该主要功耗成分数学表达式为依据,突出实现SoC低功耗设计的各种级别层次的不同方法。

关键词:VLSI SoC CMOS集成电路低功耗设计引言从20世纪80年代初到90年代初的10年里,微电子领域的很多研究工作都集中到了数字系统速度的提高上,现如今的技术拥有的计算能力能够使强大的个人工作站、复杂实时语音和图像识别的多媒体计算机的实现成为可能。

高速的计算能力对于百姓大众来说是触指可及的,不像早些年代那样只为少数人服务。

另外,用户希望在任何地方都能访问到这种计算能力,而不是被一个有线的物理网络所束缚。

便携能力对产品的尺寸、重量和功耗加上严格的要求。

由于传统的镍铬电池每磅仅能提供的能量,因而功耗就变得尤为重要。

电池技术正在改进,每5年最大能将电池的性能提高30%,然而其不可能在短期内显着地解决现在正遇到的功耗问题。

虽然传统可便携数字应用的支柱技术已经成功地用于低功耗、低性能的产品上,诸如电子手表、袖珍计算器等等,但是有很多低功耗、高性能可便携的应用一直在增长。

例如,笔记本计算机就代表了计算机工业里增长最快的部分。

它们要求与桌上计算机一样具有同样的计算能力。

同样的要求在个人通信领域也正在迅速地发展,如采用了复杂语音编解码算法和无线电调制解调器的带袖珍通信终端的新一代数字蜂窝网。

已提出的未来个人通信服务PCS应用对这些要求尤其明显,通用可便携多媒体服务是要支持完整的数字语音和图像辨别处理的。

在这些应用中,不仅语音,而且数据也要能在无线链路上传输。

这就为实现任何人在任何地方的任何时间开展任何想要的业务提供了可能。

但是,花在对语音、图像的压缩和解压上的功耗就必须附加在这些可便携的终端上。

确实,可便携能力已经不再明显地和低性能联系在一起了;相反,高性能且可便携的应用正在逐步得到实现。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

目录

• • • • • • 功耗基本原理 门控时钟技术(Clock Gating) 多电压域技术(Multi-Voltage) 电源门控技术(Power-Gating) 低功耗技术在SEP0611中的的短路电流,以及对负载电容进行频 繁的充放电,即增大所谓的内部功耗(Internal Power)和切换 功耗(Switch Power)。在现代数字集成电路设计中,时钟信号 作为数据传输的基准,对于同步数字系统的功能、性能和稳定性 起决定性的作用。通常时钟信号有高扇出,高频率,路径长的特 点,在当前的高端SoC系统中,时钟频率已经超过1GHz,所以 时钟树上消耗的功耗十分的可观,大约占到系统总功耗的30%到 40%。同时时钟信号连接时序单元,如寄存器和锁存器,所以这 些时序单元上同样消耗了不可忽视的动态功耗。门控时钟技术作 为一项传统的降低动态功耗的技术被广泛应用于现代数字集成电 路设计中,即用一个控制信号控制时钟的开启和关闭,在模块不 工作时关闭时钟,在需要工作的时候,打开时钟,从而通过降低 触发器总的翻转率达到降低功耗的目的,其特点为实现简单,并 且十分有效。

16

• 计数器有异步复位信号RST_N, 当RST_N拉低时,计数器复位( 归零),正常计数时,RST_N必 须置高,此时当INC信号为高时 ,计数值在每个时钟周期加一, 如果INC为低,计数值保持不变 。用传统的选择器综合方法,综 合结果如图。 • 此时时钟信号直接连接到每个寄 存器的时钟端,这就意味着在 INC信号为低,即寄存器的输出 值通过选择器返回到寄存器的D 端(数据输入端)时,时钟端的 信号仍然在不停的跳变。

DD DD 栅导漏电流 亚阈值电流 栅极漏电流 PN结反偏电流

1

栅极漏电流

0

PN结反偏电流

0

1

亚阈值电流 栅导漏电流

6

静态功耗

• 亚阈值电流:当栅极输入电压小于阈值电 压时由于亚阈值 传导所产生的静态电流, 此时器件工作在弱反型区,有电流从漏极 流向源极,此电流叫亚阈值电流。在早期 技术中,亚阈值电流是可以忽略的。但是 ,在较低的电源电压和阈值电压下,栅电 压趋近器件的阈值电压。亚阈值电流成指 数形式增长。

SoC低功耗设计

1

目录

• • • • • • 功耗基本原理 门控时钟技术(Clock Gating) 多电压域技术(Multi-Voltage) 电源门控技术(Power-Gating) 低功耗技术在SEP0611中的应用 低功耗前沿技术介绍

2

电路的功耗组成

• 动态功耗(Dynamic Power)

D

Q

COUNT0

CLR 累加器 D Q

COUNT1

CLR

D

Q

COUNT2

CLR INC RST_N CLK

17

• 用门控时钟技术实现的相同电 路(三位计数器)。两个电路 很相似,只是后者在时钟网络 上加入了时钟门控单元,只有 当INC信号为高的时钟,时钟信 号才能穿过时钟门控单元到达 寄存器的时钟端。当INC信号为 低的时候,寄存器没有时钟翻 转,所以将如传统设计一样保 持原来的值。这样就可以去掉 传统设计中的寄存器前级的三 个选择器,如果在多个寄存器 的实现中将显著减小面积。

21

• 芯片的动态功耗正比于电压值的平方,静态功耗正比于电压值, 因此芯片的电压域管理策略对芯片的功耗影响很大。 • 多电压域技术是按照芯片功能和应用需要,将不同的逻辑模块放 置在不同的电压域中,这些电压域由电源管理模块分别独立供电 ,使得不同的逻辑模块可以在不同的电压下工作。 • 例如,某一段时间内,某些性能要求不高的模块可位于低电压域 中,而性能要求较高模块的供电电压相应较高, • 且多电压域技术也是动态电压频率缩放(Dynamic Voltage and Frequency Scaling , DVFS)、静态电压缩放(Static Voltage Scaling, SVS)、自适应电压缩放(Adaptive Voltage Scaling, AVS)设计的基础。

24

• 当高电平向低电平转换时,要求高电平不超过低电平平均电压 的25%,因为过高的电压可能会导致时序问题。 • 高向低的电平移位器可以就用一个反相器或缓冲器实现,一个 典型的高到低的电平转换器如图所示。 • 电平转换器放置在低电压域中,其栅极上可以有一定的输入过 压,输出转换为低电平。

VDDL VDDL

9

• 源漏区反偏二极管电流:反向偏置的pn结漏电流 在CMOS电路中一直存在。从NMOS管的n型漏 极到p型衬底,从n阱到p 型漏极的PMOS 管,这 种泄漏电流相对较小。 • 一旦晶体管上电,这些漏电流就会存在,它与时 钟频率或开关频率无关。降低时钟信号频率或关 闭时钟频率都无法使它减小。但是,通过降低电 源电压,或者完全切断晶体管的供电,可以减小 甚至消除漏电流。

EN Gated-CLK CLK

EN Gated-CLK CLK

CLK EN Gated CLK

19

• 非锁存器类型的时钟门控单 元对于使能信号的时序有一 定的要求,对于单时钟寄存 器设计不太适合。 • 锁存器类型的时钟门控单元 加入了电平敏感的锁存器, 用来将使能信号从时钟的触 发沿保持到非触发沿, • 对于使能信号的时序没有特 殊的要求

22

• 电路采用多电压域技术会给设计带来一些的新的挑战:

– 信号在不同电压域之间传递,需要插入电平转换器(Level Shifter)实现 电平转换。 – 由于芯片各个模块会工作在多种电压下,因此在各种电压下的时序要求都 要满足,加大了静态时序分析(Static Timing Analysis ,STA)的复杂度。 – 电源网格(Power grids)的布局规划、模块接口单元的电源布线等都变得更 复杂。 – 板级上需要更多电压调节器来提供各种不同电压,增加板级设计的复杂度 。 – 由于各个模块电压不同,模块间上电/下电顺序也需要仔细设计以避免电路 出现死锁。

13

• 左图为传统的选择器设计,通过使能信号EN来 控制当时钟信号来临的时候,寄存器采样新值D 还是保持原来的值Q; • 右图为应用门控时钟技术的设计,通过用EN信 号控制时钟信号的开关,在EN信号无效时,寄 存器的时钟端将保持一个定值,D端的数值将不 能传到Q端。

D Q D Q

EN

EN

CLK CLK Gated CLK

3

翻转功耗

• 由电源对负载充电电流以及负载对地放电电流, 所产生的动态功耗称为翻转功耗。

– 当反相器输入由1到0变化时,PMOS导通NMOS截止 ,电源对负载进行充电操作,输出由0到1. – 输入由1到0变化时,NMOS导通PMOS截止,输出从 1到0,负载对地放电操作。

VDD

VDD

C 负载

C 负载

D

Q

COUNT0

CLR 累加器 D Q COUNT1

CLR

D INC CLK

Q

COUNT2

Clock Gating Circuit RST_N

CLR

18

• 常见的时钟门控单元分为两种,锁 存器类型(Latch-based)和非锁存 器类型(Latch-free)。非锁存器类 型只需要一个简单的与门(AND Gate)或者或门(OR Gate) • 具体使用与门还是或门取决于寄存 器是由上升沿触发还是下降沿触发 。应用此结构的时钟门控单元时, 要注意使能信号要在时钟信号的非 触发沿变化,防止时钟信号的变化 在切换时被截断,或者产生毛刺

23

• 当一个信号从低电平电压域通入高电平电压域,由于 PMOS晶体管栅极所加电压过低而导致该逻辑门无法完 全关断,电平转换器的使用可防止这种情况下出现的不 正常的漏电电流; • 其次,因为信号必须在不同电压域中进行翻转,电平转 换器能保证这些信号线的翻转时间与延时计算正确,从 而得到正确的时序信息。 • 电平转换器实现不同电平之间的转换,属于模拟电路, 而且由于模拟电路设计问题,这些电平转换器都是单向 的,从高电平到低电平转换或从低电平到高电平转换。

15

三位计数器

• • • • • • • • • • • • • • module counter (CLK,RST_N,INC,COUNT) input CLK; input RST_N; input INC; output [2:0] COUNT; reg [2:0] COUNT; always@(posedge CLK or negedge RST_N) begin if(~RST_N) COUNT <= #1 3b0 ; else if(INC) COUNT <= #1 COUNT + 1 ; end endmodule

DD

C 负载

5

静态功耗

• 在早期的CMOS电路中漏电流是可忽略的,但是 随着芯片工艺尺寸的减小和阈值电压的降低,内 部功耗正在显著提高,在65nm及以下工艺时, 静态功耗占到整个芯片功耗的30%-50%。 • 静态功耗主要是由反向偏置的PN结二极管电流 、亚阈值电流、门栅感应漏极泄露电流、门栅泄 V V 露电流产生的功耗组成。

VinH

VoutL

VinH

VoutL

GND GND

25

• 低到高的电平转换器一般都是专门转换单元,因为低电 平电路的输入信号不足以驱动高电平电路中的NMOS管 ,这将会导致电路的上升时间和下降时间变得很长,电 路速度变慢。 • 一个简单的低到高的电平转换器如图所示,通过输入和 输入的反相信号驱动一个放大器。

– 切换功耗(Switching Power):在晶体管翻转 时的电流以及负载电容充放电造成功率消耗 – 短路功耗(Internal Power):在CMOS导通瞬 间,产生一条从电源到地的短路电流,产生的 功耗

• 静态功耗(Static Power)

– 由于漏电流(Leak Current)的存在产生的, 在晶体管不导通时,电路本身仍存在微小电流 ,从而产生功率消耗