lt1088芯片引脚功能简介

IC卡基础知识

IC卡基础知识(引脚,特点及读写时序图)--------------------------------------------------------------------------------IC卡基础知识(引脚,特点及读写时序图)自从80年代中期出现IC电话卡后,基本已取代了原来流行的电话磁卡,磁卡存在存在严重的安全问题,已逐步淘汰。

即使IC电话卡,也不能算很安全,卡内所有数据只要有简单的读写装置并按时序操作都能读取,事实上电话卡和信用卡一样内部没有什么秘密信息,仅仅是带串行输出的128位EPROM而已(对二类卡是256位PROM),不要以为弄懂了它是怎么工作你就有办法重新对卡内数据重新填充,其开始的64位是带写保护的,在出厂时其熔丝位已被编程,你已无法对其更改,其后的40位计数单元受内部逻辑控制在写时只能减少不能增加直至到0为止,因此你想用一般的IC电话卡打免费电话是不可能的,除非你能用微控制器(单片机)仿真它(如果你能读懂本文介绍的所有内容)。

IC电话卡是一种一次性使用的计数卡,以一次性的计数方式,从写满的计数器中减“1”,直至存储单元减为空为止。

卡片每次消费计数的“单位价值”根据各种应用系统的实际需要而定。

例如:对于中国IC 电话卡,如30元卡对应内部计数值为300,每单位值对应0.1元,IC 卡电话机每分钟产生一次扣费信号,扣费值由当地IC电话管理系统设定,一般是价值0.5元或1元,卡片被计数5次和10次。

对于其它国家属于第一类IC电话卡而言也是如此,只是内部初始计数值不同,每次扣除额度不一样罢了。

其他对于公用加油卡,IC卡计费加油机每一公升(或一加仑)产生一次扣费操作,卡片被操作一次扣2.5元等等,均属于等同原理。

事实上,这类卡内部为128位(16字节)NMOS存储器,按如下规律分布:64 位EPPOM(8字节)写保护区(芯片数据代码区、发行数据代码区)40 位EEPROM(5字节)24 位为全“1”(3字节)共16字节数据。

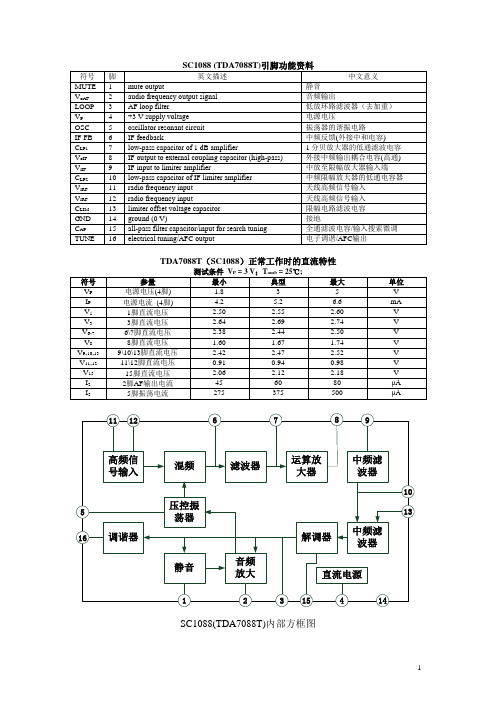

SC1088(TDA7088T)调频调频收音机资料

TDA7088T(SC1088)正常工作时的直流特性SC1088(TDA7088T)内部方框图SC1088(TDA7088T)典型接线图使用SC1088(TDA7088T)组装调频接收机●IC产品型号:SC1088(TDA7088T)●产品名称:自动调谐的调频收音机接收电路●产品概述:SC1088是一块适用于单声道便携式或手掌式超小型调频收音机的专用电路,它采用先进的双极型工艺制造,在外围元件的数量、尺寸及成本上变得很重要时,可优先选用该电路。

该电路中含有一个中频(IF)约为70kHz的锁相环回路(FLL),选择性通过一有源RC 滤波器来调整,与中频相应的未调谐信号和低输入信号由静噪电路抑制。

●主要特点:含有单声道收音机从天线接收到音频输出的所有功能静噪功能外接一只变容二极管可进行自动搜寻调谐采用内部AFC电路可进行机械调谐可支持调幅接收应用电源极性反接保护电源电压低至1.8V仍可正常工作●应用:机械调谐方式:可用、也可不用内置的AFC电路自动调谐方式:可实现单方向(向高频方向)的自动搜寻调谐功能;包括复位功能,即回到频段的最低段●封装SC1088——SOP-16-225-1.27●FM自动选台调谐收音机的制作(TDA7088与SC1088引脚及工作原理完全一样,可互换):【功能】本文介绍的袖珍FM电脑选台收音机采用飞利浦公司开发生产的TDA7088T(SC1088)集成块,采用16脚双列扁平封装,工作电压为3V,该电路除包含FM 收音机从天线接收到鉴频输出音频信号的全部功能外,还设有搜索调谐电路、信号检测电路、静噪电路以及压缩中频频偏的频率锁定环FLL电路。

TDA7088T(SC1088)电路的中频频率设计为70kHz,外围电路不用中频变压器,其中频选择由电路内部RC中频滤波器来完成。

该机像数字调谐收音机那样采用电调谐按钮(RUN),另一只是复位按钮(RESET)。

电路接通电源后,按一下搜索按钮,电路自动地由频率低端向高端搜索电台,一旦搜索到电台信号,调谐自动停止。

一种真有效值测量方案设计与验证

第 21 卷 第 7 期2023 年 7 月太赫兹科学与电子信息学报Journal of Terahertz Science and Electronic Information TechnologyVol.21,No.7Jul.,2023一种真有效值测量方案设计与验证刘宁庄1,段富才1,文迪雅1,许龙2(1.西安科技大学电气与控制工程学院,陕西西安710600;2.中国计量大学理学院,浙江杭州310018)摘要:针对目前国内真有效值(RMS)测量芯片依赖进口的问题,提出了一种基于现场可编程门阵列(FPGA)的数字式高精确度的真有效值测量方案。

首先利用FPGA设计有限长单位冲击响应滤波器(FIR)对AD采样后的数据进行滤波,然后采用改进的有效值计算式计算信号的真有效值,最后取连续8个周期真有效值的平均值作为最终的测量结果。

通过设计串行的开方运算、除法运算的算法,降低FPGA的使用资源。

经过样机实际测试表明,测量结果与信号真值的相对误差低于0.5%。

该方案测量精确度高,一致性好,使用资源少,对于真有效值数字测量芯片的设计和真有效值测量具有一定的参考价值。

关键词:数字测量;真有效值;现场可编程门阵列;冲击响应滤波器;开方运算;除法运算中图分类号:TM932 文献标志码:A doi:10.11805/TKYDA2020738Design and verification of a true root mean square measurement schemeLIU Ningzhuang1,DUAN Fucai1,WEN Diya1,XU Long2(1.School of Electric and Control Engineering,Xi'an University of Science and Technology,Xi'an Shaanxi 710600;2.College of Science,China Jiliang University,Hangzhou Zhejiang 310018)AbstractAbstract::A high-precision and digital true root mean square measurement method based on Field Programmable Gate Array(FPGA) is presented. Firstly, FPGA is employed to design Finite ImpulseResponse(FIR) filter to filter the AD sampled data. Furthermore, the improved RMS formula is adopted tocalculate the true RMS of the signal. The mean value of the true RMS value of eight consecutive cycles istaken as the final measurement result. By designing the algorithms of serial extraction and divisionoperations, the use of FPGA resources is reduced. The actual test of the prototype shows that the relativeerror between the measurement results and the true value of the signal is less than 0.5%. The solutionhas high measurement accuracy, good consistency, and less resources, which has certain reference valuefor the design of the true RMS digital measurement chip.KeywordsKeywords::digital measurement;true root mean square;Field Programmable Gate Array;Finite Impulse Response filter;square root operation;division operation测量交流信号的真有效值对分析信号的功率以及其他参数都有重要意义[1-4]。

厦华T系列IC内部框图和主要功能、引脚介绍

T#机IC内部框图和主要功能、引脚介绍一:AD9880与AD9398 HDMI接口ICHDMI接口是快速兴起的数字接口标准,适用于高级电视、前投式投影电视、液晶显示器(LCD)电视和监视器以及等离子平板显示器(PDP)。

ADI公司的AD9880同时具有高达165 MHZ工作频率的HDMI数字和模拟接口,它是业界首款能支持1080P(逐行扫描)和UXGA(1600×1200,在60 HZ频率条件下)视频格式的单芯片HDMI数字和模拟双接口,同时它也支持8个192 KHZ通道的音频。

AD9880提供一种可以取代两芯片的集成解决方案,从而将模拟和数字接口两种功能集成到一颗单芯片上以便降低设计复杂程度、缩小印制电路板面积和模拟接收接口和HDMI数字接收接口都以165 MHZ 最高速度工作。

该AD9880也支持宽带数字内容保护(HDCP)V1.1版本标准用于发送和接收数字保护的内容。

AD9398是AD9880的精简版本,删去模拟接口保留和AD9880兼容的封装和管脚定义,的HDMI接口IC。

其内部框图、引脚结构图和引脚定义表如下:AD9880(AD9398)引脚功能表二:PW2300PW2300 是一款集成高性能、多制式、3D视频解码器,三组高速AD转换器的前端信号处理芯片。

PW2300的模拟接口支持1080P(150Mhz)的最高分辨率。

该芯片还支持所有的HDTV和NTSC,PAL,SECAM等视频标准。

并且PW2300还利用Pixel works 的SteadySync TM专利技术可以保证在较差的信号下也可以收看到高质量的视频信号。

下图为内部结构框图和引脚图:PW2300引脚说明三:PW218PW218是Pixel works新产品线中第一个高质量SOC图像处理芯片,在芯片内部集成先进的Scaling和Deinterlacing功能。

四:TPA3008、TPA3008是双通道10W立体声D类音频功放。

戴尔 Vostro 1088 笔记本电脑配置

1 MHKCV DVD+/-RW,8,12.7,SATA,TRAY,HLDS

1 MU373 CARD,WARR,SERV,CCC

1 MY297 LBL,FASC,INTEL,CARTON

1 N114C TEST MOD,DIMM,2GB,800,DDR2,1X2G,VOS

显卡: ATI Mobility Radeon HD 4330 (M92) ( 512 MB / 戴尔 )

显示器: 三星 SEC5441 ( 13.6 英寸 )

光驱: 日立-LG DVD+-RW GT32N DVD刻录机

声卡: High Definition Audio 设备 @ 英特尔 82801I(ICH9) 高保真音频

缓存/固件: 8 MB / GJ002D

硬盘已使用: 共 19 次,累计 20 小时 54 分钟

接口: SATA Rev 2.5

数据传输率: 300 MB/秒

特征: S.M.A.R.T, 48-bit LBA, NCQ

光驱

产品: 日立-LG DVD+-RW GT32N DVD刻录机

1 JR749 Directship Info Mod

1 K326C 320GB SATA Hard Drive

1 K7CM0 Technical setup sheet for V1088 (Simplified Chinese)

1 K8YF9 Resource DVD for Vostro 1088 for n-Series

1 RK224 CORD,PWR,250V,2.5A,1M,C5,E,CHI

LA76810引脚功能介绍

LA76810引脚功能介绍引脚数据如下:引脚电压(V)功能说明1 2.3 音频开关选择,音频信号(TV或AV)输出端2 2.3 伴音鉴频外接去加重电容3 2.5 中频AGC检波滤波电容4 1.6 射频AGC电压输出5 2.8 图象中频信号输入16 2.8 图象中频信号输入27 0 中频电路地8 5 中频电路5V电压9 2 调频检波滤波电容10 2.5 AFT控制电压输出11 4.6 总线控制数据输入/输出端12 4.6 总线控制时钟输入端13 4.3 ABL检测输入端14 .8 字符R输入端15 .8 字符G输入端16 .8 字符B输入端17 0 快速消隐脉冲输入端,阀值电压为2V,当该脚电压大于2V时,(19)~(21)脚输出屏显R、G、B信号;当该脚电压小于2V时,(19)~(21)脚输出图象R、G、B 信号18 8 RGB输出电路电源电压输入端19 1.9 R信号输出20 1.9 G信号输出21 1.9 B信号输出22 .3 ID识别同步信号输出端23 2.3 场偏转激励锯齿波电压输出端24 2.7 场偏转锯齿波形成电容及平滑电容外接端25 5 行扫描电路及总线接口电路电源输入端26 2.6 AFC1环路低通滤波器RC时间常数影响行同步引入/保持范围及同步稳定性27 .6 行扫描激励脉冲输出端28 1.1 AFC2环路比较行,逆程脉冲输入端改变R、C值可调画面水平中心29 1.6 参考电流产生端需外接4.7K电阻接地30 .9 4MHz时钟信号输出端交流耦合(30P)送到SECAM解码电路31 5 1H基带延迟线电路5V电源电压输入端32 8.3 内藏1H基带延迟线的升压电路(泵电源)输出端外接自举电容33 0 1H延迟线及偏转信号处理电路接地端34 2.4 SECAM解码B-Y信号输入端不用时经0.01uF接地35 2.4 SECAM解码R-Y信号输入端不用时经0.01uF接地36 0 色副载波恢复VCO低通滤波电容外接端37 2.3 SECAM电路接口端此脚不用时,需经10K接地38 2.8 4.43MHz晶振39 3.5 色副载波VCO电路PLL环路低通滤波器外接端40 2.2 内置视频选择开关选择CVBS信号输出端41 0 视频、色度、偏转电路接地端42 2.5 外视频信号或Y信号输入端43 5 视频、色度、偏转电路电源44 2.7 内视频信号或外(AV)色度信号C输入端45 3.1 黑电平扩展滤波电容46 2.4 TV视频信号输出端47 3.6 图象中频载波(38MHz)VCO、PLL环路滤波器外接端48 0 图象中频载波恢复VCO振荡电路外接端149 4.2 图象中频载波恢复VCO振荡电路外接端250 2.4 VCO滤波器外接端推荐用0.1uF51 2.2 外(AV)音频信号输入端52 1.9 第二伴音中频信号输出端53 2.1 伴音解调APC低通滤波器外接端54 3.1 第二伴音中频信号(4.5~6.5MHz)输入端LA76810内部完成中频放大,锁相环视频检波、AGC电压、AFT电压检测等处理后,解调出视频信号。

LED显示屏常用IC管脚说明【LED显示屏维修资料】

常用器件的介绍1.IC的管脚功能IC芯片分别:74HC245、74HC595、74HC138、74HC04、4953。

各IC管脚功能如下:A: 74HC245功能是放大及缓冲。

各引脚如图20 和1接电源(+5V)19脚和10脚接电源地(GND)当电源是以上接时:输入脚分别为2、3、4、5、6、7、8、9。

1输出脚分别为11、12、13、14、15、16、17、18注:2脚输入时,18脚输出。

其它脚以此类推。

B:74HC138功能是8选1译码器,输出为8行。

控制行数据。

各引脚如图第8脚GND,电源地。

第15脚VCC,电源正极第1-3脚A、B、C,输入脚。

第4-6脚选通输入端,(一般第5脚为EN )9-15脚和第7脚输出端。

C:74HC595功能是8位串入、并出移位寄存器。

控制列数据。

各引脚如图216脚和10脚接电源(+5V),13脚和8脚接电源地(GND)。

列信号输出脚:1、2、3、4、5、6、7、15。

第一列输出脚为7脚,以此类推。

另第八列输出脚为15脚。

数据信号输入脚(Din)为14,数据信号输出脚(Din)为9。

锁存信号脚(L)为12脚,移位信号脚(S)为11脚。

D:74HC04功能是六带缓冲反相器,控制使零信号(EN)。

各引脚如下图314脚接电源(+5V),7脚电源地(GND)。

信号输入脚为:1、3、5、9、11、13。

信号输出脚为:2、4、6、8、10、12。

E:4953行管功能是开关作用,每个行管控制2行。

1脚和3脚接电源(+5V)。

信号输入脚:2、4。

信号输出脚:5、6、7、8。

5脚和6脚为一组输入,47脚和8脚、5脚和6脚为一组输出。

P10单元板,是由1个74HC245,一个74HC04.一个74HC138,四个行管4953和16个74HC595列管组成.TB62726与5026 5024 16126的作用:LED驱动芯片,16位移位锁存器。

第1脚GND,电源地。

第24脚VCC,电源正极第2脚DATA,串行数据输入第3脚CLK,时钟输入.第4脚STB,锁存输入 .第23脚输出电流调整端,接电阻调整第22脚DOUT,串行数据输出第21脚EN,使能输入第5-12脚和13-20脚驱动输出端。

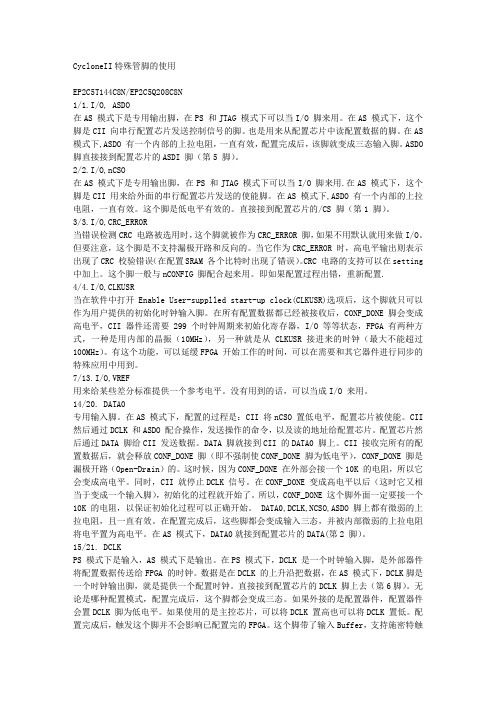

CYCLONEⅡ特殊管脚

CycloneII特殊管脚的使用EP2C5T144C8N/EP2C5Q208C8N1/1.I/O, ASDO在AS 模式下是专用输出脚,在PS 和JTAG 模式下可以当I/O 脚来用。

在AS 模式下,这个脚是CII 向串行配置芯片发送控制信号的脚。

也是用来从配置芯片中读配置数据的脚。

在AS 模式下,ASDO 有一个内部的上拉电阻,一直有效,配置完成后,该脚就变成三态输入脚。

ASDO 脚直接接到配置芯片的ASDI 脚(第5 脚)。

2/2.I/O,nCSO在AS 模式下是专用输出脚,在PS 和JTAG 模式下可以当I/O 脚来用.在AS 模式下,这个脚是CII 用来给外面的串行配置芯片发送的使能脚。

在AS 模式下,ASDO 有一个内部的上拉电阻,一直有效。

这个脚是低电平有效的。

直接接到配置芯片的/CS 脚(第1 脚)。

3/3.I/O,CRC_ERROR当错误检测CRC 电路被选用时,这个脚就被作为CRC_ERROR 脚,如果不用默认就用来做I/O。

但要注意,这个脚是不支持漏极开路和反向的。

当它作为CRC_ERROR 时,高电平输出则表示出现了CRC 校验错误(在配置SRAM 各个比特时出现了错误)。

CRC 电路的支持可以在setting 中加上。

这个脚一般与nCONFIG 脚配合起来用。

即如果配置过程出错,重新配置.4/4.I/O,CLKUSR当在软件中打开Enable User-supplled start-up clock(CLKUSR)选项后,这个脚就只可以作为用户提供的初始化时钟输入脚。

在所有配置数据都已经被接收后,CONF_DONE 脚会变成高电平,CII 器件还需要299 个时钟周期来初始化寄存器,I/O 等等状态,FPGA 有两种方式,一种是用内部的晶振(10MHz),另一种就是从CLKUSR 接进来的时钟(最大不能超过100MHz)。

有这个功能,可以延缓FPGA 开始工作的时间,可以在需要和其它器件进行同步的特殊应用中用到。