SN 芯片引脚功能

芯片引脚功能范文

芯片引脚功能范文芯片引脚是指芯片外部连接的金属引脚,用于传递信号和能量。

一、主要引脚类型及其功能:1.电源引脚:电源引脚主要用于提供芯片所需的电源电压和电流。

其中,VCC引脚是供电的正电源,GND引脚是供电的地引脚。

根据芯片的需求,可能还有多组不同电压的电源引脚,用于供给不同功能部分的工作电压。

2.输入引脚:输入引脚一般用于接收外部信号,通过这些引脚可以将外部信号输入到芯片内部,用于处理和判断。

输入引脚需要具备一定的电阻和电容来提高信号的稳定性和抗干扰能力。

3.输出引脚:输出引脚将芯片内部的处理结果输出到外部,供其他设备或电路使用。

输出引脚需要具备一定的驱动能力和电流限制,以兼容外部设备的接收能力。

4.控制引脚:控制引脚用于控制芯片内部的一些功能和模块,通过控制引脚的电平状态,可以控制芯片的工作模式、工作频率等参数。

控制引脚在外部接口中通常具备一定的阻抗保护电路,以保证控制信号的稳定性和抗干扰能力。

5.时钟引脚:时钟引脚用于将时钟信号输入芯片内部的时钟模块,以提供时钟脉冲来同步芯片内部的各个模块和功能。

时钟引脚通常需要在外部添加相应的电容和电阻来保持信号质量和抗干扰能力。

6.复位引脚:复位引脚用于将芯片或其部分功能置于预定义的初始状态。

当复位引脚接收到复位信号时,芯片内的各个模块会完成一系列复位操作,使芯片处于初始状态。

7.地址引脚:地址引脚用于选择芯片内的存储单元,例如存储器的地址引脚可以选择要读或写的存储单元。

地址引脚的数量取决于芯片的寻址范围,一般有多个地址引脚,形成一个地址总线。

8.数据引脚:数据引脚用于数据传输,通常分为输入数据引脚和输出数据引脚。

输入数据引脚接收外部数据输入,输出数据引脚将芯片内部处理的数据输出。

数据引脚的数量取决于数据位宽,一般有多个数据引脚,形成一个数据总线。

9.中断引脚:中断引脚用于外部设备向芯片发出中断请求信号,以通知芯片进行一些紧急或重要的处理。

中断引脚有助于降低芯片对处理器的频繁轮询,提高系统性能。

芯片引脚的功能和原理-概述说明以及解释

芯片引脚的功能和原理-概述说明以及解释1.引言1.1 概述概述:芯片引脚是电子芯片上的一组导线或金属接点,用于与外部电路或设备进行连接和通信。

芯片引脚的功能和原理是电子芯片设计中的关键要素,对于芯片的性能和功能起着重要的作用。

本文将从芯片引脚的功能和原理两个方面进行探讨。

首先,我们将介绍芯片引脚的功能,包括输入功能和输出功能。

其次,我们将深入探讨芯片引脚的原理,包括电信号传输原理和引脚布线设计原理。

最后,我们将对芯片引脚的设计重要性进行思考并进行总结。

通过本文的阅读,读者将对芯片引脚的功能和原理有更加深入的了解,为电子芯片的设计和应用提供有益的参考和指导。

1.2 文章结构文章结构部分的内容可以描述整篇文章的组织方式和各个章节的内容概述,为读者提供一个整体的了解。

下面是关于文章结构的内容:文章结构:本文将围绕着"芯片引脚的功能和原理"展开详细论述。

全文分为引言、正文和结论三个部分。

引言部分首先对文章的研究对象进行了概述,即芯片引脚的功能和原理。

然后介绍了整篇文章的结构和目的,以供读者了解文章的主要内容和意图。

正文部分是本文的核心,主要分为两个部分:芯片引脚的功能和芯片引脚的原理。

在芯片引脚的功能部分中,将详细讨论芯片引脚的输入功能和输出功能,包括它们的定义、作用以及在芯片电路中的应用。

而在芯片引脚的原理部分,将着重介绍电信号传输原理和引脚布线设计原理,解释芯片引脚的工作原理和其与整个芯片电路的关系,为读者提供深入的理解。

结论部分对前文的内容进行总结,并对芯片引脚设计的重要性进行思考。

通过本文的探讨,我们可以更好地理解芯片引脚的功能和原理,并认识到合理的引脚设计对芯片电路的性能和稳定性的重要性。

同时,我们也可以对今后的芯片设计提供一些思考和启示。

通过以上的文章结构,希望能够为读者提供一个清晰的阅读框架,使读者能够更好地理解和掌握芯片引脚的功能和原理。

1.3 目的文章目的是介绍和解析芯片引脚的功能和原理。

芯片的引脚

芯片的引脚芯片的引脚是一种连接芯片内部电路和外部设备的接口,用于传递信息和控制信号。

每个芯片都会有一定数量的引脚,引脚的数量和功能会因芯片的类型和用途而有所不同。

一、分类和功能1. 电源引脚:芯片的电源引脚用于提供芯片所需的正、负电压和接地。

一般情况下,芯片会有多个电源引脚,包括供电输入、地线和各种电压级别的引脚。

2. 数字输入/输出引脚:数字输入/输出引脚用于芯片与数字设备之间的数据传输。

这些引脚可以接受或发送数字信号,用于数据传输、通信和控制。

3. 模拟输入/输出引脚:模拟输入/输出引脚用于传输模拟信号。

这些引脚接收来自外部设备的模拟信号,或将芯片内部产生的模拟信号输出到外部设备。

4. 控制引脚:控制引脚用于控制芯片内部电路的工作状态。

通过这些引脚可以选择输入/输出模式、开关电源或触发特定功能。

5. 时钟引脚:时钟引脚用于提供芯片内部电路的时序信号。

这些引脚接收外部的时钟信号,以确保芯片内部电路按照正确的时序工作。

6. 复位引脚:复位引脚用于将芯片内部电路恢复到初始状态。

当复位引脚接收到复位信号时,芯片的各个模块将重新初始化。

7. 中断引脚:中断引脚用于接收来自外部设备的中断请求。

当外部设备发生某种需要芯片关注的事件时,可以通过中断引脚向芯片发送信号。

二、引脚标识方法通常情况下,芯片的引脚会根据其功能进行编号和标识。

下面介绍几种常见的引脚标识方法:1. 行号/列号标识法:引脚按照芯片的排列方式被分为行和列,并通过行号和列号进行标识。

例如,一个24x32的芯片,引脚标识为A1, A2, B1, B2,其中A和B为行号,1和2为列号。

2. 功能标识法:引脚根据其功能进行标识。

例如,V_CC表示电源引脚,D_I/O表示数字输入/输出引脚,A_I/O表示模拟输入/输出引脚。

3. 数字标识法:引脚通过数字进行标识,按照从1开始的顺序编号。

这种方法简单直观,但不便于辨识和理解引脚的功能。

三、引脚的布局引脚的布局是指芯片上引脚的物理排列方式。

电路常用IC引脚功能图

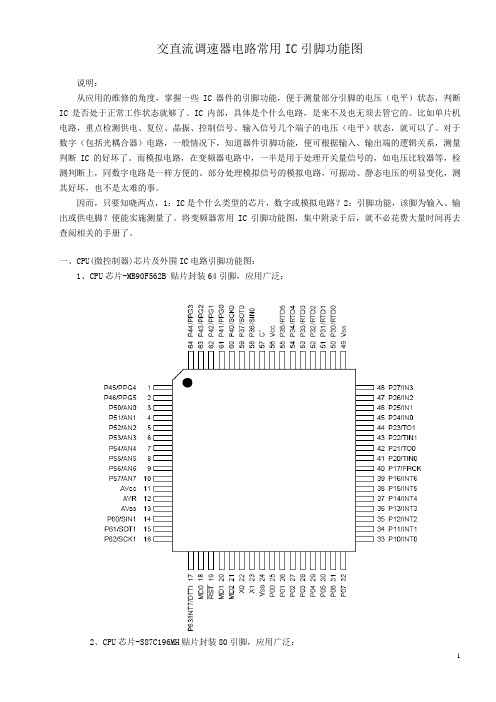

交直流调速器电路常用IC引脚功能图说明:从应用的维修的角度,掌握一些IC器件的引脚功能,便于测量部分引脚的电压(电平)状态,判断IC是否处于正常工作状态就够了。

IC内部,具体是个什么电路,是来不及也无须去管它的。

比如单片机电路,重点检测供电、复位、晶振、控制信号、输入信号几个端子的电压(电平)状态,就可以了。

对于数字(包括光耦合器)电路,一般情况下,知道器件引脚功能,便可根据输入、输出端的逻辑关系,测量判断IC的好坏了。

而模拟电路,在变频器电路中,一半是用于处理开关量信号的,如电压比较器等,检测判断上,同数字电路是一样方便的。

部分处理模拟信号的模拟电路,可据动、静态电压的明显变化,测其好坏,也不是太难的事。

因而,只要知晓两点,1:IC是个什么类型的芯片,数字或模拟电路?2:引脚功能,该脚为输入、输出或供电脚?便能实施测量了。

将变频器常用IC引脚功能图,集中附录于后,就不必花费大量时间再去查阅相关的手册了。

一、CPU(微控制器)芯片及外围IC电路引脚功能图:1、CPU芯片-MB90F562B 贴片封装64引脚,应用广泛:2、CPU芯片-S87C196MH贴片封装80引脚,应用广泛:3、CPU芯片-MN18992MDY-6 塑封双列直插,64引脚,用于松下早期DV551、DV561机型:4、CPU芯片-HD6404733037F 贴片封装80引脚,应用广泛:5、存储器引脚功能图:93C56 24C04A 93C66 6、RS485通讯模块引脚功能图:ADM485 SN75179B二、常用运算放大器引脚功能图:LF347四运放电路 LM324四运放电路 LM339四运放(开路集电极输出)LF353 双运放电路 LM393 双运放(开路集电极输出) TL072四运放电路运算放大器多用于电流、电压检测电路,用于处理模拟信号和将模拟信号转换为开关量信号——报警、停机保护信号。

开路集电极输出型多用于电压比较器电路。

单片机各个引脚功能概述

单片机各个引脚功能概述单片机是一种集成电路,其中具有多个引脚,每个引脚都具有不同的功能。

下面是单片机各个引脚的功能概述:1.VCC:VCC引脚为单片机的电源引脚,通常连到电池或电源电压上。

它为单片机提供正向电源,电压通常为3.3V或5V。

2.GND:GND引脚为单片机的接地引脚,通常使用地线连接到电路板的地方。

该引脚为单片机提供回路的参考点。

3.XTAL1和XTAL2:XTAL1和XTAL2引脚是单片机的振荡器引脚,通常连接到晶体振荡器或陶瓷谐振器中的引脚。

这些引脚提供时钟脉冲,以控制单片机的时序和计时。

4.RESET:RESET引脚是单片机的复位引脚,通常使用它来将单片机恢复到初始状态。

当RESET引脚被拉低时,单片机将重新启动。

5.P0.0-P0.7:P0.0-P0.7是单片机的I/O端口0引脚,用于连接外部设备。

这些引脚可以被配置为输入或输出端口,以与外部设备通信。

6.P1.0-P1.7:P1.0-P1.7是单片机的I/O端口1引脚,用于连接外部设备。

这些引脚也可以被配置为输入或输出端口,以与外部设备通信。

7.P2.0-P2.7:P2.0-P2.7是单片机的I/O端口2引脚,用于连接外部设备。

这些引脚可以被配置为输入或输出端口,以与外部设备通信。

8.P3.0-P3.7:P3.0-P3.7是单片机的I/O端口3引脚,用于连接外部设备。

这些引脚也可以被配置为输入或输出端口,以与外部设备通信。

9.INT0和INT1:INT0和INT1引脚是单片机的外部中断引脚,用于检测外部中断事件。

这些引脚通常用于响应外部事件,例如按下按钮或检测外部信号。

10.TXD和RXD:TXD引脚是单片机的串行传输引脚,用于发送串行数据。

RXD引脚是单片机的串行接收引脚,用于接收串行数据。

这些引脚通常用于单片机与其他设备(例如计算机或传感器)之间的通信。

11.ADC0-ADC7:ADC0-ADC7引脚是单片机的模拟输入引脚,用于连接模拟传感器或外部设备。

锁存器SN74HC使用总结

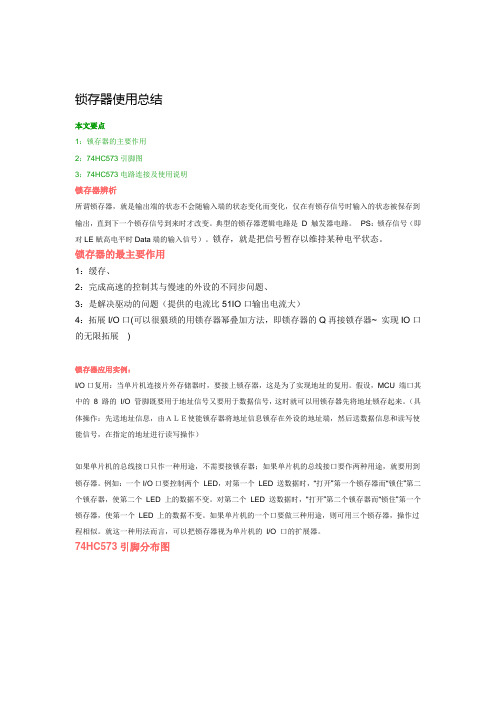

锁存器使用总结本文要点1:锁存器的主要作用2:74HC573引脚图3:74HC573电路连接及使用说明锁存器辨析所谓锁存器,就是输出端的状态不会随输入端的状态变化而变化,仅在有锁存信号时输入的状态被保存到输出,直到下一个锁存信号到来时才改变。

典型的锁存器逻辑电路是 D 触发器电路。

PS:锁存信号(即对LE赋高电平时Data端的输入信号)。

锁存,就是把信号暂存以维持某种电平状态。

锁存器的最主要作用1:缓存、2:完成高速的控制其与慢速的外设的不同步问题、3:是解决驱动的问题(提供的电流比51IO口输出电流大)4:拓展I/O口(可以很猥琐的用锁存器幂叠加方法,即锁存器的Q再接锁存器~ 实现IO口的无限拓展···)锁存器应用实例:I/O口复用:当单片机连接片外存储器时,要接上锁存器,这是为了实现地址的复用。

假设,MCU 端口其中的8 路的I/O 管脚既要用于地址信号又要用于数据信号,这时就可以用锁存器先将地址锁存起来。

(具体操作:先送地址信息,由ALE使能锁存器将地址信息锁存在外设的地址端,然后送数据信息和读写使能信号,在指定的地址进行读写操作)如果单片机的总线接口只作一种用途,不需要接锁存器;如果单片机的总线接口要作两种用途,就要用到锁存器。

例如:一个I/O口要控制两个LED,对第一个LED 送数据时,“打开”第一个锁存器而“锁住”第二个锁存器,使第二个LED 上的数据不变。

对第二个LED 送数据时,“打开”第二个锁存器而“锁住”第一个锁存器,使第一个LED 上的数据不变。

如果单片机的一个口要做三种用途,则可用三个锁存器,操作过程相似。

就这一种用法而言,可以把锁存器视为单片机的I/O 口的扩展器。

74HC573引脚分布图由上边这个真值表可以看出:OE为高时,输出始终为高阻态,此时芯片处于不可控制状态,所以在一般应用中,我们必须将OE接低电平。

LE则是输出端状态改变使能端,当LE为低电平,输出端Q始终保持上一次存储的信号(从D端输入),当LE为高电平时,Q紧随D的状态变化,并将D的状态锁存。

SN与TI,LS、HC与HCT的区别

SN与TI,LS、HC与HCT的区别公司不同+历史原因,实际区别不大CD是harris的前缀,SN是TI的前缀。

但TI也同时出品CD前缀的,可能是为了保持连续性。

74HC/LS/HCT/F系列芯片的区别1、LS是低功耗肖特基,HC是高速COMS。

LS的速度比HC略快。

HCT输入输出与LS兼容,但是功耗低;F是高速肖特基电路;2、LS是TTL电平,HC是COMS电平。

3、LS输入开路为高电平,HC输入不允许开路,hc 一般都要求有上下拉电阻来确定输入端无效时的电平。

LS 却没有这个要求4、LS输出下拉强上拉弱,HC上拉下拉相同。

5、工作电压不同,LS只能用5V,而HC一般为2V到6V;而HCT的工作电压一般为4.5V~5.5V。

6、电平不同。

LS是TTL电平,其低电平和高电平分别为0.8和V2.4,而CMOS在工作电压为5V时分别为0.3V和3.6V,所以CMOS 可以驱动TTL,但反过来是不行的7、驱动能力不同,LS一般高电平的驱动能力为5mA,低电平为20mA;而CMOS的高低电平均为5mA;8、CMOS器件抗静电能力差,易发生栓锁问题,所以CMOS的输入脚不能直接接电源。

74系列集成电路大致可分为6大类:. 74××(标准型);.74LS××(低功耗肖特基);.74S××(肖特基);.74ALS××(先进低功耗肖特基);.74AS××(先进肖特基);.74F××(高速)。

近年来还出现了高速CMOS电路的74系列,该系列可分为3大类:. HC为COMS工作电平;. HCT为TTL工作电平,可与74LS系列互换使用;. HCU适用于无缓冲级的CMOS电路。

这9种74系列产品,只要后边的标号相同,其逻辑功能和管脚排列就相同。

根据不同的条件和要求可选择不同类型的74系列产品,比如电路的供电电压为3V就应选择74HC系列的产品系列电平典型传输延迟ns 最大驱动电流(-Ioh/Lol)mAAHC CMOS 8.5 -8/8AHCT COMS/TTL 8.5 -8/8HC COMS 25 -8/8HCT COMS/TTL 25 -8/8ACT COMS/TTL 10 -24/24F TTL 6.5 -15/64ALS TTL 10 -15/64LS TTL 18 -15/24LVCACSLC注:同型号的74系列、74HC系列、74LS系列芯片,逻辑功能上是一样的。

六脚电源芯片引脚功能

六脚电源芯片引脚功能

六脚电源芯片是一种常见的电源管理芯片,它主要用于提供电源管理功能以保护电路和电子设备。

六脚电源芯片的引脚功能如下:

1. VIN引脚:VIN引脚是电源输入引脚,用于接入电源输入。

该引脚通常连接到电源轨上,例如电池或外部电源。

2. GND引脚:GND引脚是地引脚,用于连接到电路的地节点。

通常,GND引脚与VIN引脚之间应具有低阻抗路径,以确保

电流的返回路径。

3. VOUT引脚:VOUT引脚是电源输出引脚,用于提供电路所需的稳定电压。

该引脚经过稳压电路处理,以确保输出电压稳定在预定范围内。

4. EN引脚:EN引脚是使能引脚,用于控制芯片的启用或禁用。

当EN引脚保持高电平时,芯片处于启用状态;当EN引

脚保持低电平时,芯片处于禁用状态。

5. PG引脚:PG引脚是电源好引脚,用于指示电源输出是否正常。

当输出电压在合理范围内时,PG引脚会产生一个高电平

信号,否则会产生一个低电平信号。

6. BIAS引脚:BIAS引脚是芯片的参考电压引脚,用于提供其他电路模块所需的参考电压。

通常情况下,BIAS引脚需要外

部连接一个适当的电压源。

六脚电源芯片的引脚功能在不同的芯片上可能会有所差异,具体功能取决于芯片的设计和厂商的设定。

但总体来说,这些引脚在电源管理中起着关键的作用,用于保证电路的稳定工作和电源的有效管理。

为了正确使用六脚电源芯片,用户需要仔细阅读芯片的数据手册,并根据实际需求正确连接每个引脚。

此外,还需要注意芯片的额定和限制条件,以确保芯片能够在规定的环境下安全稳定地工作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SN 芯片引脚功能;**************************************************************************S N8P1602B引脚;▲ 说明引脚名 类型 说 明VDD, VSS P ;▲ 电源输入引脚, 建议在VDD 与 VSS 之间接一个0.1μF 的旁路电容RST/VPP I,PR ST:;▲ 系统复位输入端,施密特结构,低电平触发,通常保持高电平.V PP:;▲ OTP ROM 编程引脚XIN I ;▲ 外部振荡器输入端,RC 模式的输入端XOUT/P1.4 I/O ;▲ 外部振荡器输出端,在RC 模式中为基本输入输出功能引脚(P1.4),无上拉电阻。

P0.0/INT0 I ;▲ Port 0.0/INT0 触发引脚(施密特结构),内置上拉电阻。

P1.0~P1.4 I/O ;▲ 输入/输出端,内置上拉电阻。

P2.0~P2.7 I/O ;▲ 输入/输出端,内置上拉电阻。

;**********************************************************************1702A--03A1.5 引脚说明P IN 类型 ;▲ 说 明VDD, VSS P ;▲ 数字电路电源输入端R ST/VPP I RST:;▲ 系统复位输入端,施密特结构,低电平触发,通常保持高电平.V PP:;▲ OTP ROM 编程引脚XIN, XOUT I, O ;▲ 外部振荡器引脚(RC 模式中为XIN.)P0.0 / INT0 I ;▲ P 0.0 / INT0 触发引脚 (施密特结构) ,内置上拉电阻P1.0 ~ P1.1 I/O ;▲ P1.0~P1.1 输入/输出引脚,内置上拉电阻P4.0 ~ P4.3 I/O ;▲ P4.0~P4.3 输入/输出引脚,内置上拉电阻P5.0~P5.2, P5.5 I/O ;▲ P5.0~P5.2, P5.5 输入/输出引脚,内置上拉电阻P5.3 / BZ1 / PWM1 I/O ;▲ P5.3 输入/输出引脚,Buzzer 或PWM1 输出端,内置上拉电阻P5.4 / BZ0 / PWM0 I/O ;▲ P5.4 输入/输出引脚,Buzzer 或PWM0 输出端,内置上拉电阻AVREFH I ;▲ A/D 转换模拟参考电压高电平输入端AIN0 ~ AIN3 I ;▲ A/D 转换输入通道;**********************************************************************1702----1708:1.8 引脚说明引脚名称 类型;▲ 说 明VDD, VSS P ;▲ 数字电路电源输入端AVDD, AVSS P ;▲ 模拟电路电源输入端VPP/VDD P ;▲ OTP ROM 编程引脚,一般接到VDDRST I ;▲ 系统复位输入端,施密特结构,低电平触发,通常保持高电平XIN, XOUT I,O ;▲ 外部振荡器引脚(RC 模式中为XIN)P0.0 / INT0 I ;▲ Port 0.0 / INT0 触发引脚 (施密特结构),内置上拉电阻P0.1 / INT1 I ;▲ Port 0.1 / INT1 触发引脚 (施密特结构),内置上拉电阻P0.2 / INT2 I ;▲ Port 0.2 / INT2 触发引脚 (施密特结构),内置上拉电阻P1.0 ~ P1.5 I/O ;▲ Port 1.0~Port 1.5 输入/输出引脚,内置上拉电阻P2.0 ~ P2.7 I/O ;▲ Port 2.0~Port 2.7 输入/输出引脚,内置上拉电阻P4.0 ~ P4.7 I/O ;▲ Port 4.0~Port 4.7 输入/输出引脚,内置上拉电阻P5.0 / SCK I/O ;▲ Port 5.0 输入/输出引脚/SIO 时钟输入输出端,内置上拉电阻P5.1 / SI I/O ;▲ Port 5.1 输入/输出引脚/SIO 数据输入端,内置上拉电阻P5.2 / SO I/O ;▲ Port 5.2 输入/输出引脚/SIO 的数据输出端,内置上拉电阻P5.3 / BZ1 / PWM1 I/O ;▲ Port 5.3 输入/输出引脚/Buzzer 或PWM1 输出端,内置上拉电阻P5.4 / BZ0 / PWM0 I/O ;▲ Port 5.4 输入/输出引脚/Buzzer 或PWM0 输出端,内置上拉电阻P5.5 ~ P5.7 I/O ;▲ Port 5.5~Port 5.7 输入/输出引脚,内置上拉电阻AVREFH I ;▲ A/D 转换模拟参考电压高电平输入端AIN0 ~ AIN7 I ;▲ A/D 转换输入通道DAO O DAC ;▲ 信号输出端;**********************************************************************2501B 引脚功能说明:引脚 类型 ;▲ 说明V DD, VSS P 数字电路电源输入端P1.1/RST/VPP I, P;▲ P1.1:禁止外部复位的情况下仅作输入引脚 (施密特触发器)P1.1 无内置上拉电阻.具有唤醒功能.R ST:;▲ 系统复位输入引脚,施密特触发器结构,低电平触发,一般处于高电平状态V PP:;▲ OTP 烧录引脚P1.3/XIN I/O;▲ P1.3 输入/输出引脚,输入时为施密特触发器结构.内置上拉电阻.具有唤醒功能.X IN:;▲ 外部振荡器(晶振或RC)有效时作为振荡器输入引脚P1.2/XOUT I/O;▲ P1.2 输入/输出引脚,输入引脚为施密特触发器结构,内置上拉电阻.唤醒功能.X OUT:;▲ 外部晶振模式时作为振荡器输出引脚P0.0/INT0 I/O;▲ P0.0 输入/输出引脚,输入引脚为施密特触发器结构.内置上拉电阻.具有唤醒功能.INT0 触发引脚(施密特触发器).TC0 事件计数器时钟输入引脚.P1.0 I/O ;▲ P1.0 输入/输出引脚,漏极开路输入引脚为施密特触发器结构.内置上拉电阻. P2 [5:0] I/O ;▲ 输入/输出引脚,输入引脚为施密特触发器结构.内置上拉电阻.P5.4/BZ0.PWM0 I/O;▲ P5.4 输入/输出引脚,输入引脚为施密特触发器结构.内置上拉电阻. T C0 2 分频输出引脚,PWM 和蜂鸣器引脚.;***********************************************************************2602B 1.4 引脚说明引脚名 类型 描述VDD, VSS P ;▲ 数字电路电源输入端P1.5/RST/VPP I, PP1.5:;▲ 外部复位无效时仅可作输入口使用 (施密特触发器结构),P1.5无内置上拉电阻,具有唤醒功能R ST:;▲ 系统复位输入端,施密特触发器结构,低电平有效,通常保持高电平V PP:;▲ OTP 烧录引脚XIN I/O ;▲ 外部振荡信号输入端P1.4/XOUT I/O;▲ 输入/输出端,作输入端使用时为施密特触发器结构,具有唤醒功能, XOUT: ;▲ 采用外部振荡器的时晶振输出端P0.0/INT0 I/O;▲ 输入/输出端,作输入端使用时为施密特触发器结构,具有唤醒功能,内置上拉电阻,INT0 触发端 (施密特触发结构),TC0 事件计数信号输入端P1.0 I/O ;▲ 输入/输出端,漏极开路,作输入端使用时为施密特触发结构,内置上拉电阻P1 [3:1] I/O ;▲ 输入/输出端,作输入端使用时为施密特触发结构,内置上拉电阻P5 [7:0] I/O ;▲ 输入/输出端,作输入端使用时为施密特触发结构,内置上拉电阻P5.4/BZ0.PWM0 I/O;▲ 输入/输出端,作输入端使用时为施密特触发结构,内置上拉电阻,蜂鸣器及PWM 输出端;*************************************************************************2604B 引脚说明引脚名称 类型 ;▲ 说明VDD, VSS P ;▲ 数字电路的电源输入引脚P0.2/RST/VPP I, P;▲ P0.2:禁止外部复位功能时为单向输入引脚(施密特结构)/无内置上拉电阻。

RST:系统复位输入引脚,施密特结构,低电平触发,通常保持高电平。

VPP:OTPR OM 编程引脚。

XIN I ;▲ 选择外部振荡器(晶体或RC)时为振荡器输入引脚。

XOUT/Fcpu I/O ;▲ XOUT:选择外部晶体振荡器时为振荡器输出引脚.Fcpu:使能外部RC 模式时为信号输出引脚。

P0.0/INT0 I/O ;▲ P0.0:双向输入输出引脚,施密特结构(作输入时)。

内置上拉电阻。

I NT0 触发引脚(施密特结构)P0.1/INT1 I/O;▲ P0.1:双向输入输出引脚,施密特结构(作输入时)。

内置上拉电阻。

INT1 触发引脚(施密特结构),TC1 事件计数器时钟输入引脚。

P1.0~P1.1 I/O ;▲ P1.0, P1.1:双向输入输出引脚/漏极开路引脚/施密特结构(作输入时)/内置上拉电阻。

P1.2~P1.7 I/O P1.2~P1.7:双向输入输出引脚/施密特结构(作输入时)/内置上拉电阻。

P2.0~P2.7 I/O ;▲ 双向输入输出引脚/施密特结构(作输入时)/内置上拉电阻。

P5.0~P5.2, P5.4 I/O ;▲ P5:双向输入输出引脚/施密特结构(作输入时)/内置上拉电阻。

P5.3/BZ1/PWM1 I/O ;▲ P5.3:双向输入输出引脚/施密特结构(作输入时)/内置上拉电阻。

T C1 /2 :Buzzer 或PWM 信号输出引脚。

;***************************************************************************2608B 引脚说明:引脚名称 类型 ;▲ 说明VDD, VSS P ;▲ 数字电路的电源输入引脚P4.7/RST/VPP I, P;▲ P4.7:禁止外部复位功能时为单向输入引脚(施密特结构)P4.7 无内置上拉电阻,RST:系统复位输入引脚,施密特结构,低电平触发,通常保持高电平,VPP:OTP 编程引脚XIN I ;▲ 选择外部振荡器(晶体或RC)时为振荡器的输入引脚X OUT/Fcpu I/O XOUT:;▲ 选择外部晶体振荡器时为振荡器的输出引脚.Fcpu:使能外部RC 模式时为信号输出引脚P0.0/INT0 I/O;▲ P0.0:双向输入输出引脚,施密特结构(作输入时)内置上拉电阻,INT0 触发引脚(施密特结构),P0.1/INT1 I/O;▲ P0.1:双向输入输出引脚,施密特结构(作输入时),内置上拉电阻,INT1 触发引脚(施密特结构),TC1 事件计数器时钟输入引脚P0.2~P0.7 I/O ;▲ 双向输入输出引脚,施密特结构(作输入时)内置上拉电阻P1.0~P1.1 I/O ;▲ 双向输入输出引脚,施密特结构(作输入时)内置上拉电阻P1.2~P1.7 I/O ;▲ 双向输入输出引脚,施密特结构(作输入时)内置上拉电阻P2.0~P2.7 I/O ;▲ 双向输入输出引脚,施密特结构(作输入时)内置上拉电阻P4.0~P4.6 I/O ;▲ 双向输入输出引脚,施密特结构(作输入时)内置上拉电阻P5.0~P5.2,P5.4~P5.7 I/O ;▲ 双向输入输出引脚,施密特结构(作输入时)内置上拉电阻P5.3/BZ1/PWM1 I/O;▲ P5.3:双向输入输出引脚,施密特结构(作输入时)内置上拉电阻,T C1/2:Buzzer 或PWM1 信号输出引脚;***********************************************************************2612_13 引脚说明引脚名称 类型 ;▲ 说明VDD, VSS P ;▲ 数字电路电源输入P1.5/RST/VPP I, P;▲ P1.5:禁止外部复位功能时为单向输入引脚(施密特触发结构),无内置上拉电阻,具有唤醒功能,RST:系统复位引脚,施密特触发结构,低电平有效,通常保持高电平,VPP:OTP 烧录引脚P1.6/XIN I/O;▲ P1.6:双向输入输出引脚,输入模式时为施密特触发结构,内置上拉电阻,具有唤醒功能,允许外部振荡器(石英或RC)时为振荡器输入引脚P1.4/XOUT I/O;▲ P1.4:双向输入输出引脚,输入模式时为施密特触发结构,内置上拉电阻,具有唤醒功能,XOUT:允许外部晶振时为振荡器输出引脚P0.0/INT0 I/O;▲ P0.0:双向输入输出引脚,输入模式时为施密特触发结构,内置上拉电阻,具有唤醒功能,INT0 触发引脚(施密特结构),TC0 事件计数时钟输入引脚P0.1/INT1 I/O;▲ P0.1:双向输入输出引脚,输入模式时为施密特触发结构,内置上拉电阻,具有唤醒功能,INT1 触发引脚(施密特结构)P1.0 I/O P1.0:;▲ 双向输入输出引脚,漏极开路,输入模式时为施密特触发结构,内置上拉电阻,具有唤醒功能P1 [3:1], P1.7 I/O ;▲ 双向输入输出引脚,输入模式时为施密特触发结构,内置上拉电阻,具有唤醒功能.P5 [7:0] I/O 双向输入输出引脚,输入模式为施密特触发结构,内置上拉电阻P5.4/BZ0/PWM0 I/O;▲ P5.4:双向输入输出引脚,输入模式时为施密特触发结构,内置上拉电阻,Buzzer 和PWM0 的TC0/2 信号输出引脚;***********************************************************************2624 引脚描述引脚名称类型 描述VDD, VSS P ;▲ 供电输入引脚为了数字电路.P0.2/RST/VPP i, P ;▲ P0.2: 仅作输入引脚(施密特触发) 如果取消外部重置功能. P0.2 无内部上拉电阻. P0.2 是仅作输入引脚不用上拉电阻 在P0.2 模式. 增加这100Ω外部电阻在P0.2, 当它是设定到是输入引脚. 内建唤醒功能. RST: 系统重置输入引脚. 施密特触发结构,低的活动的, 正常逗留到“高”. VPP: OTP 编程序引脚. XIN I 振荡器输入引脚当外部振荡器 启动(晶体和RC).XOUT/Fcpu I/O;▲ XOUT: 振荡器输出引脚当外部晶体启动. Fcpu: 信号输出引脚当外部RC 模式启动.P0.0/INT0 I/O;▲ 端口0.0 双向引脚. 施密特触发结构作输入模式时. 内建上拉电阻. 内建唤醒功能. INT0 触发引脚(施密特触发).P0.1/INT1 I/O;▲ 端口0.1 双向引脚. 施密特触发结构作输入模式时. 内建上拉电阻. 内建唤醒功能. INT1 触发引脚(施密特触发). TC1 事件计数器时钟输入引脚.P1.0~P1.1 I/O;▲ 端口1.0, P1.1 双向引脚和开漏引脚. 施密特触发结构作输入时. 内建上拉电阻.P1.2~P1.7 I/O;▲ 端口1.2~P1.7 双向引脚. 施密特触发结构作输入模式时. 内建上拉电阻.P2.0~P2.7 I/O;▲ 双向引脚. 施密特触发结构作输入模式时. 内建上拉电阻.P5.0~P5.2, P5.4 I/O;▲ 端口5 双向引脚. 施密特触发结构作输入模式时. 内建上拉电阻.P5.3/BZ1/PWM1 I/O;▲ 端口5.3 双向引脚. 施密特触发结构作输入模式时. 内建上拉电阻. TC1 ÷ 2 信号输出引脚为了buzzer 或PWM1 输出引脚.;***********************************************************************2308 引脚描述引脚名称类型 描述VDD, VSS P ;▲ 供电输入引脚为了数字电路. VDD1 P 连接到VDD 当P3.0~P3.7 I/O启动.连接到VLCD 当SEG24~SEG31 启动.VLCD P ;▲ LCD 供电V1, V2 P ;▲ LVD 偏斜电压,在LCD R 类型模式: 连接这外部电阻到调整VLCD 电压.C1, C2 I ;▲ 连接电容器为了内部VLCD 充电泵.RST/VPP/P0.2 i, P ;▲ P0.2: 仅作输入引脚(施密特触发) 如果取消外部重置功能. P0.2 无内部上拉电阻,内建唤醒功能. RST: 系统重置输入引脚. 施密特触发结构, 低的活动的, 正常操作必须逗留到“高”. VPP: OTP 编程序引脚.XIN I ;▲ 振荡器输入引脚当外部振荡器 启动(晶体和RC).XOUT/P0.3 I/O;▲ 端口0.3 双向引脚. 施密特触发结构作输入模式时. 内建上拉电阻. 内建唤醒功能.XOUT: ;▲ 振荡器输出引脚当外部晶体启动.LXIN I ;▲ 外部低速振荡器输入引脚(32768Hz 晶体或RC).LXOUT O ;▲ 外部低速振荡器输出引脚.P0.0/INT0 I/O;▲ 端口0.0 双向引脚. 施密特触发结构作输入模式时. 内建上拉电阻. 内建唤醒功能. INT0 触发引脚(施密特触发). TC0 事件计数器时钟输入引脚.P0.1/T1IN I/O;▲ 端口0.1 双向引脚. 施密特触发结构作输入模式时. 内建上拉电阻. 内建唤醒功能. T1 事件计数器时钟输入引脚.P1 [6:0] I/O;▲ 端口1 双向引脚. 施密特触发结构作输入模式时. 内建上拉电阻. 内建唤醒功能.P3 [7:0] I/O;▲ 端口3 双向引脚在P3SEG=1. 施密特触发结构作输入模式时. 内建上拉电阻.上电后或重置,P3 预设的状态如输入低的.P5.0/ RFC0 I/O;▲ 端口5.0 双向引脚. 施密特触发结构作输入模式时. 内建上拉电阻.R FC0 是RFC 通道0 输入引脚.P5.1/RFC1 I/O;▲ 端口5.1 双向引脚. 施密特触发结构作输入模式时. 内建上拉电阻.R FC1 是RFC 通道1 输入引脚.P5.2/RFC2 I/O;▲ 端口5.2 双向引脚. 施密特触发结构作输入模式时. 内建上拉电阻. RFC2 是RFC 通道2 输入引脚.P5.3/RFCI I/O;▲ 端口5.3 双向引脚. 施密特触发结构作输入模式时. 内建上拉电阻. RFCI 是RFC 回馈输入引脚.P5.4/BZ0/PWM0 I/O;▲ 端口5.4 双向引脚. 施密特触发结构作输入模式时. 内建上拉电阻. T C1 ÷ 2 信号输出引脚为了buzzer 或PWM 输出引脚.P5.5/RFCOUT I/O;▲ 双向引脚. 施密特触发结构作输入模式时. 内建上拉电阻. RFCOUT 是R FC 输出引脚.COM0~COM3 O ;▲ LCD 驱动 COM 引脚SEG0~SEG31 O ;▲ LCD 驱动 SEG 引脚;***********************************************************************2617 引脚描述引脚名称类型 描述VDD, VSS P ;▲ 供电输入引脚 为了数字电路.RST i, P ;▲ RST 是系统外部重置输入引脚. 施密特触发结构, 活动的“低”, 正常逗留到“高”.XIN I ;▲ XIN: 振荡器输入引脚.XOUT/Fcpu O ;▲ XOUT: 振荡器输出引脚. Fpcu: 系统时钟输出引脚如RC 模式.P0.0/INT0 I/O ;▲ P0.0: 端口0 双向引脚. 施密特触发结构和内建上拉电阻作输入时.建造唤醒功能. INT0: 外部中断输入引脚. TC0 事件计数器输入引脚.P0[2:1]/INT[2:1] I/O ;▲ P0[2:1]: 端口0 双向引脚. 施密特触发结构和内建上拉电阻作输入时. 建造唤醒功能. INT[2:1]: 外部中断输入引脚.P0[4:3] I/O ;▲ P0.3, P0.4: 端口0 双向引脚. 施密特触发结构和内建上拉电阻作输入时.建造唤醒功能.P1[7:0] I/O ;▲ P1: 端口1 双向引脚. 施密特触发结构和内建上拉电阻作输入时. 建造唤醒功能被控制经由P1W 寄存器.P2[7:0] I/O ;▲ P2: 端口2 双向引脚. 施密特触发结构和内建上拉电阻作输入时.P4[7:0] I/O ;▲ P4: 端口4 双向引脚. 施密特触发结构和内建上拉电阻作输入时.P5.0/SCK I/O ;▲ P5.0: 端口5.0 双向引脚. 施密特触发结构和内建上拉电阻作输入时.S IO: SIO 时钟引脚.P5.1/SI I/O ;▲ P5.1: 端口5.1 双向引脚. 施密特触发结构和内建上拉电阻作输入时.S I: SIO 资料输入引脚.P5.2/如此I/O ;▲ P5.2: 端口5.1 双向引脚. 施密特触发结构和内建上拉电阻作输入时. 如此: SIO 资料输出引脚. 可编程开漏类型被控制经由P1OC 寄存器.P5[7:3] I/O ;▲ P5: 端口5 双向引脚. 施密特触发结构和内建上拉电阻作输入时.;***********************************************************************2704--2708:引脚说明引脚名称 类型;▲ 说明P0 [2:0] / INT [2:0] I/O P0 [0:2] / INT [0:2]:;▲ 双向输入输出引脚/唤醒功能/内置上拉电阻/外部中断/施密特触发P1 [7:0] I/O P1 [7:0]:;▲ 双向输入输出引脚/唤醒功能/内置上拉电阻/施密特触发P1 [1:0]:;▲ 可设置为漏极开路P2 [7:0] I/O P2 [7:0] :;▲ 双向输入输出引脚/内置上拉电阻/施密特触发P3.0 I/O ;▲ 双向输入输出引脚/内置上拉电阻/施密特触发P4 [7:0] /AIN [7:0] I/O :;▲ 双向输入输出引脚/内置上拉电阻/ADC 输入端/施密特触发P5 [7:0] I/O :;▲ 双向输入输出引脚/内置上拉电阻/施密特触发P5.0/SCK,P5.1/SI,P5.2/SO,P5.2 ;▲ 在SIO 从动模式中可设为漏极开路,P5.4:PWM0/BZ0,P5.3:PWM1/BZ1AVREFH I ;▲ ADC 参考电压高电平输入端AVREFL I ;▲ ADC 参考电压低电平输入端DAO O ;▲ DAC 信号输出端R ST/VPP I/P RST:;▲ 外部复位输入端,通常保持高电平V PP:;▲ OTP 编程引脚XIN I ;▲ 外部振荡器输入端 / 外部RC 振荡器输入端XOUT/Fcpu O ;▲ 外部振荡器输出端 / RC 模式时为Fcpu 时钟输出端VDD, VSS P ;▲ 电源输入端;**********************************************************************2714_15 引脚说明引脚名称 类型;▲ 说明P0 [1:0] / INT [1:0] I ;▲ P0 [1:0]:单向输入引脚/唤醒功能引脚/上拉电阻/施密特触发,INT [1:0]:外部中断P0 .2 I ;▲ P0.2 单向输入引脚/上拉电阻/施密特触发P2 [7:0] I/O ;▲ P2 [7:0]双向输入输出引脚/上拉电阻/施密特触发P4 [7:0] / AIN [7:0] I/O ;▲ 双向输入输出引脚/上拉电阻/ADC 输入/施密特触发P5 [5:0] I/O ;▲ 双向输入输出引脚/上拉电阻/施密特触发,P5.4:PWM0/BZ0,P5.3:PWM1/BZ1AVREFH I ;▲ ADC 参考电压输入端DAO O ;▲ DAC 信号输出端P0.3/RST/VPP I/P ;▲ P0.3:施密特触发/唤醒功能引脚/没有上拉电阻/RC 模式,RST:外部复位,低电平有效,VPP:OTP 编程引脚XIN I ;▲ 外部振荡器输入引脚/外部RC 振荡器输入XOUT/P5.6 I/O ;▲ XOUT:外部振荡器输出引脚,P5.6:双向输入输出/上拉电阻/在RC 模式中施密特触发VDD, VSS P ;▲ 电源输;**********************************************************************27142_142 引脚描述:引脚名称类型;▲ 描述P0 [1:0] / INT [1:0] I ;▲ P0 [1:0]: 仅作输入引脚/唤醒/上拉电阻/施密特触发输入I NT [1:0]: 外部中断P0 .2 I ;▲ P0.2: 仅作输入引脚/唤醒/上拉电阻/施密特触发输入P2 [7:0] I/O ;▲ P2 [7:0] 双向引脚/上拉电阻/施密特触发输入P4 [7:0] / AIN [7:0] I/O ;▲ 双向引脚/上拉电阻 /ADC 输入/ 不用施密特触发输入P5 [5:0] I/O ;▲ 双向引脚/上拉电阻/施密特触发输入,P5.4: PWM0/BZ0, P5.3: PWM1/BZ1 AVREFH I ;▲ ADC 最高的参考电压输入,(注意:这ADC 参考电压(AVREFH) 之SN8P27142 和S N8P27143 是VDD.)DAO O ;▲ 电流类型DAC 输出P0.3/RST/VPP I /P ;▲ P0.3: 施密特触发输入引脚/ 不是上拉电阻, 无唤醒功能/ 在RC 模式,P0.3 是仅作输入引脚不用上拉电阻在P0.3 模式. 增加这100 Ω外部电阻在P0.3, 当它是设定到是输入引脚. RST: 外部重置, 活动的“低” ,VPP: OTP 编程序引脚XIN I ;▲ 外部振荡器输入引脚. / 外部RC 振荡器输入XOUT/P5.6 I/O ;▲ XOUT: 外部振荡器输出引脚. P5.6: 双向引脚/上拉电阻/施密特触发输入在RC 模式VDD, VSS P ;▲ 供电引脚.;**********************************************************************;**********************************************************************。