西南科技大学数字电子技术期末考试试题及答案

数字电子技术期末复习试卷及答案(四套)

数字电子技术基础试卷(本科)及参考答案试卷一一、(20分)选择填空。

从每个小题的四个选项中选出一个正确答案,并将其编号填入该题后的括号中。

1.十进制数3.625的二进制数和8421BCD码分别为()A.11.11 和11.001 B.11.101 和0011.1C.11.01 和11.1 D.11.101 和11.1012.下列几种说法中错误的是()A.任何逻辑函数都可以用卡诺图表示。

B.逻辑函数的卡诺图是唯一的。

C.同一个卡诺图化简结果可能不是唯一的。

D.卡诺图中1的个数和0的个数相同。

3.和TTL电路相比,CMOS电路最突出的优点在于()A.可靠性高B.抗干扰能力强C.速度快D.功耗低4.为了把串行输入的数据转换为并行输出的数据,可以使用()A.寄存器B.移位寄存器C.计数器D.存储器5.单稳态触发器的输出脉冲的宽度取决于()A.触发脉冲的宽度B.触发脉冲的幅度C.电路本身的电容、电阻的参数D.电源电压的数值6.为了提高多谐振荡器频率的稳定性,最有效的方法是()A.提高电容、电阻的精度B.提高电源的稳定度C.采用石英晶体振荡器C.保持环境温度不变7.已知时钟脉冲频率为f cp,欲得到频率为0.2f cp的矩形波应采用()A.五进制计数器B.五位二进制计数器C.单稳态触发器C.多谐振荡器8.在图1-8用555定时器组成的施密特触发电路中,它的回差电压等于()A.5V B.2VC.4V D.3V图1-8二、(12分)已知输入信号A、B、C的波形,试画出图2所示各电路输出(L1、L2、L3)的波形。

设触发器的初态为0。

图2三、(10分)如图3所示,为检测水箱的液位,在A 、B 、C 、三个地方安置了三个水位检测元件,当水面低于检测元件时,检测元件输出低电平,水面高于检测元件时,检测元件输出高电平。

试用与非门设计一个水位状态显示电路,要求:当水面在A 、B 之间的正常状态时,仅绿灯G 亮;水面在B 、C 间或A 以上的异常状态时,仅黄Y 灯亮;水面在C 以下的危险状态时,仅红灯R 亮。

数字电子技术期末考试试题

数字电子技术期末考试试题期末考试试题课程名称 《数字电子技术》 适用专业自动化、测控 考试时间 ( 120 )分钟一、 填空题(22分每空2分)1、=⊕0A , =⊕1A 。

2、JK 触发器的特性方程为: 。

3、单稳态触发器中,两个状态一个为 态,另一个为 态.多谐振荡器两个状态都为 态, 施密特触发器两个状态都为 态.4、组合逻辑电路的输出仅仅只与该时刻的 有关, 而与 无关。

5、某数/模转换器的输入为8位二进制数字信号(D 7~D 0),输出为0~25.5V 的模拟电压。

若数字信号的最低位是“1”其余各位是“0”,则输出的模拟电压为 。

6、一个四选一数据选择器,其地址输入端有 个。

二、 化简题(15分 每小题5分)用卡诺图化简逻辑函数,必须在卡诺图上画出卡诺圈1) Y (A,B,C,D )=∑m (0,1,2,3,4,5,6,7,13,15)2)∑∑+=)11,10,9,3,2,1()15,14,13,0(),,,(d m D C B A L 利用代数法化简逻辑函数,必须写出化简过程3)__________________________________________________)(),,(B A B A ABC B A C B A F +++=三、 画图题(10分 每题5分)据输入波形画输出波形或状态端波形(触发器的初始状态为0). 1、2、四、 分析题(17分)1、分析下图,并写出输出逻辑关系表达式,要有分析过程(6分)2、电路如图所示,分析该电路,画出完全的时序图,并说明电路的逻辑功能,要有分析过程(11分)五、设计题(28分)1、用红、黄、绿三个指示灯表示三台设备的工作情况:绿灯亮表示全部正常;红灯亮表示有一台不正常;黄灯亮表示两台不正常;红、黄灯全亮表示三台都不正常。

列出控制电路真值表,要求用74LS138和适当的与非门实现此电路(20分)2、中规模同步四位二进制计数器74LS161的功能表见附表所示;请用反馈预置回零法设计一个六进制加法计数器。

数字电子技术期末考试试题含答案

.《数字电子技术》考试一试卷(第一套)课程号2904025035考试时间100分钟合用专业年级(方向):应用物理、电信科技2010级考试方式及要求:闭卷笔试题号一二三四五六七总分得分阅卷人(注:集成电路CD4532、74HC138、74HC151的功能见附表)一、填空题(共28分)1、(2分)()H=()D=()8421BCD。

2、(2分)逻辑函数L=+A+B+C+D=(1)。

3、(2分)由传输门组成的电路以以下图所示,当A=0时,输出L=B。

4、(2分)三态门可能输出的三种状态是低电平、高电平易高阻态_。

5、(3分)A/D变换器一般要经过_采样__、保持、量化和__编码__这4个步骤,A/D变换器的变换速度主要取决于变换种类。

对双积分型A/D变换器、并行比较型A/D变换器和逐次比较型A/D变换器的相对速度进行比较,变换速度最快的是_并行比较型A/D变换器__。

.西南石油大学试卷第2页共11页6、(2分)集成优先编码器CD4532(功能表见后)正常接电源和地,且 待编码信号输入端I 0 2 6 7,输入使能端 EI=1 ,其他输入端为 , =I =I =I =10 其输出Y 21Y 0为 111。

Y7、(3分)集成数据选择器74HC151组成的电路以以下图所示,则其输出Y=ABCABCABC 。

(注:不需化简)Y0 ABE YS2S174HC151CS0D0D1 D2D3D4 D5D6D70 18、(3分)某PLA 电路以以下图所示,其输出逻辑函数表达式 X=ABC A BC A BC 。

ABC×× ×× ×× × ×××× ×××××××X Y9、(2分)某单极性输出的 8位D/A 变换器正常工作,当输入数字量为 (10101010)B 时,其输出电压为,当输入数字量为(10101100) 时,其输出电压为V 。

《数字电子技术》期末考试试卷附答案

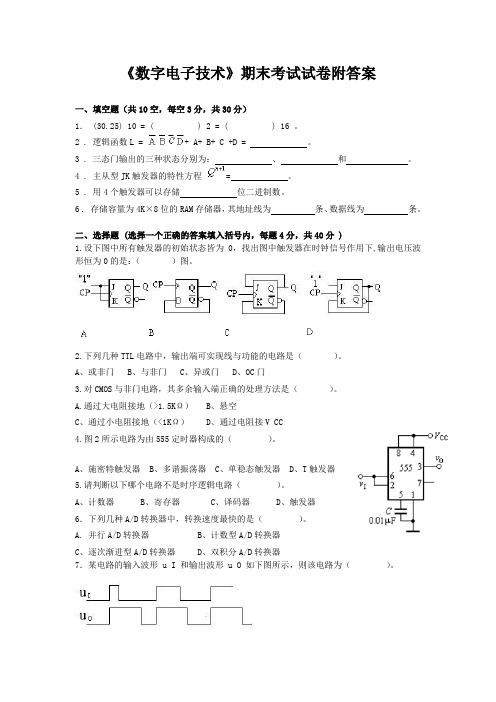

《数字电子技术》期末考试试卷附答案一、填空题(共10空,每空3分,共30分)1. (30.25) 10 = ( ) 2 = ( ) 16 。

2 . 逻辑函数L = + A+ B+ C +D = 。

3 . 三态门输出的三种状态分别为:、和。

4 . 主从型JK触发器的特性方程= 。

5 . 用4个触发器可以存储位二进制数。

6 . 存储容量为4K×8位的RAM存储器,其地址线为条、数据线为条。

二、选择题 (选择一个正确的答案填入括号内,每题4分,共40分 )1.设下图中所有触发器的初始状态皆为0,找出图中触发器在时钟信号作用下,输出电压波形恒为0的是:()图。

2.下列几种TTL电路中,输出端可实现线与功能的电路是()。

A、或非门B、与非门C、异或门D、OC门3.对CMOS与非门电路,其多余输入端正确的处理方法是()。

A.通过大电阻接地(>1.5KΩ) B、悬空C、通过小电阻接地(<1KΩ)D、通过电阻接V CC4.图2所示电路为由555定时器构成的()。

A、施密特触发器B、多谐振荡器C、单稳态触发器D、T触发器5.请判断以下哪个电路不是时序逻辑电路()。

A、计数器B、寄存器C、译码器D、触发器6.下列几种A/D转换器中,转换速度最快的是()。

A. 并行A/D转换器 B、计数型A/D转换器C、逐次渐进型A/D转换器D、双积分A/D转换器7.某电路的输入波形 u I 和输出波形 u O 如下图所示,则该电路为()。

A、施密特触发器B、反相器C、单稳态触发器D、JK触发器8.要将方波脉冲的周期扩展10倍,可采用()。

A. 10级施密特触发器 B、10位二进制计数器 C、十进制计数器 D、10位D/A转换器9、已知逻辑函数与其相等的函数为()。

A、 B、 C、 D、10、一个数据选择器的地址输入端有3个时,最多可以有()个数据信号输出。

A、4B、6C、8D、16三、分析下列电路。

(30分)1、写出如图1所示电路的真值表及最简逻辑表达式。

数电期末考试题及答案

数电期末考试题及答案一、单项选择题(每题2分,共20分)1. 在数字电路中,最基本的逻辑运算是()。

A. 与运算B. 或运算C. 非运算D. 异或运算答案:C2. 一个触发器可以存储()位二进制信息。

A. 1B. 2C. 3D. 4答案:A3. 以下哪个不是组合逻辑电路的特点?()A. 输出只依赖于当前输入B. 输出与输入之间存在时延C. 没有记忆功能D. 任何时刻输出仅由该时刻的输入决定答案:B4. 一个4位二进制计数器可以计数到()。

A. 8B. 16C. 15D. 14答案:B5. 一个D触发器的特点是()。

A. 有两个稳定状态B. 只有一个稳定状态C. 没有稳定状态D. 以上都不是答案:A6. 在数字电路中,以下哪个不是基本的门电路?()。

A. 与门B. 或门C. 非门D. 异或门答案:D7. 一个3线-8线译码器可以译码()种不同的输入。

A. 3B. 8C. 6D. 7答案:B8. 一个8位寄存器可以存储()位二进制数。

A. 8B. 16C. 32D. 64答案:A9. 以下哪个是同步时序电路的特点?()A. 电路的输出仅依赖于当前的输入B. 电路的输出依赖于当前的输入和电路的历史状态C. 电路的输出不依赖于输入D. 电路的输出仅依赖于电路的历史状态答案:B10. 一个JK触发器可以表示()种不同的状态。

A. 1B. 2C. 3D. 4答案:B二、填空题(每题2分,共20分)1. 在数字电路中,一个基本的与门电路有_____个输入端和一个输出端。

答案:22. 一个4位二进制计数器的计数范围是从0到_____。

答案:153. 一个D触发器在时钟信号的上升沿到来时,其输出Q将与输入D保持_____。

答案:一致4. 在数字电路中,一个3线-8线译码器的输出是_____进制的。

答案:二5. 一个8位寄存器可以存储的最大十进制数是_____。

答案:2556. 一个JK触发器在J=0,K=0时,其状态将保持_____。

数字电子技术期末考试试题及答案(试卷一)

、 代入规则 对偶规则 反

演规则

、

。

5、为 了 实 现 高 的 频 率 稳 定 度 , 常 采 用 石英晶体

振荡

器 ; 单 稳 态 触 发 器 受 到 外 触 发 时 进 入 暂稳态 态

6、同步 RS 触发器中 R、S 为 高 电平有效,基本 R、S 触发器中 R、S

为低

电平有效

7、在进行 A/D 转换时,常按下面四个步骤进行, 采样 保持 量化 编

码、

、

、。Βιβλιοθήκη 二、选择题(每题 1 分,共 10 分)

1、有八个触发器的二进制计数器,它们最多有(

)种计数状态。

A、8; B、16; C、256; D、64

2、下列触发器中上升沿触发的是( )。

A、主从 RS 触发器;B、JK 触发器;C、T 触发器;D、D 触发器

3、下式中与非门表达式为( d ),或门表达式为(a )。

数字电子技术期末考试试题及答案(试卷一)

目录

数字电子技术期末考试试题及答案(试卷一) ........................................................................... 1 一、填空题(每空 1 分,共 20 分).............................................................................................2 二、选择题(每题 1 分,共 10 分).............................................................................................2 三、判断(每题 1 分,共 10 分):...............................................................................................3 四、数制转化(每题 2 分,共 10 分):.......................................................................................3 五、逻辑函数化简(每题 5 分,共 10 分):...............................................................................3 六、分析电路:(每题 10 分,共 20 分).....................................................................................4 七、设计电路(共 10 分).............................................................................................................4 试题答案(一)...............................................................................................................................5

期末考试数字电子技术试题及答案..

数字电子技术基础试题(一)一、填空题 : (每空1分,共10分)1. (30.25) 10 = ( ) 2 = ( ) 16 。

2 . 逻辑函数L = + A+ B+ C +D = 。

3 . 三态门输出的三种状态分别为:、和。

4 . 主从型JK触发器的特性方程= 。

5 . 用4个触发器可以存储位二进制数。

6 . 存储容量为4K×8位的RAM存储器,其地址线为条、数据线为条。

二、选择题: (选择一个正确的答案填入括号内,每题3分,共30分 )1.设图1中所有触发器的初始状态皆为0,找出图中触发器在时钟信号作用下,输出电压波形恒为0的是:()图。

图 12.下列几种TTL电路中,输出端可实现线与功能的电路是()。

A、或非门B、与非门C、异或门D、OC门3.对CMOS与非门电路,其多余输入端正确的处理方法是()。

A、通过大电阻接地(>1.5KΩ)B、悬空C、通过小电阻接地(<1KΩ)D、通过电阻接V CC4.图2所示电路为由555定时器构成的()。

A、施密特触发器B、多谐振荡器C、单稳态触发器D、T触发器5.请判断以下哪个电路不是时序逻辑电路()。

图2A、计数器B、寄存器C、译码器D、触发器6.下列几种A/D转换器中,转换速度最快的是()。

图2A、并行A/D转换器B、计数型A/D转换器C、逐次渐进型A/D转换器D、双积分A/D转换器7.某电路的输入波形 u I 和输出波形 u O 如图 3所示,则该电路为()。

图3A、施密特触发器B、反相器C、单稳态触发器D、JK触发器8.要将方波脉冲的周期扩展10倍,可采用()。

A、10级施密特触发器B、10位二进制计数器C、十进制计数器D、10位D/A转换器9、已知逻辑函数与其相等的函数为()。

A、B、C、D、10、一个数据选择器的地址输入端有3个时,最多可以有()个数据信号输出。

A、4B、6C、8D、16三、逻辑函数化简(每题5分,共10分)1、用代数法化简为最简与或式Y= A +2、用卡诺图法化简为最简或与式Y= + C +A D,约束条件:A C + A CD+AB=0四、分析下列电路。

数字电子技术期末试卷含答案

《数字电子技术基础》(第一套)一、填空题:(每空1分,共15分)=+的两种标准形式分别为()、()。

1.逻辑函数Y AB C2.将2004个“1”异或起来得到的结果是()。

3.半导体存储器的结构主要包含三个部分,分别是()、()、()。

4.8位D/A转换器当输入数字量为5v。

若只有最低位为高电平,则输出电压为()v;当输入为,则输出电压为()v。

5.就逐次逼近型和双积分型两种A/D转换器而言,()的抗干扰能力强,()的转换速度快。

6.由555定时器构成的三种电路中,()和()是脉冲的整形电路。

7.与PAL相比,GAL器件有可编程的输出结构,它是通过对()进行编程设定其()的工作模式来实现的,而且由于采用了()的工艺结构,可以重复编程,使它的通用性很好,使用更为方便灵活。

二、根据要求作题:(共15分)1.将逻辑函数P=AB+AC写成“与或非”表达式,并用“集电极开路与非门”来实现。

2.图1、2中电路均由CMOS门电路构成,写出P、Q 的表达式,并画出对应A、B、C的P、Q波形。

三、分析图3所示电路:(10分)1)试写出8选1数据选择器的输出函数式;2)画出A2、A1、A0从000~111连续变化时,Y的波形图;3)说明电路的逻辑功能。

四、设计“一位十进制数”的四舍五入电路(采用8421BCD码)。

要求只设定一个输出,并画出用最少“与非门”实现的逻辑电路图。

(15分)五、已知电路及CP、A的波形如图4(a) (b)所示,设触发器的初态均为“0”,试画出输出端B和C的波形。

(8分)BC六、用T触发器和异或门构成的某种电路如图5(a)所示,在示波器上观察到波形如图5(b)所示。

试问该电路是如何连接的?请在原图上画出正确的连接图,并标明T的取值。

(6分)七、图6所示是16*4位ROM和同步十六进制加法计数器74LS161组成的脉冲分频电路。

ROM中的数据见表1所示。

试画出在CP信号连续作用下的D3、D2、D1、D0输出的电压波形,并说明它们和CP 信号频率之比。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《数字电子技术》期末考试试卷(B 卷)

学院:_______________班级:_____________姓名:_______________学号:____________

一、选择题(每题2分,共20分):

1.与[375]10相等的数是( )。

A .[111011101]2

B . [567]8

C . [11101110]BC

D D .[1F4]16

2、逻辑函数F= =( )。

A..B B . A C .B A ⊕ D .B A ⊕

3、以下代码中为恒权码的为( )。

A .8421BCD 码 B. 余三循环码 C. 余三码 D. 格雷码

4、一个16选1的数据选择器,其地址输入(选择控制输入)端有( )个。

A .1

B .2

C .4

D .16

5、下列电路中,属于组合逻辑电路的是( )。

A .触发器 B. 全加器 C .移位寄存器 D .计数器

6. 一个三输入 TTL 或非门,有两个输入端分别接 A 和B ,另一个输入端经 10k Ω

电阻接地,该或非门的输出( ) 。

A. 为0

B.为 1

C.为 A 十B

D. 为B A +

7、存在一次变化问题的触发器是( )

A .基本RS 触发器

B .D 锁存器

C .主从JK 触发器

D .边沿JK 触发器

8、为了把杂乱的、宽度不一的矩形脉冲信号,整形成具有固定脉冲宽度的矩形波

信号输出,我们应选用( )电路。

A .施密特触发器 B. 单稳态触发器 C. 多谐振荡器 D.555定时器

9、要构成容量为 4K ×8的RAM ,需要( )片容量为 256×4 的RAM 。

A.2

B.4

C.8

D.32

)(B A A ⊕⊕

《数字电子技术》期末考试试卷(B 卷)

10、一个4位的二进制加计数器,由0000状态开始,经过25个时钟脉冲后,此计

数器的状态为( )

A .1100

B .1000

C .1001

D .1010 二、化简题(每题5分,共15分) 1、将F1化简为最简与-或表达式:F1= 2、将F2化简为最简与非-与非表达式:F2= 3、将F3化简为最简与-或表达式:

F3= 三、分析题(共30分) 1、分析图1所示电路的逻辑功能。

列出真值表,写出电路输出函数F3的逻辑表达

式。

(7分)

图1 图2 2、根据图2所示4选1数据选择器实现的组合电路,写出输出Z 的表达式并化为

最简“与-或”表达式。

(8分)

3、由同步十进制加法计数器74LS160构成的数字系统如图3所示,74160功能表

见附表。

假设计数器的初态为0,测得组合逻辑电路的真值表如下所示:

(1)画出74LS160的状态转换图;

(2)如用ROM 实现图3中的组合逻辑电路部分,其地址线和数据线分别为几条;

(2)如图4所示画出电路的输出时序图。

(15分)

__________________________

_______________

_________________________D

A D C D C

B A +++++++C

A C

B AB ++∑∑+=)

15,11,7,5,3,2()13,9,6,4,1,0(),,,(d m D C B A L

《数字电子技术》期末考试试卷(B卷)

图

3

图4

四、波形绘制题(15分)

1、设主从JK触发器的初始状态为0,CP、J、K信号如图5所示,试画出触发器Q 端的波形。

(9分)

图5

2、电路如图6(a)所示,若输入信号u

I 如图6(b)所示,请画出u

O

的波形。

(6分)

1

西南科技大学2009——2010学年第2学期

《数字电子技术》期末考试试卷(B卷)

图6

五、设计题(20分)

1、用与非门设计一组合电路,其输入为三位二进制数,当输入能被2或3整除时,输出F=1,其余情况F=0。

(设0能被任何数整除)(10分)

2、用同步四位二进制计数器74161构成初始状态为0100的九进制计数器。

画出状态转换图和连线图。

74161的逻辑符号和功能表分别见图7和附表。

(10分)

图7

附表:74160/74161功能表(不含进位端)

参考答案及评分细则

西南科技大学2009——2010学年第2学期

《数字电子技术》期末考试试卷(B 卷)

一、选择题(每题2分,共20分)

1-5:BAACB

6-10:ACBDB

二、化简题(每题5分,共15分)

1、F1=AC+BC+D

【采用公式法化简。

选择了合理的运算律进行化简得2分,化简结果正确得5分】

2、C A AB F2∙=

【可采用公式法和卡诺图法化简。

选择了合理的运算律进行化简或正确绘制出卡

诺图得2分,化简结果正确得5分】

3、绘制卡诺图:,化简结果:F3=D A +。

【采用卡诺图法化简。

正确绘制出含无关项的卡诺图得3分,化简结果正确得5

分】

三、分析题(共30分)

1、(1)正确列出真值表;【3分】

(2)由真值表求得逻辑表达式B C CA F +=3。

【4分】

2、(1)对数据选择器实现任意函数的功能进行了正确的判断;【4分】

参考答案及评分细则

西南科技大学2009——2010学年第2学期

《数字电子技术》期末考试试卷(B 卷)

(2)C A C A B Z ++=【4分】

3、(1)状态转换图:【6分】

(2)3条地址线,1条数据线。

【4分】

(3)【5分】

四、波形题(共15分)

1、【输出波形具体变化点每个1.5分,共9分】

参考答案及评分细则

西南科技大学2009——2010学年第2学期

《数字电子技术》期末考试试卷(B卷)

2、【输出波形具体变化点每个3分,共6分】

五、设计题(共20分)

1、(1)设用ABC表示该数,输出F。

列出真值表:【4分】

F=∑2(

(2)m

(3)逻辑图略【2分】

2、(1)采用同步置数法。

预置数输入端D3-D0接为“0100”,在计数输出为“1100”产生LD的使能信号,形成九进制计数器。

【5分】其它功能端连接正确。

【2分】(2)状态转移图从“0100”态,按加法规律递增到“1100”态后回到“0100”态。

【3分】。