实用文档之74HC595完整中文资料

74HC595芯片中文资料

11

移位寄存器时钟输入

STCP

12

存储寄存器时钟输入

OE

13

输出有效(低电平)

DS

14

串行数据输入

VCC

16

电源

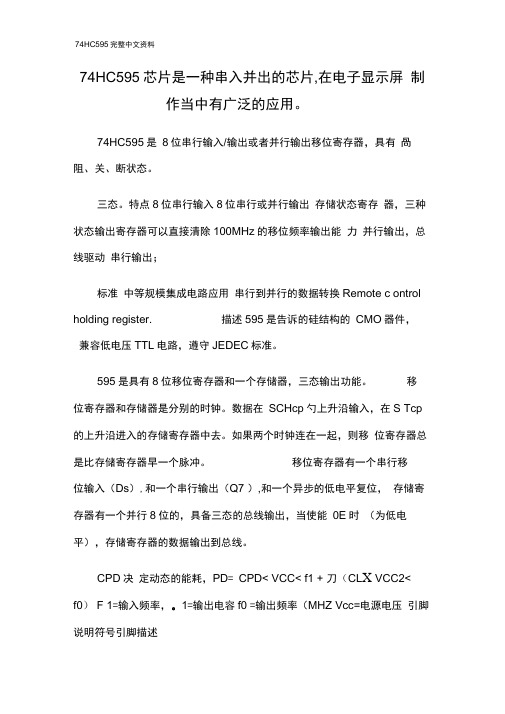

输入

输出

功能

SHCP

STCP

OE

MR

DS

Q7’

Qn

×

×

L

↓

×

L

NC

MR为低电平时紧紧影响移位寄存器

×

↑

L

L

×

L

L

空移位寄存器到输出寄存器

×

×

H

L

×

L

Z

清空移位寄存器,并行输出为高阻状态

↑

×

L

H

H

Q6’

NC

逻辑高电平移入移位寄存器状态0,包含所有的移位寄存器状态移入,例如,以前的状态6(内部Q6”)出现在串行输出位。

×

↑

L

H

×

NC

Qn’

移位寄存器的内容到达保持寄存器并从并口输

↑

↑

LHΒιβλιοθήκη ×Q6’Qn’

移位寄存器内容移入,先前的移位寄存器的内容到达保持寄存器并输出

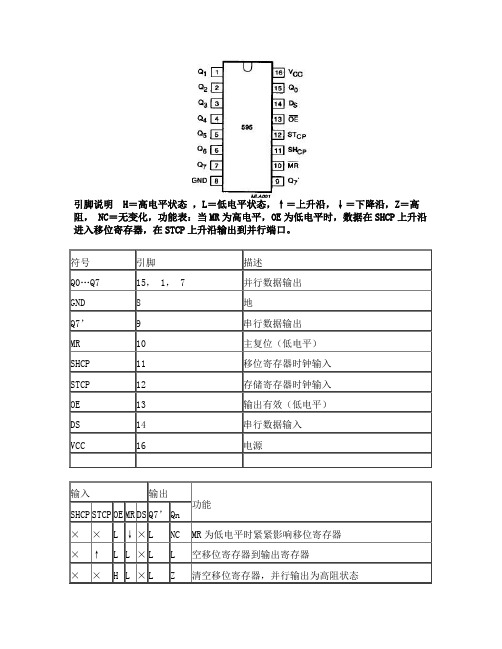

引脚说明 H=高电平状态 ,L=低电平状态,↑=上升沿,↓=下降沿,Z=高阻, NC=无变化,功能表:当MR为高电平,OE为低电平时,数据在SHCP上升沿进入移位寄存器,在STCP上升沿输出到并行端口。

符号

引脚

描述

Q0…Q7

15, 1, 7

并行数据输出

GND

8

地

Q7’

9

串行数据输出

MR

10

主复位(低电平)

74HC595史上最全的中文资料【中为电科】

X X 注:

X X

H L L L

L H H H

X H X X

L Q6S NC Q6S

Z NC QnS QnS

清空移位寄存器,并行输出高阻态 移位寄存器数据分别移动一位; 第 6 位数据 移入 Q7S 移位寄存器的内容传给存储寄存器并输出 移位寄存器的所有数据移动一位; 移位寄存 器中的所有数据转入存储寄存器并输出

7. 8. 9. 10. 11. 12. 13.

1 / 15

科技效法自然 中为电科

74HC595;74HCT595

8 位串行输入,串行或并行输出移位寄存器,输出具有锁存、三态功能

1. 简介

74HC595、 74HCT595 是一款高速硅栅 (Si‐gate) COMS 器件, 并且与低压肖特基 TTL (LSTTL) 兼容。它们符合 JEDEC 7A 号文件标准。 74HC595、74HCT595 是一个 8 位串行并且带有存储寄存器和三态输出的移位寄存器, 存储寄存器和移位寄存器同步于不同的时钟。 数据在移位寄存器时钟(SHCP)的正跳变下移动,在存储寄存器时钟(STCP)的正跳 变下数据由移位寄存器转存到存储寄存器。假如 SHCP 和 STCP 被连在一起,移位寄存器将 总是超前于存储寄存器一个时钟脉冲。 移位寄存器有一个串行输入端(DS) ,还有一个用于级联的串行输出端。8 位移位寄存 器可以异步复位 (低电平复位) 。 存储寄存器有一个 8 位三态并行输出端。 当输出使能端 (OE) 被使能(低有效)数据将从存储寄存器中输出至器件引脚。

4 / 15

科技效法自然 中为电科

6. 引脚定义

6.1 引脚图

图 4 引脚定义 6.2 引脚描述 符号 Q1 Q2 Q3 Q4 Q5 Q6 Q7 GND Q7S MR SHCP STCP OE DS Q0 Vcc 引脚号 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 地(0V) 数据串行输出 复位(低有效) 移位寄存器时钟(输入) 存储寄存器时钟(输入) 输出使能(低有效) 数据串行输入 数据并行输出 0 电源 数据并行输出 1 ~ 7 描述

74HC595完整中文资料

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有 咼阻、关、断状态。

三态。特点8位串行输入8位串行或并行输出 存储状态寄存 器,三种状态输出寄存器可以直接清除100MHz的移位频率输出能 力 并行输出,总线驱动 串行输出;

标准 中等规模集成电路应用 串行到并行的数据转换Remote c ontrol holding register.描述595是告诉的硅结构的CMO器件,

CPD决 定动态的能耗,PD=CPD< VCC< f1 +刀(CLXVCC2< f0) F 1=输入频率,。1=输出电容f0=输出频率(MHZ Vcc=电源电压 引脚说明符号引脚描述

内部结构

结合引脚说明就能很快理解595的工作情况

功能表:

管脚编号

管脚名

管脚定义功能

1、2、3、4、5、6、

7、15

QA—QH

2)74595的主要优点是具有数据存储寄存器,在移位的过程中,输出 端的数据可以保持不变。这在串行速度慢的场合很有用处,数码管没 有闪烁感。

与164只有数据清零端相比,595还多有输出端时能/禁止控制 端,可以使输出为高阻态。

3)595是串入并出带有锁存功能移位寄存器,它的使用方法很简单, 在正常使用时SCLR为高电平,G为低电平。从SER每输入一位数据, 串行输595是串入并出带有锁存功能移位寄存器,它的使用方法很简 单,如下面的真值表,在正常使用时SCLF为高电平,G为低电平。 从SER每输入一位数据,串行输入时钟SCK上升沿有效一次,直到八 位数据输入完毕,输出时钟上升沿有效一次,此时,输入的数据就被

送到了输出端。入时钟SCK上升沿有效一次,直到八位数据输入完毕, 输出时钟上升沿有效一次,此时,输入的数据就被送到了输出端。

74HC595资料

2.0V

-

0.5

0.5

0.5

V

4.5V

-

1.35

1.35

Hale Waihona Puke 1.356.0V-

1.8

1.8

1.8

VOH

Minimum HIGH Level Output Voltage最大高电平输出电压

VIN=VIH or VIL|IOUT|≤20μA

2.0V

2.0

1.9

1.9

1.9

V

4.5V

4.5

4.4

4.4

4.4

−65℃to +150℃

Power Dissipation功耗(PD)

(Note 3)

600mW

S.O. Package only

500mW

Lead Temperature (TL) (Soldering 10 seconds)

260℃

Recommended Operating Conditions建议操作条件

VIN=VCC or GND IOUT = 0μA

6.0V

-

8.0

80

160

μA

交流电气特性:

Symbol符号

Parameter参数

Conditions条件

典型

Guaranteed Limit

UNIT单位

fMax

最高工作频率

-

50

30

MHz

tPHL, tPLH

Maximum Propagation Delay,最大传输延迟SCK to Q’ H

−0.5 to VCC +0.5V

Clamp Diode Current钳位二极管电流(IIK, IOK)

74hc595中文资料

74HC595芯片是一种串入并出的芯片,在电子显示屏制作当中有广泛的应用。

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有高阻、关、断状态。

三态。

特点 8位串行输入 8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除 100MHz的移位频率输出能力并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换 Remote control holding register. 描述 595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能O E时(为低电平),存储寄存器的数据输出到总线。

CPD决定动态的能耗, PD=CPD×VCC×f1+∑(CL×VCC2×f0) F1=输入频率,CL=输出电容 f0=输出频率(MHz) Vcc=电源电压引脚说明符号引脚描述内部结构结合引脚说明就能很快理解 595的工作情况74HC595引脚图,管脚图________QB--|1 16|--VccQC--|2 15|--QAQD--|3 14|--SIQE--|4 13|--/GQF--|5 12|--RCKQG--|6 11|--SRCKQH--|7 10|--/SRCLRGND- |8 9|--QH'|________|74595的数据端:QA--QH: 八位并行输出端,可以直接控制数码管的8个段。

QH': 级联输出端。

我将它接下一个595的SI端。

74HC595完整中文资料word资料5页

74HC595芯片是一种串入并出的芯片,在电子显示屏制作当中有广泛的应用。

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有高阻、关、断状态。

三态。

特点 8位串行输入 8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除 100MHz的移位频率输出能力并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换 Remote contr ol holding register. 描述 595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp 的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

CPD决定动态的能耗, PD=CPD×VCC×f1+∑(CL×VCC2×f0) F1=输入频率,CL=输出电容 f0=输出频率(MHz) Vcc=电源电压引脚说明符号引脚描述内部结构结合引脚说明就能很快理解 595的工作情况引脚功能表:管脚编号管脚名管脚定义功能1、2、3、4、5、6、7、15QA—QH 三态输出管脚8 GND 电源地9 SQH 串行数据输出管脚10 SCLR 移位寄存器清零端11 SCK 数据输入时钟线12 RCK 输出存储器锁存时钟线13 OE 输出使能14 SI 数据线15 VCC 电源端真值表:输入管脚输出管脚SI SCK SCLR RCK OEX X X X H QA—QH 输出高阻X X X X L QA—QH 输出有效值X X L X X 移位寄存器清零L 上沿H X X 移位寄存器存储LH 上沿H X X 移位寄存器存储HX 下沿H X X 移位寄存器状态保持X X X 上沿X 输出存储器锁存移位寄存器中的状态值X X X 下沿X 输出存储器状态保持74595的数据端:QA--QH: 八位并行输出端,可以直接控制数码管的8个段。

74HC595完整中文资料

74HC595芯片是一种串入并出的芯片,在电子显示屏制作当中有广泛的应用。

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有高阻、关、断状态。

三态。

特点 8位串行输入 8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除 100MHz的移位频率输出能力并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换 Remote contr ol holding register. 描述 595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp 的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

CPD决定动态的能耗, PD=CPD×VCC×f1+∑(CL×VCC2×f0) F1=输入频率,CL=输出电容 f0=输出频率(MHz) Vcc=电源电压引脚说明符号引脚描述内部结构结合引脚说明就能很快理解 595的工作情况引脚功能表:真值表:74595的控制端说明:/SRCLR(10脚): 低点平时将移位寄存器的数据清零。

通常我将它接Vcc。

SRCK(11脚):上升沿时数据寄存器的数据移位。

QA-->QB-->QC-->...-->QH;下降沿移位寄存器数据不变。

(脉冲宽度:5V时,大于几十纳秒就行了。

我通常都选微秒级)RCK(12脚):上升沿时移位寄存器的数据进入数据存储寄存器,下降沿时存储寄存器数据不变。

(通常我将RCK置为低电平,) 当移位结束后,在RCK端产生一个正脉冲(5V时,大于几十纳秒就行了。

74HC595完整中文资料

74HC595芯片是一种串入并出的芯片,在电子显示屏制作当中有广泛的应用。

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有高阻、关、断状态。

三态。

特点8位串行输入8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除100MHz的移位频率输出能力并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换Remote contr ol holding register. 描述595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp 的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

CPD决定动态的能耗,PD=CPD×VCC×f1+∑(CL×VCC2×f0) F1=输入频率,CL=输出电容f0=输出频率(MHz)Vcc=电源电压引脚说明符号引脚描述内部结构结合引脚说明就能很快理解595的工作情况引脚功能表:真值表:74595的控制端说明:/SRCLR(10脚): 低点平时将移位寄存器的数据清零。

通常我将它接Vcc。

SRCK(11脚):上升沿时数据寄存器的数据移位。

QA-->QB-->QC-->...-->QH;下降沿移位寄存器数据不变。

(脉冲宽度:5V时,大于几十纳秒就行了。

我通常都选微秒级)RCK(12脚):上升沿时移位寄存器的数据进入数据存储寄存器,下降沿时存储寄存器数据不变。

(通常我将RCK置为低电平,) 当移位结束后,在RCK端产生一个正脉冲(5V时,大于几十纳秒就行了。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实用文档之"74HC595芯片是一种串入并出的芯片,在电子显示屏制作当中有广泛的应用。

"

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有高阻、关、断状态。

三态。

特点 8位串行输入 8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除 100MHz的移位频率输出能力并行输出,总线驱动串行输出;

标准中等规模集成电路应用串行到并行的数据转换 Remo te control holding register. 描述 595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

CPD决定动态的能耗, PD=CPD×VCC×f1+∑(CL×VCC2×f0) F1=输入频率,CL=输出电容 f0=输出频率(MHz)Vcc=电源电压引脚说明符号引脚描述

内部结构

结合引脚说明就能很快理解 595的工作情况

引脚功能表:

真值表:

串行输595是串入并出带有锁存功能移位寄存器,它的使用方法很简单,如下面的真值表,在正常使用时SCLR为高电平, G为低电平。

从SER每输入一位数据,串行输入时钟SCK上升沿有效一次,直到八位数据输入完毕,输出时钟上升沿有效一次,此时,输入的数据就被送到了输出端。

入时钟SCK上升沿有效一次,直到八位数据输入完毕,输出时钟上升沿有效一次,此时,输入的数据就被送到了输出端。

其实,看了这么多595的资料,觉得没什么难的,关键是看懂其时序图,说到底,就是下面三步(引用):

第一步:目的:将要准备输入的位数据移入74HC595数据输入端上。

方法:送位数据到 P1.0。

第二步:目的:将位数据逐位移入74HC595,即数据串入

方法:P1.2产生一上升沿,将P1.0上的数据移入74HC595中.从低到高。

第三步:目的:并行输出数据。

即数据并出

方法:P1.1产生一上升沿,将由P1.0上已移入数据寄存器中的数据

送入到输出锁存器。

说明:从上可分析:从P1.2产生一上升沿(移入数据)和P1.1产生一上升沿

(输出数据)是二个独立过程,实际应用时互不干扰。

即可输出数据的

同时移入数据。

而具体编程方法为

如:R0中存放3FH,LED数码管显示“0”

;*****接口定义:

DS_595 EQU P1.0 ;串行数据输入(595-14)

CH_595 EQU P1.2 ;移位时钟脉冲(595-11)

CT_595 EQU P1.1 ;输出锁存器控制脉冲(595-12)

;*****将移位寄存器内的数据锁存到输出寄存器并显示OUT_595:

CALL WR_595 ;调用移位寄存器接收一个字节数据子程序

CLR CT_595 ;拉低锁存器控制脉冲

NOP

NOP

SETB CT_595 ;上升沿将数据送到输出锁存器,LED数码管显示“0”

NOP

NOP

CLR CT_595

RET

;*****移位寄存器接收一个字节(如3FH)数据子程

序

WR_595:

MOV R4,#08H ;一个字节数据(8位)

MOV A,R0 ;R0中存放要送入的数据3FH

LOOP:

;第一步:准备移入74HC595数据

RLC A ;数据移位

MOV DS_595,C ;送数据到串行数据输入端上(P1.0)

;第二步:产生一上升沿将数据移入74HC595

CLR CH_595 ;拉低移位时钟

NOP

NOP

setb CH_595 ;上升沿发生移位(移入一数据)

DJNZ R4,LOOP ;一个字节数据没移完继续

RET

而其级联的应用

74HC595主要应用于点阵屏,以16*16点阵为例:传送一行共二个字节(16位)

如:发送的是06H和3FH。

其方法是:

1.先送数据3FH,后送06H。

2.通过级联串行输入后,3FH在IC2内,06H在IC1内。

应用如图二

3.接着送锁存时钟,数据被锁存并出现在IC1和IC2的并行输出口上显

示。

编程方法:

数据在30H和31H中

;MOV 30H,#3FH

;MOV 31H,#06H

;*****接口定义:

DS_595 EQU P1.0 ;串行数据输入(595-14)

CH_595 EQU P1.2 ;移位时钟脉冲(595-11)

CT_595 EQU P1.1 ;输出锁存器控制脉冲(595-12)

;*****串行输入16位数据

MOV R0,30H

CALL WR_595 ;串行输入3FH

nop

NOP

MOV R0,31H

CALL WR_595 ;串行输入06H

NOP

NOP

SETB CT_595 ;上升沿将数据送到输出锁存器,显示

NOP

NOP

CLR CT_595

RET

MC74HC595A包括一个8位移位寄存器和一个8位D型锁存器和三态并行输出。

移位寄存器接受串行数据并提供串行输出。

移位寄存器也提供并行数据输出和8位锁存器。

移位寄存器和锁存器都有独立的时钟输入。

这个IC还具有异步复位的功能。

HC595A可以直接和CMOS MPU的和MCU的SPI接口进行连接。