八D锁存器74HC573中文资料

74HC573

型号:74HC573D

尺寸:12mm(长)*8mm(宽)

12mm(长)*11mm(宽)

8D数据锁存器和373一样

注:74HC573参数

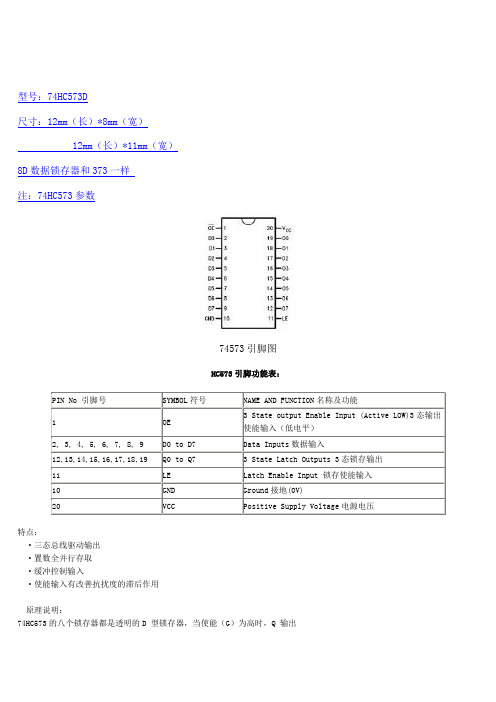

74573引脚图

HC573引脚功能表:

特点:

·三态总线驱动输出

·置数全并行存取

·缓冲控制输入

·使能输入有改善抗扰度的滞后作用

原理说明:

74HC573的八个锁存器都是透明的D 型锁存器,当使能(G)为高时,Q 输出

将随数据(D)输入而变。

当使能为低时,输出将锁存在已建立的数据电平上。

输出控制不影响锁存器的内部工作,即老数据可以保持,甚至当输出被关闭时,

新的数据也可以置入。

这种电路可以驱动大电容或低阻抗负载,可以直接与系统总线接口并驱动总线,而不需要外接口。

特别适用于缓冲寄存器,I/O 通道,双向总线驱动器和工作寄存器。

真值表:

ABSOLUTE MAXIMUM RATINGS绝对最大额定值:

RECOMMENDED OPERATING CONDITIONS建议操作条件:

DC SPECIFICATIONS直流电气规格:

应用电路图:点击图片查看大图。

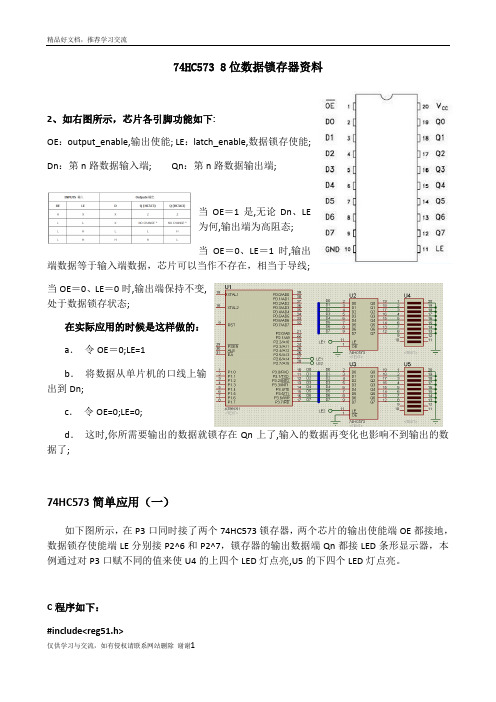

最新74HC573单片机应用

74HC573 8位数据锁存器资料2、如右图所示,芯片各引脚功能如下:OE:output_enable,输出使能; LE:latch_enable,数据锁存使能;Dn:第n路数据输入端; Qn:第n路数据输出端;当OE=1是,无论Dn、LE为何,输出端为高阻态;当OE=0、LE=1时,输出端数据等于输入端数据,芯片可以当作不存在,相当于导线;当OE=0、LE=0时,输出端保持不变,处于数据锁存状态;在实际应用的时候是这样做的:a.令OE=0;LE=1b.将数据从单片机的口线上输出到Dn;c.令OE=0;LE=0;d.这时,你所需要输出的数据就锁存在Qn上了,输入的数据再变化也影响不到输出的数据了;74HC573简单应用(一)如下图所示,在P3口同时接了两个74HC573锁存器,两个芯片的输出使能端OE都接地,数据锁存使能端LE分别接P2^6和P2^7,锁存器的输出数据端Qn都接LED条形显示器,本例通过对P3口赋不同的值来使U4的上四个LED灯点亮,U5的下四个LED灯点亮。

C程序如下:#include<reg51.h>sbit LE1=P2^6;sbit LE2=P2^7;void main(){LE1=1;P3=0X0F;LE1=0; //开启锁存功能,使U2输出端锁存数据0X0FLE2=1;P3=0XF0;LE2=0; //开启锁存功能,使U3输出端锁存数据0XF0while(1);}74HC573简单应用(二)两片74HC573的数据输入端同时接到P0口,输出使能端OE都接地,数据锁存端LE分别接到P2^6和P2^7,U2的数据输出端接六个数码管的段码,U3的数据输出端接六个数码管的位码。

本例使六个数码管同时循环点亮0到9十个数字。

C程序如下:#include<reg51.h>#define uchar unsignedc har#define uint unsigned int//延时函数void delay(uint x){uchar i;while(x--)for(i=0;i<120;i++);}//0到9的共阴显示代码uchar code dis[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,0x7f,0x6f}; sbit LE1=P2^6;sbit LE2=P2^7;uchar i;void main(){ LE2=1;P0=0XC0;LE2=0;while(1){LE1=1;P0=dis[i];LE1=0;delay(400);//延时1s左右i=(i+1)%10;//i取值为0到9}}木兰诗北朝民歌唧(jī)唧复唧唧,木兰当户织。

74HC573中文资料

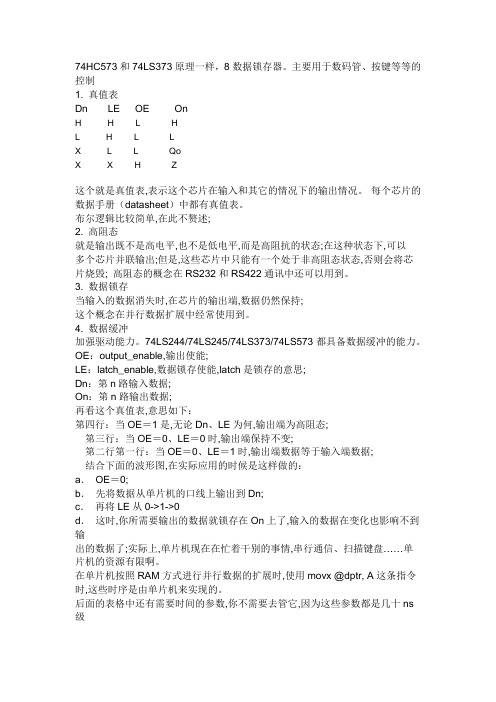

74HC573和74LS373原理一样,8数据锁存器。

主要用于数码管、按键等等的控制1. 真值表Dn LE OE OnH H L HL H L LX L L QoX X H Z这个就是真值表,表示这个芯片在输入和其它的情况下的输出情况。

每个芯片的数据手册(datasheet)中都有真值表。

布尔逻辑比较简单,在此不赘述;2. 高阻态就是输出既不是高电平,也不是低电平,而是高阻抗的状态;在这种状态下,可以多个芯片并联输出;但是,这些芯片中只能有一个处于非高阻态状态,否则会将芯片烧毁; 高阻态的概念在RS232和RS422通讯中还可以用到。

3. 数据锁存当输入的数据消失时,在芯片的输出端,数据仍然保持;这个概念在并行数据扩展中经常使用到。

4. 数据缓冲加强驱动能力。

74LS244/74LS245/74LS373/74LS573都具备数据缓冲的能力。

OE:output_enable,输出使能;LE:latch_enable,数据锁存使能,latch是锁存的意思;Dn:第n路输入数据;On:第n路输出数据;再看这个真值表,意思如下:第四行:当OE=1是,无论Dn、LE为何,输出端为高阻态;第三行:当OE=0、LE=0时,输出端保持不变;第二行第一行:当OE=0、LE=1时,输出端数据等于输入端数据;结合下面的波形图,在实际应用的时候是这样做的:a.OE=0;b.先将数据从单片机的口线上输出到Dn;c.再将LE从0->1->0d.这时,你所需要输出的数据就锁存在On上了,输入的数据在变化也影响不到输出的数据了;实际上,单片机现在在忙着干别的事情,串行通信、扫描键盘……单片机的资源有限啊。

在单片机按照RAM方式进行并行数据的扩展时,使用movx @dptr, A这条指令时,这些时序是由单片机来实现的。

后面的表格中还有需要时间的参数,你不需要去管它,因为这些参数都是几十ns级别的,对于单片机在12M下的每个指令周期最小是1us的情况下,完全可以实现;如果是你自己来实现这个逻辑,类似的指令如下:mov P0,A ;将数据输出到并行数据端口clr LEsetb LEclr LE ;上面三条指令完成LE的波形从0->1->0的变化74ls573跟74LS373逻辑上完全一样,只不过是管脚定义不一样,数据输入和输出端。

74HC573功能说明(原创编辑)

1.真值表74HC573真值表,意思如下:第一行/第二行:当OE=0、LE=1时,输出端数据等于输入端数据;第三行:当OE=0、LE=0时,输出端保持不变;第四行:当OE=1是无论Dn、LE为何,输出端为高阻态;2. 高阻态就是输出既不是高电平,也不是低电平,而是高阻抗的状态;在这种状态下,可以多个芯片并联输出;但是,这些芯片中只能有一个处于非高阻态状态,否则会将芯片烧毁。

高阻态的概念在RS232和RS422通讯中还可以用到。

3. 数据锁存当输入的数据消失时,在芯片的输出端,数据仍然保持;这个概念在并行数据扩展中经常使用到。

4. 数据缓冲加强驱动能力:74LS244/74LS245/74LS373/74LS573都具备数据缓冲的能力。

◆OE:output_enable,输出使能;◆LE:latch_enable,数据锁存使能,atch是锁存的意思;◆Dn:第n路输入数据;◆On:第n路输出数据;74HC573波形图,在实际应用的时候是这样做的:a.OE=0;b.先将数据从单片机的口线上输出到Dn;c.再将LE从0->1->0 ;d.这时,你所需要输出的数据就锁存在On上了,输入的数据在变化也影响不到输出的数据了;实际上,单片机现在在忙着干别的事情,串行通信、扫描键盘……单片机的资源有限啊。

在单片机按照RAM方式进行并行数据的扩展时,使用movx @dptr, A这条指令时,这些时序是由单片机来实现的。

后面的表格中还有需要时间的参数,你不需要去管它,因为这些参数都是几十ns级别的,对于单片机在12M下的每个指令周期最小是1us的情况下,完全可以实现;如果是你自己来实现这个逻辑,类似的指令如下:MOV P0,A ; //将数据输出到并行数据端口CLR LESETB LECLR LE ; //上面三条指令完成LE的波形从0->1->0的变化74LS573跟74LS373逻辑上完全一样,只不过是管脚定义不一样,数据输入和输出端.。

(完整word版)74HC573功能说明(原创编辑)0001

74CH573锁存器的功能74HC573和74LS373原理一样,8数据锁存器。

主要用于数码管、按键等等的控制 74HC573有20个脚,数据的进和出没有逻辑关系,这个芯片主要是看高电压激活还是低 电压激活:1是低电压激活芯片2~9脚是数据的输入脚从 DO 到D710脚是接地11脚是高电压激活芯片12~19脚是数据的输出脚20是电源SNS4HCS7 3A . . FK PACKAGE(TOP VIEW)1•真值表3 2 1 20 19 厂ZUIH E苛[ 171stOE1D益3D 4D5Dec0D GKD]^ec ]1Q]%]4a ]5Q ]7Q 1 5Q ■ ■ILEOurPLFT ENABLE乂>EXPAMJtD I 1MAC ;K\M3C4D 5 口 6D7D/ t_n_IT _re_r~ir~LT~u~~m2Q 3Q4Q50fid亡I □ Ld □口 B N —l 在 g功能範高阻抗74HC573真值表,意思如下:第一行/第二行:当0E = 0、LE = 1时,输出端数据等于输入端数据;第三行:当0E = 0、LE = 0时,输出端保持不变;第四行:当0E = 1是无论Dn、LE为何,输出端为高阻态;2. 高阻态就是输出既不是高电平,也不是低电平,而是高阻抗的状态;在这种状态下,可以多个芯片并联输出;但是,这些芯片中只能有一个处于非高阻态状态,否则会将芯片烧毁。

高阻态的概念在RS232和RS422通讯中还可以用到。

3. 数据锁存当输入的数据消失时,在芯片的输出端,数据仍然保持;这个概念在并行数据扩展中经常使用到。

4. 数据缓冲加强驱动能力:74LS244/74LS245/74LS373/74LS573 都具备数据缓冲的能力。

0E : output_enable,输出使能;LE : latch_enable,数据锁存使能,atch是锁存的意思;Dn :第n路输入数据;On :第n路输出数据;74HC573波形图,在实际应用的时候是这样做的:OE = 0;先将数据从单片机的口线上输出到 出的数据了;实际上,单片机现在在忙着干别的事情,串行通信、扫描键盘 片机的资源有限啊。

74hc573可以驱动几位共阴数码管?74hc573驱动数码管应用解析

74hc573可以驱动几位共阴数码管?74hc573驱动数码管应用解析74hc573能够驱动几位共阴数码管取决于你使用几片74hc573,如果用两片,一片锁存段码,一片锁存位码,就可以驱动8位数码管。

在讲解74hc573驱动数码管问题之前我们要清楚,什么是74hc573及什么是数码管?数码管数码管是一种半导体发光器件,其基本单元是发光二极管,文章用到的是2位连体共阴数码管。

这种数码管有8根段码引脚和2根位码引脚,段码决定了显示的是什么字符,位码决定了哪位数码管被点亮。

对于共阴数码管来讲,位码引脚为低电平时,相应的数码管被点亮。

74hc573锁存器74HC573是拥有八路输出的透明锁存器,输出为三态门,是一种高性能硅栅CMOS器件。

具有8个数据输入端、8个数据输出端和3个控制端。

1脚(OE)为输出使能端,11脚(LE)为锁存使能端。

锁存器的工作原理:当OE为高时,输出为高阻态,即锁存器不能正常工作。

当OE为低且LE为高时,输出Q将随输入D而变,此时锁存器工作在直通模式下。

当OE为低且LE为低时,输出Q将不随输入D而变,此时锁存器工作在锁存模式下,输出Q保持上一时刻数值不变。

74hc573可以驱动几位共阴数码管?理论上说只要你74hc573使用得够多,就能驱动更多的数码管,下面来分享74hc573驱动数码管的应用电路及程序分享74hc573驱动2位数码管在程序开头部分先定义1个数组,数组元素为数码管的段码:uchar+code+table[]={0x3f,0x06,0x5b,0x4f,0x66%,0x6d,0x7d,0x07,0x7f,0x6f}关键代码及注释如下。

数据拆分和显示函数该函数在具体实现时,不停地先送显个位数,然后送显十位数,即采用了数码管动态扫描法。

扫描间隔不宜太长,文章为1毫秒,用delay(1)实现这个间隔,若扫描间隔太长,会导致扫描刷新不及时,出现个位和十位交替闪烁的现象。

定时计数器的初始化及其中断函数结论本电路采用单片机作为主控制器,设计了0-99循环计数并显示的电路,采用了锁存器实现2位数码管动态扫描显示。

74hc573完整中文资料培训讲学

74h c573完整中文资料74hc573中文资料参数-74hc573引脚图-功能原理-74hC573的作用-应用电路-74hC563-54hC57高性能硅门 CMOS器件SL74HC573跟 LS/AL573的管脚一样。

器件的输入是和标准CMOS输出兼容的;加上拉电阻,他们能和 LS/ALSTTL输出兼容。

当锁存使能端为高时,这些器件的锁存对于数据是透明的(也就是说输出同步)。

当锁存使能变低时,符合建立时间和保持时间的数据会被锁存。

×输出能直接接到CMOS,NMOS和 TTL接口上×操作电压范围:2.0V~6.0V×低输入电流:1.0uA×CMOS器件的高噪声抵抗特性·三态总线驱动输出·置数全并行存取·缓冲控制输入·使能输入有改善抗扰度的滞后作用原理说明:M54HC563/74HC563/M54HC573/74HC573的八个锁存器都是透明的D 型锁存器,当使能(G)为高时,Q 输出将随数据(D)输入而变。

当使能为低时,输出将锁存在已建立的数据电平上。

输出控制不影响锁存器的内部工作,即老数据可以保持,甚至当输出被关闭时,新的数据也可以置入。

这种电路可以驱动大电容或低阻抗负载,可以直接与系统总线接口并驱动总线,而不需要外接口。

特别适用于缓冲寄存器,I/O 通道,双向总线驱动器和工作寄存器。

HC563引脚功能表:HC573引脚功能表:1OE 3 State output Enable Input (Active LOW)3态输出使能输入(低电平)2, 3, 4, 5, 6, 7, 8, 9D0 to D7Data Inputs数据输入12,13,14,15,16,17,18,19Q0 to Q7 3 State Latch Outputs 3态锁存输出11LE Latch Enable Input 锁存使能输入10GND Ground接地(0V)20VCC Positive Supply Voltage电源电压图1 HC573引脚图图2 HC573 国际电工委员会逻辑符号图3 HC563引脚图图4 HC563 国际电工委员会逻辑符号图5 HC563 逻辑图图6 HC573 逻辑图图7 输入输出等效电路真值表:INPUTS 输入Outputs输出OE LE D Q (HC573) Q (HC563) H X X Z ZL L X NO CHANGE *NO CHANGE * L H L L HL H H H L ABSOLUTE MAXIMUM RATINGS绝对最大额定值:Symbol 符号Parameter 参数Value 数值Unit 单位VCC Supply Voltage电源电压-0.5 to +7VVI DC Input Voltage 直流输入电压-0.5 to VCC + 0.5VVO DC Output Voltage直流输出电压-0.5 to VCC + 0.5VIIK DC Input Diode Current直流输入二极管电流± 20mA IOK DC Output Diode Current直流输出二极管电流± 20mA IO DC Output Source Sink Current Per Output Pin± 35mA ICC or IGND DC VCC or Ground Current± 70mA PD Power Dissipation功耗500 (*)mW Tstg Storage Temperature贮藏温度-65 to +150℃TL Lead Temperature 焊接温度 (10 sec)300℃RECOMMENDED OPERATING CONDITIONS建议操作条件:Symbol 符号Parameter 参数Value 数值Unit单位VCC Supply Voltage电源电压 2 to 6V VI Input Voltage输入电压0 to VCC V VO Output Voltage输出电压0 to VCC VTop Operating Temperature: M54HC Series M74HC Series操作温度: M54HC系列M74HC系列-55 to +125 -40 to +85℃tr,tf Input Rise and Fall Time输入上升和下降时间VCC =2V0 to 1000ns VCC=4.5V0 to 500VCC =6V0 to 400VOHHigh Level Output Voltage输出高电平电压2.0 VI = VIH or VILIO=-20 μA1.92.0-1.9 -1.9 -V4.54.44.54.44.4---6.05.96.05.95.9-4.5IO=-6.0 mA4.184.314.134.10-6.0IO=-7.8 mA5.685.85.635.60-VOLLow Level Output Voltage输出低电平电压2.0 VI = VIH or VILIO=20 μA-0.0 0.1 -0.1-0.1V4.5-0.00.1 0.10.16.0-0.00.10.10.14.5IO= 6.0mA-0.170.260.330.406.0IO= 7.8mA-0.180.260.330.40IIInput Leakage Current输入漏电流6.0VI=VCC or GND--±0.1-±1±1μA IOZState Output Off State Current关断状态3态输出电流6.0VI =VIH or VIL VO =VCC or GND--±0.5-±5.0-±10μAICCQuiescent Supply Current静态电源电流6.0VI =VCC or GND--4-40-80μA应用电路图:点击图片查看大图图8。

74hc573和74hc595有什么不同?该怎样区分74hc573和74hc595

74hc573 和74hc595 有什么不同?该怎样区分

74hc573 和74hc595

这是两种完全不同的器件,74hc573 是个锁存器,而74hc595 则是一个串转并的芯片。

虽然它俩都能节约外部引脚及增大驱动能力,但不是不同点还是大于相同点的,本文是要比较74hc573 和74hc595 的不同点,看看它俩差别在哪些地方。

74hc573

74HC573 是拥有八路输出的透明锁存器,输出为三态门,是一种高性能硅栅CMOS 器件。

器件的输入是和标准CMOS 输出兼容的,加上拉电阻他们能和LS/ALSTTL 输出兼容。

八进制3 态非反转透明锁存器+74HC573+高性能硅门CMOS 器件+SL74HC573 跟LS%2FAL573 的管脚一样。

器件的输入是和标准CMOS 输出兼容+的;加上拉电阻,他们能和LS%2FALSTTL 输出兼容。

当锁存使能端为高时,这些器件的锁存对于数据是透明的(也就是说输出同步)。

当锁存使能变低时,符合建立时间和保持时间的数据会被锁存。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

八D锁存器74HC573中文资料

74HC573特点:

·三态总线驱动输出

·置数全并行存取

·缓冲控制输入

·使能输入有改善抗扰度的滞后作用

原理说明:

M54HC563/74HC563/M54HC573/74HC573的八个锁存器都是透明的D型锁存器,当使能(G)为高时,Q 输出将随数据(D)输入而变。

当使能为低时,输出将锁存在已建立的数据电平上。

输出控制不影响锁存器的内部工作,即老数据可以保持,甚至当输出被关闭时,新的数据也可以置入。

这种电路可以驱动大电容或低阻抗负载,可以直接与系统总线接口并驱动总线,而不需要外接口。

特别适用于缓冲寄存器,I/O 通道,双向总线驱动器和工作寄存器。