锁存器SN74HC使用总结

74HC74管脚排列中文资料

74HC74管脚排列

74HC74 概述

74HC74是一款高速CMOS器件,74HC74引脚兼容低功耗肖特基TTL (LSTTL)系列。

74HC74遵循JEDEC标准no.7A。

74HC74是双路D 型上升沿触发器,带独立的数据(D)输入、时钟(CP)输入、设置(SD)和复位(RD)输入、以及互补的Q和Q输出。

设置和复位为异步低电平有效,且不依赖于时钟输入。

74HC74数据输入口的信息在时钟脉冲的上升沿传输到Q口。

为了获得预想中的结果,D输入必须在时钟脉冲上升沿来临之前,保持稳定一段就绪时间。

74HC74时钟输入的施密特触发功能使得电路对于缓慢的脉冲上升和下降具备更高的容差性。

74HC74 特性

工作电压范围:2.0~6.0 V

对称输出阻抗

高抗扰

低功耗

ESD保护

HBM EIA/JESD22-A114-A超过2000 V

MM EIA/JESD22-A115-A超过200 V

74HC74 参数

74HC74 基本参数

电压 2.0~6.0V

驱动电流+/-5.2 mA

传输延迟14 ns@5V

74HC74 其他特性

逻辑电平CMOS

功耗考量低功耗或电池供电应用74HC74 封装与引脚

SO14, SSOP14, DIP14, TSSOP14。

74HC系列 全部 功能列表

4位双向通用移位寄存器 4位并行存取移位寄存器 双单稳态多谐振荡器 3—8线译码器(带地扯锁存) 3—8线译码器/多路分配器 八缓冲器/驱动器/接收器 八缓冲器/驱动器/接收器 四总线收发器(三态、反相) 四总线收发器(三态、同相) 八缓冲器/驱动器/接收器 八总线收发器(三态) 8选1数据选择器(三态) 四2输入与非门 四2输入或非门 六反相器 六反相器(OC) 四2输入与门 四2输入与门(OC) 三3输入与非门 三3输入与门 六反相器(施密特触发) 双4输入与非门 双4输入与门 三3输入或非门 8输入与非门 四2输入或门 BCD—十进制译码器 2输入/3输入双与或非门 2输入/3输入双与或门 双J—K触发器(带清除端) 双D型正沿触发器 4位双稳态D型锁存器 双J—K触发器(带预置清除端) 4位幅度比较器 四2输入异或门 从J—K触发器(带清除端) 双J—K正沿触发器

74HC系列全部功能列表

型 号 74HC253 74HC257 74HC259 74HC266 74HC273 74HC279 74HC280 74HC283 74HC298 74HC365 74HC366 74HC367 74HC368 74HC373 74HC374 74HC377 74HC386 74HC390 74HC393 74HC540 74HC541 74HC573 74HC574 74HC589 74HC595 74HC688 74HC4002 74HC4015 74HC4017 74HC4040 74HC4046 74HC4049 74HC4050 74HC4051 功 能 双4选1数据选择器(三态) 四2选1数据选择器(三态) 8位可寻址锁存器 四2输入异或非门(OC) 八D型触发器(带清除端) 四R—S锁存器 9位奇偶数产生器/校验器 4位二进制全加器(带超前进位) 4位2选1数据选择器 六缓冲器/总线驱动(同相) 六缓冲器/总线驱动(反相) 六缓冲器/总线驱动(同相) 六缓冲器/总线驱动(反相) 八D触发器(三态) 八D触发器(三态) 八D触发器 四2输入异或门 双4位十进制计数器 双4位二进制计数器(异步清除) 八缓冲器/总线驱动器 八缓冲器/总线驱动器 八D锁存器(三态) 八D锁存器(三态) 8位输入锁存输出移位寄存器 8位输出锁存移位寄存器 8位数值比较器/等值检测器 从4输入或非门 双4位串入并出移位寄存器 十进制计数器/分配器 12位二进制串行计数器 锁相环 六缓冲器/电平变换器(反相) 六缓冲器/电平变换器(同相) 单8通道模拟开关

74hc373锁存器作用

74HC373锁存器作用什么是74HC373锁存器?74HC373是一种集成电路芯片,属于高速CMOS逻辑系列,由意法半导体公司生产。

它是一种8位锁存器,可用于在数字电路中存储8位数据。

锁存器是数电中常见的一个功能模块,用于存储和保持信号。

74HC373锁存器的作用74HC373锁存器在数字电路中起到重要的作用,以下是几个典型的应用场景:1. 数据缓存在某些情况下,需要将某个电平的信号保持一段时间,并在需要时输出。

74HC373锁存器可以用作数据缓存,将输入信号锁存,并在需要时输出。

这在通信系统、计算机存储和控制电路中经常使用。

通过将数据输入到锁存器中,可以防止数据丢失,确保在更合适的时机进行处理。

2. 数据传输74HC373锁存器通常被用作数据传输的工具。

当需要将数据从一个电路传输到另一个电路时,可以使用锁存器来暂存待传输的数据。

通过将数据输入到锁存器中,并在需要传输时将数据输出,可以确保数据传输的可靠性和稳定性。

3. 地址寄存器在微处理器系统中,锁存器经常被用作地址寄存器。

地址寄存器用于存储指令的地址,以便微处理器能够从存储器中读取指令。

通过使用74HC373锁存器作为地址寄存器,可以实现高效的地址存储和解码。

4. 控制信号在数字电路中,锁存器也可以用于存储和控制信号的生成。

通过将控制信号输入到锁存器中,并根据需要输出,可以实现复杂的控制逻辑。

锁存器可以存储不同的控制状态,并在需要时将相应的控制信号输出到其他电路中,从而实现对数字系统的控制。

5. 边沿检测锁存器还可以用于边沿检测。

在数字信号处理中,有时需要检测信号的上升沿或下降沿。

通过将信号输入到锁存器中,并与之前的状态进行比较,可以检测到信号的边沿。

这对于时序控制和触发器电路非常有用。

总结74HC373锁存器是一种常见的集成电路芯片,用于存储和保持信号。

它的作用多种多样,可以用于数据缓存、数据传输、地址寄存器、控制信号和边沿检测等场景。

锁存器在数字电路中起到重要的作用,对于数字系统的设计和控制至关重要。

完整word版74HC573功能说明原创编辑

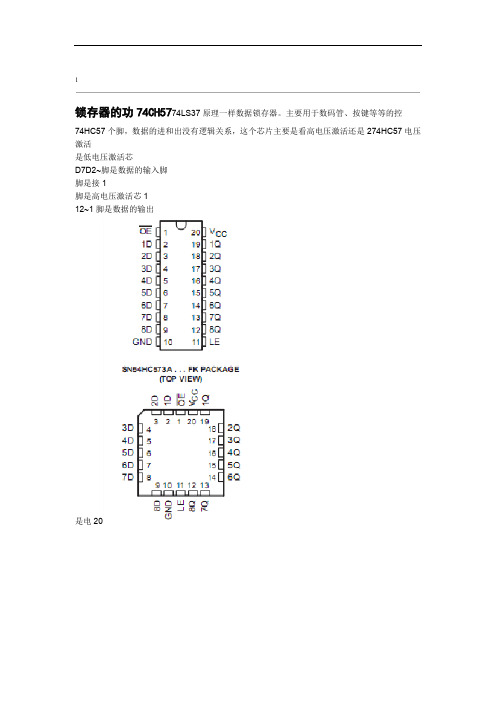

1锁存器的功74CH5774LS37原理一样数据锁存器。

主要用于数码管、按键等等的控74HC57个脚,数据的进和出没有逻辑关系,这个芯片主要是看高电压激活还是274HC57电压激活是低电压激活芯D7D2~脚是数据的输入脚脚是接1脚是高电压激活芯112~1脚是数据的输出是电20121.真值表意思如下:74HC573真值表,1时,输出端数据等于输入端数据;、LE==?第一行/第二行:当OE0 时,输出端保持不变;=、LE0?第三行:当OE=0 为何,输出端为高阻态;Dn、LE 第四行:当OE=1是无论? 2. 高阻态在这种状态下,可以多而是高阻抗的状态;就是输出既不是高电平,也不是低电平,这些芯片中只能有一个处于非高阻态状态,否则会将芯片烧毁。

高个芯片并联输出;但是,通讯中还可以用到。

RS422 阻态的概念在RS232和数据锁存3.数据仍然保持;这个概念在并行数据扩展中当输入的数据消失时,在芯片的输出端, 经常使用到。

4. 数据缓冲加强驱动能力:74LS244/74LS245/74LS373/74LS573都具备数据缓冲的能力。

,输出使能;:output_enable? OE 是锁存的意思;atch:latch_enable,数据锁存使能,LE?路输入数据;:第n ?Dn 路输出数据;On :第n?23在实际应用的时候是这样做的:74HC573波形图,;OE=0a.;先将数据从单片机的口线上输出到Dnb.从0->1->0 ;c.再将LE 这时,你所需要输出的数据就锁存在On上了,输入的数据在变化也影响不到输d.……单出的数据了;实际上,单片机现在在忙着干别的事情,串行通信、扫描键盘片机的资源有限啊。

这条方式进行并行数据的扩展时RAM,使用movx @dptr, A在单片机按照指令时,这些时序是由单片机来实现的。

因为这些参数都是几后面的表格中还有需要时间的参数,你不需要去管它,的情况下,完12M下的每个指令周期最小是1us十ns级别的,对于单片机在全可以实现;如果是你自己来实现这个逻辑,类似的指令如下:MOV P0,A ; //将数据输出到并行数据端口LE CLRSETB LE的波形从LE ; //上面三条指令完成LE0->1->0的变化CLR数据输入和,,74LS37374LS573跟逻辑上完全一样只不过是管脚定义不一样输出端.3。

74HC573锁存器

74HC573锁存器编程时,先将使能端置1,此时输出数据和输入数据一致;为了将输出的数据锁定,防止误操作,可将使能端清0,此时,输出端保持原有值,不再变化。

(1,使能置1;2,数据输入到锁存器输入端(输出=输入);3,使能置0(输出恒定=先前输入);(达到锁存功能))74HC系列的数字集成电路,当5V供电时,输出高电平接近5V,带负载后,能输出4.95V左右。

从你图上看,这里需要573输出高电平段码,138输出位码,进行动态显示。

但是图上有错,为了LED安全使用,在573的输出端与7LED连接之间,应串联300Ω电阻。

附加:锁存器的作用锁存器(Latch)是一种对脉冲电平敏感的存储单元电路,它们可以在特定输入脉冲电平作用下改变状态。

锁存,就是把信号暂存以维持某种电平状态。

锁存器的最主要作用是缓存,其次完成高速的控制其与慢速的外设的不同步问题,再其次是解决驱动的问题,最后是解决一个I/O 口既能输出也能输入的问题。

74HC37374HC37374hc373中文资料:373为三态输出的八D 透明锁存器,共有54/74S373 和54/74LS373 两种线路结构型式,其主要电器特性的典型值如下(不同厂家具体值有差别):型号tPd PD54S373/74S373 7ns 525mW54LS373/74LS373 17ns 120mW373 的输出端O0~O7 可直接与总线相连。

当三态允许控制端OE 为低电平时,O0~O7 为正常逻辑状态,可用来驱动负载或总线。

当OE 为高电平时,O0~O7 呈高阻态,即不驱动总线,也不为总线的负载,但锁存器内部的逻辑操作不受影响。

当锁存允许端LE 为高电平时,O 随数据D 而变。

当LE 为低电平时,O 被锁存在已建立的数据电平。

当LE 端施密特触发器的输入滞后作用,使交流和直流噪声抗扰度被改善400mV。

74ls74 锁存器

解: 在t1之前,CP脉冲没有到达,输出Q为初始状态0(图中标注为“初 态”),为高电平。 在t1时,第1个CP到达,在CP=1期间,S=1、R=0,触发器置1;CP脉 冲结束之后,触发器仍锁定为1状态(图中标注为“置1”), 故Q=1、=0。

7 触发器

本章将按照触发器的功能分类介绍触发器的电路组成、工作原理、逻 辑符号、特性描述等,其中包括RS触发器、D触发器、JK触发器、T及 T'触发器、施密特触发器、单稳态触发器和无稳态单元——定时器等。

7.1 RS触发器

7.1.1 基本RS触发器

我们知道,1个非门,入高出低,入低出高;把2个非门串联起来, 如图7.1.1-1(a)所示,则入高出高,入低出低;如果象图7.1.1-1(b)中的虚 线那样再把与输入信号S同为高(或低)电平的输出信号Q引回到输入 端并迅速移去输入信号,则电路必将永久锁定并保存原来的输入状态, 所以,这种电路称为锁存器。锁存器中的2个非门总是1个导通另1个关 断,只有这两种稳定状态,因此锁存器也叫做双稳态。在一种稳态下, 输出处于高电平,即Q=1,我们说电路为1状态;在另一种稳态下,输 出处于低电平,即Q=0,我们说电路为0状态;这样,我们就可以用锁 存器保存数字0和1了。

在数字电路或数字系统中,各个部分必须同步协调工作。而基本RS 触发器的特点是,输入一到达输出立即改变状态。那么,怎样才能使基 本RS触发器具有同步功能呢?

大家知道,1个与门,设有2个输入S、CP,CP=0时,与门输出恒等于 0,好象门被关闭,无论S怎样变化,输出都不受S的影响;而当CP=1 时,与门的输出恒等于S,好象门已经打开,输出始终跟随S变化。根据 这一思路,在基本RS触发器R、S输入端各加1个与门,并用CP信号进行 控制,如图7.1.2-1(a)所示,这就是同步RS触发器。工作原理如 下:CP=0时,门G3、G4被封锁,G3、G4输出均为低电平0,输入信号 R、S不能到达基本RS触发器的输入端,触发器保持原状态;当CP=1 时,门G3、G4打开,输入信号R、S到达基本RS触发器的输入端,情况 与图7.1.1-1(d)的基本RS触发器完全一样,特性方程与式(7.1.1-1)相 同,特性表如表7.1.2-1所示,电路符号给出在图7.1.2-1(b)中,其中同步 控制信号称为时钟脉冲CP(Clock Pulse)。所以同步RS触发器也叫做 钟控RS触发器。

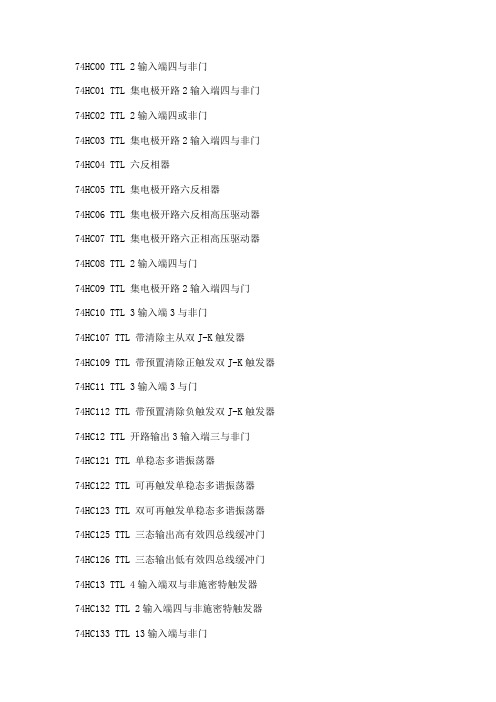

74HC系列通用逻辑电路功能表

74HC00 TTL 2输入端四与非门74HC01 TTL 集电极开路2输入端四与非门74HC02 TTL 2输入端四或非门74HC03 TTL 集电极开路2输入端四与非门74HC04 TTL 六反相器74HC05 TTL 集电极开路六反相器74HC06 TTL 集电极开路六反相高压驱动器74HC07 TTL 集电极开路六正相高压驱动器74HC08 TTL 2输入端四与门74HC09 TTL 集电极开路2输入端四与门74HC10 TTL 3输入端3与非门74HC107 TTL 带清除主从双J-K触发器74HC109 TTL 带预置清除正触发双J-K触发器74HC11 TTL 3输入端3与门74HC112 TTL 带预置清除负触发双J-K触发器74HC12 TTL 开路输出3输入端三与非门74HC121 TTL 单稳态多谐振荡器74HC122 TTL 可再触发单稳态多谐振荡器74HC123 TTL 双可再触发单稳态多谐振荡器74HC125 TTL 三态输出高有效四总线缓冲门74HC126 TTL 三态输出低有效四总线缓冲门74HC13 TTL 4输入端双与非施密特触发器74HC132 TTL 2输入端四与非施密特触发器74HC133 TTL 13输入端与非门精选文档74HC136 TTL 四异或门74HC138 TTL 3-8线译码器/复工器74HC139 TTL 双2-4线译码器/复工器74HC14 TTL 六反相施密特触发器74HC145 TTL BCD—十进制译码/驱动器74HC15 TTL 开路输出3输入端三与门74HC150 TTL 16选1数据选择/多路开关74HC151 TTL 8选1数据选择器74HC153 TTL 双4选1数据选择器74HC154 TTL 4线—16线译码器74HC155 TTL 图腾柱输出译码器/分配器74HC156 TTL 开路输出译码器/分配器74HC157 TTL 同相输出四2选1数据选择器74HC158 TTL 反相输出四2选1数据选择器74HC16 TTL 开路输出六反相缓冲/驱动器74HC160 TTL 可预置BCD异步清除计数器74HC161 TTL 可予制四位二进制异步清除计数器74HC162 TTL 可预置BCD同步清除计数器74HC163 TTL 可予制四位二进制同步清除计数器74HC164 TTL 八位串行入/并行输出移位寄存器74HC165 TTL 八位并行入/串行输出移位寄存器74HC166 TTL 八位并入/串出移位寄存器74HC169 TTL 二进制四位加/减同步计数器74HC17 TTL 开路输出六同相缓冲/驱动器精选文档74HC170 TTL 开路输出4×4寄存器堆74HC173 TTL 三态输出四位D型寄存器74HC174HC TTL 带公共时钟和复位六D触发器74HC175 TTL 带公共时钟和复位四D触发器74HC180 TTL 9位奇数/偶数发生器/校验器74HC181 TTL 算术逻辑单元/函数发生器74HC185 TTL 二进制—BCD代码转换器74HC190 TTL BCD同步加/减计数器74HC191 TTL 二进制同步可逆计数器74HC192 TTL 可预置BCD双时钟可逆计数器74HC193 TTL 可预置四位二进制双时钟可逆计数器74HC194 TTL 四位双向通用移位寄存器74HC195 TTL 四位并行通道移位寄存器74HC196 TTL 十进制/二-十进制可预置计数锁存器74HC197 TTL 二进制可预置锁存器/计数器74HC20 TTL 4输入端双与非门74HC21 TTL 4输入端双与门74HC22 TTL 开路输出4输入端双与非门74HC221 TTL 双/单稳态多谐振荡器74HC240 TTL 八反相三态缓冲器/线驱动器74HC241 TTL 八同相三态缓冲器/线驱动器74HC243 TTL 四同相三态总线收发器74HC244 TTL 八同相三态缓冲器/线驱动器74HC245 TTL 八同相三态总线收发器精选文档74HC247 TTL BCD—7段15V输出译码/驱动器74HC248 TTL BCD—7段译码/升压输出驱动器74HC249 TTL BCD—7段译码/开路输出驱动器74HC251 TTL 三态输出8选1数据选择器/复工器74HC253 TTL 三态输出双4选1数据选择器/复工器74HC256 TTL 双四位可寻址锁存器74HC257 TTL 三态原码四2选1数据选择器/复工器74HC258 TTL 三态反码四2选1数据选择器/复工器74HC259 TTL 八位可寻址锁存器/3-8线译码器74HC26 TTL 2输入端高压接口四与非门74HC260 TTL 5输入端双或非门74HC266 TTL 2输入端四异或非门74HC27 TTL 3输入端三或非门74HC273 TTL 带公共时钟复位八D触发器74HC279 TTL 四图腾柱输出S-R锁存器74HC28 TTL 2输入端四或非门缓冲器74HC283 TTL 4位二进制全加器74HC290 TTL 二/五分频十进制计数器74HC293 TTL 二/八分频四位二进制计数器74HC295 TTL 四位双向通用移位寄存器74HC298 TTL 四2输入多路带存贮开关74HC299 TTL 三态输出八位通用移位寄存器74HC30 TTL 8输入端与非门74HC32 TTL 2输入端四或门精选文档74HC322 TTL 带符号扩展端八位移位寄存器74HC323 TTL 三态输出八位双向移位/存贮寄存器74HC33 TTL 开路输出2输入端四或非缓冲器74HC347 TTL BCD—7段译码器/驱动器74HC352 TTL 双4选1数据选择器/复工器74HC353 TTL 三态输出双4选1数据选择器/复工器74HC365 TTL 门使能输入三态输出六同相线驱动器74HC365 TTL 门使能输入三态输出六同相线驱动器74HC366 TTL 门使能输入三态输出六反相线驱动器74HC367 TTL 4/2线使能输入三态六同相线驱动器74HC368 TTL 4/2线使能输入三态六反相线驱动器74HC37 TTL 开路输出2输入端四与非缓冲器74HC373 TTL 三态同相八D锁存器74HC374 TTL 三态反相八D锁存器74HC375 TTL 4位双稳态锁存器74HC377 TTL 单边输出公共使能八D锁存器74HC378 TTL 单边输出公共使能六D锁存器74HC379 TTL 双边输出公共使能四D锁存器74HC38 TTL 开路输出2输入端四与非缓冲器74HC380 TTL 多功能八进制寄存器74HC39 TTL 开路输出2输入端四与非缓冲器74HC390 TTL 双十进制计数器74HC393 TTL 双四位二进制计数器74HC40 TTL 4输入端双与非缓冲器精选文档74HC42 TTL BCD—十进制代码转换器74HC352 TTL 双4选1数据选择器/复工器74HC353 TTL 三态输出双4选1数据选择器/复工器74HC365 TTL 门使能输入三态输出六同相线驱动器74HC366 TTL 门使能输入三态输出六反相线驱动器74HC367 TTL 4/2线使能输入三态六同相线驱动器74HC368 TTL 4/2线使能输入三态六反相线驱动器74HC37 TTL 开路输出2输入端四与非缓冲器74HC373 TTL 三态同相八D锁存器74HC374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74447 TTL BCD—7段译码器/驱动器7445 TTL BCD—十进制代码转换/驱动器74450 TTL 16:1多路转接复用器多工器精选文档74451 TTL 双8:1多路转接复用器多工器74453 TTL 四4:1多路转接复用器多工器7446 TTL BCD—7段低有效译码/驱动器74460 TTL 十位比较器74461 TTL 八进制计数器74465 TTL 三态同相2与使能端八总线缓冲器74466 TTL 三态反相2与使能八总线缓冲器74467 TTL 三态同相2使能端八总线缓冲器74468 TTL 三态反相2使能端八总线缓冲器74469 TTL 八位双向计数器7447 TTL BCD—7段高有效译码/驱动器7448 TTL BCD—7段译码器/内部上拉输出驱动74490 TTL 双十进制计数器74491 TTL 十位计数器74498 TTL 八进制移位寄存器7450 TTL 2-3/2-2输入端双与或非门74502 TTL 八位逐次逼近寄存器74503 TTL 八位逐次逼近寄存器7451 TTL 2-3/2-2输入端双与或非门74533 TTL 三态反相八D锁存器74534 TTL 三态反相八D锁存器7454 TTL 四路输入与或非门74540 TTL 八位三态反相输出总线缓冲器7455 TTL 4输入端二路输入与或非门74563 TTL 八位三态反相输出触发器精选文档74564 TTL 八位三态反相输出D触发器74573 TTL 八位三态输出触发器74574 TTL 八位三态输出D触发器74645 TTL 三态输出八同相总线传送接收器74670 TTL 三态输出4×4寄存器堆7473 TTL 带清除负触发双J-K触发器7474 TTL 带置位复位正触发双D触发器7476 TTL 带预置清除双J-K触发器7483 TTL 四位二进制快速进位全加器7485 TTL 四位数字比较器7486 TTL 2输入端四异或门7490 TTL 可二/五分频十进制计数器7493 TTL 可二/八分频二进制计数器7495 TTL 四位并行输入\输出移位寄存器7497 TTL 6位同步二进制乘法器注:同型号的74系列、74HC系列、74LS系列芯片,逻辑功能上是一样的。

锁存器和寄存器的使用方法

锁存器和寄存器的使用方法一、引言在计算机领域中,锁存器(Latch)和寄存器(Register)是两个常见的存储器件。

它们在计算机的存储和处理数据过程中起着重要的作用。

本文将分别介绍锁存器和寄存器的使用方法。

二、锁存器的使用方法锁存器是一种用于存储数据的电子元件,它可以存储一个或多个比特的数据,并且可以保持数据的状态。

锁存器常用于存储中间结果、状态标志等临时数据。

1. 锁存器的结构和工作原理锁存器由触发器(Flip-Flop)构成,触发器是一种可以存储一个比特数据的电路。

触发器有多种类型,如D触发器、JK触发器等。

其中,D触发器是最常用的一种。

2. 锁存器的使用场景锁存器常用于存储中间结果,以便在需要时能够保持数据的状态。

比如,在计算机的算术逻辑单元(ALU)中,使用锁存器来存储运算结果。

另外,锁存器还可以用于存储状态标志,如溢出标志、零标志等。

3. 锁存器的使用方法使用锁存器时,首先需要确定所需存储的数据的位数。

然后,选择合适的触发器类型,并按照需要的功能进行连接。

连接后,可以通过控制信号来写入数据或读取数据。

对于多位数据存储,可以使用多个锁存器进行级联。

三、寄存器的使用方法寄存器是一种用于存储和处理数据的电子元件,它可以存储多个比特的数据,并且可以进行运算和逻辑操作。

寄存器是计算机中最常见的存储器件之一。

1. 寄存器的结构和工作原理寄存器由多个触发器构成,通常是由多个D触发器级联而成。

每个触发器可以存储一个比特的数据。

寄存器还包含一些控制逻辑,用于实现不同的功能。

2. 寄存器的使用场景寄存器广泛应用于计算机的数据处理过程中。

它可以用于存储操作数、存储运算结果、存储地址等。

在计算机的指令执行过程中,寄存器起着至关重要的作用。

3. 寄存器的使用方法使用寄存器时,首先需要确定所需存储的数据的位数。

然后,选择合适的寄存器类型,并按照需要的功能进行连接。

连接后,可以通过控制信号来写入数据、读取数据或进行运算操作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

锁存器使用总结

本文要点

1:锁存器的主要作用

2:74HC573引脚图

3:74HC573电路连接及使用说明

锁存器辨析

所谓锁存器,就是输出端的状态不会随输入端的状态变化而变化,仅在有锁存信号时输入的状态被保存到输出,直到下一个锁存信号到来时才改变。

典型的锁存器逻辑电路是 D 触发器电路。

PS:锁存信号(即对LE赋高电平时Data端的输入信号)。

锁存,就是把信号暂存以维持某种电平状态。

锁存器的最主要作用

1:缓存、

2:完成高速的控制其与慢速的外设的不同步问题、

3:是解决驱动的问题(提供的电流比51IO口输出电流大)

4:拓展I/O口(可以很猥琐的用锁存器幂叠加方法,即锁存器的Q再接锁存器~ 实现IO口的无限拓展···)

锁存器应用实例:

I/O口复用:当单片机连接片外存储器时,要接上锁存器,这是为了实现地址的复用。

假设,MCU 端口其中的8 路的I/O 管脚既要用于地址信号又要用于数据信号,这时就可以用锁存器先将地址锁存起来。

(具体操作:先送地址信息,由ALE使能锁存器将地址信息锁存在外设的地址端,然后送数据信息和读写使能信号,在指定的地址进行读写操作)

如果单片机的总线接口只作一种用途,不需要接锁存器;如果单片机的总线接口要作两种用途,就要用到锁存器。

例如:一个I/O口要控制两个LED,对第一个LED 送数据时,“打开”第一个锁存器而“锁住”第二个锁存器,使第二个LED 上的数据不变。

对第二个LED 送数据时,“打开”第二个锁存器而“锁住”第一个锁存器,使第一个LED 上的数据不变。

如果单片机的一个口要做三种用途,则可用三个锁存器,操作过程相似。

就这一种用法而言,可以把锁存器视为单片机的I/O 口的扩展器。

74HC573引脚分布图

由上边这个真值表可以看出:OE为高时,输出始终为高阻态,此时芯片处于不可控制状态,所以在一般应用中,我们必须将OE接低电平。

LE则是输出端状态改变使能端,当LE为低电平,输出端Q始终保持上一次存储的信号(从D端输入),当LE为高电平时,Q紧随D的状态变化,并将D的状态锁存。

也就是说当锁存使能端LE为高时,这些器件的锁存对于数据是透明的(也就是说输出同步)。

当锁存使能变低时,符合建立时间和保持时间的数据会被锁存。

另外:对锁存器的输入是和标准CMOS 输出兼容的;若再加上上拉电阻,他们能和

LS/ALSTTL 输出兼容。

锁存器的电路连接及使用详解:

(结合上面的锁存器引脚说明)

0:vcc gnd供电不用多说吧?

1:OE接地

2:D0-D7接我们的信号发射端(一般为单片机用来传输数据的I/O口)

3:Q0-Q7接我们要接受信息的终端(数码管,液晶,or anyother device)

4:LE接一个I/O口(此I/O脚可视为锁存器锁存功能的开关,高电平为更新Q端信号(要更新的信号从D输入)低电平则不更新)。