74HC573(八进制3 态非反转透明锁存器)

最新74HC573单片机应用

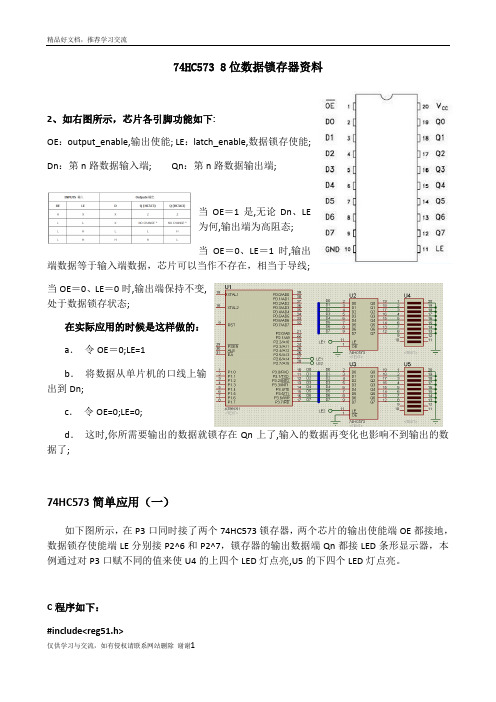

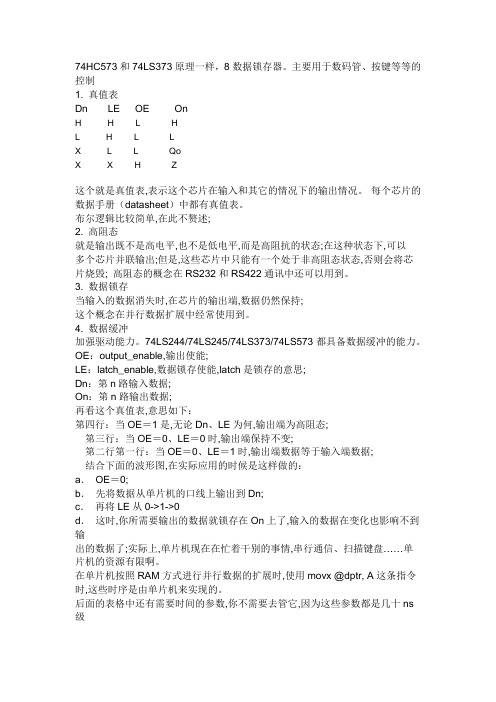

74HC573 8位数据锁存器资料2、如右图所示,芯片各引脚功能如下:OE:output_enable,输出使能; LE:latch_enable,数据锁存使能;Dn:第n路数据输入端; Qn:第n路数据输出端;当OE=1是,无论Dn、LE为何,输出端为高阻态;当OE=0、LE=1时,输出端数据等于输入端数据,芯片可以当作不存在,相当于导线;当OE=0、LE=0时,输出端保持不变,处于数据锁存状态;在实际应用的时候是这样做的:a.令OE=0;LE=1b.将数据从单片机的口线上输出到Dn;c.令OE=0;LE=0;d.这时,你所需要输出的数据就锁存在Qn上了,输入的数据再变化也影响不到输出的数据了;74HC573简单应用(一)如下图所示,在P3口同时接了两个74HC573锁存器,两个芯片的输出使能端OE都接地,数据锁存使能端LE分别接P2^6和P2^7,锁存器的输出数据端Qn都接LED条形显示器,本例通过对P3口赋不同的值来使U4的上四个LED灯点亮,U5的下四个LED灯点亮。

C程序如下:#include<reg51.h>sbit LE1=P2^6;sbit LE2=P2^7;void main(){LE1=1;P3=0X0F;LE1=0; //开启锁存功能,使U2输出端锁存数据0X0FLE2=1;P3=0XF0;LE2=0; //开启锁存功能,使U3输出端锁存数据0XF0while(1);}74HC573简单应用(二)两片74HC573的数据输入端同时接到P0口,输出使能端OE都接地,数据锁存端LE分别接到P2^6和P2^7,U2的数据输出端接六个数码管的段码,U3的数据输出端接六个数码管的位码。

本例使六个数码管同时循环点亮0到9十个数字。

C程序如下:#include<reg51.h>#define uchar unsignedc har#define uint unsigned int//延时函数void delay(uint x){uchar i;while(x--)for(i=0;i<120;i++);}//0到9的共阴显示代码uchar code dis[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,0x7f,0x6f}; sbit LE1=P2^6;sbit LE2=P2^7;uchar i;void main(){ LE2=1;P0=0XC0;LE2=0;while(1){LE1=1;P0=dis[i];LE1=0;delay(400);//延时1s左右i=(i+1)%10;//i取值为0到9}}木兰诗北朝民歌唧(jī)唧复唧唧,木兰当户织。

74HC573中文资料

74HC573和74LS373原理一样,8数据锁存器。

主要用于数码管、按键等等的控制1. 真值表Dn LE OE OnH H L HL H L LX L L QoX X H Z这个就是真值表,表示这个芯片在输入和其它的情况下的输出情况。

每个芯片的数据手册(datasheet)中都有真值表。

布尔逻辑比较简单,在此不赘述;2. 高阻态就是输出既不是高电平,也不是低电平,而是高阻抗的状态;在这种状态下,可以多个芯片并联输出;但是,这些芯片中只能有一个处于非高阻态状态,否则会将芯片烧毁; 高阻态的概念在RS232和RS422通讯中还可以用到。

3. 数据锁存当输入的数据消失时,在芯片的输出端,数据仍然保持;这个概念在并行数据扩展中经常使用到。

4. 数据缓冲加强驱动能力。

74LS244/74LS245/74LS373/74LS573都具备数据缓冲的能力。

OE:output_enable,输出使能;LE:latch_enable,数据锁存使能,latch是锁存的意思;Dn:第n路输入数据;On:第n路输出数据;再看这个真值表,意思如下:第四行:当OE=1是,无论Dn、LE为何,输出端为高阻态;第三行:当OE=0、LE=0时,输出端保持不变;第二行第一行:当OE=0、LE=1时,输出端数据等于输入端数据;结合下面的波形图,在实际应用的时候是这样做的:a.OE=0;b.先将数据从单片机的口线上输出到Dn;c.再将LE从0->1->0d.这时,你所需要输出的数据就锁存在On上了,输入的数据在变化也影响不到输出的数据了;实际上,单片机现在在忙着干别的事情,串行通信、扫描键盘……单片机的资源有限啊。

在单片机按照RAM方式进行并行数据的扩展时,使用movx @dptr, A这条指令时,这些时序是由单片机来实现的。

后面的表格中还有需要时间的参数,你不需要去管它,因为这些参数都是几十ns级别的,对于单片机在12M下的每个指令周期最小是1us的情况下,完全可以实现;如果是你自己来实现这个逻辑,类似的指令如下:mov P0,A ;将数据输出到并行数据端口clr LEsetb LEclr LE ;上面三条指令完成LE的波形从0->1->0的变化74ls573跟74LS373逻辑上完全一样,只不过是管脚定义不一样,数据输入和输出端。

74hc573在应用电路作用解析 74hc573驱动数码管动态扫描

74hc573在应用电路作用解析74hc573驱动数码管动态扫描74HC573D是8位三态锁存器,一般在实际应用电路中用于地址或数据的锁存。

本文主要探讨了74HC573D在实际应用电路中的作用以及如何驱动数码管动态显示,下面就来一一介绍74HC573D。

大家都知道74HC573D是一种锁存器,那么锁存器是干嘛用的呢?锁存器辨析所谓锁存器,就是输出端的状态不会随输入端的状态变化而变化,仅在有锁存信号时输入的状态被保存到输出,直到下一个锁存信号到来时才改变。

典型的锁存器逻辑电路是D 触发器电路。

PS:锁存信号(即对LE赋高电平时Data端的输入信号)。

锁存,就是把信号暂存以维持某种电平状态。

锁存器的最主要作用1:缓存、2:完成高速的控制其与慢速的外设的不同步问题、3:是解决驱动的问题(提供的电流比51IO口输出电流大)4:拓展I/O口(可以很猥琐的用锁存器幂叠加方法,即锁存器的Q再接锁存器~ 实现IO 口的无限拓展···)锁存器应用实例:I/O口复用:当单片机连接片外存储器时,要接上锁存器,这是为了实现地址的复用。

假设,MCU 端口其中的8 路的I/O 管脚既要用于地址信号又要用于数据信号,这时就可以用锁存器先将地址锁存起来。

(具体操作:先送地址信息,由ALE使能锁存器将地址信息锁存在外设的地址端,然后送数据信息和读写使能信号,在指定的地址进行读写操作)如果单片机的总线接口只作一种用途,不需要接锁存器;如果单片机的总线接口要作两种用途,就要用到锁存器。

例如:一个I/O口要控制两个LED,对第一个LED 送数据时,“打开”第一个锁存器而“锁住”第二个锁存器,使第二个LED 上的数据不变。

对第二个LED 送数据时,“打开”第二个锁存器而“锁住”第一个锁存器,使第一个LED 上的数据不变。

如果单片机的一个口要做三种用途,则可用三个锁存器,操作过程相似。

就。

(完整word版)74HC573功能说明(原创编辑)0001

74CH573锁存器的功能74HC573和74LS373原理一样,8数据锁存器。

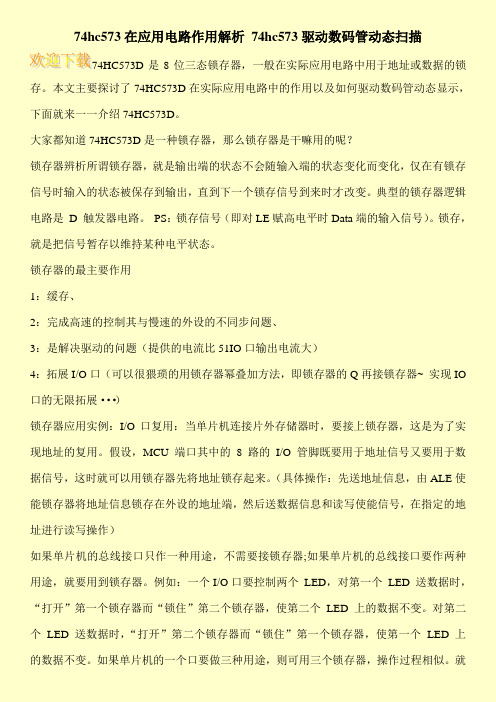

主要用于数码管、按键等等的控制 74HC573有20个脚,数据的进和出没有逻辑关系,这个芯片主要是看高电压激活还是低 电压激活:1是低电压激活芯片2~9脚是数据的输入脚从 DO 到D710脚是接地11脚是高电压激活芯片12~19脚是数据的输出脚20是电源SNS4HCS7 3A . . FK PACKAGE(TOP VIEW)1•真值表3 2 1 20 19 厂ZUIH E苛[ 171stOE1D益3D 4D5Dec0D GKD]^ec ]1Q]%]4a ]5Q ]7Q 1 5Q ■ ■ILEOurPLFT ENABLE乂>EXPAMJtD I 1MAC ;K\M3C4D 5 口 6D7D/ t_n_IT _re_r~ir~LT~u~~m2Q 3Q4Q50fid亡I □ Ld □口 B N —l 在 g功能範高阻抗74HC573真值表,意思如下:第一行/第二行:当0E = 0、LE = 1时,输出端数据等于输入端数据;第三行:当0E = 0、LE = 0时,输出端保持不变;第四行:当0E = 1是无论Dn、LE为何,输出端为高阻态;2. 高阻态就是输出既不是高电平,也不是低电平,而是高阻抗的状态;在这种状态下,可以多个芯片并联输出;但是,这些芯片中只能有一个处于非高阻态状态,否则会将芯片烧毁。

高阻态的概念在RS232和RS422通讯中还可以用到。

3. 数据锁存当输入的数据消失时,在芯片的输出端,数据仍然保持;这个概念在并行数据扩展中经常使用到。

4. 数据缓冲加强驱动能力:74LS244/74LS245/74LS373/74LS573 都具备数据缓冲的能力。

0E : output_enable,输出使能;LE : latch_enable,数据锁存使能,atch是锁存的意思;Dn :第n路输入数据;On :第n路输出数据;74HC573波形图,在实际应用的时候是这样做的:OE = 0;先将数据从单片机的口线上输出到 出的数据了;实际上,单片机现在在忙着干别的事情,串行通信、扫描键盘 片机的资源有限啊。

74hc573原理

74hc573原理74HC573是一种常用的集成电路芯片,属于高速CMOS逻辑系列。

它是一种8位透明锁存器,可以实现数据的存储和传输功能。

本文将介绍74HC573的原理和应用。

我们来了解一下74HC573的基本结构。

它由8个锁存器单元组成,每个单元都具有一个数据输入端(D)、一个时钟输入端(CK)和一个数据输出端(Q)。

这些单元可以独立地将数据存储在内部存储器中,并在时钟脉冲到达时将数据传输到输出端。

除此之外,74HC573还具有一个输出使能端( OE ),通过控制该端口的高低电平,可以使输出端的数据有效或者无效。

接下来,我们来看一下74HC573的工作原理。

当时钟输入端接收到一个信号时,数据输入端的数据会被存储在内部存储器中。

存储的数据可以通过数据输出端输出。

当输出使能端为高电平时,数据输出端的数据有效;当输出使能端为低电平时,数据输出端的数据无效。

通过控制输出使能端的状态,我们可以实现数据的读取和屏蔽操作。

那么,74HC573的应用有哪些呢?它广泛应用于数字电路中,特别是在数据存储和传输方面。

例如,在微处理器系统中,我们可以使用74HC573将数据从外部设备传输到微处理器中,或者将数据从微处理器传输到外部设备中。

它还可以用于存储数据,以便在需要时进行读取。

除了数据存储和传输外,74HC573还可以用于地址译码。

通过将地址线连接到74HC573的数据输入端,我们可以根据地址信号的不同将数据传输到不同的输出端。

这在存储器和外设的选择和控制中起着重要作用。

74HC573还可以用于时序控制。

通过控制时钟输入端和输出使能端的状态,我们可以实现对数据传输的控制。

例如,可以根据特定的时序要求将数据传输到其他模块,并在需要时将其输出。

总结一下,74HC573是一种功能强大的集成电路芯片,可以实现数据的存储和传输功能。

它广泛应用于数字电路中,特别是在数据存储、传输、地址译码和时序控制等方面。

通过灵活的控制和应用,我们可以实现不同的功能需求。

74hc573和74hc595有什么不同?该怎样区分74hc573和74hc595

74hc573 和74hc595 有什么不同?该怎样区分

74hc573 和74hc595

这是两种完全不同的器件,74hc573 是个锁存器,而74hc595 则是一个串转并的芯片。

虽然它俩都能节约外部引脚及增大驱动能力,但不是不同点还是大于相同点的,本文是要比较74hc573 和74hc595 的不同点,看看它俩差别在哪些地方。

74hc573

74HC573 是拥有八路输出的透明锁存器,输出为三态门,是一种高性能硅栅CMOS 器件。

器件的输入是和标准CMOS 输出兼容的,加上拉电阻他们能和LS/ALSTTL 输出兼容。

八进制3 态非反转透明锁存器+74HC573+高性能硅门CMOS 器件+SL74HC573 跟LS%2FAL573 的管脚一样。

器件的输入是和标准CMOS 输出兼容+的;加上拉电阻,他们能和LS%2FALSTTL 输出兼容。

当锁存使能端为高时,这些器件的锁存对于数据是透明的(也就是说输出同步)。

当锁存使能变低时,符合建立时间和保持时间的数据会被锁存。

74HC_HCT573 三态锁存器

Octal D-type transparent latch; 3-state

Rev. 7 — 4 March 2016 Product data sheet

1. General description

The 74HC573; 74HCT573 is an 8-bit D-type transparent latch with 3-state outputs. The device features latch enable (LE) and output enable (OE) inputs. When LE is HIGH, data at the inputs enter the latches. In this condition the latches are transparent, a latch output will change each time its corresponding D-input changes. When LE is LOW the latches store the information that was present at the inputs a set-up time preceding the HIGH-to-LOW transition of LE. A HIGH on OE causes the outputs to assume a high-impedance OFF-state. Operation of the OE input does not affect the state of the latches. Inputs include clamp diodes. This enables the use of current limiting resistors to interface inputs to voltages in excess of VCC.

74HC573中文资料

6.0

VIN=VCC 或者 GND

6.0

高阻抗态下的输出 6.0

VIN=VIH 或者 VIL,

VOUT=VCC 或者 GND

VIN=VCC 或者 GND

6.0

IOUT=0uA

3.15 3.15 3.15 4.2 4.2 4.2 0.5 0.5 0.5 V 1.35 1.35 1.35 1.8 1.8 1.8 1.9 1.9 1.9 V 4.4 4.4 4.4 5.9 5.9 5.9

6.0

VIN=VIH 或者 VIL,

2.0

|IOUT|≤20uA

4.5

6.0Biblioteka VIN=VIH 或者 VIL,

|IOUT|≤6.0mA

4.5

|IOUT|≤7.8mA

6.0

VIN=VIH 或者 VIL,

2.0

|IOUT|≤20uA

4.5

6.0

VIN=VIH 或者 VIL,

|IOUT|≤6.0mA

4.5

|IOUT|≤7.8mA

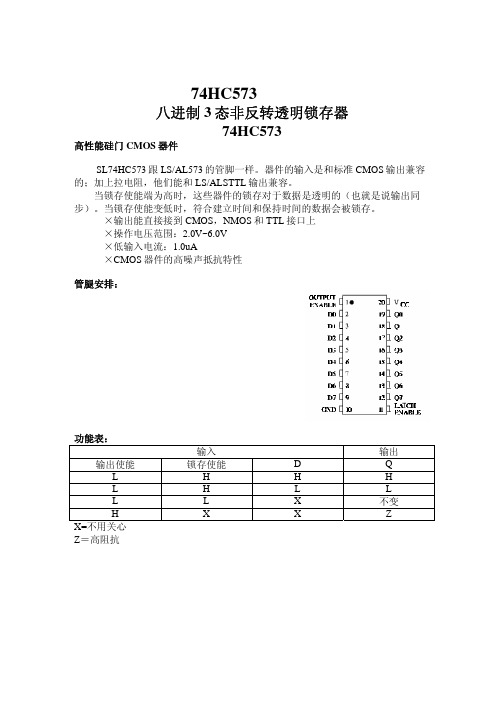

×输出能直接接到 CMOS,NMOS 和 TTL 接口上 ×操作电压范围:2.0V~6.0V ×低输入电流:1.0uA ×CMOS 器件的高噪声抵抗特性

管腿安排:

功能表:

输入

输出使能

锁存使能

D

L

H

H

L

H

L

L

L

X

H

X

X

X=不用关心

Z=高阻抗

输出 Q H L

不变 Z

http://www.elecfans.com

符号

参数

VCC

条件限制

单

V 25℃~ ≤85 ≤125 位

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

4.5

6.0

VIN=VIH 或者 VIL,

|IOUT|≤6.0mA

4.5

|IOUT|≤7.8mA

6.0

VIN=VIH 或者 VIL,

2.0

|IOUT|≤20uA

4.5

6.0

VIN=VIH 或者 VIL,

|IOUT|≤6.0mA

4.5

|IOUT|≤7.8mA

6.0

VIN=VCC 或者 GND

6.0

高阻抗态下的输出 6.0

最大 6.0 VCC +125 1000 500 400

单位 V V ℃ ns

这个器件带有保护电路,以免被高的静态电压或电场损坏。然而,对于高阻抗

电路,必须要采取预防以免工作在任何高于最大值范围的条件下工作。VIN 和 VOUT 应该被约束在 GND≤(VIN 或 VOUT)≤VCC。

不用的输入管腿必须连接总是连接到一个适合的逻辑电压电平(也就是 GND

VIN=VIH 或者 VIL,

VOUT=VCC 或者 GND

VIN=VCC 或者 GND

6.0

IOUT=0uA

3.15 3.15 3.15 4.2 4.2 4.2 0.5 0.5 0.5 V 1.35 1.35 1.35 1.8 1.8 1.8 1.9 1.9 1.9 V 4.4 4.4 4.4 5.9 5.9 5.9

6.0

26

33

38

tTLH, 任何输出的最大输出延迟(图 2.0

60

75

90 ns

tTHL

1 和图 5)

4.5

12

15

18

6.0

10

13

15

CIN

最大输入电容

-

10

10

10 pF

COUT 最大三态输出电容(在高阻态 -

15

15

15 pF

下的输出)

CPD

功耗电容(使能所有输出)

典型在 25℃,VCC=5V 条件下 pF

SOIC:-7 mW/℃ ,65℃~125℃

推荐操作条件: 符号 VCC

VIN,VOUT TA tr,tf

参数 DC 供电电压(参考 GND) DC 输入电压,输出电压(参考 GND)

所有封装的操作温度 输入上升和下降时间 VCC=2.0V

VCC=4.5V VCC=6.0V

最小 2.0 0 -55 0 0 0

用于确定没有负载时的动态功

23

耗:

时序要求(CL=50pF,输入 符号 参数

):

VCC V

tSU 输入 D 到锁存使能最小建立时 2.0

间(图 4)

4.5

6.0

th

锁存使能到输入 D 最小保持时 2.0

间(图 4)

4图 2) 2.0

4.5

6.0

tr ,tf 最大输入上升沿和下降沿时序 2.0

(图 1)

4.5

6.0

限制条件 25℃~- 55℃

50 10 9 5 5 5 75 15 13 1000 500 400

≤85 ℃

65 13 11 5 5 5 95 19 16 1000 500 400

单

≤125 位 ℃

75

ns

15

13

5

ns

5 5

110 ns 22 19

1000 ns 500 400

74HC573

八进制 3 态非反转透明锁存器

高性能硅门 CMOS 器件

SL74HC573 跟 LS/AL573 的管脚一样。器件的输入是和标准 CMOS 输出兼容 的;加上拉电阻,他们能和 LS/ALSTTL 输出兼容。

当锁存使能端为高时,这些器件的锁存对于数据是透明的(也就是说输出同 步)。当锁存使能变低时,符合建立时间和保持时间的数据会被锁存。

符号

参数

VCC

条件限制

单

V 25℃~ ≤85 ≤125 位

-55℃ ℃

℃

tPLH, 输入 D 到 Q,最大延迟(图 1 2.0

150

190 225 ns

tPHL

和 5)

4.5

30

38

45

6.0

26

33

38

tPLH, 锁存使能到 Q 的最大延迟(图 2.0

160

200 240 ns

tPHL

2 和图 5)

值 -0.5~+7.0 -1.5~VCC+1.5 -0.5~VCC+0.5

20 35 75 750 500

-65~+150 260

单位 V V V mA mA mA mW

℃ ℃

*最大值范围是指超过这个值,将损害器件。 操作最好在下面的推荐操作条件下。 +额定功率的下降——PDIP:-10mW/℃ ,65℃~125℃

4.5

32

40

48

6.0

27

34

41

tPLZ, 输出使能到 Q 的最大延迟(图 2.0

150

190 225 ns

tPHZ

3 和图 6)

4.5

30

48

45

6.0

26

33

38

74HC573

tPZH, 输出使能到 Q 最大延迟(图 3 2.0

150

190 225 ns

tPZL

和图 6)

4.5

30

48

45

或者 VCC)。不用的输出管腿必须悬空。 DC 电子特性(电压是以 GND 为参考):

符号 参数

测试条件

VCC 条件限制

V 25

≤85

℃~ ℃

-55

单位 ≤125 ℃

℃

VIH 最小高 VOUT=0.1V 或者 VCC- 2.0 1.5

1.5

1.5

V

VIL VOH

电平输 入电压 最大低 电压输 入电压 最大高 电平输 出电压

VOL

最大低 电平输 出电压

IIN 最大输 入漏电 流

IOZ 最大三 态漏电 流

ICC 最大静 态供电 电流

74HC573

0.1V,

4.5

|IOUT|≤20uA

6.0

VOUT=0.1V 或者 VCC- 2.0

0.1V,

4.5

|IOUT|≤20uA

6.0

VIN=VIH 或者 VIL,

2.0

|IOUT|≤20uA

3.98 3.84 3.7 5.48 5.34 5.2 0.1 0.1 0.1 V 0.1 0.1 0.1 0.1 0.1 0.1

0.26 0.33 0.4 0.26 0.33 0.4 ±0.1 ±0.1 ±0.1 uA

±0.5 ±5.0 ±10 uA

4.0 4.0 4.0 uA

AC 电子特性(CL=50pF,输入 tr=tf=6.0ns):

×输出能直接接到 CMOS,NMOS 和 TTL 接口上 ×操作电压范围:2.0V~6.0V ×低输入电流:1.0uA ×CMOS 器件的高噪声抵抗特性

管腿安排:

功能表:

输入

输出使能

锁存使能

D

L

H

H

L

H

L

L

L

X

H

X

X

X=不用关心

Z=高阻抗

输出 Q H L

不变 Z

74HC573

最大值范围:

符号

参数

VCC VIN VOUT IIN

DC 供电电压(参考 GND) DC 输入电压(参考 GND) DC 输出电压(参考 GND) 每一个 PIN 的 DC 输入电流

IOUT

每一个 PIN 的 DC 输出电流

ICC

DC 供电电流,VCC 和 GND 之间

PD

在自然环境下,PDIP 和 SOIC 封装下的

功耗

Tstg

存储温度

TL

引线温度,10 秒(PDIP,SOIC)

74HC573

逻辑图:

74HC573