Xilinx的FPGA和CPLD烧写步骤Xilinx ISE10.1

FPGA烧写的方式和具体过程分析

FPGA烧写的方式和具体过程分析做了三年四个项目最近才第一次需要深入的搞一下FPGA 烧写。

在这里简单总结一下FPGA烧写的具体过程和玩的花样大家常用的办法对于大部分人来说,至少入门时会用到的烧写方式就两种:① 通过JTAG直接将bitsteam 烧录到FPGA。

断电后信息丢失。

这种方式多用于发开调试阶段,板子一直连着电脑。

通过ISE 或者 Vivado (2020年开始估计还有Vitis)使用JTAG接口烧录。

② 在设计release以后,到产品上一般都是把配置文件通过IDE工具保存存在Nor Flash里。

上电后自动编程FPGA。

较为进阶的一种方法通常情况下这两种方式也就可以满足大部分需求了。

开发调试直接JTAG。

产品出货前,配置文件通过JTAG接口,用VIVADO或者SDK等工具烧进Flash。

之后把接口封起来。

产品需要更新的时候,派技术支持去,重新打开接口,插上JTAG,把新的配置文件烧入Flash。

但是这次项目是个小型手持测量设备,JTAG接口只有在设备拆散状态下通过扩展板才能使用。

组装好后FPGA只能通过Flash来编程。

由于是个精密仪器,每次拆开再组装,整个设备都需要重新校准,非常费事费力。

组装后更新Flash里面的配置文件只能用别的办法了。

这种情况下常用的方法是通过一个和外界有通信能力的微控制器将image发送给FPGA,再由FPGA写入Flash。

这种remote update Xilinx提供了一种解决方案,相对应的ApplicaTIon Note 是:QuickBoot Method for FPGA DesignRemote Update (文档号码XAPP1081)采用这种方案的前提是理解FPGA通过Flash配置的细节,所以以7系FPGA为例先需要看一下这个文档:7 Series FPGAsConfiguraTIon (UG470)主要是看第五章:Chapter 5 ConfiguraTIon DetailsXilinx 远程烧录FPGA方法远程烧录一般是为了设备出厂以后还需对FPGA进行更新或者升级。

ISE10.1使用教程简介

ISE 10.1Steps1 new project (1)2 new source (3)3 run behavior simulation (5)4 ChipScope (7)5 Constraints (12)6 synthesize your design (13)7 implement your design (13)8 Generate Programming File (13)9Analyze Design Using Chipscope (13)1 new project1. 双击桌面Xilinx ISE10.1 快捷方式打开ISE 工程管理器(Project Navigator)。

2. 打开 Project Navigator 后,选择File → New Project ,弹出新建工程对话框,填写工程名字,工程存放发热位置。

注意,不要填写含有中文的名字,以免发生错误。

3.点击 Next 按钮,弹出器件特性对话框。

Device Family选择“Virtex2P”,Device选“XC2VP30 ,Package选择ff896,Speed选 -7”,其他选择如下图所示。

其中这些选择由按FPGA开发板的型号来决定的。

然后点击NEXT,继续单击Next 按钮,然后单击Finish按钮完成对工程的建立和基本设置。

2 new source1在工程的Source for下在的空白处单击右键选择New Source菜单2然后在弹出的对话框中选择Verilog Module,并且在右边的File name中输入你的模块名称,然后单击Next按钮。

2.这是一个设置输入输出端口的对话框,可以设置,也可以不设置。

一般选择不设置,直接点击NEXT,最后单击Finish按钮完成成对Verilog Module模块资源的添加。

3.双击Source for下面的.v文件(本实验双击counter.v)进入源代码编辑框中,并在里面编写Verilog源程序,然后点击保存按钮。

赛灵思ise10.1XP下安装说明

ISE10.1 安装使用说明(FOR XP)打开安装文件夹双击setup.exe.出现欢迎界面:

点击Next。

出现如下界面

选择安装文件夹内的序列号文本文档复制序列号到该界面ID框内。

点击next。

进入选择安装产品界面,按默认的选择直接点击next即可。

进入如下界面,在I accept……该栏打钩(如图),点击next。

继续打钩点击next进入安装路径选择界面:

选择您想要安装到的路径,以及开始菜单的名称。

然后点击next。

一直点击next(中间过程默认选择即可)直到出现以下界面:

点击Install,等待安装,安装过程中尽量不要做其他操作,以防电脑

死机造成安装失败。

安装大约十分钟左右会出现如下窗口

选择choose later 继续安装,稍带出现如下

点击next安装winpcap插件,一路点击next直到出现如下界面

点击I agree 继续安装中间过程可能会出现防火墙报警,选择允许一直到安装完成。

出现升级界面

选择cancel,安装完成。

ISE10.1使用教程简介

ISE 10.1Steps1 new project (1)2 new source (3)3 run behavior simulation (5)4 ChipScope (7)5 Constraints (12)6 synthesize your design (13)7 implement your design (13)8 Generate Programming File (13)9Analyze Design Using Chipscope (13)1 new project1. 双击桌面Xilinx ISE10.1 快捷方式打开ISE 工程管理器(Project Navigator)。

2. 打开 Project Navigator 后,选择File → New Project ,弹出新建工程对话框,填写工程名字,工程存放发热位置。

注意,不要填写含有中文的名字,以免发生错误。

3.点击 Next 按钮,弹出器件特性对话框。

Device Family选择“Virtex2P”,Device选“XC2VP30 ,Package选择ff896,Speed选 -7”,其他选择如下图所示。

其中这些选择由按FPGA开发板的型号来决定的。

然后点击NEXT,继续单击Next 按钮,然后单击Finish按钮完成对工程的建立和基本设置。

2 new source1在工程的Source for下在的空白处单击右键选择New Source菜单2然后在弹出的对话框中选择Verilog Module,并且在右边的File name中输入你的模块名称,然后单击Next按钮。

2.这是一个设置输入输出端口的对话框,可以设置,也可以不设置。

一般选择不设置,直接点击NEXT,最后单击Finish按钮完成成对Verilog Module模块资源的添加。

3.双击Source for下面的.v文件(本实验双击counter.v)进入源代码编辑框中,并在里面编写Verilog源程序,然后点击保存按钮。

FPGA程序烧写流程

F P

G A程序下载方法

(1)设备上电;

(2)双击IMPACT,打开下载软件,界面如图1.1所示。

图1.1IMPACT界面

(3)选择“Loadmostresentproject”,单击“Browse”,选择解压目录里的“FPGA.ipf”,

如图1.2所示。

图1.2路径选择界面

单击“打开”,在弹出的窗口中双击左边的PROMFileFormater,如图1.3所示。

图1.3IMPACT选择窗口界面

在弹出的窗口选择XilinxPROM文件格式选择mcs,PROMFilename为:test.mcs.选择好保存路径进行下一步,如图1.4所示。

图1.4文件选择窗口

点击下一步,选择PROM(bits),选择XC3S1000,点击Add,Finish,会有一个选择bit文件的窗口,选择一个已经编好的EDK或者ISE工程生成的.bit文件,OK后提示是否加入其它器件,选择NO,然后双击窗口右边的GenerateFile,生成.mcs文件,如图1.5所示。

图1.5PROMFileFormater窗口

双击BoundaryScan,在空白处,点击鼠标右键,选择Initializechain,弹出的第一个窗口选择Bypass,第二个选择刚才生成的.mcs文件,第三个也选择Bypass,然后选中间那个模块,点击窗口左下角的program,如图1.6所示。

弹出窗口选中OK就可以了,烧写完后会看到,ProgramSuccessful提示,程序下载完成。

图1.6BoundaryScan选择窗口。

测试方法FPGA,CPLD,烧写,烧录,测试

CZC100上电测试过程详解

一、准备工具

5V恒压源

直流万用表

二、过程

三、先按测试报告要求测试是否存在短路

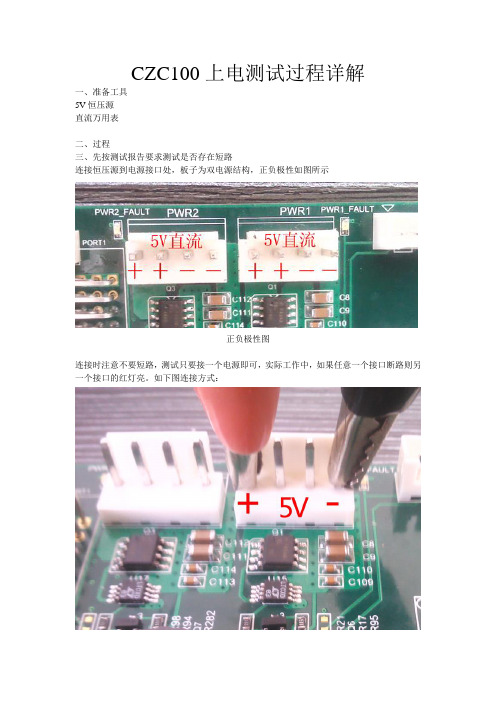

连接恒压源到电源接口处,板子为双电源结构,正负极性如图所示

正负极性图

连接时注意不要短路,测试只要接一个电源即可,实际工作中,如果任意一个接口断路则另一个接口的红灯亮。

如下图连接方式:

我接的右边的接口,左面的pwr2 led灯亮了,如下:

按测试报告要求对元器件进行短路以及电压测试,下图给出部分待测元器件的位置以及测量值范围

根据要求完成测试,做好记录,关闭电源。

Vivado安装、生成bit文件及烧录FPGA的简要流程

使用Vivado制作FPGA的简要流程一、在Windows下安装Xilinx Vivado Design Suite:1.1.Xilinx Vivado Design Suite安装文件,解压后得到安装目录:1.2.运行xsetup.exe文件,进入安装程序。

如果提示要更新就直接点continue关掉。

1.3.选一些根本看都不会看的I agree.1.4.选第二个或者第三个应该都可以。

我感觉第三个看起来更加高大上一点,我就选了第三个:1.5.直接点next:1.6.选择路径,稍等片刻就能安装完成:1.7.安装完成后,在开始菜单找到Xilinx Design Tools\Vivado2014.3文件夹,打开Manage Xilinx Licenses:1.8.打开后选择左边的load license选项卡:1.9.点击copy license,选中刚才安装目录中的crack文件夹中的license.lic:1.10.至此Windows下的Xilinx Vivado Design Suite已经全部安装完成。

二、在服务器中使用Vivado生成bit文件:2.0.由于综合和布局布线需要较好的硬件资源,所以本次流程中综合和布局布线在linux环境的服务器中完成。

在linux环境中运行vivado请确保正确安装JVM,在Windows环境下图形界面流程完全一致。

2.1.在服务器上正确安装JVM后执行以下指令:2.2.执行“Vivado&”打开Vivado。

注意Vivado会在你执行这条命令的目录下生成一些log 信息,所以最好新建一个目录再打开Vivado:2.3.点击Create New Project建立新的项目,在弹出的对话框中点Next:2.4.输入项目名称,然后再点击Next:2.5.选择项目类型,因为我们要从RTL代码开始综合,因此选择RTL Project。

下面的Do not specify source at this time的勾也可以打上。

CPLD烧写方法 FPGA,CPLD,烧写,烧录,测试

CPLD烧写步骤

一、前期准备:

1、要烧写的CPLD程序

2、电脑以及相关软件以及下载器驱动(默认自动安装)。

3、下载工具以及连接线

二、连线方式:通过连接线连接下载器和J2接口,连接的时候注意1口对1口连接,连接错误将导致无法下载。

左图中三角号对应的是1脚,连接图示下载器1脚,另一端连接P3的1脚,下载器另一端连接到笔记本的usb接口上。

下载线以及下载器

接口示意图

下面是连接后的示意图

连接示意图

三、下载方法

连好线后,打开XILINX工具软件,默认在开始-所有程序菜单里,如下图

xilinx打开路径图

点击文件-新建工程

然后会弹出一个对话框,这时候点yes,然后点ok。

下面添加烧写的程序,在空白处右击,选择如图示

然后选择要烧写的jed程序

选择后,在添加的程序上右击,选择programmer进行烧写。

等待提示success。

如果failed请检查连线是否松动尝试重复烧写几次。