si9979控制器资料

AD9959数据手册部分内容中文翻译

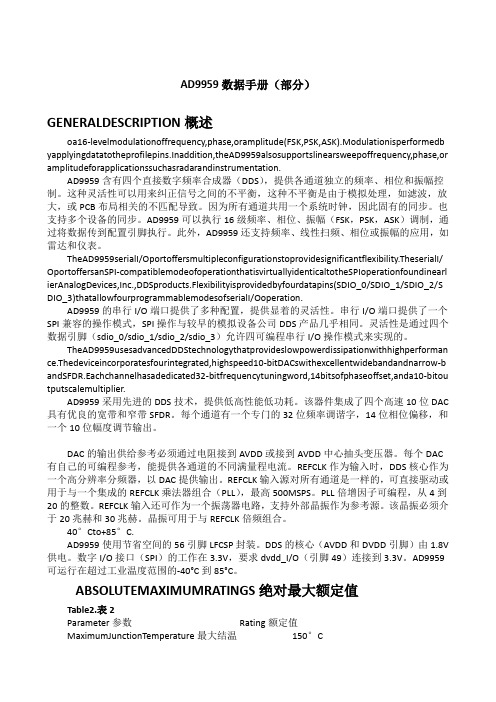

AD9959数据手册(部分)GENERALDESCRIPTION概述oa16-levelmodulationoffrequency,phase,oramplitude(FSK,PSK,ASK).Modulationisperformedb yapplyingdatatotheprofilepins.Inaddition,theAD9959alsosupportslinearsweepoffrequency,phase,or amplitudeforapplicationssuchasradarandinstrumentation.AD9959含有四个直接数字频率合成器(DDS),提供各通道独立的频率、相位和振幅控制。

这种灵活性可以用来纠正信号之间的不平衡,这种不平衡是由于模拟处理,如滤波,放大,或PCB布局相关的不匹配导致。

因为所有通道共用一个系统时钟,因此固有的同步。

也支持多个设备的同步。

AD9959可以执行16级频率、相位、振幅(FSK,PSK,ASK)调制,通过将数据传到配置引脚执行。

此外,AD9959还支持频率、线性扫频、相位或振幅的应用,如雷达和仪表。

TheAD9959serialI/Oportoffersmultipleconfigurationstoprovidesignificantflexibility.TheserialI/ OportoffersanSPI-compatiblemodeofoperationthatisvirtuallyidenticaltotheSPIoperationfoundinearl ierAnalogDevices,Inc.,DDSproducts.Flexibilityisprovidedbyfourdatapins(SDIO_0/SDIO_1/SDIO_2/S DIO_3)thatallowfourprogrammablemodesofserialI/Ooperation.AD9959的串行I/O端口提供了多种配置,提供显着的灵活性。

997 中文维修手册

997 中文维修手册

【原创版】

目录

1.7809 稳压管概述

2.7809 稳压管的工作原理

3.7809 稳压管的电压差

4.7809 稳压管的应用领域

5.结论

正文

7809 稳压管是一种常用的集成电路,具有稳定的输出电压,广泛应用于电子设备中。

其工作原理是通过内部的调整电阻,将输入电压转化为稳定的输出电压,以供电子设备使用。

7809 稳压管的电压差指的是其输入电压与输出电压之间的差值。

根据其型号和制造厂家的不同,电压差可能会有所不同。

一般来说,7809 稳压管的电压差在 1~2V 之间。

7809 稳压管广泛应用于各种电子设备中,如电源供应器、充电器、电视机、收音机等。

其稳定的输出电压可以保证电子设备的正常工作,提高设备的可靠性和稳定性。

综上所述,7809 稳压管是一种重要的电子元器件,其电压差是其重要的性能指标之一。

调速器硬件手册

ETD 790直流调速器

页码:2 /86

ETD 790直流调速器 电流预测控制

6.4e 模拟输出 .............................................................................................................. 39 6.4f 422/485串行口....................................................................................................... 41 6.4g 直流测速电机反馈接线 ......................................................................................... 42 6.4h 用于指示输入和输出的LED指示器 ....................................................................... 43 6.5 RS 232、CAN总线、编码器1、编码器2的连接器....................................................

L297 L298的中文资料

L297-L298中文资料L297的工作原理介绍L297是意大利SGS半导体公司生产的步进电机专用控制器,它能产生4相控制信号,可用于计算机控制的两相双极和四相单相步进电机,能够用单四拍、双四拍、四相八拍方式控制步进电机。

芯片内的PWM斩波器电路可开关模式下调节步进电机绕组中的电机绕组中的电流。

该集成电路采用了SGS公司的模拟/数字兼容的I2L技术,使用5V的电源电压,全部信号的连接都与TFL/CMOS或集电极开路的晶体管兼容。

L297的芯片引脚特别紧凑,采用双列直插20脚塑封封装,其引脚见图1,内部方框见图2。

在图2所示的L297的内部方框图中。

变换器是一个重要组成部分。

变换器由一个三倍计算器加某些组合逻辑电路组成,产生一个基本的八格雷码(顺序如图3所示)。

由变换器产生4个输出信号送给后面的输出逻辑部分,输出逻辑提供禁止和斩波器功能所需的相序。

为了获得电动机良好的速度和转矩特性,相序信号是通过2个PWM斩波器控制电动波器包含有一个比较器、一个触发器和一个外部检测电阻,如图4所示,晶片内部的通用振荡器提供斩波频率脉冲。

每个斩波器的触发器由振荡器的脉冲调节,当负载电流提高时检测电阻上的电压相对提高,当电压达到Uref时(Uref是根据峰值负载电流而定的),将触发器重置,切断输出,直至第二个振荡脉冲到来、此线路的输出(即触发器Q输出)是一恒定速率的PWM信号,L297的CONTROL端的输入决定斩波器对相位线A,B,C,D或抑制线INH1和INH2起作用。

CONTROL 为高电平时,对A,B,C,D有抑制作用;为低电平时,则对抑制线INH1和INH2有抑制作用,从而可对电动机和转矩进行控制。

图1 L297引脚图图2 L297内部方框电路图图3 L297变换器换出的八步雷格码(顺时针旋转)图4 斩波器线路图5 多个L297同步工作连接图L297 ABSOLUTE MAXIMUM RATINGS绝对最大额定值:SymbolParameter 参数Value 数值Unit 单位符号Vs Supply voltage 电源电压10 VVi Input signals 输入信号7 VPtot Total power dissipation 总功率耗散(Tamb = 70℃) 1 WTstg, Tj Storage and junction temperature 储存和结温-40 to + 150 ℃L297 ELECTRICAL CHARACTERISTICS (Refer to the block diagram Tamb = 25℃, Vs = 5V unless otherwisespecified) L297 电气特性:Symbol符号Parameter 参数Test conditions测试条件最小典型最大单位Vs Supply voltage (pin 12) 电源电压 4.75 7 VIsQuiescent supply current静态电源电流(引脚12) Outputs floating580 mAViInput voltage输入电压(引脚11,17,18,19,20) Low0.6V High 2 Vs VIiInput current输入电流(引脚11,17,18,19,20) Vi = L1μA Vi = H 10μAVenEnable input voltage 使能输入电压(引脚10)Low1.3V High 2 Vs VIenEnable input current使能输入电流(引脚10) Ven = L10μA Ven = H 10μAVoPhase output voltage 相输出电压(引脚4,6,7,9)Io = 10mA VOL0.4V Io =5mA VOH 3.9 VVinhInhibit output voltage (pins 5, 8)抑制输出电压(引脚5,8)Io = 10mA Vinh L0.4VIo =5mA Vinh H 3.9 V VSYNC Sync Output Voltage 同步输出电压Io = 5mA VSYNC H 3.3 VIo = 5mA VSYNC V0.8IleakLeakage current(pin3)泄漏电流(引脚3) VCE = 7 V 1μAVsat Saturation voltage饱和电压(引脚3) I = 5 mA0.4V VoffComparators offset voltage比较器的偏移电压(引脚13,14,15)Vref = 1 V 5 mV IoComparator bias current 比较器偏置电流(引脚13,14,15)-100 10 mA VrefInput reference voltage输入参考电压(引脚15)0 3 V tCLK Clock time 时钟时间0.5μs tS Set up time 建立时间 1μs tH Hold time保持时间 4μs tR Reset time复位时间 1μs tRCLK Reset to clock delay 重置时钟延迟 1μsL297各引脚功能说明1脚(SYNG)——斩波器输出端。

2.4G 9通道模型遥控器说明书

9 Channels Digital Proportional Radio Control System INSTRUCTION MANUAL9通道数字协议无线控制系统说明书深圳市雷诺特遥控技术有限公司SHENZHEN RAYLIGHT Remote Control Technology CO.,LTDMENU目录1.说明Introduction2.服务Services3.特殊符号说明The special symbols4.安全指南Safety guides5.第二代自动跳频数字系统2AFHDS6.充电说明Battery charging notes7.发射机参数说明Transmitter parameters8.接收机参数说明Receiver parameters9.对码操作说明2.4G BIND OPERATION NOTES10.开机和关机POWER ON & SHUT DOWN11.发射机和接收机各部位说明EACH PART OF THE TRANSMITTER & RECEIVER12.发射机功能说明Transmitter function notes13.适用范围Scope of application14.功能详细说明Function in detail15.免责声明Disclaimer16.包装包含内容清单Packaging with content list1 、INTRODUCTION说明Thank you for choosing RAYLIGHT 2.4G radio remote control digital products, if you are the first time to use this type of products, please read this statement carefully and strictly in accordance with the requirements of operation.You could refer to the manual if you meet any problems during the operation. Please well keep the manual after use because you might have to use it again next time. Once again, thanks for buying our products.非常感谢您选择使用RAYLIGHT 2.4G数码比率遥控产品,如果您是第一次使用该类型产品,请您在使用之前先仔细阅读此说明书,并严格按说明要求进行操作。

保时捷维修手册:997_TI_9c

工作时间: 91 10 25 42 不包括:

PCM 2.1 中的编码行车日志 路试时测试功能

40 个时间 单位

参考资料:

⇒ 车间指南 ’271000 蓄电池滴流充电’ 车间设备手册 3.9.1 – 蓄电池检测仪/充电器 ⇒ 技术信息 ’911025 PCM2.1 导航更新’ PCM 操作说明

© Dr. Ing. h.c. F. Porsche AG Printed in Germany

危险 如不遵守操作说明则必然导致死亡或重伤的警告。

警告 如不遵守操作说明则可能会导致死亡或重伤的警告。

注意 如不遵守操作说明则会导致轻伤或财产损失的警告。

为防止由于工作不当而导致伤害、损失车辆性能和交通安全性、或者损坏车辆,请仔细阅读这些警告注 释和安全指南并严格遵守。

Dr. Ing. h.c. F. Porsche AG 不可能为执行此项工作的人详细评估所有的危险状况。因此,所有对保时捷车 辆进行修理和维护的人都必须依靠自己的专门知识来保证自己的安全,并且所选择的过程不会对车辆带来 任何负面效果,尤其不能损失车辆的安全性能。

1 x 行车日志 CD-ROM

注释:

PCM2.1 的操作说明和快速参考指南不包括在供货范围内,对于 2005 年款,必须在以下 地址使用要求的语言单独订购。

地址: 电子邮件:

arvato Logistics services (Bertelsmann) Friedrich-Menzefricke-Str. 16 -18D 33775 Versmold 电话: +49-5423-15-42621/传真:+49-5423-42820

verena.belke@bertelsmann.de

订单号:

NICE900调试流程

50.0%(增加) ★

c收整、刀 关异之门步前收门,刀刀厅速收门度刀若和调有收整轻刀微时撞间门。现相象关, 参稍 数微 参增 照大 下表F4:08,保证不撞门,然后进行调

F408 F409 F410

关门到位低速运行时间 收刀速度设定 收刀运行时间

1~9999ms 0.00Hz~F403 1~9999ms

H

设定值 113 115 114 112 1 2 2 1

5

异步机速度控制方式接线检查

在调试之前首先我们要检查门机所有线路是否连接正确 1.确认门机控制器输入端子L1、L2的电源为单相AC220V 2.确认开关门减速开关、限位开关接线正确 3.确认开关门指令接线正确 4.确认门机控制器输出开关门到位信号正确

关门速度及受阻参数:

功能码 名称

F400

关门启动低速设定

F401

关门启动加速时间

F402

速度控制关门启动低速运行时间

F403

关门高速设定

F404 F405

关门加速时间 关门结束低速设定

F406

关门减速时间

F407

关门到位低速设定

F408

关门到位低速运行时间

F409 F410

收刀速度设定 收刀运行时间

外围线路检查

旋转编码器检查

控制器相关规格参数 设定

门宽自学习

手动调试运行

确定开关/脉冲换速 点位置

平滑换速开关门

结束

【注】为保证门机顺利调试,请按顺序执行此步骤。

H

15

AC220V

异步机距离控制方式输入输出端子示意

电 源

门

机 马 达

H

开门到位 信号输出 关门到位 信号输出

AD9779资料

Rev. PrDInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 Fax: 781.326.8703© 2005 Analog Devices, Inc. All rights reserved.Dual 16-Bit, 1.0 GSPSD/A ConverterPreliminary Technical DataAD9779FEATURES• 1.8/3.3 V Single Supply Operation• Low power: 950mW (I OUTFS = 20 mA; f DAC = 1 GSPS, 4× Interpolation• DNL = ± 1.5 LSB, INL = ± 5.0 LSB • SFDR =82 dBc to f OUT = 100 MHz • ACLR = 87 dBc @ 80 MHz IF• CMOS data interface with Autotracking Input Timing • Analog Output: Adjustable 10-30mA (RL=25 Ω to 50 Ω) • 100-lead Exposed Paddle TQFP Package • Multiple Chip Synchronization Interface• 84dB Digital Interpolation Filter Stopband Attenuation • Digital Inverse Sinc FilterAPPLICATIONS• Wireless Infrastructure Direct Conversion Transmit Diversity• Wideband Communications Systems: Point-to-Point Wireless, LMDSPRODUCT DESCRIPTIONThe AD9779 is a dual 16-bit high performance, high frequencyDAC that provides a sample rate of 1 GSPS, permitting multi carrier generation up to its Nyquist frequency. It includes features optimized for direct conversion transmit applications, including complex digital modulation and gain and offset compensation. The DAC outputs are optimized to interface seamlessly with analog quadrature modulators such as the AD8349. A serial peripheral interface (SPI) provides for programming many internalparameters and also enables read-back of status registers. Theoutput current can be programmed over a range of 10mA to 30mA. The AD9779 is manufactured on an advanced 0.18µm CMOSprocess and operates from 1.8V and 3.3V supplies for a total power consumption of 950mW . It is supplied in a 100-lead QFP package.PRODUCT HIGHLIGHTSUltra-low noise and Intermodulation Distortion (IMD) enable high quality synthesis of wideband signals from baseband to high intermediate frequencies.Single-ended CMOS interface supports a maximum input rate of300 MSPS with 1x interpolation.Manufactured on a CMOS process, the AD9779 uses a proprietary switching technique that enhances dynamic performance.The current outputs of the AD9779 can be easily configured for various single-ended or differential circuit topologies.FUNCTIONAL BLOCK DIAGRAMP2D[15:0]IOUT2_PIOUT2_NCLK+CLK-DATACLK_OUTS D I OS D O S C L K C S BIOUT1_PIOUT1_NVREF RSET AUX1_P AUX1_N AUX2_P AUX2_NP1D[15:0]SYNC_ISYNC_OFigure 1 Functional Block DiagramAD9779Preliminary Technical DataRev. PrD | Page 2 of 34TABLE OF CONTENTSSpecifications............................................................................................3 DC SPECIFICATIONS......................................................................3 DIGITAL SPECIFICATIONS............................................................4 AC SPECIFICATIONS.......................................................................4 Pin Function Descriptions.....................................................................5 Pin Configuration....................................................................................6 Interpolation Filter Coefficients............................................................7 INTERPOLATION Filter RESPONSE CURVES................................8 CHARACTERIZATION DATA............................................................9 General Description..............................................................................12 Serial Peripheral Interface................................................................12 General Operation of the Serial Interface......................................12 Instruction Byte.................................................................................12 Serial Interface Port Pin Descriptions............................................12 MSB/LSB Transfers...........................................................................13 Notes on Serial Port Operation.......................................................13 SPI Register Map...............................................................................14 Internal Reference/Full Scale Current Generation.......................22 Auxiliary DACs..................................................................................22 Power Down and Sleep Modes........................................................22 Internal PLL Clock Multiplier / Clock Distribution.....................23 Timing Information..........................................................................23 Interpolation Filter Architecture.....................................................25 EvaLuation Board Schematics.. (27)REVISION HISTORYRevision PrA: Initial VersionRevision PrB: Updated Page 1 Features, added eval board schematics, SPI register map, filter coefficients and filter response curves Revision PrC: Added characterization data, description of modulation modes, internal clock distribution architecture, timing information Revision PrD: Added more ac characterization data, power dissipationPreliminary Technical DataAD9779Rev. PrD | Page 3 of 34SPECIFICATIONS 1DC SPECIFICATIONS(VDD33 = 3.3 V, VDD18 = 1.8 V, MAXIMUM SAMPLE RATE, UNLESS OTHERWISE NOTED)Parameter Temp Test Level Min Typ Max UnitRESOLUTION16 Bits Integral Nonlinearity (DNL) ± 1.5 LSB ACCURACYDifferential Nonlinearity (INL) ± 5 LSB Offset Error± TBD % F SR Gain Error (With Internal Reference) ± TBD % FSR Gain Error (Without Internal Reference)± TBD % F SR Full Scale Output Current 10 20 30 mA Output Compliance Range 1.0 V Output Resistance TBD k Ω ANALOG OUTPUTSOutput Capacitance TBD pF OffsetTBD ppm/°C GainTBD ppm/°CTEMPERATURE DRIFTReference VoltageTBDppm/°CInternal Reference Voltage 1.2 V REFERENCE Output Current 100 nA VDDA33 3.13 3.3 3.47 V ANALOG SUPPLYVOLTAGES VDDA18 1.70 1.8 1.90 V VDDD33 3.13 3.3 3.47 VVDDD18 1.70 1.8 1.90 V DIGITAL SUPPLY VOLTAGESVDDCLK 1.70 1.8 1.90 V 600 MSPS TBD mW POWER CONSUMPTIONStandby Power TBD mWTable 1: DC Specifications1Specifications subject to change without noticeAD9779Preliminary Technical DataRev. PrD | Page 4 of 34DIGITAL SPECIFICATIONS(VDD33 = 3.3 V, VDD18 = 1.8 V, MAXIMUM SAMPLE RATE, UNLESS OTHERWISE NOTED)Parameter Temp Test Level Min Typ Max UnitDifferential peak-to-peak Voltage 800 mV Common Mode Voltage 400 mV DAC CLOCK INPUT(CLK+, CLK-) Maximum Clock Rate1 GSPS Maximum Clock Rate (SCLK) 40 MHz Maximum Pulse width high TBD ns SERIAL PERIPHERAL INTERFACEMaximum pulse width lowTBDnsTable 2: Digital SpecificationsAC SPECIFICATIONS(VDD33 = 3.3 V, VDD18 = 1.8 V, MAXIMUM SAMPLE RATE, UNLESS OTHERWISE NOTED)Parameter Temp Test Level Min Typ Max UnitOutput Settling Time (tst) (to 0.025%) TBD ns Output Rise Time (10% to 90%) TBD ns Output Fall Time (90% to 10%) TBD nsDYNAMICPERFORMANCEOutput Noise (IoutFS=20mA) TBD pA/rtHz f DAC = 100 MSPS, f OUT = 20 MHz 82 dBc f DAC = 200 MSPS, f OUT = 50 MHz 82 dBc f DAC = 400 MSPS, f OUT = 70 MHz 84 dBc SPURIOUS FREE DYNAMIC RANGE (SFDR)f DAC = 800 MSPS, f OUT = 70 MHz 87 dBc f DAC = 200 MSPS, f OUT = 50 MHz 91 dBc f DAC = 400 MSPS, f OUT = 60 MHz 88 dBc f DAC = 400 MSPS, f OUT = 80 MHz 81 dBc TWO-TONEINTERMODULATION DISTORTION (IMD)f DAC = 800 MSPS, f OUT = 100 MHz 88 dBc f DAC = 156 MSPS, f OUT = 60 MHz -158 dBm/Hz f DAC = 200 MSPS, f OUT = 80 MHz -157 dBm/Hz f DAC = 312 MSPS, f OUT = 100 MHz -159 dBm/Hz NOISE SPECTRAL DENSITY (NSD) f DAC = 400 MSPS, f OUT = 100 MHz -159 dBm/Hz f DAC = 245.76 MSPS, f OUT = 20 MHz 80 dBc f DAC = 491.52 MSPS, f OUT = 100 MHz 79 dBc WCDMA ADJACENT CHANNEL LEAKAGE RATIO (ACLR), SINGLE CARRIERf DAC = 491.52 MSPS, f OUT = 200 MHz 74 dBc f DAC = 245.76 MSPS, f OUT = 60 MHz 78 dBc f DAC = 491.52 MSPS, f OUT = 100 MHz 80 dBc WCDMA SECOND ADJACENT CHANNEL LEAKAGE RATIO (ACLR), SINGLE CARRIERf DAC = 491.52 MSPS, f OUT = 200 MHz76dBcTable 3: AC SpecificationsPreliminary Technical DataAD9779Rev. PrD | Page 5 of 34PIN FUNCTION DESCRIPTIONSPin No.N ame Description Pin No.N ame Description1 VDDC18 1.8 V Clock Supply 51 P2D<6> Port2 Data Input D6 2 VDDC18 1.8 V Clock Supply 52 P2D<5> Port 2 Data Input D53 VSSC Clock Common 53 VDDD18 1.8 V Digital Supply4 VSSC Clock Common 54 VSSD Digital Common5 CLK+ Differential Clock Input 55 P1D<4> Port 2 Data Input D46 CLK- Differential Clock Input 56 P1D<3> Port 2 Data Input D37 VSSC Clock Common 57 P1D<2> Port 2 Data Input D28 VSSC Clock Common 58 P1D<1> Port 2 Data Input D19 VDDC18 1.8 V Clock Supply 59 P1D<0> Port 2 Data Input D0 (LSB) 10 VDDC18 1.8 V Clock Supply 60 VDDD18 1.8 V Digital Supply 11 VSSC Clock Common 61 VDDD33 3.3 V Digital Supply 12 VSSC Clock Common 62 SYNC_O- Differential Synchronization Output 13 SYNC_I+ Differential Synchronization Input 63 SYNC_O+ Differential Synchronization Output 14 SYNC_I- Differential Synchronization Input 64 VSSD Digital Common 15 VSSD Digital Common 65 PLL_LOCK PLL Lock Indicator 16 VDDD33 3.3 V Digital Supply 66 SPI_SDO SPI Port Data Output 17 P1D<15> Port 1 Data Input D15 (MSB) 67 SPI_SDIO SPI Port Data Input/Output 18 P1D<14> Port 1 Data Input D14 68 SPI_CLK SPI Port Clock 19 P1D<13> Port 1 Data Input D13 69 SPI_CSB SPI Port Chip Select Bar 20 P1D<12> Port 1 Data Input D12 70 RESET Reset 21 P1D<11> Port 1 Data Input D11 71 IRQ Interrupt Request 22 VSSD Digital Common 72 VSS Analog Common 23 VDDD18 1.8 V Digital Supply 73 IPTAT Reference Current 24 P1D<10> Port 1 Data Input D10 74 VREF Voltage Reference Output 25 P1D<9> Port 1 Data Input D9 75 I120 120 µA Reference Current 26 P1D<8> Port 1 Data Input D8 76 VDDA33 3.3 V Analog Supply 27 P1D<7> Port 1 Data Input D7 77 VSSA Analog Common 28 P1D<6> Port 1 Data Input D6 78 VDDA33 3.3 V Analog Supply 29 P1D<5> Port 1 Data Input D5 79 VSSA Analog Common 30 P1D<4> Port 1 Data Input D4 80 VDDA33 3.3 V Analog Supply 31 P1D<3> Port 1 Data Input D3 81 VSSA Analog Common 32 VSSD Digital Common 82 VSSA Analog Common 33 VDDD18 1.8 V Digital Supply 83 IOUT2_P Differential DAC Current Output, Channel 2 34 P1D<2> Port 1 Data Input D2 84 IOUT2_N Differential DAC Current Output, Channel 2 35 P1D<1> Port 1 Data Input D1 85 VSSA Analog Common 36 P1D<0> Port 1 Data Input D0 (LSB) 86 AUX2_P Auxiliary DAC Voltage Output, Channel 2 37 DATACLK_OUT Data Clock Output 87 AUX2_N Auxiliary DAC Voltage Output, Channel 2 38 VDDD33 3.3 V Digital Supply 88 VSSA Analog Common 39 TXENABLE Transmit Enable 89 AUX1_N Auxiliary DAC Voltage Output, Channel 1 40 P2D<15> Port 2 Data Input D15 (MSB) 90 AUX1_P Auxiliary DAC Voltage Output, Channel 1 41 P2D<14> Port 2 Data Input D14 91 VSSA Analog Common 42 P2D<13> Port 2 Data Input D13 92 IOUT1_N Differential DAC Current Output, Channel 1 43 VDDD18 1.8 V Digital Supply 93 IOUT1_P Differential DAC Current Output, Channel 1 44 VSSD Digital Common 94 VSSA Analog Common 45 P2D<12> Port 2 Data Input D12 95 VSSA Analog Common 46 P2D<11> Port 2 Data Input D11 96 VDDA33 3.3 V Analog Supply 47 P2D<10> Port 2 Data Input D10 97 VSSA Analog Common 48 P2D<9> Port 2 Data Input D9 98 VDDA33 3.3 V Analog Supply 49 P2D<8> Port 2 Data Input D8 99 VSSA Analog Common 50 P2D<7> Port 2 Data Input D7 100 VDDA33 3.3 V Analog SupplyTable 4: Pin Function DescriptionsAD9779Preliminary Technical DataRev. PrD | Page 6 of 34PIN CONFIGURATIONVDDD18VDDD18VSSD P2D<5>P2D<4>P2D<3>P2D<2>P2D<1>P2D<0>SYNC_O-SPI_SDOSPI_SDIV D D A 33V S S AV D D A 33V S S AV D D A 33V S S AA U X 2_PA U X 2_NV S S AI O U T 2_PI O U T 2_NV S S AV S S AV S S AI O U T 1_NI O U T 1_PV S S AA U X 1_NVSSD VDDD33VSSD VDDD18P1D<10>P1D<11>P1D<12>P1D<13>P1D<14>P1D<15>SYNC_I-SYNC_I+VSSC VSSC P 2D <11>V D D D 33P 2D <12>P 2D <13>P 2D <14>P 2D <15>D C L KP 1D <0>P 1D <1>P 1D <2>P 1D <3>V D D D 18V S S DP 1D <4>P 1D <5>P 1D <6>P 1D <7>P 1D <8>P1D<9>P 2D <7>P 2D <8>P 2D <9>P 2D <10>A U X 1_PV S S AV D D A 33V S S AV D D A 33CLK-CLK+VDDC18VSSC VSSC VDDC18VSSC VSSC VDDC18VDDC18SPI_CLK SPI_CSB RESET IPTAT VREF IRQ V S S AV D D A 33SYNC_O+VSSD VSS T X E n a b l eP2D<6>I120PLL_LOCK V D D D 18V S S DVDDD33Figure 2. Pin ConfigurationPreliminary Technical DataAD9779Rev. PrD | Page 7 of 34INTERPOLATION FILTER COEFFICIENTSTable 5: Halfband Filter 1Lower Coefficient Upper Coefficient Integer Value H(1) H(55) -4 H(2) H(54) 0 H(3) H(53) 13 H(4) H(52) 0 H(5) H(51) -34 H(6) H(50) 0 H(7) H(49) 72 H(8) H(48) 0 H(9) H(47) -138 H(10) H(46) 0 H(11) H(45) 245 H(12) H(44) 0 H(13) H(43) -408 H(14) H(42) 0 H(15) H(41) 650 H(16) H(40) 0 H(17) H(39) -1003 H(18) H(38) 0 H(19) H(37) 1521 H(20) H(36) 0 H(21) H(35) -2315 H(22) H(34) 0 H(23) H(33) 3671 H(24) H(32) 0 H(25) H(31) -6642 H(26) H(30) 0 H(27) H(29) 20755 H(28) 32768Table 6: Halfband Filter 2 Lower Coefficient Upper Coefficient Integer Value H(1) H(23) -2 H(2) H(22) 0 H(3) H(21) 17 H(4) H(20) 0 H(5) H(19) -75 H(6) H(18) 0 H(7) H(17) 238 H(8) H(16) 0 H(9) H(15) -660 H(10) H(14) 0 H(11) H(13) 2530 H(12) 4096Table 7: Halfband Filter 3 Lower Coefficient Upper Coefficient Integer Value H(1) H(15) -39 H(2) H(14) 0 H(3) H(13) 273 H(4) H(12) 0 H(5) H(11) -1102 H(6) H(10) 0 H(7) H(9) 4964 H(8) 8192Table 8: Inverse Sinc Filter Lower Coefficient Upper Coefficient Integer Value H(1) H(9) 2 H(2) H(8) -4 H(3) H(7) 10 H(4) H(6) -35 H(5) 401AD9779 Preliminary Technical Data INTERPOLATION FILTER RESPONSE CURVESFigure 3. AD9779 2x Interpolation, Low Pass Response to±4x Input Data Rate (Dotted Lines Indicate 1dBRoll-Off)Figure 4. AD9779 4x Interpolation, Low Pass Response to±4x Input Data Rate (Dotted Lines Indicate 1dBRoll-Off)Figure 5.AD9779 8x Interpolation, Low Pass Response to±4x Input Data Rate (Dotted Lines Indicate 1dBRoll-Off)Rev. PrD | Page 8 of 34Preliminary Technical DataAD9779Rev. PrD | Page 9 of 34CHARACTERIZATION DATAFigure 6. AD9779 Typical INLFigure 7. AD9779 Typical DNLFigure 8. SFDR vs. F OUT , 1x InterpolationFigure 9. SFDR vs. F OUT , 2x InterpolationFigure 10. SFDR vs. F OUT, 4x InterpolationOUTAD9779Preliminary Technical DataRev. PrD | Page 10 of 34Figure 12. Third Order IMD vs. F OUT , 1x InterpolationOUTOUTOUTOUTOUTFigure 18. ACLR for 1stAdjacent Band WCDMA, 4x Interpolation. On-ChipModulation is used to translate baseband signal to IF.Modulation is used to translate baseband signal to IF.Modulation is used to translate baseband signal to IF.Figure 23. Power Dissipation of Inverse Sinc FilterGENERAL DESCRIPTIONThe AD9779 combines many features which make it make it a very attractive DAC for wired and wireless communications systems. The dual digital signal path and dual DAC structure allow an easy interface with common quadrature modulators when designing single sideband transmitters. The speed and performance of the AD9779 allow wider bandwidths/more carriers to be synthesized than with previously available DACs. The digital engine in the AD9779 uses a breakthrough filter architecture that combines the interpolation with a digital quadrature modulator. This allows the AD9779 to do digital quadrature frequency up conversion. The AD9779 also has features which allow simplified synchronization with incoming data, and also allows multiple AD9779s to be synchronized.Serial Peripheral InterfaceAD9779SPI PORTSPI_CSB (pin 69)SPI_SCLK (pin 68)SPI_SDI (pin 67)SPI_SDO (pin 66)Figure 24. AD9779 SPI PortThe AD9779 serial port is a flexible, synchronous serialcommunications port allowing easy interface to many industry-standard microcontrollers and microprocessors. The serial I/O is compatible with most synchronous transfer formats, including both the Motorola SPI® and Intel® SSR protocols. The interface allows read/write access to all registers that configure the AD9779. Single or multiple byte transfers are supported, as well as MSB first or LSB first transfer formats. The AD9779’s serial interface port can be configured as a single pin I/O (SDIO) or two unidirectional pins for in/out (SDIO/SDO).General Operation of the Serial InterfaceThere are two phases to a communication cycle with the AD9779. Phase 1 is the instruction cycle, which is the writing of aninstruction byte into the AD9779, coincident with the first eight SCLK rising edges. The instruction byte provides the AD9779 serial port controller with information regarding the data transfer cycle, which is Phase 2 of the communication cycle. The Phase 1instruction byte defines whether the upcoming data transfer is read or write, the number of bytes in the data transfer, and the starting register address for the first byte of the data transfer. The first eight SCLK rising edges of each communication cycle are used to write the instruction byte into the AD9779.A logic high on the CS pin, followed by a logic low, will reset the SPI port timing to the initial state of the instruction cycle. This is true regardless of the present state of the internal registers or the other signal levels present at the inputs to the SPI port. If the SPI port is in the midst of an instruction cycle or a data transfer cycle,none of the present data will be written.The remaining SCLK edges are for Phase 2 of the communication cycle. Phase 2 is the actual data transfer between the AD9779 and the system controller. Phase 2 of the communication cycle is a transfer of 1, 2, 3, or 4 data bytes as determined by the instruction byte. Using one multibyte transfer is the preferred method. Single byte data transfers are useful to reduce CPU overhead whenregister access requires one byte only. Registers change immediately upon writing to the last bit of each transfer byte.Instruction ByteThe instruction byte contains the information shown in Error! Reference source not found..MSB LSBI7 I6 I5 I4 I3 I2 I1 I0 R/W N1 N0 A4 A3 A2 A1 A0Table 9. SPI Instruction ByteR/W , Bit 7 of the instruction byte, determines whether a read or a write data transfer will occur after the instruction byte write. Logic high indicates read operation. Logic 0 indicates a write operation. N1, N0, Bits 6 and 5 of the instruction byte, determine the number of bytes to be transferred during the data transfer cycle. The bit decodes are shown in Table 10.A4, A3, A2, A1, A0, Bits 4, 3, 2, 1, 0 of the instruction byte, determine which register is accessed during the data transferportion of the communications cycle. For multibyte transfers, this address is the starting byte address. The remaining registeraddresses are generated by the AD9779 based on the LSBFIRST bit (REG00, bit 6).N1 N2 Description 0 0 Transfer 1 Byte 0 1 Transfer 2 Bytes 1 0 Transfer 3 Bytes 11Transfer 4 BytesTable 10. Byte Transfer CountSerial Interface Port Pin DescriptionsSCLK—Serial Clock . The serial clock pin is used to synchronize data to and from the AD9779 and to run the internal statemachines. SCLK’s maximum frequency is 20 MHz. All data input to the AD9779 is registered on the rising edge of SCLK. All data is driven out of the AD9779 on the falling edge of SCLK.CSB—Chip Select . Active low input starts and gates acommunication cycle. It allows more than one device to be used on the same serial communications lines. The SDO and SDIO pins will go to a high impedance state when this input is high. Chip select should stay low during the entire communication cycle.SDIO—Serial Data I/O . Data is always written into the AD9779 onthis pin. However, this pin can be used as a bidirectional data line. The configuration of this pin is controlled by Bit 7 of register address 00h. The default is Logic 0, which configures the SDIO pin as unidirectional.SDO—Serial Data Out. Data is read from this pin for protocols that use separate lines for transmitting and receiving data. In thecase where the AD9779 operates in a single bidirectional I/O mode, this pin does not output data and is set to a high impedance stat e. MSB/LSB TransfersThe AD9779 serial port can support both most significant bit (MSB) first or least significant bit (LSB) first data formats. This functionality is controlled by register bit LSBFIRST (REG00, bit 6). The default is MSB first (LSBFIRST = 0).When LSBFIRST = 0 (MSB first) the instruction and data bytes must be written from most significant bit to least significant bit. Multibyte data transfers in MSB first format start with an instruction byte that includes the register address of the most significant data byte. Subsequent data bytes should follow in order from high address to low address. In MSB first mode, the serial port internal byte address generator decrements for each data byte of the multibyte communication cycle.When LSBFIRST = 1 (LSB first) the instruction and data bytes must be written from least significant bit to most significant bit. Multibyte data transfers in LSB first format start with an instruction byte that includes the register address of the least significant data byte followed by multiple data bytes. The serial port internal byte address generator increments for each byte of the multibyte communication cycle.The AD9779 serial port controller data address will decrement from the data address written toward 0x00 for multibyte I/O operations if the MSB first mode is active. The serial port controller address will increment from the data address written toward 0x1F for multibyte I/O operations if the LSB first mode is active. Notes on Serial Port OperationThe AD9779 serial port configuration is controlled by REG00, bits 6 and 7 . It is important to note that the configuration changes immediately upon writing to the last bit of the register. For multibyte transfers, writing to this register may occur during the middle of communication cycle. Care must be taken to compensate for this new configuration for the remaining bytes of the current communication cycle.The same considerations apply to setting the software reset, RESET (REG00, bit 5). All registers are set to their default values EXCEPT REG00 and REG04 which remain unchanged.Use of only single byte transfers when changing serial port configurations or initiating a software reset is recommended to prevent unexpected device behavior.R/W N0N1A0A1A2A3A4D7D6N D5N D00D10D20D30D7D6N D5N D00D10D20D30INSTRUCTION CYCLE DATA TRANSFER CYCLECSBSCLKSDIOSDO3152--4 Figure 25. Serial Register Interface Timing MSB FirstA0A1A2A3A4N1N0R/W D00D10D20D7ND6ND5ND4ND00D10D20D7ND6ND5ND4NINSTRUCTION CYCLE DATA TRANSFER CYCLECSBSCLKSDIOSDO3152--5 Figure 26. Serial Register Interface Timing LSB First3152-PrD-6Figure 27. Timing Diagram for SPI Register WriteCSB3152-PrD-7 Figure 28. Timing Diagram for SPI Register ReadSPI Register MapRegister Name AddressBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0DefaultComm Register00h 00 SDIOBidirectionalLSB,MSB FirstSoftware ResetPower Down ModeAuto Power Down EnablePLL Lock Indicator00h01h 01Filter Interpolation Factor <1: 0>Filter Interpolation Mode <4:0>Zero Stuffing Enable00hDigital Control Register02h 02 Data FormatOne Port ModeReal ModeInverse Sinc EnableDATACLK InvertIQ Select InvertQ First00h03h 03 Data Delay Mode <1:0> Data Clock Delay <2:0> Data Window Delay <2:0>00h 04h04Sync Out Delay <3:0>Sync Window Delay <3:0>00h Sync Control05h 05 Sync Enable Sync Driver Enable Dac Clock Offset <2:0>00hInterruptRegister 06h 06 Data DelayIRQ Sync Delay IRQCrossControl IRQ Data Delay IRQ Enable Sync DelayIRQ EnableCrossControl IRQ Enable00h07h 07 PLL Band Select <4:0> PLL Loop Cap Select <2:0> CFh PLL Control 08h08PLL EnablePLL Output Freq Divide <1:0>PLL Loop Freq Divide <1:0>PLL Loop Filter Pole/Zero <2:0>37hMisc. Control Register 09h 24 PLL ErrorSource PLL Ref BypassPLL Gain <2:0> PLL Bias <2:0> 38h0Ah 09 IDAC Gain Adjustment <7:0> F9hI DAC Control Register0Bh10IDAC SLEEPIDAC Power DownIDAC Gain Adjustment <9:8>01h0Ch 11 Auxiliary DAC1 Data <7:0>00hAux 1 DAC Control Register0Dh 12 AuxiliaryDAC1 SignAuxiliary DAC1 Current DirectionAuxiliary DAC1 SleepAuxiliary DAC1 Data <9:8>00h0Eh 13 QDAC Gain Adjustment <7;0>F9hQ DAC Control Register0Fh 14 QDAC SLEEP QDAC SleepQDAC Gain Adjustment <9:8>01h10h 15 Auxiliary DAC2 Data <7:0>00hAux 2 DAC Control Register11h 16 AuxiliaryDAC2 SignAuxiliary DAC2 Current DirectionAuxiliary DAC2 Power DownAuxiliary DAC2 Data <9:8>00h12h 17 Cross Updel <7:0> 00h 13h 18 Cross Dndel <7:0> 00h 14h19Cross Clock Divide <3:0>Cross Wiggle Delay <3:0>00h CrossRegister15h 20 Cross RunCross StatusCross DoneCross Wiggle <2:0>Cross Step <1:0>00h AnalogWrite 16h 23 Analog Write <7:0>00h17h 21 Mirror Roll Off <1:0>Band Gap Trim <2:0> 00h Analog Control Register 18h22Stack Headroom Control<7:0>CAh Analog Status Register 19h 25 Analog Status <7:0>--hTest 1 Register1Ah 26 MISR EnableMISR IQSelect MISR SamplesInternalData Enable Test Mode <2:0>00h1Bh 27 BIST<31:24> --h 1Ch 28 BIST<23:16> --h 1Dh 29 BIST<15:8> --h Test 2Register1Eh 30 BIST<7:0>--hTable 11: SPI Register MapRegister (hex) Bits Name Function Default7 SDIO Bidirectional 0: Use SDIO pin as input data only1: Use SDIO as both input and output data0 6 LSB/MSB First 0: First bit of serial data is MSB of data byte1: First bit of serial data is LSB of data byte0 5 Software RESET Bit must be written with a 1, then 0 to soft reset SPI register map 0 4 Power Down Mode 0: All circuitry is active1: Disable all digital and analog circuitry, only SPI port is active0 3 Auto Power Down Enable0 00Comm Register1 PLL LOCK (read only) 0: PLL is not locked1: PLL is locked0 7:6 F ilter Interpolation Rate 00: 1x interpolation01: 2x interpolation10: 4x interpolation 11: 8x interpolation005:2 Control Halfband Filters 1,2,3See Table 13 for filter modes0000 01Digital Path Filter Control0 Zero Stuffing 0: Zero stuffing off1: Zero stuffing on0 7 Data Format 0: Signed binary1: Unsigned binary0 6 One Port Mode 0: Both input data ports receive data1: Data port 1 only receives data0 5 Real Mode 0: Enable Q path for signal processing1: Disable Q path data (clocks disabled) 0 3 Inverse Sinc Enable 0: Inverse sinc disabled1: Inverse sinc disabled0 2 DATACLK Invert 0: Output DATACLK same phase as internal capture clock1: Output DATACLK opposite phase as internal capture clock0 1 IQ Select Invert 0: TxEnable (pin 39) =1, routes input data to I channelTxEnable (pin 39) =0, routes input data to Q channel 1: TxEnable (pin 39) =1, routes input data to Q channel TxEnable (pin 39) =0, routes input data to I channel02General Mode Control0 Q First 0: First byte of data is always I data at beginning of transmit1: First byte of data is always Q data at beginning of transmit7:6 Data Delay Mode 00: Manual, no error correction01: Manual, continuous error correction 10: automatic, one pass check11: automatic, continuous pass check005:3 Data Clock Delay Data Clock delay control 000 03Data Clock Delay2:0 Data Window DelayWindow delay control000 7:4 Sync Output Delay 0000 04Synchronization Delay 3:0 Sync Window Delay0000 7 Sync Enable 0: LVDS and synchronization rceiver logic off1: LVDS and synchronization rceiver logic on0 6 Sync Driver Enable 0: LVDS driver off1: LVDS driver on0 05Chip Sync and Data Delay Control5:3 DAC Clock Offset。

V909产品培训资料(2.2)

二、3.5寸高清电容屏

3.5寸高清电容屏,480×320分辨率HVGA 屏幕Байду номын сангаас屏幕更清晰,颜色更鲜艳,视角 更宽广。

V909配备最高端模组电容触摸屏,是普通手机灵敏度的10 倍,专为宽屏触控而生,指尘轻轻点滑,画面行云流水般 变幻,给你超乎想象的触控体验,并支持10页菜单左右轻 轻点滑翻页,可支持10×16=160个应用程序。

深圳酷比通信设备有限公司

电容屏: 静电感应,手 指轻轻接触屏 幕就会有反应, 轻轻滑动即可。 只要手指轻轻触摸屏幕即可被 识别。那么,普通的手写笔是 没法用于电容屏了。 优点:99%的准确度 的准确度、 优点:99%的准确度、灵敏,支 持多点触摸,适合娱乐玩游戏。 缺点: 缺点:不能精确定位.

市场部培训组

V909采用500万像素高清AF (Auto Focus)自动对焦摄像头, 可以进行人脸识别、微笑快门,支持单点、多点、连续 单点、 单点 多点、连续自 动对焦,微距拍照。照片分辨率最高可达2592×1944,最 低可达480×320;相片库呈现立体效果的相片墙。

深圳酷比通信设备有限公司

市场部培训组

酷PHONE V909产品培训资料

市场部培训组 2011-09-13

深圳酷比通信设备有限公司 市场部培训组

认识酷PhoneV909

光感应器 电源开关/待机键和3.5mm耳机接口 音量调节键 摄 像 头 / A A C 扬 声 器

USB接口 电容式确定键

深圳酷比通信设备有限公司

主菜单键/返回键

相机快捷键

深圳酷比通信设备有限公司

电容屏

市场部培训组

4.怕磁场; 4.怕磁场;特别是电磁场 怕磁场 特别是电磁场,拿块小磁铁在电容 屏上放一会,电容屏就会暂时性失 效(也有可能会造成永久性损伤)别 靠近音箱或带磁性的螺丝批等物品, 回到家不要把顺手手机放在音箱上。

5功能遥控器PT8A977_978的应用

●主题论文5功能遥控器PT 8A977/978的应用李峻(大连铁道学院,辽宁大连116028)摘要:研究了具有优异性能的5功能无线遥控电路PT 8A977/978的主要性能、内部电路结构特点以及控制逻辑关系,详细介绍了PT 8A977/978的典型应用电路及其电路工作原理。

关键词:PT 8A977/978;编码;解码;伺服电机;遥控车分类号:TP336文献标识码:A 文章编号:1006-6977(2004)03-0070-04A pp lication of 5-Function R emote Controller PT8A977/978LI Jun(Dalian Railwa y Institute ,liaonin g 116028)Abstract :T he m ain function ,internal circuit and control relation of the ex cellent 5function w ireless rem ote con 2troler PT 8A9771978are introduced in this p a p er.T he t y p ical a pp lication circuit is introduced detail.K e y w ords :PT 8A9771978;Encoder ;Decode ;S erved m otor ;T he rem ote -controlled car1引言玩具遥控车采用的是伺服电机无线遥控技术。

遥控电路设计的基本要求是高性能、低成本、运行平稳、控制灵活、线路简单、抗干扰能力强。

通常玩具遥控车的驱动要用两个微型直流伺服电动机来实现玩具遥控车的前进、后退、左转、右转和加速等功能。

玩具遥控车市场竞争的日趋激烈,对玩具遥控车的电气性能也提出了越来越高的要求。

玩具遥控车的无线遥控控制电路设计决定着玩具遥控车的整体性能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Si9979Vishay SiliconixDocument Number: 70012S-41209—Rev. E, 21-Jun-0413-Phase Brushless DC Motor ControllerFEATURESHall-Effect Commutation 60 or 120 Sensor SpacingIntegral High-Side Drive for all N-Channel MOSFET Bridges PWM InputQuadrature Selection Tachometer Output Reversible BrakingOutput Enable ControlCross Conduction Protection Current LimitingUndervoltage Lockout Internal Pull-Up ResistorsDESCRIPTIONThe Si9979 is a monolithic brushless dc motor controller with integral high-side drive circuitry. The Si9979 is configured to allow either 60or 120 commutation sensor spacing. The internal low-voltage regulator allows operation over a wide input voltage range, 20- to 40-V dc.The Si9979 provides commutation from Hall-effect sensors.The integral high-side drive, which utilizes combination bootstrap/charge pump supplies, allows implementation of an all n-channel MOSFET 3-phase bridge. PWM, direction,quadrature select, and braking inputs are included for control along with a tachometer output. Protection features include cross conduction protection, current limiting, and undervoltage lockout. The FAULT output indicates when undervoltage, over current, disable, or invalid sensor shutdown has occurred.The Si9979 is available in both standard and lead (Pb)-free 48-pin SQFP packages and is specified to operate over the commercial temperature range of 0 to 70C (C suffix), and the industrial temperature range of −40 to 85C (D suffix).FUNCTIONAL BLOCK DIAGRAMIN A IN C BRK PWM TACH QS V+GT A F/R ENR T V DDI S −I S +R T /C TS A GT B S B CAP A CAP B GB A GB B GND GT C S C CAP C GB C FAULTIN B 60/120End of Life. Last Available Purchase Date is 31-Dec-2014Si9979Vishay Siliconix2Document Number: 70012S-41209—Rev. E, 21-Jun-04ABSOLUTE MAXIMUM RATINGSVoltage on Pin 4250 V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Voltage on Pins 1−4, 10, 11 −0.3 V to V DD + 0.3 V . . . . . . . . . . . . . . . . . . . . . Voltage on Pins 5−9−0.3 V to 5.5 V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Voltage on Pins 26, 28, 30, 32, 34, 3660 V . . . . . . . . . . . . . . . . . . . . . . . . . . . . Voltage on Pins 27, 31, 35−2 to 50 V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Operating TemperatureC Suffix 0 to 70_C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .D Suffix −40 to 85_C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Storage Temperature −65 to 150_C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Junction Temperature (T J )150_C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Power Dissipation (P D )C Suffix 0.70 W . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .D Suffix 0.55 W. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . RECOMMENDED OPERATING RANGEV++20 to 40 V DC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . R T 10 k W Min. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . SPECIFICATIONSTest ConditionsLimitsParameterSymbolUnless Otherwise SpecifiedV+ = 20 to 40 V, I DD = 0 mAMin aTyp bMax aUnitPowerSupply Voltage Range V+2040Logic Voltage V DD −20 mA v I DD v 0 mA14.51617.5V Supply Current I+ 4.5Logic Current I DD −20mA Internal Reference dV REF4.2VCommutation Inputs (IN A , IN B , IN C , 60/120)High-State V IH 4.0Low-StateV IL 1.0V High-State Input Current I IH V IH = V DD 10Low-State Input CurrentI ILV IL = 0 V−50m ALogic Inputs (F/R, EN, QS, PWM, BRK)High-State V IH 2.0Low-StateV IL 0.8V High-State Input Current I IH V IH = 5.5 V 10Low-State Input CurrentI ILV IL = 0 V−125m AOutputsLow-Side Gate Drive, High State V GBH 141617.5Low-Side Gate Drive, Low State V GBL 0.1High Side Gate Drive High State T A = 0 to 70_C C Suffix 1618High-Side Gate Drive, High State V GTH T A = −40 to 85_CD Suffix1620VHigh-Side Gate Drive, Low State V GTL 0.1Capacitor Voltage dV CAP V+ = 40 V55Low-Side Switching, Rise Time t rL 70Low-Side Switching, Fall Time t fL Risetime = 1 to 10 V25High-Side Switching, Rise Time t rH Falltime = 10 to 1 VC 100High-Side Switching, Fall Time t fH L = 600 pF40nsBreak Before Make Time t BLH 100Break-Before-Make Time t BHL 300TACH Output/FAULT Output V OL I OL = 1.0 mA0.150.4V TACH Output Pulsewidth t T300600nsSi9979Vishay SiliconixDocument Number: 70012S-41209—Rev. E, 21-Jun-043SPECIFICATIONSLimitsTest ConditionsUnless Otherwise SpecifiedParameterUnitMax aTyp bMin aV+ = 20 to 40 V, I DD = 0 mASymbolProtectionLow-Side Undervoltage Lockout UVLL 12.2Low-Side HysteresisV H 0.8VHigh-Side Undervoltage LockoutUVLHS A, B, C = 0 VV DD − 3.3Current LimitComparator Input Bias Current I IB −5m A T A = 0 to 70_C C Suffix 90100110Comparator Threshold Voltage V TH T A = −40 to 85_CD Suffix85100125mV Common Mode Voltage V CM 01V R T = 10 k, C T = 0.001 m F 81012One Shot Pulse Widtht pR T = 10 k, C T = 0.01 m F 80100120m sNotesa.The algebraic convention whereby the most negative value is a minimum and the most positive a maximum.b.Typical values are for DESIGN AID ONLY , not guaranteed nor subject to production testing.c.The reference voltage is not available for external use.d.V CAP = (V+) + (V DD ).COMMUTATION TRUTH TABLEInputsOutputsConditionsSensors (60_Spacing)Sensors (120_Spacing)Top DriveBottom Drive IN AIN BIN CIN AIN BIN CENF/RBR KI S +GT-A GT-B GT-C GBA GBB GBC FAULT000101110010001011001001100100001111011011000100011111010110001010010110111100001100100100111000010101000101100001010011001001000001100111011010000010101111010100010001010110111000100001100100110000100011X X X X X X 0X 0X 0000000Disable X X X X X X 0X 1X 0001110Power DownL L L L L L 1X 100001111Brake L L L L L L 1X 110001110Over I in BRKL L L L L L 1X 010000000Over I1011111X 0X 00000001011111X 1X 00011100100001X 0X 0000000011X1X111Notes:L. Any valid sensor combination X. Don’t care60/120EN F/R QS PWM IN B IN C GNDCAP A S A GB CGT A GB A CAP B S B GT B GB B CAP C BRK S C TACH GT C FAULTSQFP-48Top ViewG N DG N DG N DG N DG N DV +G N DG N DG N DG N DG N DG N DG N DG N DG N DG N DG N DG N DG N DV D DIN A I S −I S +/C TR TR TSi9979Vishay Siliconix4Document Number: 70012S-41209—Rev. E, 21-Jun-04PIN CONFIGURATION AND ORDERING INFORMATIONORDERING INFORMATIONStandard Part NumberLead (Pb)-Free Part NumberTemperature Range PackageSi9979CS Si9979CS—E30 to 70_C Si9979DSSi9979DS—E3−40 to 85_CSQFP-48NOTE: Si9979CS and Si9979DS are supplied in trays.PIN DESCRIPTIONPins 1−3: IN A , IN B , IN CIN A , IN B , and IN C are the commutation sensor inputs, and areintended to be driven by open collector Hall effect switches.These inputs have internal pull up resistors tied to V DD , which eliminates the need for external pull up resistors.Pin 4: 60/120The 60/120 input allows the use of the Si9979 with either a 60_or 120_ commutation sensor spacing. An internal pull up resistor, which is tied to V DD , sets the default condition to 60_spacing. 120_ spacing is selected by pulling this input to ground.Pin 5: EN (Enable)A logic “1” on this input allows commutation of the motor. This is the default condition as this pin is pulled up internally. When this pin is pulled to ground, all gate drive outputs are turned off.Pin 6: F/R (Forward/Reverse)A logic “1” on this input selects commutation for motor rotation in the “forward” direction. This is the default condition as thispin is pulled up internally. When this pin is pulled to ground, the commutation sensor logic levels are inverted internally,causing reverse rotation.Pin 7: QS (Quadrature Select)This input determines whether the bottom MOSFETs or both bottom and top MOSFETs switch in response to the PWM signal. A logic “1” on this input enables only the bottom MOSFETs. This is the default condition as this pin is pulled up internally. When this pin is pulled to ground, both the bottom and top MOSFETs are enabled.Pin 8: PWMAn open collector (drain) or TTL compatible signal is applied to this input to control the motor speed. The QS input determines which MOSFETs are switched in response to the PWM signal. If no PWM signal is being used, this input is left open. It is pulled up internally, which allows the MOSFETs to follow the commutation sequence.Si9979 Vishay SiliconixDocument Number: 70012 S-41209—Rev. E, 5PIN DESCRIPTION (CONT’D)Pin 9: BRKWith this input at logic “1”, the top MOSFET s are turned off and the bottom MOSFETs are turned on, shorting the motor windings together. This provides a braking torque which is dependent on the motor speed. This is the default condition as this pin is pulled up internally. When this pin is pulled to ground, the MOSFETs are allowed to follow the commutation sequence.Pin 10: TACHThis output provides a minimum 300-nanosecond output pulse for every commutation sensor transition, yielding a 6 pulse per electrical revolution tachometer signal. This output is open drain.Pin 11: FAULTThe FAULT output switches low to indicate that at least one of the following conditions exists, controller disable (EN), undervoltage lockout, invalid commutation sensor code shutdown, or overcurrent shutdown. This output is open drain.Pin 17: R T/C TThe junction of the current limit one shot timing resistor and capacitor is connected to this pin. This one-shot is triggered by the current limit comparator when an overcurrent condition exists. This action turns off all the gate drives for the period defined by R T and C T, thus stopping the flow of current.Pin 18: R TOne side of the current limit one shot timing resistor is connected to this pin.Pin 19: I S+This is the sensing input of the current limit comparator and should be connected to the positive side of the current sense resistor. When the voltage across the current sense resistor exceeds 100 mV, the comparator switches and triggers the current limit one-shot. The one-shot turns off all the gate drives for the period defined by R T and C T, thus stopping the flow of current. If the overcurrent condition remains after the shutdown period, the gate drives will be held off until the overcurrent condition no longer exists.Pin 20: I S−This pin is the ground reference for the current limit comparator. It should be connected directly to the ground side of the current sense resistor to enhance noise immunity.Pins 12−16: 21−24, 37−41, 44−48, GNDThese pins are the return path for both the logic and gate drive circuits. Also, they serve to conduct heat out of the package, into the circuit board.Pin 25: GB CThis is the gate drive output for the bottom MOSFET in Phase C.Pin 26: GT CThis is the gate drive output for the top MOSFET in Phase C.Pin 27: S CThis pin is negative supply of the high-side drive circuitry. As such, it is the connection for the negative side of the bootstrap capacitor, the top MOSFET Source, the bottom MOSFET Drain, and the Phase C output.Pin 28: CAP CThis pin is the positive supply of the high-side circuitry. The bootstrap capacitor for Phase C is connected between this pin and SC.Pin 29: GB BThis is the gate drive output for the bottom MOSFET in Phase B.Pin 30: GT BThis is the gate drive output for the top MOSFET in Phase B.Pin 31: S BThis pin is negative supply of the high-side drive circuitry. As such, it is the connection for the negative side of the bootstrap capacitor, the top MOSFET Source, the bottom MOSFET Drain, and the Phase B output.Pin 32: CAP BThis pin is the positive supply of the high-side circuitry. The bootstrap capacitor for Phase B is connected between this pin and SB.Pin 33: GB AThis is the gate drive output for the bottom MOSFET in Phase A.Si9979 Vishay Siliconix 6Document Number: 70012 S-41209—Rev. E, 21-Jun-04PIN DESCRIPTION (CONT’D)Pin 34: GT AThis is the gate drive output for the top MOSFET in Phase A.Pin 35: S AThis pin is negative supply of the high-side drive circuitry. As such, it is the connection for the negative side of the bootstrap capacitor, the top MOSFET Source, the bottom MOSFET Drain, and the Phase A output.Pin 36: CAP AThis pin is the positive supply of the high-side circuitry. The bootstrap capacitor for Phase A is connected between this pin and SA.Pin 42: V+The supply voltage for the Si9979 is connected between this pin and ground. The internal logic and high-side supply voltages are derived from V+.Pin 43: V DDV DD is the internal logic and gate drive voltage. It is necessary to connect a capacitor between this pin and ground to insure that the current surges seen at the turn on of the bottom MOSFETs does not trip the undervoltage lockout circuitry.APPLICATION CIRCUITSFIGURE 1.Three-Phase Brushless DC Motor Controller To Motor WindingsToLITTLE FOOTSi9979 Vishay SiliconixDocument Number: 70012 S-41209—Rev. E, 7APPLICATION CIRCUITSA, IN B, and IN CA, IN B,C to GND. Use F/R in-s.ToMotorWindingsFIGURE 3.Three-Phase AC Motor ControllerSi9979 Vishay Siliconix 8Document Number: 70012 S-41209—Rev. E, 21-Jun-04APPLICATION CIRCUITSV DD’DD DD BEFIGURE 4.External V DD Regulator* For reference onlyPackage InformationVishay SiliconixDocument Number: 72823 29-Jan-041SQFP: 48-LEAD (7X7X1.4 MM) SQUARE (POWER IC ONL Y)MILLIMETERSINCHES*Dim MinMaxMinMaxA 1.40 1.600.0550.063A 10.050.150.0020.006A 2 1.35 1.450.0530.057b 0.170.260.0060.010C 0.1170.1770.0050.007D 8.709.300.3430.366D 1 6.907.100.2700.280e 0.50 TYP 0.020 TYPL 0.450.750.0180.030L 10.90 1.100.0350.043∅10_7_0_7_ECN: S-40084—Rev. A, 02-Feb-04DWG: 5928Legal Disclaimer Notice VishayDisclaimerALL PRODU CT, PRODU CT SPECIFICATIONS AND DATA ARE SU BJECT TO CHANGE WITHOU T NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively,“Vishay”), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.Statements regarding the suitability of products for certain types of applications are based on Vishay’s knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer’s responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and/or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer’s technical experts. Product specifications do not expand or otherwise modify Vishay’s terms and conditions of purchase, including but not limited to the warranty expressed therein.Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.Material Category PolicyVishay Intertechnology, Inc. hereby certifies that all its products that are identified as RoHS-Compliant fulfill the definitions and restrictions defined under Directive 2011/65/EU of The European Parliament and of the Council of June 8, 2011 on the restriction of the use of certain hazardous substances in electrical and electronic equipment (EEE) - recast, unless otherwise specified as non-compliant.Please note that some Vishay documentation may still make reference to RoHS Directive 2002/95/EC. We confirm that all the products identified as being compliant to Directive 2002/95/EC conform to Directive 2011/65/EU.Vishay Intertechnology, Inc. hereby certifies that all its products that are identified as Halogen-Free follow Halogen-Free requirements as per JEDEC JS709A standards. Please note that some Vishay documentation may still make reference to the IEC 61249-2-21 definition. We confirm that all the products identified as being compliant to IEC 61249-2-21 conform to JEDEC JS709A standards.Revision: 02-Oct-121Document Number: 91000。