全数字接收机中定时同步算法和实现

QPSK全数字接收机的关键技术

一 ~ 。 ~

PO (C3 ) 微 源43 产生中 1 H、 特率2 M p 釜 耋 : R MX f P 波 48 2。 C 频 0M z 比 5 0 bs 竺 盏 j 兰

的Q S P K信 号 ,I 、Q数 据格 式 同上 。任意波 形 发生器输 出 6 I H 0V z的 [ 图 1 实 解调 测 结果

信 噪I d : B I U

பைடு நூலகம்

图 2 误码 率性 能测试

包括AD 样芯 D65 高 样率为6 瑚 z 1 b) 时 一 ‘ 一_ /采 片A 6 ( 采 4最 5 , 4 i 钟分 t ,

配 器 C 20 Y 3 5, Vr xI r F G XC V 7 和 配 置 用 的 ie— P o P A t I 2 P0 j ~

一_ 二

47 Q S 全数字接收机 的关键 技术 —0 P K

代 涛

介 绍 了一种高码 率 Q S P K全数 字接 收机 的定 时 同步和 载波 同步方 法 ,采用 数字转 换跟踪环 和 C T OS AS

环实现 同步 。

首 先进行 定时 同步 。数 字转换 跟踪 环提 取定 时误 差仅 要求一 至两 个采样 点 ,得到 定时误差 后经 过滤波

维普资讯

2 6 中国工程物理研 究院科 技年报 6

重复 频率 高、脉冲波 形较理想 、脉冲 幅度和 宽度 易调节 。在 本 实验 中采用雪 崩管 与脉冲变 压器 “ ”驱 动 过 及 多管 串联 的方法得 到高压 脉冲输 出如 图 2所 示 。实验 表 明多管 串联脉冲源 输 出前后 沿 的快慢 取 决于栅 极 驱动 脉冲源 的驱动 能力 以及 场效应管 串联 电路 的参数 ,可采 用过 驱动和 多路并 联法进 一步提 高输 出指标 。

一种数字中频接收机的符号定时同步方法

传统 的方法是 由定 时误 差估计算法 加环路滤 波估 内插滤波得到最佳 时刻采样值 。

计采样 时钟 和最佳 采样时刻 之间的相位 差 ,然后通 过

开环结构是全数字化的 ,更加适合采用D P S 通过软

控制数 控振荡 器 ( O)调 整采样 时钟…。数字接 收 件完成 ,符合软 件无线 电的思路 。开环结构 是当前 的 NC 机 通常利用估 计的 时钟 差值控 制内插滤波器 ,对采样 趋 势和 主流 ,同步 速度快得 多 ,但是 精度稍差 ,同步

yk ( O 2 ) — ) ( ( () 4

尽管在这个模型 中包括假想的模拟部分 ,但如果知

要解调 器的判决 数据 ,必须在载 波恢复 、数据 判决之 道 以下三种 条件 :输入的序列xm) ( ;内插滤波器的冲激 T和k 。我们仍可以用全数 后才能提取定时误 差信号 。G r e算法是FM.a nr a nr d G r e于 相应 ;入和输 出的抽样 时间m T d 18 年提出的一种适用于B S / S 的算法 6 9 P K QP K J ,它的收 字 的方式计算 内插值 ,因此 内插器是数字的。其 中,T 敛速度快 、运算量小 ,易于高速实现。每个数据符号需 是未知的,通过变换 ,可 以用采样时钟表示插值 :

维普资讯

Mont ig & De e t n i n or t ci o

种数字 中频接收机 的 符号定时 同步方法

一

■ 郑州大学信息工程 学院 西 安 电子 科 技 大 学

河南 省 无 线 电监 测站 郑 州 大 学 信 息工 程 学 院

摘 要

展 ,接收机 的数字化 、软 件化成 为无线通信 发展的主 速度和精度。

流 。作为软件 无线 电技术 发展 的一 个重要步骤 ,数字 中频 技术得到 了广泛应用 。数字 中频接收机特点 之一

全数字接收机码元同步算法的VLSI实现研究

全数字接收机码元同步算法的VLSI实现探究专业品质权威编制人:______________审核人:______________审批人:______________编制单位:____________编制时间:____________序言下载提示:该文档是本团队精心编制而成,期望大家下载或复制使用后,能够解决实际问题。

文档全文可编辑,以便您下载后可定制修改,请依据实际需要进行调整和使用,感谢!同时,本团队为大家提供各种类型的经典资料,如办公资料、职场资料、生活资料、进修资料、教室资料、阅读资料、知识资料、党建资料、教育资料、其他资料等等,想进修、参考、使用不同格式和写法的资料,敬请关注!Download tips: This document is carefully compiled by this editor. I hope that after you download it, it can help you solve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you!And, this store provides various types of classic materials for everyone, such as office materials, workplace materials, lifestyle materials, learning materials, classroom materials, reading materials, knowledge materials, party building materials, educational materials, other materials, etc. If you want to learn about different data formats and writing methods, please pay attention!全数字接收机码元同步算法的VLSI实现探究全数字接收机码元同步算法的VLSI实现探究摘要:随着通信技术的进步,全数字接收机成为了一种重要的接收设备,在数字通信系统中起着至关重要的作用。

ATSC全数字接收机的符号定时同步方法

是 sn ( 为无 限冲激 效应 , i ) c 属于非 因果滤波器 , 在实 现中 可以通过截取冲激宽度的方法来实现 。 .M. ad e 在 F G rnr

文献【 中则指 出, 3 ] 在综合 了实现难度 和 内插效 果后 , 分段

抛 物线就可以满足设计 要求 。 本文在 Ma a Ⅱb建模时, 两 对 个 内插 函数 作 了 比较分 析 , 真结 果 表 明 , 于 8 A K 仿 对 - S

【 src】 T e i epltn ft i ic i us ep ne bsd o arw s u tr i ue o rsle tepo lm o mig Abtat h n roao l rwt Sn mpl rso s ae n F r t c e s sd t e ov r e ft n t i ie h e o r u h b i

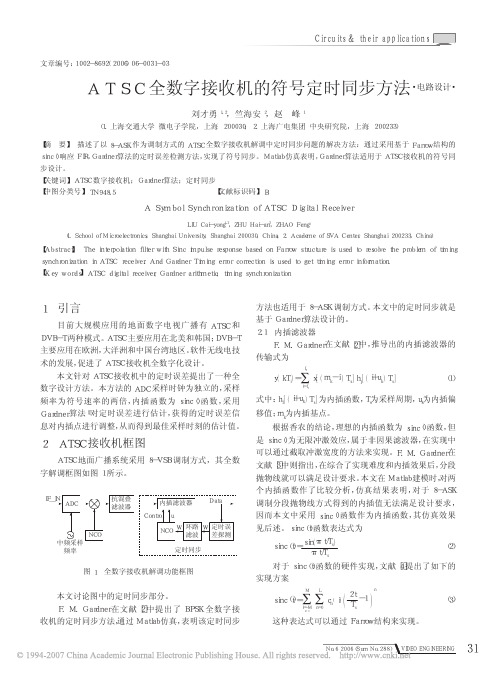

本文针对 A C接 收机 中的定 时误 差提出 了一种全 数字设计 方法 。本方法 的 A C采样时钟为独立 的 , D 采样

) ) , = (

il =。

【 k ) 】, iu) (— h( k m 【 + 】

() 1

频率 为符号 速率 的 两倍 , 内插 函数 为 s c ) i ( 函数 , 用 n 采 G rn r a e 算法[ d 1 1 对定时误 差进行 估计 , 获得 的定 时误差 信 息对 内插点进行调整 , 而得 到最佳 采样 时刻的估计值 。 从

式中: f+ ] ( ) 为内插函数, 为采样周期, ,i r 为内插偏

移值 ; k 内插基点 。 m为

根据香农的结论 , 想的 内插 函数 为 s c ) 理 i ( 函数 , n 但

全数字接收机码元同步的研究

定时脉冲序列信号。在全数字接收机 中。由 于解调前对信

号 采用异步采样 。为了解决位 同步问题 ,提出了 G rnr a e d

算 法。G de算法在一个 码元 中需要 2 r a r n 个样点就能进 行

判决 ,所以在码元同步算法 中有广泛的应用。

输入采样 时间

Gad e 符号定 时同步环路 rn r

了定时误差的大小 。 算法具有两个特点 : 一是每个符号只需要两个采样点 , 且以码元速 率输 出误差信号 ; 是估 计算法是独立于载 波 二 相位的 , 即可 以在载波相位 同步之前分 , 用插值的方法对本地定 时相位进行调整 , 使得

采样 的结果尽可能接近最佳采样点。设 h c为内插滤波器 I ( )

Ga nr r e 符号 定时 同步 环路 主要 由 G r e 定时误 d a r n d

12G rn r . ad e 定时误差检测

本文采用的是 G de 提出的定时误差算法 。Ga e r an r r r n d

算法 是一种在载波同步之前先进行定时同步 ,该算法 的

差检测 , 环路滤波器 ,数控振荡器及内插滤波器组成。数

设计与研发

2 1 o 11 1

.

1 . 路滤 波器 3环

环 路滤 波器 采用理想积分滤波器 ,其传递 函数在 S 域

在图 3 中横轴为时间,纵轴为寄存器值 。根据相似三

角形的知识 ,很容易得到 :

上 示 表 为:

变换到 z 域为 :

、 ) :

一 盯1 () 4

(一 ) 1 T( 1 T( +1 1, ) 一 17 )

图 l G d e符 号定时同步环路 ,AD转换器 以独 为 a nr r / 立时钟对接收到的模拟信号进行采样 。

ATSC全数字接收机的符号定时同步方法

VIDEOENGINEERINGNo.62006(SumNo.288)文章编号:1002-8692(2006)06-0031-03ATSC全数字接收机的符号定时同步方法刘才勇1,2,竺海安2,赵峰1(1.上海交通大学微电子学院,上海200030;2.上海广电集团中央研究院,上海200233)【摘要】描述了以8-ASK作为调制方式的ATSC全数字接收机解调中定时同步问题的解决方法:通过采用基于Farrow结构的sinc()响应FIR,Gardner算法的定时误差检测方法,实现了符号同步。

Matlab仿真表明,Gardner算法适用于ATSC接收机的符号同步设计。

【关键词】ATSC数字接收机;Gardner算法;定时同步【中图分类号】TN948.5【文献标识码】BASymbolSynchronizationofATSCDigitalReceiverLIUCai-yong1,2,ZHUHai-an2,ZHAOFeng1(1.SchoolofMicroelectronics,ShanghaiUniversity,Shanghai200030,China;2.AcademeofSVACenter,Shanghai200233,China)【Abstract】TheinterpolationfilterwithSincimpulseresponsebasedonFarrowstructureisusedtoresolvetheproblemoftimingsynchronizationinATSCreceiver.AndGardnerTimingerrorcorrectionisusedtogettimingerrorinformation.【Keywords】ATSCdigitalreceiver;Gardnerarithmetic;timingsynchronization・电路设计・1引言目前大规模应用的地面数字电视广播有ATSC和DVB-T两种模式。

OFDM系统中定时同步算法的研究

OFDM系统中定时同步算法的研究OFDM(正交频分复用)是一种多载波调制技术,广泛应用于无线通信系统中。

由于OFDM系统中涉及到多个子载波,因此需要进行定时同步以确保接收端能够正确识别和解调接收到的数据。

在OFDM系统中,定时同步的主要目标是实现正确的符号定时,即将接收到的信号与发送的信号进行正确对齐,以便解码接收到的数据。

在接收端,定时同步算法通常由两个主要部分组成:粗定时同步和细定时同步。

粗定时同步是指通过估计信号的起始位置来找到粗略的接收时刻,以便后续的细定时同步。

常用的粗定时同步算法包括自相关算法和能量自相关算法。

自相关算法基于接收信号的自相关特性进行定时同步。

该算法通过计算接收信号的自相关函数的峰值位置来确定接收的起始位置。

自相关函数是通过将接收信号与其自身进行卷积得到,因此其峰值位置对应于信号的起始位置。

该算法的优点是计算简单,但对信号的前导序列和信道噪声比较敏感。

能量自相关算法则是基于接收信号的能量特性进行定时同步。

该算法计算接收信号的能量在不同偏移量下的累积,然后选择能量最大的位置作为接收的起始位置。

能量自相关算法的优点是对信号的前导序列和信道噪声影响较小,但对多径干扰比较敏感。

细定时同步是在粗定时同步的基础上进一步细化接收时刻的算法。

其主要目标是使接收信号与发送信号的符号对齐,以便进行数据解调。

常用的细定时同步算法包括最大似然算法和闭环算法。

最大似然算法是通过计算接收信号的每个子载波的符号能量与发送信号的符号能量之间的差异,选择能量差异最小的位置作为细定时同步的位置。

最大似然算法的优点是对信道衰落环境和多径干扰适应性较好,但计算量较大。

闭环算法是基于估计信道的特性进行定时同步。

该算法首先通过信道估计算法估计接收信号的信道响应,然后根据估计的信道响应调整接收时刻,使接收信号与发送信号符号对齐。

闭环算法的优点是对信道衰落环境和多径干扰适应性很好,但对信道估计的准确性要求较高。

总结起来,OFDM系统中的定时同步算法主要包括粗定时同步和细定时同步两部分。

数字通信原理06-定时与同步

6.1.2 收发定时系统

发定时系统就是产生各种定时脉冲的系统, 一般采用高精度的时钟脉冲发生器作为主时 钟,然后经过分频,得到相应频率的路脉冲、 位脉冲等,如图6-1所示。 目前使用的主时钟类型主要有原子钟、振荡 器等,也可以采用GPS、北斗一号等定时系 统的外基准定时信号。

在点与点之间进行数字传输时,接收端为了 正确地再生所传递的信号,必须产生一个时 间上与发送端信号同步的、位于最佳取样判 决位置的脉冲序列,这就是收定时系统,可 由收到的信码或锁相法获得。

3. 我国数字同步网

我国同步网等级结构,如图6-6所示。

第一级是基准时钟,由铯原子钟或GPS配铷钟组成。 第二级为有保持功能的高稳时钟(受控铷钟和高稳定度晶体钟),分 为A类和B类。上海、南京、西安、沈阳、广州、成都等六个大区中心 及乌鲁木齐、拉萨、昆明、哈尔滨、海口等五个边远省会中心配置地 区级基准时钟(LPR,Local Primary Reference,二级标准时钟),此 外还增配GPS定时接收设备,它们均属于A类时钟。全国30个省、市、 自治区中心的长途通信大楼内安装的大楼综合定时供给系统,以铷 (原子)钟或高稳定度晶体钟作为二级B类标准时钟。 各省内设置在汇接局(Tm)和端局(C5)的时钟是第三级时钟,采用 有保持功能的高稳定度晶体时钟,其频率偏移率可低于二级时钟。 另外第四级时钟是一般晶体时钟,通过同步链路与第三级时钟同步, 设置在远端模块、数字终端设备和数字用户交换设备当中。

6.2.4 网同步

同步网是由节点时钟设备和定时链路组成的 一个实体网,负责为各种业务网提供定时, 以实现各种业务网的同步,是电信网能够正 常运行的支撑系统。 同步网的基本功能是准确地将同步信息从基 准时钟向同步网的各下级或同级节点传递, 从而建立并保持全网同步。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

川 -y

y ( n , A k ) =艺

n 二 一 ( N- 1 ) m= 0

表 1 N = 3 , M= 2 F a r r o w滤波器系数表

n 场 一3 一 2 一1 0

1 2

0 0 0 1 0 0

0

1

2

0. 0 9 3 1 7 一0. 4 9 2 8 6 一0. 5 9 6 6 3 1 . 4 0 3 3 7 一 0. 4 9 2 8 6

误差的计算式[ 2 ) , 不难将它推广到n Q P S K , n Q A M

等其它解 调 系统 。

3 F P G A实现

3 . 1从S I MU L I N K仿真 到 F P G A实现

利用 S I M U L I N K搭建 B P S K解调系统 , 主要 目的是确定定时同步的结构、仿真定时算法的性能 , 同 时也为下一 步的设计— 用现场可编程 芯片 ( F P G A) 实 现该算法 ,提供了简单有效的方法。由于 S I M U L I N K仿 真的电路 已经做到寄存器级 , 各部分的电路主要 由乘法 器 、加/ 减法器、锁存器和移位寄存器等组成 ,便于向 F P G A的设计输人方法转换。 事实上 , 一些公司已经开发 出第三方软件 , 如A l t e r a开发 的 D S P B u i l d e r , 可 以嵌人 在M A T L A B软件中,直接完成从 M A T L A B的设计到 F P G A

一0. 0 9 3 1 7 0. 4 9 2 8 6 一0. 4 0 3 3 7 一0. 4 0 3 3 7 0 . 4 9 2 8 6

0 . 0 9 3 1 7

- 0 . 0 9 3 1 7

L P F N C O 图 4环路滤 波器 和数控 振荡器

为小整数。对 y ( k T ) 进行 K倍抽取 , 即得到与发送端符 号同步的最佳采样值序列 : ( - T ) o 内插恢复 电路包括一个 内插滤波器和内插滤波控制

实现 内插器, 去逼近理想内插器的频谱特性。通常采用基于

L a g r a n g e 多项式的内插方法,即滤波器可以写成系数为

= 艺二 [ ( 、 一 ‘ ) T s ] h j [ ( i + l l k ) T s ]

( 4 ) 式即定时同步 内插的基本公式。 理想内插器的冲激响应为 : i 函数 , 因此

( 4 )

h , [ ( i + N - k ) T s ] = s i [ 会 ( i T s + J l k T S ) ]

通 讯与 电视

全数字接收机中定时同步算法和实现

晏 蕾,余 荣,梅顺 良

( 清华大学 微波与数字通信国家 重点实验室, 北京 1 0 0 0 8 4 )

摘 要 :采 用 了基 于 F a r r o w结构 的 内插 滤波 器 , 同时使 用 G a r n d e r 的定 时误 差计算方 法为 内擂 滤

y ( t ) 二 Y , x ( - T s ) h , ( , 一 m T s )

再对 y ( t ) 以 T为间隔采样得 y ( k T ) , 则有

( 1 )

y ( k T ) 二 I二 ( m T s ) h , ( k T ; - m T s )

由于 T未知 , 利用 以下定 义 :

( 2 )

滤 波 的定 时同步结 构框 图 。

( N C O ) , 向内插滤波器提供插值相位和插值输出时各个信

号 的权值 。下面简单介绍 内插恢 复电路的各个部分。 1 . ,内插滤波器

设内插滤波器冲激响应的连续形式为 h , ( t ) , 采样信

号x ( m T s ) 经过 内插器 , 输出

那么 , 输 出为

( 6 )

《 电子技术应用》2 0 0 5 年第 1 2 期

本 刊邮 箱: e t a @ n c s e . c o m. c n 4 5

通 讯 与 电视

y ( t n ) 两个符号值相同, 则【 y ( t n + T ) - y ( t n - . + , r ) ] 为零 , 使得 y ( t n - 1 / 2 + 灼的值被屏蔽了, 在这

2数字解调 系统 的定 时同步仿真

本文对一个全数字 B P S K解调 系统进行 了 M A T L A B 仿 真 , 旨在 验 证 上 述 定 时 同 步 算 法 。 首 先 ,利 用 S I M U L I N K搭建 了整个接收系统 , 包括 A D转换 、 载波同 步、 定 时 同步 、 匹配滤波和判决 ; 其次 , 对输人信号进行 了模拟 , 模拟的输人信号为 中频 1 0 . 7 M H z 、 带宽 1 . 5 M H z

的数值代表定时误差的大小。但是 以 t n - 1 / 2 + 灼并不能指

示误差调整的方向, 因此用【 烈t n + 钓一 烈t o - 1 + 灼] 来表示误 e 和N C O的输出f 4 的仿真结果。可以看到, 大约1 0 0 个符号 差调整方向, 二者的乘积即为定时误差信号。如果 烈t o - 1 ) , 后 N - 趋于一稳定值 , 定时环路锁定同步。

在数字接收系统中, 为了正确恢复出发送端的符号 信息, 必须做到定时同步。 传统的接收机采用同步采样 , 利用定时误差信号调整接收端采样时钟的相位 , 使之与 符号同步 ; 而全数字接收机采用 固定 的采样频率 , 一般 来说 , 采样时钟和符号时钟相互独立 , 这种情况下可以 用数字信号处理 的方法实现对符号速率 的锁定 。 随着数字信号处理器和可编程逻辑芯片速度 的提 高, 利用这些芯片完成定时同步算法 , 为接收机的设计 带来 了很大 的灵活性 。 本文对全数字接收机 中的定时同 步算法进行 了分析 ,将 内插 滤波与误 差检测算法 相结 合, 提出了一种简单有效的算法 , 同时利用 M A T L A B进 行了仿真 。 实验结果表明该算法确实具有简单高效的特 点。最后 , 给出了 F P G A实现该算法的方法。 1定时同步算法 根据 F M. G a r d n e r的结论[ U , 内插恢复电路可以从采 样序列中恢复出最佳采样点的值 。 图1 给出了基于内插

4 6

欢迎 网上投稿 w w w . a e t n e t . c n w w w . a e t n e t . c o m. c n

《 电子技术应用》 2 0 0 5 年第 1 2 期

通 讯与 电视

在这种定时结构下 , 对1 0 0 , 0 0 ( ) 个随机符号 进行数次仿真 , 实现的 B P S K接收系统在输入信 噪比E , I N a = 1 2 . 5 d B情况下 , 平 均能够达 到 1 0 - 6 的误码性能。事实上 , 基于内插滤波的定时算 法不仅适用于 B P S K接收系统 ,只要修改定时

种情 况下是不能提取误差信号 的 。根据 + 八‘一 << K G a r n d e r 算法可以构造出定时误差提取 的 实现结构如图 3 0 1 . 3 环路滤 波器 ( L P F)和 数 控 振 荡 器 《 N C O) 定 时误 差信 号 通 过低 通环 路 滤 波器 ( L P F ) 滤 波后 , 控 制数控振荡器 ( N C O) 工 作 。这两部分的实现结构如图 4 0 L P F采用二阶滤波器 ,包含 比例路径 挥肠卜一破叮 K - 和积分路径 , 这两 条路 径分 别可 以跟踪相 位误差 和频率 误 差 。通过控制 比例增益 + } - 川 x k l 和积分增益 k 2 ,可以调整环路的带宽 和收敛速度 。N C O是一个相位 累加器 , 对 图 2 F a r r o w结构的 L a g r a n g e内插滤波器 输人 的相位误 差进 行 累加 , 为 内插 滤 波器 提供插 值相 位 。 ( 7 ) [ 艺。 C 。 } ( n 卜 ) j L m K已调信号, 符号速率为 6 6 0 k b p s 。对此信号带通 采样, 采样频率为符号速率的5 倍即 3 . 3 M b p s 。 由于上述

定时同步算法要求一个符号有两个采样信号 , 故载波 同 步恢复成基带信号后 , 调整采样速率使之成 为符号速率 的2 倍, 再进行定时同步、 匹配滤波和判决输出。 图5给出了定时同步模块中 T E D的输出 s , L P F的输出

i = i n t [ k T / T s ] 一 m

M k 二 i n t [ k T l T s ]

A二 k T / T s - m k

( 3 )

其中A k 为插值相位 , 满足/ 4 e [ O , 1 ) , m k 为插值抽取

的位置 , 将式 ( 2 ) 改写成

y ( k T ) = y [ ( m k + g k ) T s ]

l l k 的多项式 :

电路。内插滤波器( I n t e r p o l a t o r ) 从采样序列中恢复出最佳

采样值 , 是整个定时同步技术的关键。控制电路包括定时 误 差 检 测 电路 ( T E D) 、 环 路滤波器 ( L P F ) 和数控 振荡器

h r ( n , l i k ) = 艺c L 万 I ) n ( m

, n - n ‘

N M

M 为多项式 的阶数 , 2 N- 1为滤波器的阶数 。 基于多项式 的内插滤波器可用 F a r r o w结构实现, 如图 2所示。 这种滤波器实现起来很简单 , 使用较低的阶数( N = 3 , M= 2 ) 就能获得较好 的频谱性能。表 1 给 出了 F a r r o w滤 波器 的各 阶系数 。

波器提供插值相位。通过 M A T L A B仿真, 表明这种内插滤波器可以很好地解决定时同步问题 , 并在现 场可编程芯片 F P G A上实现 了该算法, 使得数字解调的硬件实现具有很好的移植性和灵活性。 关键词:内擂滤波器( I n t e r p o l a t o r ) 定时误差 擂值相位 S I M U L I N K F P G A实现