第10章VHDL有限状态机设计2015

第九次课 第7章 VHDL有限状态机设计到17页

10-1

接上页

10.1 VHDL状态机的一般形式

7.1.2 一般有限状态机的结构

10.1 VHDL状态机的一般形式

7.1.3 状态机设计初始控制与表述

(1)打开“状态机萃取”开关

(2)状态图观察

10.2 Moore型(莫尔型)状态机

莫尔型状态机的输出逻辑仅与当前状态 有关,与输入变量无关,输入变量的作 用只是与当前状态一起决定当前状态的 下一状态是什么,属于同步状态机。莫 尔型状态机框图如图所示。

实验与设计

7-4 五功能智能逻辑笔设计

(1)实验目的: (2)实验原理:

实验与设计

7-4 五功能智能逻辑笔设计

(1)实验目的: (2)实验原理:

示例文件:/KX_7C5EE+/EXPERIMENTs/EXP14_LOGIC_PEN/ (3)实验内容:

实验与设计

7-5 比较器加DAC器件实现ADC转换功能电路设计

10.1.2 一般有限状态机的结构 1. 说明部分 p259 位置一般在ARCHITECTURE BEGIN 之间

2. 主控时序进程 负责状态机转换和时钟驱动下负责状态转换的进程, 状态机是随外部时钟信号,依同步时序方式工作的

10.1 VHDL状态机的一般形式

10.1.2 一般有限状态机的结构 3. 主控组合进程p260(译码器进程)根据外部输入的控制信号,以及来自状态 机的内部其他主控的组合或时序进程的信号,给出当前状态的状态值及确定下 个状态。

4. 辅助进程 配合状态机工作的组合进程或时序进程

VHDL有限状态机

P260某生产车间共分5道工序,(S0,S1,S2,S3,S4) 1)首道工序S0为粗分拣车间,工序号为5号,红色 按钮按下表示继续分拣,绿色按钮按下表示完成去 下道工序,下道工序为S1; 2)S1为清洗车间,工序号为8号,红色按钮按下表 示继续清洗,绿色按钮按下表示完成去下道工序, 下道工序为S2; 3)S2为消毒车间,工序号为12号,红色按钮按下 表示不合格,打回S0,绿色按钮按下表示完成去下 道工序,下道工序为S3;

有限状态机

comreg:PROCESS(clk) --时钟进程和状态转化进程 BEGIN IF clk‘event AND clk=‘1' THEN CASE state IS WHEN s0=> IF x='0' THEN state<=s0; ELSE state<=s1; END IF; WHEN s1=> IF x='0' THEN state<=s0; ELSE state<=s2; END IF; WHEN s2=> IF x='0' THEN state<=s0; ELSE state<=s2; END IF; END CASE; END IF; END PROCESS;

---输出进程

已知米里型电路的状态转换图如图所示,试给出其VHDL描述。 描述。 例 已知米里型电路的状态转换图如图所示,试给出其 描述

S

X/Y

0/0

0/0

S0

1/ 0

S1Leabharlann 1/ 0S21/ 1

0/0

该电路有一个输入信号X和一个输出信号Y以及三个状态,因此在描述 时需要定义一个仅含S0、S1、S2三个状态的枚举类型,并定义一个信 号表示电路状态。VHDL描述如下: 2个进程描述

com1:PROCESS(present_state,x) --状态转换进程 BEGIN CASE present_state IS WHEN s0=> IF x='0' THEN next_state<=s0; ELSE next_state<=s1; END IF; WHEN s1=> IF x='0' THEN next_state<=s0; ELSE next_state<=s2; END IF; WHEN s2=> IF x='0' THEN next_state<=s0; ELSE next_state<=s3 next_state<=s3; END IF; WHEN s3=> IF x='0' THEN next_state<=s0; ELSE next_state<=s3; END IF; END CASE; END PROCESS;

10 第十章 使用VHDL语言来设计状态机

第十章 使用VHDL语言来设计状态机

思考和练习——填空题

1、所有的时序电路从理论上都可以表示为____。 2、数字系统一般可分为____和____,数据通道通常由组合逻辑电路

构成,而控制单元通常由时序逻辑电路构成。 3、输出信号只和当前状态有关的状态机称为____型状态机。 4、在状态机的设计中,需要对状态机的各个状态设定唯一对应的

己控制编码方式。

第十章 使用VHDL语言来设计状态机

10.1.4 状态机的非法状态

在状态机的正常运行中是不需要出现或者 未被定义的状态,被称为状态机的非法状 态。

对非法状态的处理就是状态机设计中的容 错技术,即状态机进入错误的状态之后的 处理。

第十章 使用VHDL语言来设计状态机

10.2 状态机的VHDL语言实现

第十章 使用VHDL语言来设计状态机

10.3.1 序列信号发生器

本应用是一个按照规定输出8位“0”、“1” 序列的信号发生器,其实质是一个8位的计 数器,计数器的每一位都可以输出位长为8 的“0”、“1”周期序列信号。

第十章 使用VHDL语言来设计状态机

10.3.2 循环彩灯控制器

循环彩灯控制器用于控制红绿黄三个LED 按照黄色LED亮1秒,红色LED亮2秒,绿色 LED亮3秒的方式循环点亮,其时钟频率为 1Hz

____。 5、状态机的每一个状态在实际电路中都是以一组____的当前状态组

合来表示的。 6、直接状态编码有顺序编码、____和一位有效的热码状态编码这三

种常用的编码方式。 7、在状态机的正常运行中是不需要出现或者未被定义的状态,通常

称为____。 8、状态机设计的关键是如何把一个实际的时序逻辑关系抽象成一个

状态机VHDL讲解

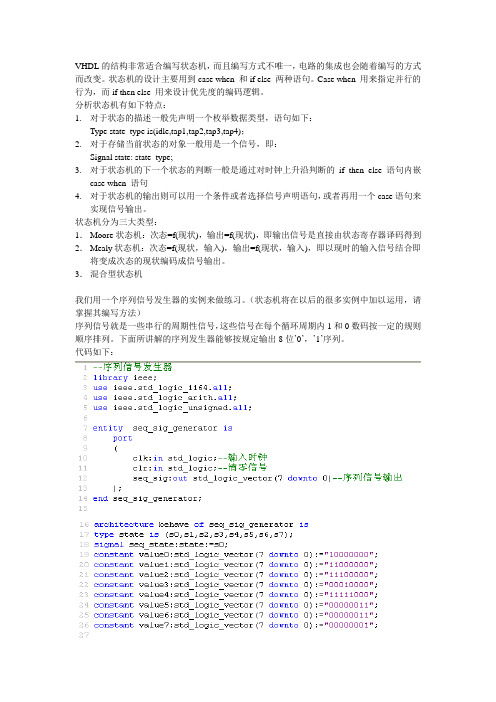

VHDL的结构非常适合编写状态机,而且编写方式不唯一,电路的集成也会随着编写的方式而改变。

状态机的设计主要用到case when 和if else 两种语句。

Case when 用来指定并行的行为,而if then else 用来设计优先度的编码逻辑。

分析状态机有如下特点:1.对于状态的描述一般先声明一个枚举数据类型,语句如下:Type state_type is(idle,tap1,tap2,tap3,tap4);2.对于存储当前状态的对象一般用是一个信号,即:Signal state: state_type;3.对于状态机的下一个状态的判断一般是通过对时钟上升沿判断的if then else 语句内嵌case when 语句4.对于状态机的输出则可以用一个条件或者选择信号声明语句,或者再用一个case语句来实现信号输出。

状态机分为三大类型:1.Moore状态机:次态=f(现状),输出=f(现状),即输出信号是直接由状态寄存器译码得到2.Mealy状态机:次态=f(现状,输入),输出=f(现状,输入),即以现时的输入信号结合即将变成次态的现状编码成信号输出。

3.混合型状态机我们用一个序列信号发生器的实例来做练习。

(状态机将在以后的很多实例中加以运用,请掌握其编写方法)序列信号就是一些串行的周期性信号,这些信号在每个循环周期内1和0数码按一定的规则顺序排列。

下面所讲解的序列发生器能够按规定输出8位’0’,’1’序列。

代码如下:逐行解释:10:清零复位信号,高电平复位清零。

12:序列信号输出。

因为是8位的端口,但序列信号是串行的,所以相当于有8路的序列信号,任取一位端口就是一个序列信号输出。

17:用type声明一种枚举类型。

共8中状态,每个状态都对应唯一的一种输出,至于在什么状态输出什么信号则由程序决定。

18:定义一个state类型信号量,其初始的状态为s0。

19-26:用constant定义一些常量,这些常量将作为在不同状态时的输出信号。

VHDL状态机

ST0 ST1

ST2

ST3 ST4

42

st0 对0809初始化

LOCK:

0-→1 由LOCK 信号锁 存转换 好的数

据

st4 OE=’1'

st1

数据输出 有效

采样周 期等待

st3

st2

启动AD 转换 EOC=

‘0’正 在转换

EOC=‘1'转换结束

图8-6 控制ADC0809采样状态图

43

PROCESS

30

31

32

33

34

35

36

37

38

以下以ADC0809为例 ,说明状态机的设计 方法。用状态机对 0809进行采样控制首 先必须了解工作时序 ,然后据此作出状态 图,最后写出相应的 VHDL代码。

ADC0809 ALE

sin START OE

clk ADDA EOC D[7..0]

VHDL状态机设计

1

2

3

4

5

6

Moore型有限状态机的结构图

7

Mealy型有限状态机的结构图

8

9

10

11

12

13

14

用户自定义数据类型定义语句

这里介绍与有限状态机设计有重要联 系的其它语法现象,即用户自定义数据类 型定义语句及相关的语法现象。如枚举型 、整数类型、数组类型、记录类型、时间 类型、实数类型等。

39

ADC0809工作时序 地址锁存信号

转换启动控制 进入转换状态 转换状态结束

输出有效控制

输出数据 稳定 40

时序图中,START为转换启动控制 信号,高电平有效;ALE为模拟信号输 入选通端口地址锁存信号,上升沿有效; 一旦START信号有效后,状态信号EOC 即变为低电平,表示进入转换状态。转换 结束后,EOC将变为高电平。此后外部 控制可以使OE由低电平变为高电平(输 出有效),此时,0809的输出数据总线 D[7..0]从原来的高阻态变为输出数据有效 。

有限状态机的VHDL设计

8.4 米立状态机设计(续2)

例8.3四状态米立状态机的描述。

COM:PROCESS (state, input) -- 依据当前状态和输入信号决定输出信号,与时钟无关 BEGIN CASE state IS WHEN s0=> IF input = '0' THEN output <= "00"; ELSE output <= "01"; END IF; WHEN s1=> IF input = '0' THEN output <= "01"; ELSE output <= "10"; END IF; WHEN s2=> IF input = '0' THEN output <= "10"; ELSE output <= "11"; END IF; WHEN s3=> IF input = '0' THEN output <= "11"; ELSE output <= "00"; END IF; END CASE; END PROCESS; END rtl;

8.3 摩尔状态机设计(续1)

例8.2 四状态摩尔型有限状态机的描述。

BEGIN PROCESS (clk, reset) -- 状态转换的时序进程 BEGIN IF reset = '1' THEN state <= s0; ELSIF (clk'EVENT and clk='1') THEN CASE state IS WHEN s0=> IF input = '1' THEN ELSE END IF; WHEN s1=> IF input = '1' THEN ELSE END IF; WHEN s2=> IF input = '1' THEN ELSE END IF; WHEN s3 => IF input = '1' THEN ELSE END IF; END CASE; END IF; END PROCESS; PROCESS (state) -- 输出由当前状态唯一决定的组合逻辑进程 BEGIN CASE state IS WHEN s0 => output <= "00"; WHEN s1 => output <= "01"; WHEN s2 => output <= "10"; WHEN s3 => output <= "11"; END CASE; END PROCESS;

《VHDL状态机》课件

总结与展望

1 VHDL 状态机对数字电路设计的重要性

VHDL状态机能够将数字电路行为直观地表示出来,提高设计效率。

2 VHDL 状态机在工业自动化控制中的作用

VHDL状态机在自动化控制系统中扮演着重要的角色,提高系统的智能化。

3 VHDL 状态机的发展前景

随着数字电路和自动化技术的不断发展,VHDL状态机将继续发挥重要作用。

《VHDL状态机》PPT课件

VHDL状态机是一种描述数字电路行为的建模语言,本课件将介绍VHDL状态机 的定义、作用以及其在数字电路设计中的重要性。

什么是 VHDL 状态机

定义

VHDL状态机是一种用于描述数字电路中组合逻辑与时序逻辑之间关系的建模方法。

作用

VHDL状态机能够将数字电路行为清晰地表示出来,方便设计者进行分析和调试。

VHDL 状态机的设计方法

1

状态定义

确定所需的状态数量,并为每个状态指定一个唯一的编码。

2

状态转移

根据输入信号和当前状态,定义状态之间的转移条件。

3

输出定义

根据当前状态和输入信号,定义对应的输出信号。

1 VHDL 状态机设计实例

设计一个灯泡控制系统,根据不同输入信号以及当前状态控制灯泡的亮、灭。

VHDL 状态机的调试技巧

VHDL 状态机的基本结构

状态寄存器

用于存储当前状态信息,决 定下一状态的变化。

组合逻辑

根据输入信号和当前状态, 决定下一状态。

输出逻辑

根据当前状态和输入信号, 产生输出信号。

1 VHDL 状态机的两种类型

Moore 状态机:输出只与当前状态有关;Mealy 状态机:输出与当前状态和输入信号有关。

用VHDL设计有限状态机的方法

用VHDL设计有限状态机的方法现代数字系统的设计一般都采用自顶向下的模块化设计方法。

即从整个系统的功能出发,将系统分割成若干功能模块。

在自顶向下划分的过程中,最重要的是将系统或子系统按计算机组成结构那样划分成控制器和若干个受控制的功能模块。

受控部分通常是设计者们所熟悉的各种功能电路,设计较为容易。

主要任务是设计控制器,而其控制功能可以用有限状态机来实现。

因而有必要深入探讨有限状态机的设计方法。

1 状态机设计的一般方法 传统的设计方法是首先绘制出控制器的状态利用VHDL设计状态机,不需要进行繁琐的状态分配、绘制状态表和化简次态方程。

设计者不必使用卡诺(1)根据系统要求确定状态数量、状态转移的条件和各状态输出信号的赋值,并画出状态转移(2)按照状态转移(3)利用EDA工具对状态机的功能进行仿真验证。

下面以离心机定时顺序控制器的设计为例,说明状态机的设计方法。

2 定时顺序控制状态机的设计 在化工生产中,离心机用于固、液分离的工艺流程,如系统工作方式如下:当系统处于初始状态或复位信号reset有效时,系统处于复位状态。

按下自动工作键C0,系统进入加料工序并开始自动控制离心机的运行。

以加水工序为例,首先在加水预置数状态(water_ld)时,状态机输出信号FO,开启加水电磁阀及指示灯,同时输出信号G控制选通加水时间预置数,在LD1信号的控制下,将预置数送入COUNTER1。

此时ENA1=1,J=1,使计数器为减计数状态。

然后,在下一个时钟周期进入加水工作状态(water),并开始减计时。

当计时为零时,计数器发出借位信号R1作为此工序结束的信号送入状态机,使其转入。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

或

TYPE 数据类型名 IS 数据类型定义 ;

TYPE m_state IS

( st0,st1,st2,st3,st4,st5 ) ;

SIGNAL present_state,next_state : m_state ;

10.1 一般有限状态机的设计 10.1.2一般有限状态机的设计

1. 说明部分

高可靠性

10.1 VHDL状态机的一般形式

状态机分类

从状态机的信号输出方式上分,Mealy和Moore型 从状态机的描述结构上分,单进程和多进程 从状态表达方式上分,有符号化和确定状态编码 从状态机编码方式上分,有顺序、一位热式

数据类型定义语句

TYPE语句的用法如下: TYPE 数据类型名 IS 数据类型定义 OF 基本数据类型 ;

10.1 VHDL状态机的一般形式

10.1.2 一般有限状态机的设计

图10-2 例10-1状态机的工作时序

10.1 VHDL状态机的一般形式

10.1.3 状态机设计初始控制与表述

打开QuartusII状态图观察器

10.1 VHDL状态机的一般形式

10.1.3 状态机设计初始控制与表述

图10-3 例10-1的状态图

10.1 VHDL状态机的一般形式

10.1.1 为什么要使用状态机

状态机克服了纯硬件数字系统顺序方式控制不灵活的缺点 容易利用现成的EDA优化工具 性能稳定。状态机容易构成性能良好的同步时序逻辑模块 设计实现效率高。状态机的VHDL表述丰富多样、程序层次分明, 易读易懂 高速性能。在高速运算和控制方面,状态机更有其巨大的优势

ARCHITECTURE ...IS TYPE FSM_ST IS (s0,s1,s2,s3); SIGNAL current_state, next_state: FSM_ST; ...

2. 主控时序进程:负责状态机运转和在时钟驱动下负责状态 转换的进程

FSM: PROCESS REG next_state s_m achine PROCESS COM com b_outputs

EDA 技术实用教程

第 10 章 VHDL有限状态机设计

引言

▲ 广义而论状态机

涉及触发器应用的电路,无论大小都能归结成状态机 例如:D触发器构成的二分频电路,四位二进制计数器都可以算作一个状态机

▲有限状态机的应用

操作和控制流程非常明确的系统设计,在数字通信领域,自动控制 领域,CPU涉及等领域都有应用

10.2 Moore型有限状态机设计

10.2.1 ADC采样控制设计及多进程结构状态机

图10-7 ADC0809采样状态机工作时序

【例10-3】组合进程分成两个组合进程,结构清晰,分工明确 COM1: PROCESS(current_state,EOC) BEGIN CASE current_state IS WHEN st0=> next_state <= st1; WHEN st1=> next_state <= st2; WHEN st2=> IF (EOC='1') THEN next_state <= st3; ELSE next_state <= st2; END IF ; WHEN st3=> next_state <= st4;--开启OE WHEN st4=> next_state <= st0; WHEN OTHERS => next_state <= st0; END CASE ; END PROCESS COM1 ; COM2: PROCESS(current_state) BEGIN CASE current_state IS WHEN st0=>ALE<='0';START<='0';LOCK<='0';OE<='0' WHEN st1=>ALE<='1';START<='1';LOCK<='0';OE<='0' WHEN st2=>ALE<='0';START<='0';LOCK<='0';OE<='0' WHEN st3=>ALE<='0';START<='0';LOCK<='0';OE<='1' WHEN st4=>ALE<='0';START<='0';LOCK<='1';OE<='1' WHEN OTHERS => ALE<='0';START<='0';LOCK<='0'; END CASE ; END PROCESS COM2 ;

current_state

clk reset state_inputs

图10-1 一般状态机结构框图工作示意图

10.1.2 一般有限状态机的设计 3. 主控组合进程 主控组合进程的任务是根据外部输入的控制信号(包括来 自状态机外部的信号和来自状态机内部其它非主控的组合或时 序进程的信号),或(和)当前状态的状态值确定下一状态 (next_state)的取向,即next_state的取值内容,以及确定 对外输出或对内部其它组合或时序进程输出控制信号的内容。

COM:PROCESS(c_state, state_Inputs) --主控组合进程 BEGIN CASE c_state IS WHEN s0 => comb_outputs<= 5; IF state_inputs = "00" THEN next_state<=s0; ELSE next_state<=s1; END IF; WHEN s1 => comb_outputs<= 8; IF state_inputs = "01" THEN next_state<=s1; ELSE next_state<=s2; END IF; WHEN s2 => comb_outputs<= 12; IF state_inputs = "10" THEN next_state <= s0; ELSE next_state <= s3; END IF; WHEN s3 => comb_outputs <= 14; IF state_inputs = "11" THEN next_state <= s3; ELSE next_state <= s4; END IF; WHEN s4 => comb_outputs <= 9; next_state <= s0; WHEN OTHERS=> next_state <= s0; END case; END PROCESS; END behv;

START 0 1 0 0 0

ALE 0 1 0 0 0

OE 0 0 0 1 1

LOCK 0 0 0 0 1

EOC

功能说明 初始态 启动转换 若测得EOC=1时,转下一状态ST3 输出转换好的数据 利用LOCK的上升沿将转换好的数据锁存

0 0 1 0 0

10.2.1 ADC采样控制设计及多进程结构状态机

FSM: PROCESS REG next_state s_m achine PROCESS COM com b_outputs

current_state

clk reset state_inputs

4. 辅助进程:配合状态机工作的组合或时序进程

10.1 VHDL状态机的一般形式

10.1.2 一般有限状态机的设计

图10-6 采样状态机结构框图

【例10-2】

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY ADC0809 IS PORT(D : IN STD_LOGIC_VECTOR(7 DOWNTO 0); --来自0809转换好的8位数据 CLK,RST : IN STD_LOGIC; --状态机工作时钟 EOC : IN STD_LOGIC; --转换状态指示,低电平表示正在转换 ALE : OUT STD_LOGIC; --8个模拟信号通道地址锁存信号 START : OUT STD_LOGIC; --转换开始信号 OE : OUT STD_LOGIC; --数据输出3态控制信号 ADDA : OUT STD_LOGIC; --信号通道最低位控制信号 LOCK_T : OUT STD_LOGIC; --观察数据锁存时钟 Q : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); --8位数据输出 END ADC0809; ARCHITECTURE behav OF ADC0809 IS TYPE states IS (st0, st1, st2, st3,st4) ; --定义各状态子类型 SIGNAL current_state, next_state: states :=st0 ; SIGNAL REGL : STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL LOCK : STD_LOGIC; -- 转换后数据输出锁存时钟信号 BEGIN ADDA <= ‘0';--当ADDA<='0',模拟信号进入通道IN0; Q <= REGL; LOCK_T<= LOCK ; COM: PROCESS(current_state,EOC) BEGIN --规定各状态转换方式 CASE current_state IS WHEN st0=>ALE<='0';START<='0';LOCK<='0';OE<='0'; next_state <= st1; --0809初始化 (接下页)