数字电子技术试题及答案题库

数字电子技术试题及答案(题库)

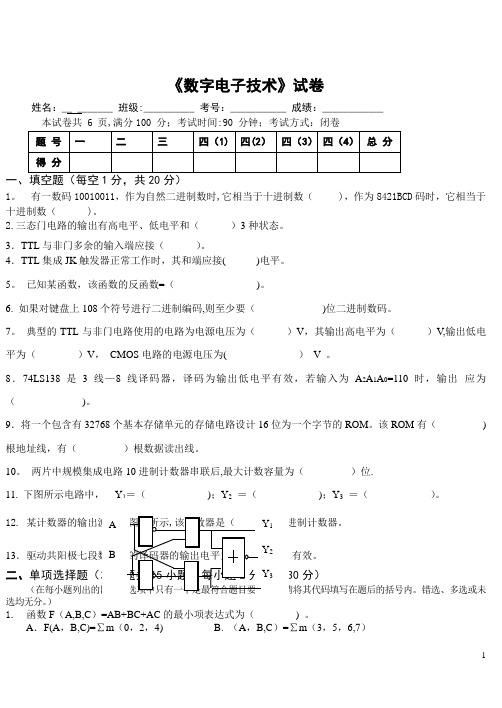

《数字电子技术》试卷姓名:__ _______ 班级:__________ 考号:___________ 成绩:____________本试卷共 6 页,满分100 分;考试时间:90 分钟;考试方式:闭卷1。

有一数码10010011,作为自然二进制数时,它相当于十进制数( ),作为8421BCD码时,它相当于十进制数( )。

2.三态门电路的输出有高电平、低电平和()3种状态。

3.TTL与非门多余的输入端应接()。

4.TTL集成JK触发器正常工作时,其和端应接( )电平。

5。

已知某函数,该函数的反函数=()。

6. 如果对键盘上108个符号进行二进制编码,则至少要()位二进制数码。

7。

典型的TTL与非门电路使用的电路为电源电压为()V,其输出高电平为()V,输出低电平为()V,CMOS电路的电源电压为( )V 。

8.74LS138是3线—8线译码器,译码为输出低电平有效,若输入为A2A1A0=110时,输出应为()。

9.将一个包含有32768个基本存储单元的存储电路设计16位为一个字节的ROM。

该ROM有()根地址线,有()根数据读出线。

10。

两片中规模集成电路10进制计数器串联后,最大计数容量为()位.11.);Y3=()。

12.13二、分)选均无分。

)1. 函数F(A,B,C)=AB+BC+AC的最小项表达式为() 。

A.F(A,B,C)=∑m(0,2,4) B. (A,B,C)=∑m(3,5,6,7)C.F(A,B,C)=∑m(0,2,3,4) D. F(A,B,C)=∑m(2,4,6,7)2.8线—3线优先编码器的输入为I0—I7,当优先级别最高的I7有效时,其输出的值是().A.111 B. 010 C。

000 D. 1013.十六路数据选择器的地址输入(选择控制)端有()个。

A.16 B.2 C。

4 D.84。

有一个左移移位寄存器,当预先置入1011后,其串行输入固定接0,在4个移位脉冲CP作用下,四位数据的移位过程是()。

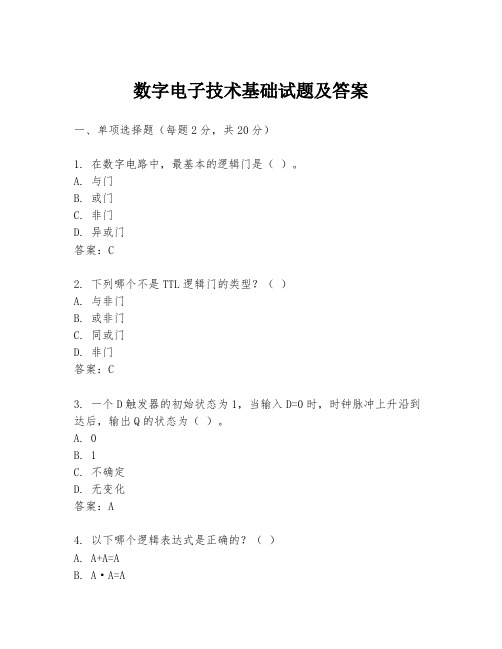

数字电子技术基础试题及答案

数字电子技术基础试题及答案一、单项选择题(每题2分,共20分)1. 在数字电路中,最基本的逻辑门是()。

A. 与门B. 或门C. 非门D. 异或门答案:C2. 下列哪个不是TTL逻辑门的类型?()A. 与非门B. 或非门C. 同或门D. 非门答案:C3. 一个D触发器的初始状态为1,当输入D=0时,时钟脉冲上升沿到达后,输出Q的状态为()。

A. 0B. 1C. 不确定D. 无变化答案:A4. 以下哪个逻辑表达式是正确的?()A. A+A=AB. A·A=AC. A+A=0D. A·A=0答案:B5. 一个4位二进制计数器,从0000开始计数,当计数到1111时,下一个状态是()。

A. 0000B. 1000C. 10000D. 0111答案:A6. 在数字电路中,若要实现一个逻辑函数,下列哪种方法最为经济?()A. 使用与非门B. 使用或非门C. 使用与门D. 使用或门答案:A7. 一个三态输出门,当控制端为高电平时,输出状态为()。

A. 高阻态B. 低电平C. 高电平D. 低阻态答案:C8. 以下哪个是BCD码的特点?()A. 每个十进制数字对应一个唯一的二进制代码B. 每个二进制数字对应一个唯一的十进制数字C. 每个二进制数字对应一个唯一的十六进制数字D. 每个十进制数字对应多个二进制代码答案:A9. 在数字电路中,一个反相器的逻辑功能是()。

A. 与B. 或C. 非D. 异或答案:C10. 一个JK触发器在时钟脉冲上升沿到达时,如果J=1,K=0,则触发器的状态()。

A. 保持不变B. 翻转C. 置0D. 置1答案:D二、填空题(每题2分,共20分)1. 一个2输入的与门,当两个输入都为1时,输出为______。

答案:12. 在数字电路中,一个D触发器的D端输入为0,时钟脉冲上升沿到达后,输出Q的状态为______。

答案:03. 一个4位二进制计数器,如果初始状态为0101,下一个状态为______。

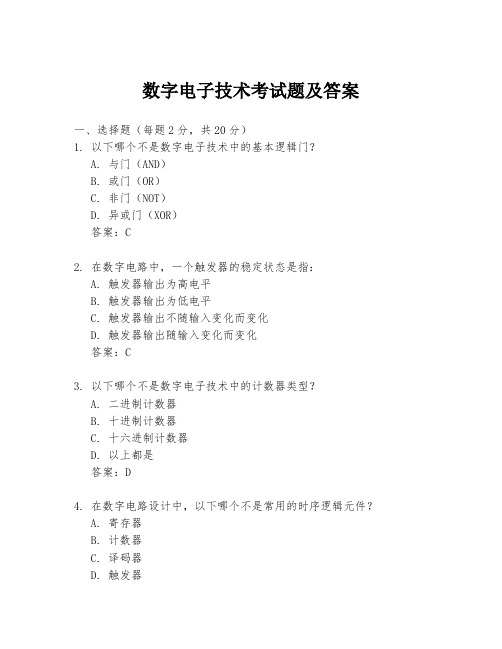

数字电子技术考试题及答案

数字电子技术考试题及答案一、选择题(每题2分,共20分)1. 以下哪个不是数字电子技术中的基本逻辑门?A. 与门(AND)B. 或门(OR)C. 非门(NOT)D. 异或门(XOR)答案:C2. 在数字电路中,一个触发器的稳定状态是指:A. 触发器输出为高电平B. 触发器输出为低电平C. 触发器输出不随输入变化而变化D. 触发器输出随输入变化而变化答案:C3. 以下哪个不是数字电子技术中的计数器类型?A. 二进制计数器B. 十进制计数器C. 十六进制计数器D. 以上都是答案:D4. 在数字电路设计中,以下哪个不是常用的时序逻辑元件?A. 寄存器B. 计数器C. 译码器D. 触发器答案:C5. 以下哪个不是数字电路的分类?A. 组合逻辑电路B. 时序逻辑电路C. 模拟电路D. 混合电路答案:C6. 一个简单的数字电子系统通常包括哪些基本部分?A. 输入、处理、输出B. 电源、输入、输出C. 输入、存储、输出D. 电源、输入、处理、输出答案:D7. 以下哪个不是数字电子技术中常用的存储元件?A. 触发器B. 寄存器C. 锁存器D. 放大器答案:D8. 在数字电子技术中,一个信号的上升时间是指:A. 信号从0%到90%的最大值所需的时间B. 信号从10%到90%的最大值所需的时间C. 信号从0%到100%的最大值所需的时间D. 信号从10%到100%的最大值所需的时间答案:A9. 以下哪个是数字电子技术中的同步电路的特点?A. 所有触发器的时钟信号是独立的B. 所有触发器的时钟信号是同步的C. 电路中没有时钟信号D. 电路中只有一个触发器答案:B10. 在数字电子技术中,以下哪个不是布尔代数的基本运算?A. 与(AND)B. 或(OR)C. 非(NOT)D. 除(DIV)答案:D二、填空题(每空2分,共20分)11. 在数字电路中,逻辑“1”通常表示电压为______,逻辑“0”通常表示电压为______。

数字电子技术试题及答案(题库)

数字电子技术基础试题(一)一、填空题 : (每空1分,共10分)1. (30.25) 10 = ( ) 2 = ( ) 16 。

2 . 逻辑函数L = + A+ B+ C +D = 。

3 . 三态门输出的三种状态分别为:、和。

4 . 主从型JK触发器的特性方程= 。

5 . 用4个触发器可以存储位二进制数。

6 . 存储容量为4K×8位的RAM存储器,其地址线为条、数据线为条。

二、选择题: (选择一个正确的答案填入括号内,每题3分,共30分 )1.设图1中所有触发器的初始状态皆为0,找出图中触发器在时钟信号作用下,输出电压波形恒为0的是:()图。

图 12.下列几种TTL电路中,输出端可实现线与功能的电路是()。

A、或非门B、与非门C、异或门D、OC门3.对CMOS与非门电路,其多余输入端正确的处理方法是()。

A、通过大电阻接地(>1.5KΩ)B、悬空C、通过小电阻接地(<1KΩ)D、通过电阻接V CC4.图2所示电路为由555定时器构成的()。

A、施密特触发器B、多谐振荡器C、单稳态触发器D、T触发器5.请判断以下哪个电路不是时序逻辑电路()。

图2A、计数器B、寄存器C、译码器D、触发器6.下列几种A/D转换器中,转换速度最快的是()。

图2A、并行A/D转换器B、计数型A/D转换器C、逐次渐进型A/D转换器D、双积分A/D转换器7.某电路的输入波形 u I 和输出波形 u O 如图 3所示,则该电路为()。

图3A、施密特触发器B、反相器C、单稳态触发器D、JK触发器8.要将方波脉冲的周期扩展10倍,可采用()。

A、10级施密特触发器B、10位二进制计数器C、十进制计数器D、10位D/A转换器9、已知逻辑函数与其相等的函数为()。

A、B、C、D、10、一个数据选择器的地址输入端有3个时,最多可以有()个数据信号输出。

A、4B、6C、8D、16三、逻辑函数化简(每题5分,共10分)1、用代数法化简为最简与或式Y= A +2、用卡诺图法化简为最简或与式Y= + C +A D,约束条件:A C + A CD+AB=0四、分析下列电路。

数字电子技术测试试卷与答案精选全文完整版

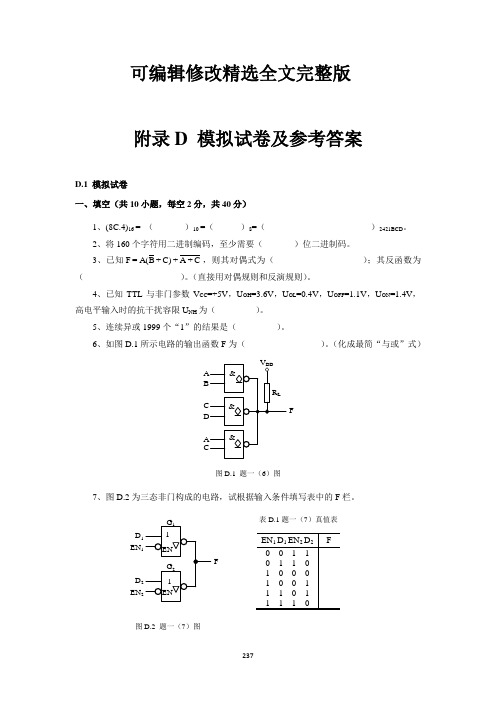

可编辑修改精选全文完整版附录D 模拟试卷及参考答案D.1 模拟试卷一、填空(共10小题,每空2分,共40分)1、(8C.4)16 = ( )10 =( )8=( )2421BCD 。

2、将160个字符用二进制编码,至少需要( )位二进制码。

3、已知F =A(B +C)+A +C ,则其对偶式为( );其反函数为( )。

(直接用对偶规则和反演规则)。

4、已知TTL 与非门参数V CC =+5V ,U OH =3.6V ,U OL =0.4V ,U OFF =1.1V ,U ON =1.4V ,高电平输入时的抗干扰容限U NH 为( )。

5、连续异或1999个“1”的结果是( )。

6、如图D.1所示电路的输出函数F 为( )。

(化成最简“与或”式)F图D.1 题一(6)图7、图D.2为三态非门构成的电路,试根据输入条件填写表中的F 栏。

图D.2 题一(7)图表D.1题一(7)真值表D 1EN 1D 2EN 2F8、设计模值为61的自然二进制码计数器、十进制计数器和余3 BCD码计数器分别需要()级、()级和()级触发器。

一个五位二进制加法计数器,由00000状态开始,问经过109个输入脉冲后,此计数器的状态为()。

9、用()片1024×4位的RAM可组成8K×8位的RAM,需要增加()条地址线、()条数据线。

10、在10位的倒T型电阻网络D/A转换器中,若U REF = ─10V,该D/A转换器能分辨的最小输出电压U LSB=()mV。

二、选择题(共10小题,每小题2分,共20分)1、有符号位二进制数的补码为(10011),则对应的十进制数为()。

A、-29B、+13C、-13D、-32、下列说法正确的是()。

A、n个变量所构成的全部最小项之和恒等于0B、n个变量所构成的全部最大项之和恒等于0C、n个变量所构成的全部最小项之积恒等于1D、n个变量所构成的全部最大项之积恒等于03、下列说法正确的是()。

数字电子技术试卷和答案

数字电子技术试卷和答案(总59页)--本页仅作为文档封面,使用时请直接删除即可----内页可以根据需求调整合适字体及大小--数字电子技术试卷(1)一.填空(16)1.十进制数123的二进制数是 1111011 ;十六进制数是 7B 。

2.是8421BCD码,其十进制为861 。

3.逻辑代数的三种基本运算是与,或和非。

4.三态门的工作状态是0 , 1 ,高阻。

5.描述触发器逻辑功能的方法有真值表,逻辑图,逻辑表达式,卡诺图,波形图。

6.施密特触发器的主要应用是波形的整形。

7.设4位D/A转换器的满度输出电压位30伏,则输入数字量为1010时的输出模拟电压为。

8.实现A/D转换的主要方法有,,。

二.判断题(10)1.BCD码即8421码(错)2.八位二进制数可以表示256种不同状态。

(对)3.TTL与非门与CMOS与非门的逻辑功能不一样。

()4.多个三态门的输出端相连于一总线上,使用时须只让一个三态门传送信号,其他门处于高阻状态。

(对)5.计数器可作分频器。

(对)三.化简逻辑函数(14)1.用公式法化简--+++=ADDCEBDBAY,化为最简与或表达式。

解;D B A Y +=-2.用卡诺图化简∑∑=m d D C B A Y ),,,,()+,,,,(84210107653),,,(,化为最简与或表达式。

四.电路如图1所示,要求写出输出函数表达式,并说出其逻辑功能。

(15) 解;C B A Y ⊕⊕=, C B A AB C )(1++=,全加器,Y 为和,1C 为进位。

五.触发器电路如图2(a ),(b )所示,⑴写出触发器的次态方程; ⑵对应给定波形画出Q 端波形(设初态Q =0)(15) 解;(1)AQ Q Qn +=-+1,(2)、A Q n =+1六.试用触发器和门电路设计一个同步的五进制计数器。

(15)七.用集成电路定时器555所构成的自激多谐振荡器电路如图3所示,试画出V O ,V C 的工作波形,并求出振荡频率。

数字电子技术试题库及答案

数字电子技术期末试题库一、选择题:A组:1.如果采用偶校验方式,下列接收端收到的校验码中,( A )是不正确的A、00100B、10100C、11011D、111102、某一逻辑函数真值表确定后,下面描述该函数功能的方法中,具有唯一性的是(B)A、逻辑函数的最简与或式B、逻辑函数的最小项之和C、逻辑函数的最简或与式D、逻辑函数的最大项之和3、在下列逻辑电路中,不是组合逻辑电路的是(D)A、译码器B、编码器C、全加器D、寄存器4、下列触发器中没有约束条件的是(D)A、基本RS触发器B、主从RS触发器C、同步RS触发器D、边沿D触发器5、555定时器不可以组成D。

A.多谐振荡器B.单稳态触发器C.施密特触发器D.J K触发器6、编码器(A)优先编码功能,因而(C)多个输入端同时为1。

A、有B、无C、允许D、不允许7、(D)触发器可以构成移位寄存器。

A、基本RS触发器B、主从RS触发器C、同步RS触发器D、边沿D触发器8、速度最快的A/D转换器是(A)电路A、并行比较型B、串行比较型C、并-串行比较型D、逐次比较型9、某触发器的状态转换图如图所示,该触发器应是( C )A. J-K触发器B. R-S触发器C. D触发器D. T触发器10.(电子专业作)对于VHDL以下几种说法错误的是(A )A VHDL程序中是区分大小写的。

B 一个完整的VHDL程序总是由库说明部分、实体和结构体等三部分构成C VHDL程序中的实体部分是对元件和外部电路之间的接口进行的描述,可以看成是定义元件的引脚D 结构体是描述元件内部的结构和逻辑功能B组:1、微型计算机和数字电子设备中最常采用的数制是--------------------------------( A )A.二进制B.八进制C. 十进制D.十六进制2、十进制数6在8421BCD码中表示为-------------------------------------------------( B )A.0101B.0110C. 0111D. 10003、在图1所示电路中,使__AY 的电路是---------------------------------------------( A )A. ○1B. ○2C. ○3D. ○44、接通电源电压就能输出矩形脉冲的电路是------------------------------------------( D )A. 单稳态触发器B. 施密特触发器C. D触发器D. 多谐振荡器5、多谐振荡器有-------------------------------------------------------------------------------( C )A. 两个稳态B. 一个稳态C. 没有稳态D. 不能确定6、已知输入A、B和输出Y的波形如下图所示,则对应的逻辑门电路是-------( D )A. 与门B. 与非门C. 或非门D. 异或门7、下列电路中属于时序逻辑电路的是------------------------------------------------------( B )A. 编码器B. 计数器C. 译码器D. 数据选择器8、在某些情况下,使组合逻辑电路产生了竞争与冒险,这是由于信号的---------( A )A. 延迟B. 超前C. 突变D. 放大9、下列哪种触发器可以方便地将所加数据存入触发器,适用于数据存储类型的时序电路--------------------------------------------------------------------------------( C )A. RS触发器B. JK触发器C. D触发器D. T触发器10、电路和波形如下图,正确输出的波形是-----------------------------------------------( A )A. ○1B. ○2C. ○3D. ○4C组:1.十进制数25用8421BCD码表示为 A 。

数字电子技术题库及答案

数字电子技术习题库一、单项选择题(本大题共15小题,每小题2分,共30分)(在每小题列出的四个备选项中只有一个是最符合题目要求的,请将其代码填写在题后的括号内。

错选、多选或未选均无分。

)1. 函数F(A,B,C)=AB+BC+AC 的最小项表达式为( ) 。

A .F(A,B,C)=∑m (0,2,4) B. (A,B,C)=∑m (3,5,6,7)C .F(A,B,C)=∑m (0,2,3,4) D. F(A,B,C)=∑m (2,4,6,7)2.8线—3线优先编码器的输入为I 0—I 7 ,当优先级别最高的I 7有效时,其输出012Y Y Y ••的值是( )。

A .111 B. 010 C. 000 D. 1013.十六路数据选择器的地址输入(选择控制)端有( )个。

A .16 B.2 C.4 D.84. 有一个左移移位寄存器,当预先置入1011后,其串行输入固定接0,在4个移位脉冲CP 作用下,四位数据的移位过程是( )。

A. 1011--0110--1100--1000--0000B.1011--0101--0010--0001--0000C. 1011--1100--1101--1110--1111D.1011--1010--1001--1000--01115.已知74LS138译码器的输入三个使能端(E 1=1, E 2A = E 2B =0)时,地址码A 2A 1A 0=011,则输出 Y 7 ~Y 0是( ) 。

A. 11111101B. 10111111C. 11110111D.111111116. 一只四输入端或非门,使其输出为1的输入变量取值组合有( )种。

A .15B .8C .7D .17. 随机存取存储器具有( )功能。

A.读/写B.无读/写C.只读D.只写8.N 个触发器可以构成最大计数长度(进制数)为( )的计数器。

9其计数的容量为A . 八 B. 五 C. 四 D. 三10.已知某触发的特性表如下(A 、B 为触发器的输入)其输出信号的逻辑表达式为( )。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《数字电子技术》试卷姓名:__ _______ 班级:__________ 考号:___________ 成绩:____________ 本试卷共 6 页,满分100 分;考试时间:90 分钟;考试方式:闭卷1. 有一数码10010011,作为自然二进制数时,它相当于十进制数( ),作为8421BCD 码时,它相当于十进制数( )。

2.三态门电路的输出有高电平、低电平和( )3种状态。

3.TTL 与非门多余的输入端应接( )。

4.TTL 集成JK 触发器正常工作时,其d R 和d S 端应接( )电平。

5. 已知某函数⎪⎭⎫ ⎝⎛+⎪⎭⎫ ⎝⎛++=D C AB D C A B F ,该函数的反函数F =( )。

6. 如果对键盘上108个符号进行二进制编码,则至少要( )位二进制数码。

7. 典型的TTL 与非门电路使用的电路为电源电压为( )V ,其输出高电平为( )V ,输出低电平为( )V , CMOS 电路的电源电压为( ) V 。

8.74LS138是3线—8线译码器,译码为输出低电平有效,若输入为A 2A 1A 0=110时,输出 01234567Y Y Y Y Y Y Y Y 应为( )。

9.将一个包含有32768个基本存储单元的存储电路设计16位为一个字节的ROM 。

该ROM 有( )根地址线,有( )根数据读出线。

10.两片中规模集成电路10进制计数器串联后,最大计数容量为( )位。

11. );Y 3 =( )。

12. 某计数器的输出波形如图1所示,该计数器是( )进制计数器。

13.驱动共阳极七段数码管的译码器的输出电平为( )有效。

二、单项选择题(本大题共15小题,每小题2分,共30分)(在每小题列出的四个备选项中只有一个是最符合题目要求的,请将其代码填写在题后的括号内。

错选、多选或未选均无分。

)1. 函数F(A,B,C)=AB+BC+AC 的最小项表达式为( ) 。

A .F(A,B,C)=∑m (0,2,4) B. (A,B,C)=∑m (3,5,6,7) C .F(A,B,C)=∑m (0,2,3,4) D. F(A,B,C)=∑m (2,4,6,7)2.8线—3线优先编码器的输入为I 0—I 7 ,当优先级别最高的I 7有效时,其输出012Y Y Y ••的值是( )。

A .111 B. 010 C. 000 D. 1013.十六路数据选择器的地址输入(选择控制)端有( )个。

A .16 B.2 C.4 D.84. 有一个左移移位寄存器,当预先置入1011后,其串行输入固定接0,在4个移位脉冲CP 作用下,四位数据的移位过程是( )。

A. 1011--0110--1100--1000--0000B. 1011--0101--0010--0001--0000C. 1011--1100--1101--1110--1111D. 1011--1010--1001--1000--01115.已知74LS138译码器的输入三个使能端(E 1=1, E 2A = E 2B =0)时,地址码A 2A 1A 0=011,则输出 Y 7 ~Y 0是( ) 。

A. 11111101B. 10111111C. 11110111D. 111111116. 一只四输入端或非门,使其输出为1的输入变量取值组合有( )种。

A .15 B .8 C .7 D .17. 随机存取存储器具有( )功能。

A.读/写 B.无读/写 C.只读 D.只写8.N 个触发器可以构成最大计数长度(进制数)为( )的计数器。

A.N B.2N C.N 2D.2N9.某计数器的状态转换图如下, 其计数的容量为( )A . 八 B. 五 C. 四 D. 三10.已知某触发的特性表如下(A 、BA . Q n+1 =A B. n n 1n Q A Q A Q +=+ C. n n 1n QB Q A Q +=+ D. Q n+1 = B 11. 有一个4位的D/A 转换器,设它的满刻度输出电压为10V ,当输入数字量为1101时,输出电压为( )。

A . 8.125V B.4V C. 6.25V D.9.375V 12.函数F=AB+BC ,使F=1的输入ABC 组合为( )A .ABC=000B .ABC=010C .ABC=101D .ABC=110 13.已知某电路的真值表如下,该电路的逻辑表达式为( )。

A .C Y = B. ABC Y = C .C AB Y +=D .C C B Y +=0 0 1 1 1 0 1 1 0 1 0 0 1 1 0 1 0111111114.四个触发器组成的环行计数器最多有( )个有效状态。

A.4 B. 6 C. 8 D. 16三、判断说明题(本大题共2小题,每小题5分,共10分)(判断下列各题正误,正确的在题后括号内打“√”,错误的打“×”。

) 1、逻辑变量的取值,1比0大。

( )2、D/A 转换器的位数越多,能够分辨的最小输出电压变化量就越小( )。

3.八路数据分配器的地址输入(选择控制)端有8个。

( ) 4、因为逻辑表达式A+B+AB=A+B 成立,所以AB=0成立。

( )5、利用反馈归零法获得N 进制计数器时,若为异步置零方式,则状态S N 只是短暂的过渡状态,不能稳定而是立刻变为0状态。

( )6.在时间和幅度上都断续变化的信号是数字信号,语音信号不是数字信号。

( )7.约束项就是逻辑函数中不允许出现的变量取值组合,用卡诺图化简时,可将约束项当作1,也可当作 0。

( )8.时序电路不含有记忆功能的器件。

( )9.计数器除了能对输入脉冲进行计数,还能作为分频器用。

( )10.优先编码器只对同时输入的信号中的优先级别最高的一个信号编码. ( )四、综合题(共30分)1.对下列Z 函数要求:(1)列出真值表;(2)用卡诺图化简;(3)画出化简后的逻辑图。

(8分)Z=C B A C B A B A ••+••+ BC=0(1)真值表(2分)(2)卡诺图化简(2分)(3) 表达式(2分)逻辑图(2分)2.试用3线—8线译码器74LS138和门电路实现下列函数。

(8分)Z(A、B、C)=AB+A C3.74LS161是同步4位二进制加法计数器,其逻辑功能表如下,试分析下列电路是几进制计数器,并画出其状态图。

(8分)74LS161逻辑功能表CP“1”””4.触发器电路如下图所示,试根据CP及输入波形画出输出端Q1、Q2 的波形。

设各触发器的初始状态均为“0”(6分)。

CPAQ1Q2《数字电子技术》A卷标准答案一、填空题(每空1分,共20分)DC B AD C A B ++1. 147 , 93 2. 高阻 3. 高电平或悬空 4. 高 5. F =6. 77. 5 , 3.6 ,0.35 , 3—18 8. 10111111 9. 11 ,1610. 100 11. Y 1=A B ; Y 2=A B + A B ;Y 3=A B 13. 5 14.低 二、选择题(共30分,每题2分)1 2 3 4 5 6 7 8 910 11 12 13 1415 A C C A C A A DB C AD CDB 三、判断题(每题2分,共20分)1 2 3 4 5 6 7 8 9 10 ×√××√√√×√√四、综合题(共30分,每题10分)1.解:(1)真值表 (2分) (2)卡诺图化简(2分)( 3 ) 表达式(2分, ( 4 ) 逻辑图(2分) Z=C B A B A++=A ⊕B+C BC=0ZCB A2. 解:Z (A 、B 、C )=AB +A C =AB (C +C )+A C (B +B )=ABC +AB C +A BC +A B C = m 1+ m 3+ m 6+ m 7=7 6 3 1 m m m m ••• (4分)3.解:1.当74LS161从0000开始顺序计数到1010时,与非门输出“0”,清零信号到来,异步清零。

(2分) 2.该电路构成同步十进制加法计数器。

(2分) 3.状态图(4分)4.Q 1、Q 2的波形各3分。

CP” ” ”“Z《数字电子技术》试卷姓名:__ _______ 班级:__________ 考号:___________ 成绩:____________ 本试卷共 6 页,满分100 分;考试时间:90 分钟;考试方式:闭卷1. 有一数码10010011,作为自然二进制数时,它相当于十进制数( ),作为8421BCD 码时,它相当于十进制数( )。

2.三态门电路的输出有高电平、低电平和( )3种状态。

3.TTL 与非门多余的输入端应接( )。

4.TTL 集成JK 触发器正常工作时,其d R 和d S 端应接( )电平。

5. 已知某函数⎪⎭⎫ ⎝⎛+⎪⎭⎫ ⎝⎛++=D C AB D C A B F ,该函数的反函数F =( )。

6. 如果对键盘上108个符号进行二进制编码,则至少要( )位二进制数码。

7. 典型的TTL 与非门电路使用的电路为电源电压为( )V ,其输出高电平为( )V ,输出低电平为( )V , CMOS 电路的电源电压为( ) V 。

8.74LS138是3线—8线译码器,译码为输出低电平有效,若输入为A 2A 1A 0=110时,输出 01234567Y Y Y Y Y Y Y Y 应为( )。

9.将一个包含有32768个基本存储单元的存储电路设计16位为一个字节的ROM 。

该ROM 有( )根地址线,有( )根数据读出线。

10. 两片中规模集成电路10进制计数器串联后,最大计数容量为( )位。

11. );Y 3 =( )。

12. 某计数器的输出波形如图1所示,该计数器是( )进制计数器。

13.驱动共阳极七段数码管的译码器的输出电平为( )有效。

二、单项选择题(本大题共15小题,每小题2分,共30分)(在每小题列出的四个备选项中只有一个是最符合题目要求的,请将其代码填写在题后的括号内。

错选、多选或未选均无分。

)1. 函数F(A,B,C)=AB+BC+AC 的最小项表达式为( ) 。

A .F(A,B,C)=∑m (0,2,4) B. (A,B,C)=∑m (3,5,6,7) C .F(A,B,C)=∑m (0,2,3,4) D. F(A,B,C)=∑m (2,4,6,7)2.8线—3线优先编码器的输入为I 0—I 7 ,当优先级别最高的I 7有效时,其输出012Y Y Y ••的值是( )。

A .111 B. 010 C. 000 D. 1013.十六路数据选择器的地址输入(选择控制)端有( )个。

A .16 B.2 C.4 D.84. 有一个左移移位寄存器,当预先置入1011后,其串行输入固定接0,在4个移位脉冲CP 作用下,四位数据的移位过程是( )。