ASIC设计实例(verilog)

可编程ASIC设计实训报告

可编程ASIC设计实训报告1.引言1.1 概述概述:可编程ASIC(Application-Specific Integrated Circuit)设计是一种针对特定应用领域进行定制优化的集成电路设计方法。

与传统的ASIC 设计相比,可编程ASIC设计可以在不改变硬件的情况下,通过重新编程实现不同的功能和逻辑。

在本报告中,我们将介绍可编程ASIC设计的基本概念和原理,以及在实训中搭建设计环境和进行设计实例分析的具体过程和方法。

通过本报告的学习,读者可以深入了解可编程ASIC设计的实践应用,以及进一步掌握ASIC设计的相关技术和方法。

文章结构部分的内容可以包括对整篇文章的组织架构和每个部分的内容概述。

可以介绍文章的逻辑顺序以及每个部分的重点内容和目的。

同时,文章结构部分也可以包括对整篇文章的写作目的和读者对象的介绍。

": , "3.2 成果展示": ,"3.3 展望":请编写文章1.2 文章结构部分的内容1.3 目的目的部分:通过本报告的撰写和实训内容的呈现,旨在让读者了解可编程ASIC设计的基本概念和原理,掌握实训环境搭建的方法和技巧,以及通过设计实例分析进行实际操作,从而提升对可编程ASIC设计的理解和应用能力。

同时,通过总结和成果展示,展示实训成果,激发更多人对可编程ASIC设计领域的兴趣,为未来的发展展望提供参考。

2.正文2.1 可编程ASIC设计简介可编程ASIC(Application Specific Integrated Circuit)是一种专门定制的集成电路,与传统的ASIC相比,可编程ASIC具有更高的灵活性和可编程性。

可编程ASIC设计允许工程师在硅片上实现特定的电路功能,同时又可以根据需求进行修改和重新配置,从而实现多种功能的实现。

可编程ASIC设计的主要特点包括灵活性、可编程性和高性能。

通过使用可编程ASIC,设计人员可以快速构建复杂的数字电路,同时减少电路设计的时间和成本。

Verilog的135个经典设计实例

Verilog的135个经典设计实例1、立即数放大器:立即数放大器是一种用于将输入电平放大到更高电平的电路,它可以实现任意输入到输出的映射,并且可以在Verilog中使用。

立即数放大器的Verilog实现如下:module immedamp(in, out);input in;output out;reg [3:0] immed;assign out = immed[3];begincase (in)4'b0000: immed = 4'b1000;4'b0001: immed = 4'b1001;4'b0010: immed = 4'b1010;4'b0011: immed = 4'b1011;4'b0100: immed = 4'b1100;4'b0101: immed = 4'b1101;4'b0110: immed = 4'b1110;4'b0111: immed = 4'b1111;4'b1000: immed = 4'b1000;4'b1001: immed = 4'b1001;4'b1010: immed = 4'b1010;4'b1011: immed = 4'b1011;4'b1100: immed = 4'b1100;4'b1101: immed = 4'b1101;4'b1110: immed = 4'b1110;4'b1111: immed = 4'b1111;endcaseendendmodule2、多路复用器:多路复用器是一种用于将多个输入选择转换为单个输出的电路,它可以实现由多种方式选择的输出,并可以使用Verilog实现。

ASIC设计举例

先 用 Microwind中的 压焊盘 (PAD)生成命令,

正电源线+Vdd 接地线

生成一个具有 Pad Ring 的空白芯片. 然后反复

压焊块 PAD

运用Insert , Copy, Move 等命令,将 已设计好的 模块与单元电路, 按布 图规划放到芯片上. 再 用连线将它们互连起来. 其间应经常进行设计规 则检查与模拟测试.有 错随时纠正.

T T 触 发 器的 版 图 与 电 路 图

2

© Digital Integrated Circuits2nd Manufacturing

2. COUNT60 模 块 版 图

© Digital Integrated Circuits2nd Manufacturing

M.D. 2.COUNT60 计 数 器 版 图 模 拟 测 试 波 形Manufacturing © Digital Integrated Circuits2nd

© Digital Integrated Circuits2nd Manufacturing

步骤 1

步骤 2

步骤 3

步骤 4

得 成 功 的 关 键 !

步骤 5

© Digital Integrated Circuits2nd

自 始 至 终 运 用 正 确 的 设 计 策 略 是 取 Manufacturing

© Digital Integrated Circuits2nd

Manufacturing

Design Flow

第三、四步:

逻 辑 设 计和 电 路 设 计

逻辑设计的主要任务是得到一个实现系统功能的逻辑结构,并对它进行模拟 ,验证其正确性。设计中采用逻辑图来表示系统的逻辑结构。 电路设计的任务是将逻辑部件细化到由各个基本门电路互连的结构,进而细 化到由晶体管互连的电路结构,通常采用详细的电路图来表示设计结果。我们用 设计软件来完成逻辑设计与电路设计。DSCH软件能够进行逻辑图与电路图的输 入与模拟验证。

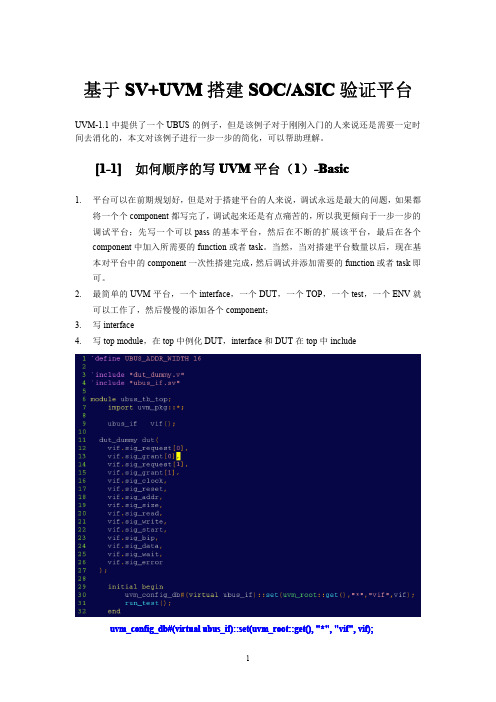

利用Systemverilog+UVM搭建SOC及ASIC的RTL验证环境

基于SV+UVM搭建SOC/ASIC验证平台UVM-1.1中提供了一个UBUS的例子,但是该例子对于刚刚入门的人来说还是需要一定时间去消化的,本文对该例子进行一步一步的简化,可以帮助理解。

[1-11]如何顺序的写UVM平台(1)-Basic[1-1.平台可以在前期规划好,但是对于搭建平台的人来说,调试永远是最大的问题,如果都将一个个component都写完了,调试起来还是有点痛苦的,所以我更倾向于一步一步的调试平台;先写一个可以pass的基本平台,然后在不断的扩展该平台,最后在各个component中加入所需要的function或者task。

当然,当对搭建平台数量以后,现在基本对平台中的component一次性搭建完成,然后调试并添加需要的function或者task即可。

2.最简单的UVM平台,一个interface,一个DUT,一个TOP,一个test,一个ENV就可以工作了,然后慢慢的添加各个component;3.写interface4.写top module,在top中例化DUT,interface和DUT在top中includeuvm_config_db#(virtual ubus_if)::set(uvm_root::get(),"*","vif",vif);run_test();5.写Makefile,此时编译可以通过6.写自定义的package,然后在top中include该packagetypedef uvm_config_db#(virtual ubus_if)ubus_vif_config;typedef virtual ubus_if ubus_vif;后来证明,这两句话在ubus的env中根本没有用上;7.定义Environment,并将该文件加入到自定义的package中,这个时候编译不能通过此处的get和top中的set是一对,如果top中没有set则会报告·uvm_fatal中的错误if(!uvm_config_db#(virtual ubus_if)::get(this,"","vif",vif))`uvm_fatal("NOVIF",{"virtual interface must be set for: ",get_full_name(),".vif"});8.定义base_test,需要在top中include该test文件,并在makefile中加入编译该test的命令;此时可以再次编译通过,并运行最basic的testcase编译第一次通过总结一:在一个芯片的验证平台中,总会给一个最basic 的base_test ,但是可能每个人负责验证的部分是不一样的,比如说我要验证USB ,那我一定会从base_test 中派生一个usb_base_test 来给自己用,这样我可以在usb_base_test 加入任何我想要的函数,而不会影响到其他人。

用verilog-a写的一些电路模块的例子

用verilog-a写的一些电路模块的例子以下是几个用Verilog-A 语言编写的电路模块的例子:1. 增益电路模块````include "disciplines.vams"module gain_circuit(va, vb, vout, g);input va, vb;output vout;parameter real g=10.0;analog beginvout = g * (va - vb);endendmodule```这个例子展示了一个简单的增益电路模块,其中输入是两个电压va、vb,输出是vout,增益系数为g。

在模块中使用了Verilog-A 的`analog begin` 语句来定义电路的行为。

2. RC 低通滤波器模块````include "disciplines.vams"module rc_lowpass_filter(vin, vout, r, c);input vin;output vout;parameter real r=1.0, c=1e-6;real v1;analog begini(vin, v1) <+ (vin - v1)/(r*c);vout <+ v1;endendmodule```这个例子展示了一个基于RC 电路的低通滤波器模块,其中输入为vin,输出为vout,RC 电路的参数由r 和c 决定。

在模块中使用了Verilog-A 的`i()` 语句来定义电路的行为。

3. 三角波发生器模块````include "disciplines.vams"module triangle_wave_generator(vout, freq, amp, dc);output vout;parameter real freq=1e3, amp=1.0, dc=0.0;real t;analog begint = $abstime;vout <+ amp * (2 * (t * freq - floor(t * freq + 0.5)) - 1) + dc;endendmodule```这个例子展示了一个简单的三角波发生器模块,其中输出为vout,频率由freq 决定,幅值由amp 决定,直流分量由dc 决定。

ASIC_Onehot_code Verilog实现

ASIC设计作业——Verilog HDL 设计产生One_Hot Code专业:电子科学与技术班级:学号:姓名:Beijing University ofPostsandTelecommunicationsASIC 设计作业——Verilog HDL 设计产生One_Hot Code姓名: 学号: 班级:一、名词解释——One-Hotcode独热码,在英文文献中称做 one-hot code, 直观来说就是有多少个状态就有多少比特,而且只有一个比特为1,其他全为0的一种码制。

通常,在通信网络协议栈中,使用八位或者十六位状态的独热码,且系统占用其中一个状态码,余下的可以供用户使用。

例如,有6个状态的独热码状态编码为:000001,000010,000100,001000,010000,100000。

二、独热码的生成模块的代码编写//File :one_hot_zp.v //Autor: zhangpeng//Date : 06/11/2013 //Version: 1.04//Abstraco: This file make out at the tool of Modelsim.// The function of this module is produce the// One_Hotcode.The module has three ports,// they are clk,rst and onehot. //Modeification history://Date BY Version Change Description //06/10/2013 zhangpeng 1.0 Original,have some ? //06/11/2013 zhangpeng 1.04 change clk,rst; ok //moduleonehot_zp(inputclk, // System clock, can change if neccessary inputrst, // System resetoutputreg [9:0] onehot // output onehot );reg [3:0] counter = 0;//variable,to fractional frequency reg [3:0] state = 0;// the ten states will map the one_hot codealways @ (posedgeclk, negedgerst)if (!rst)counter<= 0;文件头部分这个模块是生成独热码模块 复位,低电平信号时实现输入复位信号elsecounter<= counter + 1'b1;always @ (posedge counter[3])//counter 的最高位上升沿触发 if (!rst)state <= 0; // 复位是,状态置初始状态 elsebegin //counter 的最高位每次为高时,state 加1转到下一位 if (state == 4'b1001) state<= 0; elsestate<= state + 1'b1; endalways @ (posedgeclk, negedgerst) if (!rst)//重置信号,低有效 onehot<= 0; else begincase (state) //根据state 的状态转移,每个状态对应输出一个独热码 default: onehot<= 10'b00000_00001;4'b0000: onehot<= 10'b00000_00001;4'b0001: onehot<= 10'b00000_00010;4'b0010: onehot<= 10'b00000_00100; 4'b0011: onehot<= 10'b00000_01000; 4'b0100: onehot<= 10'b00000_10000; 4'b0101: onehot<= 10'b00001_00000; 4'b0110: onehot<= 10'b00010_00000; 4'b0111: onehot<= 10'b00100_00000; 4'b1000: onehot<= 10'b01000_00000; 4'b1001: onehot<= 10'b10000_00000;endcase endendmodule三、测试程序的代码编写//File: onehot_zp_test //Author: zhangpeng //Date: 06/12/2013 //Version: 1.0// Function: This module is the file of testbeach.The function of this module is to // test the module of onehot_zp that I make out whether can work normally这里,利用前面的生成的不同的状态,使每一个状态生成相应的独热码,最后将独热码送输出 这里default 最好写在前面,有利于综合同时给出初始状态 分频计数器// or not. //`timescale 1 ns / 1 ns //moduleonehot_zp_test; regclk_t; regrst_t;wire [9:0] onehot_t;完成变量的声明 //例化被测试模块onehot_zponehot_zp_inst(.clk (clk_t),.rst (rst_t), .onehot (onehot_t) );//产生输入激励 initialbeginclk_t = 0;while (1) //利用while ()循环,条件值为1;产生时钟激励 #10 clk_t = ~clk_t; //延时10个时间单位翻转一次 endinitial begin rst_t = 0; forever#20rst_t = 1; End//显示输出结果initialbegin$monitor("At time %t,clk_t=%d, rst_t=%d, onehot_t=%b", $time, clk_t, rst_t,onehot_t); $finish; end//establish task expect,dispaly every step state task expect;input [10:0]expects;if({onehot_t}!=expects) begin$display("At time %t state is %b , expects is %b,wrong",$time,onehot_t,expects); $display("Test failed"); $finish end下面是测试程序模块 测试模块实例化 激励产生部分 输出送显示,在仿真器的脚本文件里面记录下输出的信号情况 输出与期望值对比部分else$display("one step succeeds"); endtaskinitialbegin@(posedgeclk)rst_n=1'b0;@(posedgeclk)#20 expect(10'b0000000001); @(posedgeclk)rst_n=1'b1;#20 expect(10'b0000000010); @(posedgeclk)#20 expect(10'b0000000100); @(posedgeclk)#20 expect(10'b0000001000); @(posedgeclk)#20 expect(10'b0000010000);@(posedgeclk)#20 expect(10'b0000100000); @(posedgeclk)#20 expect(10'b0001000000); @(posedgeclk)#20 expect(10'b0010000000); @(posedgeclk)#20 expect(10'b010*******); @(posedgeclk)#20 expect(10'b1000000000); $display("succeed"); $finish endendmodule四、仿真波形1、整体情况图分析:从图中,我们可以清晰的看到10位的变量onehot 随着仿真时时钟的行走,按照预先独热码产生模块里面写得一样,输出了准确的值。

asic实验报告

asic实验报告ASIC实验报告引言ASIC(Application-Specific Integrated Circuit)是一种专用集成电路,它被广泛应用于各种领域,包括通信、计算机、医疗、汽车等。

本实验报告旨在介绍ASIC的基本原理、设计流程以及应用案例,以便更好地理解和应用这一技术。

一、ASIC的基本原理ASIC是根据特定应用需求而设计的集成电路,相比通用集成电路(如微处理器),ASIC具有更高的性能和更低的功耗。

ASIC的设计基于硬件描述语言(HDL),如Verilog或VHDL,通过对电路逻辑的描述来实现特定功能。

ASIC的设计流程包括电路设计、逻辑综合、布局布线和验证等步骤,最终生成可用于生产的掩模。

二、ASIC的设计流程1. 电路设计:在这一阶段,根据应用需求和功能规格书,设计师使用HDL语言描述电路的逻辑功能。

这包括组合逻辑和时序逻辑的设计,并考虑到时钟频率、功耗和面积等方面的优化。

2. 逻辑综合:逻辑综合将HDL描述的电路转化为门级电路的表示形式。

在这一过程中,综合工具会根据约束条件(如时钟频率)进行优化,并生成电路的结构和时序信息。

3. 布局布线:布局布线是将逻辑综合结果映射到物理层面的过程。

此阶段包括将逻辑电路映射到物理单元(如逻辑门、寄存器)和进行连线布局,以满足时序和电气约束。

4. 验证:验证是ASIC设计流程中至关重要的一步。

通过仿真和验证工具,设计师可以验证电路的功能和时序,并进行调试和优化。

三、ASIC的应用案例1. 通信领域:ASIC在通信领域中扮演着重要的角色。

例如,ASIC可以用于实现高性能的调制解调器,以提供更快速和可靠的数据传输。

此外,ASIC还可以用于实现各种通信协议的编解码器,如以太网、USB和HDMI等。

2. 计算机领域:ASIC在计算机领域中也有广泛的应用。

例如,ASIC可以用于实现高性能的图形处理器(GPU),以提供更好的图形渲染和计算性能。

ASIC设计流程(精选5篇)

ASIC设计流程(精选5篇)第一篇:ASIC设计流程1.使用语言:VHDL/verilog HDL2.各阶段典型软件介绍:输入工具:Summit ,ultraeditSummit公司,ultraedit仿真工具:VCS, VSSSynopsys 公司综合器:DesignCompile, BC CompileSynopsys 公司布局布线工具:Preview 和Silicon EnsembleCadence公司版图验证工具:Dracula, DivaCadence公司静态时序分析: Prime TimeSynopsys 公司测试:DFTCompileSynopsys 公司3.流程第一阶段:项目策划形成项目任务书(项目进度,周期管理等)。

流程:【市场需求--调研--可行性研究--论证--决策--任务书】。

第二阶段:总体设计确定设计对象和目标,进一步明确芯片功能、内外部性能要求,参数指标,论证各种可行方案,选择最佳方式,加工厂家,工艺水准。

流程:【需求分析--系统方案--系统设计--系统仿真】。

第三阶段:详细设计和可测性设计分功能确定各个模块算法的实现结构,确定设计所需的资源按芯片的要求,速度,功耗,带宽,增益,噪声,负载能力,工作温度等和时间,成本,效益要求选择加工厂家,实现方式,(全定制,半定制,ASIC,FPGA等);可测性设计与时序分析可在详细设计中一次综合获得,可测性设计常依据需要采用FullScan,PartScan等方式,可测性设计包括带扫描链的逻辑单元,ATPG,以及边界扫描电路BoundScan,测试Memory的BIST。

流程:【逻辑设计--子功能分解--详细时序框图--分块逻辑仿真--电路设计(算法的行为级,RTL级描述)--功能仿真--综合(加时序约束和设计库)--电路网表--网表仿真】。

第四阶段:时序验证与版图设计静态时序分析从整个电路中提取出所有时序路径,然后通过计算信号沿在路径上的延迟传播,找出违背时序约束的错误(主要是SetupTime 和HoldTime),与激励无关。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ASIC设计实例 ASIC设计实例

设计一个交通灯信号控制电路。 要求输入为1KHz的时钟和复位信号,输出为 红、绿、黄三个信号(高电平为亮)。 具体描述:复位信号(低电平)有效,红、 绿、黄灯灭;接着进行如下循环:绿灯亮60 秒,黄灯闪烁10秒(闪烁周期是1秒),红 灯亮60秒。

设计端口及需求: 设计端口及需求:

always @(posedge clk) //??(50MHz->1KHz) begin if(~reset) begin count<=0; clk_scan<=0; end else begin if(count==25000) begin count<=0; clk_scan<=~clk_scan; end else count<=count+1; end end

always @(posedge clk_scan,negedge reset) //第5位 begin if (~reset) five<=0; else begin if (one==9 && two==9 && three==9 && four==9 && five==9) five<= 0; else begin if (one==9 && two==9 && three==9 && four==9) five<=five+1; end end end

always @(posedge clk_scan,negedge reset) //第4位 begin if (~reset) four<=0; else begin if (one==9 && two==9 && three==9 && four==9) four<= 0; else begin if (one==9 && two==9 && three==9) four<=four+1; end end end

always @(posedge clk) //产生扫描信号 产生扫描信号 begin if (~reset) sel_temp<=3'b000; else sel_temp<=sel_temp+1; end

always @(posedge clk_scan,negedge reset) //第1位 第 位 begin if (~reset) one<=0; else begin if (one==9) one<=0; else one<=one+1; end end

always @(posedge clk_scan,negedge reset) //第2位 第 位 begin if (~reset) two<=0; else begin if (one==9 && two==9) two<= 0; else begin if (one==9) two<=two+1; end end end

end

ASIC设计实例 ASIC设计实例

设计端口及需求: 设计端口及需求:

D0—D6 Clk(50MHz) reset sel0 sel1 sel2

段值

D0—D6

D6 D5 D4 D3 D2 D1 D0

位选

sel0 sel1 sel2

0 1 2 3

D5 D4 D3 D2 D1 D0 位5 位4 位3 位2

always @(dis_out_temp) //根据扫描值选择当前 always @(sel_temp) 显示的位 //根据扫描值选择当前显示的位 begin begin case (dis_out_temp) sel<= sel_temp; 0:ledout=7'b1111110;//dis_out_temp<=0; case (sel_temp) 1:ledout=7'b0110000;//dis_out_temp<=1; 3'b000:dis_out_temp=one; 2:ledout=7'b1101101;//dis_out_temp<=2; 3:ledout=7'b1111001;//dis_out_temp<=3; 3'b001:dis_out_temp=two; 4:ledout=7'b0110011;//dis_out_temp<=4; 3'b010:dis_out_temp=three; 5:ledout=7'b1011011;//is_out_temp<=5; 3'b011:dis_out_temp=four; 6:ledout=7'b1011111;//dis_out_temp<=6; 3'b100:dis_out_temp=five; 7:ledout=7'b1110000;//dis_out_temp<=7; 3'b101:dis_out_temp=six; 8:ledout=7'b1111111;//dis_out_temp<=8; 3'b110:dis_out_temp=seven; 9:ledout=7'b1111011;//dis_out_temp<=9; 3'b111:dis_out_temp=eight; default:ledout=7'b1111011;//dis_out_temp<=7; default:dis_out_temp=eight; endcase; endcase; end end endmodule

always @(posedge clk_scan,negedge reset) //第3位 第 位 begin if (~reset) three<=0; else begin if (one==9 && two==9 && three==9) three<= 0; else begin if (one==9 && two==9) three<=three+1; end end end

4 5位1 位074来自S 138数码管为 共阴极

设计需要知识点: 设计需要知识点: 1. 如何分频? 如何分频? 2. 数码管动态显示原理及设计代码? 数码管动态显示原理及设计代码? 3. 芯片接口电路时序设计

module display(clk,ledout,sel,reset); input clk; input reset; output reg [6:0] ledout; output reg [2:0] sel; reg [14:0] count; reg clk_scan; reg [2:0] sel_temp;

always @(posedge clk1k , reset) if(~reset) begin count2<=0; G<=1'b0; Y<=1'b0; R<=1'b0; end else begin if(count2==129999) begin count2<=0; end else begin if(count2>=0 && count2<60000) begin G<=1'b1; Y<=1'b0; R<=1'b0; count2<=count2+1; end

module count(clk,ledout,sel,reset); input clk; input reset; output reg [6:0] ledout; output reg [2:0] sel; reg [14:0] count; reg clk_scan; reg [3:0] dis_out_temp,one,two,three, four,five,six,seven,eight; reg [2:0] sel_temp;

`timescale 1ns/1ns module testbench; reg clk,reset; wire [6:0] ledout; wire [2:0] sel; parameter dely=10;

//test module

count test(clk,ledout,sel,reset); always #(dely/2) clk=~clk; initial begin reset=1; clk=0; #dely reset=0; #(dely*8) reset=1; end endmodule

always @(posedge clk_scan,negedge reset) //第6位 begin if (~reset) six<=0; else begin if (one==9 && two==9 && three==9 && four==9 && five==9 && six==9) six<= 0; else begin if (one==9 && two==9 && three==9 && four==9 && five==9) six<=six+1; end end end

always @(posedge clk_scan,reset) begin if (~reset) begin sel_temp<=3'b000; end else sel_temp<=sel_temp+1; end

always @(posedge clk) //??????? begin sel<= sel_temp; case (sel_temp) 3'b000:ledout=7'b1111110; 3'b001:ledout=7'b0110000; 3'b010:ledout=7'b1101101; 3'b011:ledout=7'b1111001; 3'b100:ledout=7'b0110011; 3'b101:ledout=7'b1011011; 3'b110:ledout=7'b1011111; 3'b111:ledout=7'b1110000; default:ledout=7'b0000000; endcase; end endmodule