Verilog语言示例

verilog模块例化实例

verilog模块例化实例以下是一个Verilog模块的实例化示例:假设有一个简单的4位加法器模块(add4), 输入包括两个4位数(a和b),输出为一个5位数(sum)。

现在我们希望实例化这个模块来构建一个8位的加法器。

module add4 (input [3:0] a,input [3:0] b,output [4:0] sum);assign sum = a + b;endmodule现在,我们可以在一个顶层模块中实例化这个add4模块,并将其连接起来。

module top_module (input [7:0] a,input [7:0] b,output [8:0] sum);wire [3:0] a_part;wire [3:0] b_part;wire [4:0] sum_part;// 实例化add4模块,并将连接输入和输出add4 add4_1 (.a(a[3:0]), .b(b[3:0]), .sum(sum_part[3:0]));add4 add4_2 (.a(a[7:4]), .b(b[7:4]), .sum(sum_part[7:4]));// 连接add4模块的输出assign sum = {sum_part[7:4], sum_part[3:0]};endmodule在顶层模块中,我们首先定义了一些中间信号(a_part,b_part和sum_part),它们用于连接不同的add4模块。

然后,我们实例化了两个add4模块(add4_1和add4_2),并将它们的输入和输出连接起来。

最后,我们通过连接sum_part的高4位和低4位,得到了最终的8位和。

verilog代码乘法除法编写

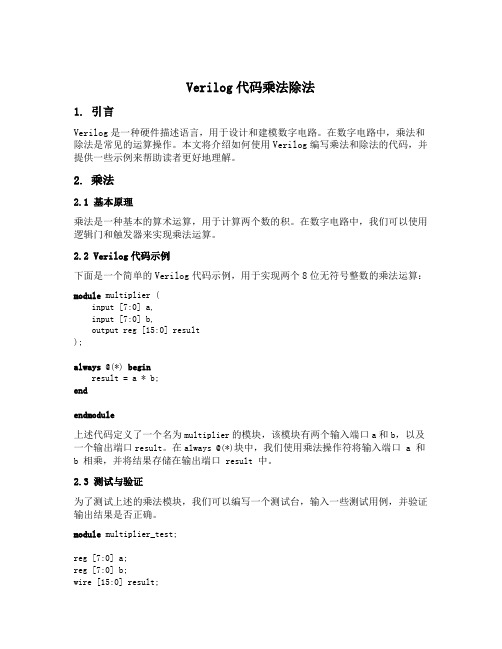

Verilog代码乘法除法1. 引言Verilog是一种硬件描述语言,用于设计和建模数字电路。

在数字电路中,乘法和除法是常见的运算操作。

本文将介绍如何使用Verilog编写乘法和除法的代码,并提供一些示例来帮助读者更好地理解。

2. 乘法2.1 基本原理乘法是一种基本的算术运算,用于计算两个数的积。

在数字电路中,我们可以使用逻辑门和触发器来实现乘法运算。

2.2 Verilog代码示例下面是一个简单的Verilog代码示例,用于实现两个8位无符号整数的乘法运算:module multiplier (input [7:0] a,input [7:0] b,output reg [15:0] result);always @(*) beginresult = a * b;endendmodule上述代码定义了一个名为multiplier的模块,该模块有两个输入端口a和b,以及一个输出端口result。

在always @(*)块中,我们使用乘法操作符将输入端口a和b相乘,并将结果存储在输出端口result中。

2.3 测试与验证为了测试上述的乘法模块,我们可以编写一个测试台,输入一些测试用例,并验证输出结果是否正确。

module multiplier_test;reg [7:0] a;reg [7:0] b;wire [15:0] result;multiplier dut(.a(a),.b(b),.result(result));initial begin// Test case 1: a = 5, b = 3a = 5;b = 3;#10; // Wait for 10 time unitsif (result !== 15)$display("Test case 1 failed");// Test case 2: a = 10, b = 0a = 10;b = 0;#10; // Wait for 10 time unitsif (result !== 0)$display("Test case 2 failed");// Add more test cases here...endendmodule上述代码定义了一个名为multiplier_test的测试台模块。

verilog参数

在Verilog中,参数(parameter)是一种常量定义,用于在设计中声明和设置常量值。

参数可以用于定义模块的尺寸、延迟、地址范围等常量。

在Verilog中声明参数的语法如下:verilogCopy codeparameter <data_type> <parameter_name> = <value>;其中:<data_type>:参数的数据类型,可以是整型(integer)、实数型(real)、布尔型(boolean)等。

<parameter_name>:参数的名称,自定义的标识符。

<value>:参数的初始值,可以是一个常数或表达式。

以下是一些使用Verilog参数的示例:verilogCopy codeparameter WIDTH = 8; // 定义一个宽度参数,值为8parameter ADDR_BITS = 12; // 定义一个地址位数参数,值为12 parameter DELAY = 10; // 定义一个延迟参数,值为10parameter ENABLE = 1'b1; // 定义一个使能参数,值为1(布尔类型)parameter PI = 3.14159; // 定义一个圆周率参数,值为3.14159(实数类型)parameter MASK = 8'hFF; // 定义一个掩码参数,值为16进制的FFmodule ExampleModule #(parameter WIDTH = 4);// 使用参数定义模块的宽度reg [WIDTH-1:0] data;// ...endmodule通过使用参数,可以在设计中灵活地配置常量值,提高设计的可重用性和灵活性。

可综合的verilog语句

可综合的verilog语句(原创版)目录1.Verilog 语言概述2.Verilog 语句的分类3.可综合的 Verilog 语句4.应用举例正文1.Verilog 语言概述Verilog 是一种硬件描述语言,主要用于数字系统硬件的描述、模拟和验证。

它最初由 Phil Moorby 在 1983 年开发,后来由 Cadence 公司进行商业化推广。

Verilog 具有易学易用、功能强大的特点,广泛应用于集成电路设计、计算机体系结构、数字信号处理等领域。

2.Verilog 语句的分类Verilog 语句主要分为两大类:行为描述语句(Behavioral Description)和结构描述语句(Structure Description)。

行为描述语句主要用于描述数字电路的功能和行为,包括 always 语句、initial 语句等;结构描述语句主要用于描述数字电路的物理结构,包括 module 语句、wire 语句等。

3.可综合的 Verilog 语句可综合的 Verilog 语句是指在数字集成电路设计中,可以被合成器(Synthesizer)转换为实际硬件电路的 Verilog 语句。

这类语句主要包括以下几类:(1)简单的逻辑门和寄存器:如与门、或门、非门、与非门、或非门、异或门等,以及触发器、计数器、寄存器等。

(2)各种运算和操作:如算术运算(加、减、乘、除等)、关系运算(大于、小于、等于、不等于等)、位运算(按位与、按位或、按位异或、取反等)、移位运算等。

(3)控制结构:如 if-else 语句、case 语句、for 循环、while 循环等。

(4)其他:如声明、实例化、端口定义、模块调用等。

4.应用举例以下是一个可综合的 Verilog 语句示例,用于实现一个 4 位全加器的功能:```verilogmodule full_adder(input a, input b, input cin, output sum, output cout);assign sum = a ^ b ^ cin; // 异或运算实现和assign cout = (a & b) | (a & cin) | (b & cin); // 与、或运算实现进位endmodule```在这个例子中,我们声明了一个名为 full_adder 的模块,包含两个输入端口 a、b,一个输入端口 cin,以及两个输出端口 sum 和 cout。

verilog 类 实例

verilog 类实例Verilog类是一种硬件描述语言,用于描述和设计数字电路。

它是一种基于事件驱动的语言,主要用于描述电子系统中的逻辑电路和时序电路。

本文将介绍Verilog类的基本概念和用法,以及如何使用Verilog类来实现数字电路设计。

我们来了解一下Verilog类的基本结构。

Verilog类由模块(module)、端口(port)、信号(signal)和过程块(always block)组成。

模块是Verilog类的最基本单位,用于封装和组织电路的功能。

端口是模块与外部环境之间的接口,用于输入和输出数据。

信号是数字电路中的数据流,用于表示电路内部的状态和数据。

过程块是Verilog类中的关键部分,用于描述电路的行为和逻辑。

在Verilog类中,我们可以使用各种语句和运算符来实现电路的功能。

例如,我们可以使用赋值语句(assign)来给信号赋值,使用条件语句(if-else)来实现逻辑判断,使用循环语句(for、while)来实现重复操作。

此外,Verilog类还支持多种逻辑运算符和算术运算符,如与(and)、或(or)、非(not)、加(add)、减(subtract)等。

Verilog类的一个重要应用是设计和实现各种数字逻辑电路,例如加法器、乘法器、寄存器、计数器等。

下面以一个简单的全加器为例来说明Verilog类的使用。

全加器是一种常用的组合逻辑电路,用于实现两个二进制数的相加操作。

它由两个半加器和一个或门组成。

每个半加器用于计算两个输入位的和(Sum)和进位(Carry),而或门用于将两个半加器的进位相加得到最终的进位。

以下是一个使用Verilog类实现的全加器的代码示例:```module FullAdder(input A, input B, input Cin, output Sum, output Cout);wire S1, C1, C2;HalfAdder HA1(.A(A), .B(B), .Sum(S1), .Carry(C1));HalfAdder HA2(.A(S1), .B(Cin), .Sum(Sum), .Carry(C2));or Gate(.A(C1), .B(C2), .Y(Cout));endmodulemodule HalfAdder(input A, input B, output Sum, output Carry);assign {Carry, Sum} = A + B;endmodule```在上述代码中,FullAdder模块是一个顶层模块,它实例化了两个HalfAdder模块和一个或门。

Verilog语言实现5分频电路的设计

Verilog语言实现5分频电路的设计1.行为建模方法:使用行为建模方法,可以通过描述电路的功能行为来实现5分频电路。

以下是使用Verilog语言进行行为建模的代码示例:```verilogmodule DivideBy5input wire clk,output wire clk_outreg [2:0] counter;counter <= 0;clk_out <= ~clk_out;end else begincounter <= counter + 1;endendendmodule```在该示例中,定义了一个模块`DivideBy5`,包含一个输入端口`clk`和一个输出端口`clk_out`,分别用于输入时钟信号和输出分频后的时钟信号。

`reg [2:0] counter`是一个3位的寄存器,用于计数。

当计数达到5时,即计数器的值为5,会将`counter`复位为0,并将输出时钟信号`clk_out`取反。

否则,计数器的值会自增12.结构建模方法:使用结构建模方法,可以通过组合和顺序电路的连接方式来实现5分频电路。

以下是使用Verilog语言进行结构建模的代码示例:```verilogmodule DivideBy5input wire clk,output wire clk_outwire clk_out_2;wire clk_out_3;wire clk_out_4;DivideBy2 div_by_2 ( .clk(clk), .clk_out(clk_out_2) );DivideBy2 div_by_3 ( .clk(clk_out_2), .clk_out(clk_out_3) );DivideBy2 div_by_4 ( .clk(clk_out_3), .clk_out(clk_out_4) );DivideBy2 div_by_5 ( .clk(clk_out_4), .clk_out(clk_out) );endmodulemodule DivideBy2input wire clk,output wire clk_outreg clk_out;clk_out <= ~clk_out;endendmodule```在该示例中,定义了两个模块`DivideBy5`和`DivideBy2`。

verilog 原语例化语法

verilog 原语例化语法Verilog是一种硬件描述语言,可以用来描述和设计数字集成电路。

Verilog原语是一组内置的底层硬件建模功能,用于描述和建模集成电路中的基本单元。

文本中将深入探讨Verilog原语例化语法。

1、例化指令的基础语法在Verilog中,使用“module”指定一个硬件模块,然后使用“endmodule”关闭该模块。

Verilog实例化使用“module” 关键字来引用硬件模块。

例化语法:module module_name (port_list);... module body ...endmodule这里,模块名称表示实例化模块的名称,接下来是端口列表,是模块是否双向、数据类型等信息,接着是模块主体。

2、例化语法示例下面是一个简单的 Verilog 原语例化示例,使用了常见的内置原语之一 AND。

module example AND_INST (output reg y, input a, b);and and_inst(y, a, b);endmodule上述例化将输入端口a和b连接到与门原语,将结果存储在输出端口y中。

3、实例化复合模块通过例化,可以将单个硬件原语连接到模块中。

模块可以嵌套,这意味着模块自身可以包含其他模块。

在这种情况下,我们需要进行复杂例化,以适应其包含的模块。

在下面的示例中,我们将实例化两个硬件模块,并将它们连接在一起,以便每个模块都处理一部分数据。

其中第一个模块处理第一位和第二位,第二个模块处理第三位和第四位。

module example(input [0:3] data_in, output [0:3]data_out);wire [1:0] a;wire [1:0] b;wire [1:0] c;wire [1:0] d;module1 m1(a, b, data_in[0], data_in[1]);module2 m2(c, d, data_in[2], data_in[3]);endmodule在上面的示例中,我们使用了 comma ',' 分隔符来分别为每个模块声明输出端口,以便在主模块中使用。

verilog条件赋值语句

verilog条件赋值语句Verilog是一种硬件描述语言,用于设计和描述数字电路。

条件赋值语句是Verilog中常用的语句之一,用于根据给定的条件对变量进行赋值。

下面是以Verilog条件赋值语句为题的非重复内容示例:1. 三目运算符三目运算符是一种常用的条件赋值语句,它可以根据条件的真假来选择不同的赋值。

例如:```verilogassign result = (a > b) ? a : b;```上述语句的意思是,如果a大于b,则result等于a,否则result 等于b。

2. case语句case语句是一种多分支的条件赋值语句,它根据给定的表达式值选择不同的赋值。

例如:```verilogreg [1:0] sel;reg [7:0] result;always @(sel)begincase (sel)2'b00: result = 8'b00000000;2'b01: result = 8'b11111111;2'b10: result = 8'b01010101;2'b11: result = 8'b10101010;endcaseend```上述语句的意思是,根据sel的值选择不同的赋值给result。

3. if语句if语句是一种常见的条件赋值语句,它根据给定的条件选择是否进行赋值。

例如:```verilogreg [7:0] a, b, result;always @(a, b)beginif (a > b)result = a;elseresult = b;end```上述语句的意思是,如果a大于b,则将a赋值给result,否则将b赋值给result。

4. for循环for循环也可以用于条件赋值,它可以根据给定的条件重复执行赋值操作。

例如:```verilogreg [7:0] result;always @(posedge clk)beginfor (i = 0; i < 8; i = i + 1)result[i] = data[i];end```上述语句的意思是,每当时钟上升沿到来时,将data的每个位赋值给result。

verilog for语句

verilog for语句Verilog的for语句用于循环执行一段代码指定的次数。

for语句的语法如下:```for (循环变量初始化; 循环条件; 循环变量更新) begin// 代码块end```其中:- 循环变量初始化:在进入循环前执行一次的初始化表达式。

- 循环条件:在每次迭代前都会被检查的表达式。

只要条件为真,代码块内的语句就会被执行。

- 循环变量更新:在每次迭代结束后更新循环变量的表达式。

以下是一个用Verilog的for语句实现简单计数的示例:```reg [7:0] count;always @(posedge clk) begincount <= 8'd0; // 初始化计数变量for (count=8'd0; count<8'd10; count=count+1) begin$display("Count: %d", count); // 打印当前计数值endend```本示例中,每当时钟上升沿到来时,计数变量`count`会被初始化为0,并自增1。

在循环内部,会打印当前的计数值。

循环会执行10次(0到9),并在控制台上打印计数值。

需要注意的是,Verilog的for循环在硬件描述语言中的行为与传统编程语言中的for循环不同。

在Verilog中,for循环是硬件描述的一种方式,不会显式地生成循环结构。

取而代之的是,每次循环中的代码会被展开并并行执行,类似于插入多个连续的语句。

因此,在使用Verilog的for循环时,需要确保生成的硬件电路表现与预期一致。

verilog { a, b};语句

verilog { a, b};语句verilog中的 {a, b} 语句是用来将两个信号 a 和 b 连接在一起形成一个新的信号的。

在这个新的信号中,首先会包含信号 a 的所有位,然后再包含信号 b 的所有位。

下面是关于 {a, b} 语句的一些用途和示例:1. 连接两个信号:假设信号 a 是一个 4 位的信号,信号 b 是一个 8 位的信号,使用 {a, b} 语句将它们连接在一起,得到一个 12 位的新信号。

2. 扩展信号的位数:假设信号 a 是一个 8 位的信号,信号 b 是一个 4 位的信号,使用 {a, b} 语句将它们连接在一起,得到一个 12 位的新信号。

新信号的前 8 位是信号 a 的位,后 4 位是信号 b 的位。

3. 信号分割:假设信号 a 是一个 8 位的信号,信号 b 是一个 4 位的信号,使用 {a[7:4], b} 语句将它们连接在一起,得到一个 8 位的新信号。

新信号的前 4 位是信号 a 的高 4 位,后 4 位是信号 b 的位。

4. 信号重排:假设信号 a 是一个 8 位的信号,信号 b 是一个 4 位的信号,使用 {a[7:4], a[3:0], b} 语句将它们连接在一起,得到一个 16 位的新信号。

新信号的前 4 位是信号 a 的高 4 位,接着是信号 a的低 4 位,最后是信号 b 的位。

5. 信号连接与扩展:假设信号 a 是一个 4 位的信号,信号 b 是一个 8 位的信号,使用 {a, b[7:4]} 语句将它们连接在一起,得到一个 12 位的新信号。

新信号的前 4 位是信号 a 的位,后 8 位是信号 b 的高 4 位。

6. 信号连接与重复:假设信号 a 是一个 4 位的信号,信号 b 是一个 2 位的信号,使用 {a, b, a, b} 语句将它们连接在一起,得到一个 12 位的新信号。

新信号的前 4 位是信号 a 的位,接着是信号 b 的位,再接着是信号 a 的位,最后是信号 b 的位。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

endcase

endmodule

设计示例四 (续)

还可以用另一个Verilog HDL模型来表示同一个有限状态,见 下例: module fsm (Clock, Reset, A, F, G);

input Clock, Reset, A; output F,G; reg F,G; reg [3:0] state ; parameter Idle Start Stop Clear = = = = 4’b1000, 4’b0100, 4’b0010, 4’b0001;

case (state) idle: begin if (A)

state <= Start; G<=0;

start: Stop:

Clear:

end if (!A) state <= Stop; begin if (A) state <= Clear; F <= 1; end begin if (!A) state <=Idle; F<=0; G<=1; end

parameter

Idle Stop

= 2’b00, = 2’b10,

Start = 2’b01, Clear = 2’b11;

always @(posedge Clock) if (!Reset) begin state <= Idle; F<=0; G<=0; end else

设计示例四 (续)

设计示例三 (续)

/*------------------------------------------------宏定义stim引用,等同于 #100 data=4'b 注意引用时要 用 `符号。--------------------------------------*/ `stim 0000; `stim 0001; . . . . . . `stim 1111; end #200 -> end_first_pass; /*------------------------------------------------延迟200个单位时间,触发事件end_first_pass -------------------------------------------------*/ $finish; //结束仿真 end endmodule

设计示例四 (续)

always @(posedge Clock) if (!Reset) begin state <= Idle; end else case (state) Idle: if (A) Start: if (!A) Stop: if (A) Clear: if (!A) default: state <= endcase

state <= state <= state <= state <= 2 ’bxx;

Start; Stop; Clear; Idle;

设计示例四 (续)

always @(state or Reset or A) begin if ( !Reset) F = 0; else if (state == Stop) F = 1; end

设计示例一

• 用门级结构描述D触发器:

设计示例一 module input output nand #10 flop(data,clock,clear,q,qb); data,clock,clear; q,qb; nd1(a,data,clock,clear), nd2(b,ndata,clock), nd4(d,c,b,clear), nd5(e,c,nclock), nd6(f,d,nclock), nd8(qb,q,f,clear); nd3(c,a,d), nd7(q,e,qb); iv1(ndata,data), iv2(nclock,clock);

设计示例三 (续)

hardreg reg_4bit(.d(data),.clk(clock), .clrb(clearb), .q(qout)); /*--------------------------------------------------把本模块中产生的测试信号data、clock、clearb输入实例 reg_4bit以观察输出信号qout.实例reg_4bit引用了hardreg ---------------------------------------------------*/ initial begin clock = 0; clearb = 1; end always #50 clock = ~clock;

Verilog HDL 设计示例四

• 有限状态机的设计

- 有限状态机是由寄存器组和组合逻辑构成的 硬件时序电路; - 其状态(即由寄存器组的1和0的组合状态所 构成的有限个状态)只能在同一时钟跳变沿 的 情况下才能从一个状态转向另一个状态; - 究竟转向哪一状态不但取决于各个输入值, 还取决于当前状态。 - 状态机可用于产生在时钟跳变沿时刻开关的 复杂的控制逻辑,是数字逻辑的控制核心。

设计示例三

• 编写测试模块通过仿真检查设计正确与否:

`include “hardreg.v” module hardreg_top; reg clock, clearb; reg [3:0] data; wire [3:0] qout; `define stim #100 data=4'b //宏定义 stim,可使源程序简洁 event end_first_pass; //定义事件end_first_pass

设计示例四 (续)

F <= 1; end

Clear: begin if (!A) state <=Idle; F<=0; G<=1;

end default: state <=Idle; endcase endmodule

设计示例四 (续)

我们还可以用另一种风格的Verilog HDL模型来表示同一个有 限状态。在这个模型中,我们把用always语句在时钟沿触发 条件下的状态变化放在一个独立的块中, 而把在状态控制下 的两个开关分两个独立的组合逻辑always块来描述。见下例 :

设计示例四 (续)

A/G=0 !Reset/F=0 G=0 !Reset /F=0 G=0

Start

!A

Idle

!Reset /F=0 G=0

Stop

!Reset | !A/F=0 G=1

Clear

A/F=1

设计示例四 (续)

module fsm (Clock, Reset, A, input Clock, Reset, A; output F,G; reg F,G; reg [1:0] state ; F, G);

module fsm (Clock, Reset, A, input Clock, Reset, A; output F,G; reg [1:0] state ; reg F,G;

parameter Idle = 2’b00, Stop = 2’b10,

F, G);

Start = 2’b01, Clear = 2’b11;

nand #9 not #10

endmodule

设计示例二

• 由已设计的模块来构成高一级的模块

q3 q2 q1 q0

d

q

d

f4

clk clr

f3

clk clrຫໍສະໝຸດ qdf2clk clr

q

d

f1

clk clr

q

clrb

clk

d3

d2

d1

d0

四位寄存器电路结构图

设计示例二

`include “ flop.v ” module hardreg(d,clk,clrb,q); input clk,clrb; input[3:0] d; output[3:0] q; flop f1(d[0],clk,clrb,q[0],), f2(d[1],clk,clrb,q[1],), f3(d[2],clk,clrb,q[2],), f4(d[3],clk,clrb,q[3],); endmodule

always @(state or Reset or A) begin if (! Reset) G = 0; else if (state == Clear) G = 1; end

endmodule

设计示例四 (续)

always @(posedge clock) if (!Reset) begin state <= Idle; F<=0; G<=0; end else case (state) Idle: begin if (A) state <= Start; G<=0; end Start: if (!A) state <= Stop; Stop: begin if (A) state <= Clear;