四路竞赛抢答器设计

四路抢答器电路组成及工作原理(含电路图)

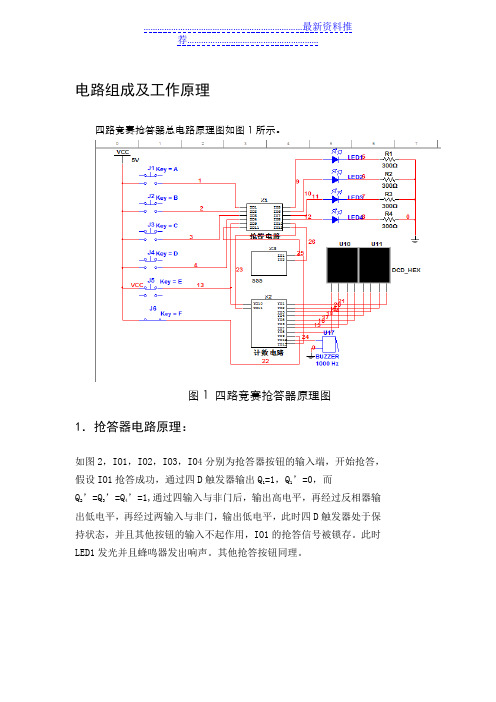

电路组成及工作原理四路竞赛抢答器总电路原理图如图1所示。

图1 四路竞赛抢答器原理图1.抢答器电路原理:如图2,IO1,IO2,IO3,IO4分别为抢答器按钮的输入端,开始抢答,假设IO1抢答成功,通过四D触发器输出Q1=1,Q1’=0,而Q 2’=Q3’=Q4’=1,通过四输入与非门后,输出高电平,再经过反相器输出低电平,再经过两输入与非门,输出低电平,此时四D触发器处于保持状态,并且其他按钮的输入不起作用,IO1的抢答信号被锁存。

此时LED1发光并且蜂鸣器发出响声。

其他抢答按钮同理。

图2 抢答器部分电路图2.计时电路原理:计时电路为两片74LS160用置数法构成的31进制计数器,因为可以为了让答题者直观的看到30S这个时间点,所以设置了31进制的计数器。

两片的四个输入端均接低电平,两片的输出端分别接七段译码管直接显示数字,高位的74LS160芯片的Q1Q2接到一个二输入的与非门(U8A)输出到计数器的LD端、三输入与非门端、反相器端。

输出到LD端是为了构成31进制计数器,当高位变为3时,计数器置0。

输出到三输入与非门(U9A)和时钟脉冲、开关的电平信号一起输入到与非门中,这就是为什么能控制计时的开始与暂停了,当开关输入低电平时,无论是否有时钟信号,时钟均不发生改变,此时时钟信号为无效信号;而当开关输入高电平时,U8A输出也为高,因此,时钟信号为有效信号,因此,凭借这样的类似锁存的电路,就可以控制计时的开始与暂停。

而当时间到了30s时,U8A输出为低电平,时钟信号又成为无效信号,时间被停止在30s,此时将U8A信号通过一个反相器输出到蜂鸣器,蜂鸣器发出响声。

图3 计时器电路3.555函数发生器:输出高电平时间:T1=(R1+R2)Cln2 输出低电平时间:T2=R2Cln2 振荡周期:T=(R1+2R2)Cln2图4 555函数发生器。

四路智力竞赛抢答器课程设计

2016届课程设计《四路智力竞赛抢答器》课程设计说明书学生姓名学号所属学院信息工程学院专业计算机科学与技术班级计算机16-6班指导教师教师职称讲师塔里木大学教务处制塔里木大学课程设计任务书课程名称:四路智力竞赛抢答器目录摘要: (1)1.设计目的和要求 (2)1.1设计要求 (2)1.2设计目的 (2)2.功能介绍 (3)3.总体方案设计 (3)4.具体电路设计 (4)4.1 主电路设计 (4)5.设计原理 (5)6.四路抢答器元器件清单 (6)7.主要器件介绍 (6)7.1 74ls175 四d触发器 (6)7.2 74LS20 与非门87.3 74LS00 二输入与非门 (10)7.4 555的工作原理 (12)8.四人抢答器仿真 (15)9.实验步骤及操作 179.1 检测与查阅器件 199.2 连接电路 (19)9.3 电路调试 (19)10.实物图如下 (19)11.实验困难问题及解决措施 (20)11.1困难一 (20)11.2困难二 (21)11.3困难三 (21)11.4困难四 (21)11.5 困难五 2212.设计成品的优点与不足 (21)12.1优点 (21)12.2不足 (21)12.3改良 (22)总结 24致谢 (24)参考文献 (25)塔里木大学课程设计评审意见表 28课程设计验收鉴定表 29塔里木大学教学实习日志 30塔里木大学数字电路课程设计说明书四路智力竞赛抢答器摘要:在日常生活中各种竞赛场合经常要用到抢答器,在电视台和娱乐场所等大型场合中的智力抢答更是不可缺的系统,其利用的是大型显示屏显示数字。

抢答器不但在以上场合取到很大的作用,而且在现代制造业中也有很重要的作用。

现代电子技术的飞跃发展,各类智能化产品相应而出,抢答器器也不例外;数字电路具有电路简单、可靠性高、成本低等优点,本设计就以数字电路为核心设计四路抢答器。

而本次课程设计技术目标与要求是设计四路的抢答器,附有简单的抢答功能,不仅可以用于比赛,娱乐抢答,知识竞赛等活动,也可以用于各类需要竞争的场合,抢答器的运用非常附有人性化,应用非常广泛。

最新四路智力竞赛抢答器设计

…………………………………………………………最新精品资料推荐……………………………………………………重庆信息技术职业学院毕业设计题目四路智力竞赛抢答器设计选题性质: 设计□报告□其他院系电子工程学院专业电子信息工程技术班级 10 级(2)班学号 1025090234学生姓名王楷指导教师王芳莉教务处制2012年 9 月 1 日..................................................................最新精品资料推荐 (I)…………………………………………………………最新精品资料推荐……………………………………………………2013 届电子工程学院毕业设计选题审批单年级 10 专业电子班级 2班..................................................................最新精品资料推荐 (II)…………………………………………………………最新精品资料推荐……………………………………………………2013 届电子工程学院毕业设计开题报告及进度要求..................................................................最新精品资料推荐 (III)…………………………………………………………最新精品资料推荐……………………………………………………..................................................................最新精品资料推荐 (IV)…………………………………………………………最新精品资料推荐……………………………………………………目录目录 (I)摘要 (II)绪论 (1)第1章方案与论证 (2)1.1设计要求 (2)1.2方案论证 (2)第2章单元电路设计 (4)2.1抢答器按键保持与封锁电路 (4)2.2 选手号码显示电路 (6)2.2.1 74LS148优先编码器 (6)2.2.2 74LS248七段译码器 (8)2.3 脉冲发生器电路 (10)2.3.1 555定时器 (10)2.4 8421BCD码递减计数器电路 (12)2.4.1 十进制可逆计数器74LS192 (12)2.5 抢答及限时鸣响电路 (14)2.5.1 74LS04非门 (14)2.5.2 74LS02与非门 (15)总结 (17)参考文献 (18)附录Ⅰ总电路图 (19)附录Ⅱ元器件清单 (20)..................................................................最新精品资料推荐 (I)…………………………………………………………最新精品资料推荐……………………………………………………摘要本文设计可供四人抢答的抢答器电路并对其进行仿真。

四路智力竞赛抢答器设计.

吉林建筑大学电气与电子信息工程学院数字电子技术课程设计报告设计题目:四路竞赛抢答电路专业班级:信工131班学生姓名:学号:指导老师:设计时间:前言关于这次设计的用于多人竞赛抢答的器件,在现实生活中很常见,尤其是在随着各种智益电视节目的不断发展,越来越多的竞赛抢答器被用在了其中,这种抢答器的好处是不仅能够锻炼参赛选手的反应能力,而且能增加节目现场的紧张、活跃气氛,让观众看得更有情趣。

可见抢答器在现实生活中确实很实用,运用前景非抢答器的设计与制作智力竞赛是一种生动活泼的教育形式和方法,通过抢答和必答两种方式能引起参赛者和观众的极大兴趣,并且能在极短时间内,使人们增加一些科学知识和生活常识。

常广泛。

在知识竞赛中,特别是做抢答题时,在抢答过程中,为了知道哪一组或哪一位选手先答题,必须要有一个系统来完成这个任务。

如果在抢答中,只靠人的视觉是很难判断出哪组先答题。

这次设计就是用几个触发器以及三极管巧妙的设计抢答器,使以上问题得以解决,即使两组的抢答时间相差几微秒,也可分辨出哪组优先答题。

本文主要介绍了抢答器的工作原理及设计,以及它的实际用途。

目录前言 (4)一 . 课程设计目的 (5)二 . 课程设计题目与内容 (5)三 . 系统设计方案 (7)四 . 电路工作原理 (8)五 . 单元电路设计参数计算及元器件选择 (11)六 . 完整电路图 (16)七 .需要的元器件清单: (17)八 . 总结与体会 (18)九 . 参考文献 (20)一、课程设计目的:数字电子技术课程设计是数字电子技术课程的实践性教学环节,是对学生学习数字电子技术的综合性训练,这种训练是通过学生独立进行某一课题的设计、安装和调试来完成的,训练学生综合运用学过的数字电子技术的基本知识,独立设计比较复杂的数字电路的能力。

通过数字电路课程设计使学生做到:1、综合运用电子设计课程中所学到的理论知识,独立完成一个设计课题。

2、通过查阅手册和文献资料,培养学生独立分析和解决实际问题的能力。

VHDL四路抢答器的设计

VHDL四路抢答器的设计设计要求:1.抢答器同时供N名选手,(此处假设4个)分别用4个按钮S0~ S3表示。

2.设置一个系统“开始复位”开关S,该开关由主持人控制(当主持人按下该开关后以前的状态复位并且开始计时抢答)。

3.抢答器具有锁存与显示功能。

即选手按动按钮,锁存相应的编号,并在LED数码管上显示,同时扬声器发出报警声响提示。

选手抢答实行优先锁存,优先抢答选手的编号一直保持到主持人将系统清除为止。

4. 抢答器具有定时抢答功能,且一次抢答的时间(0-99S)。

当主持人启动“开始复位”键后,定时器进行减计时。

5. 如果定时时间已到,无人抢答,本次抢答无效,系统报警并禁止抢答,定时显示器上显示00。

一、概述抢答器的逻辑结构主要由抢答鉴别lock模块、定时模块、译码模块和报警器模块组成。

在整个抢答器中最关键的是如何实现抢答封锁,在控制键按下的同时计数器倒计时显示有效剩余时间。

除此之外,整个抢答器还需有一个“复位开始”信号,以便抢答器能实现清零和开始。

抢答器共有3个输出显示,选手代号、计数器的个位和十位,他们输出全都为BCD码输出,这样便于和显示译码器连接。

当主持人按下控制键、选手按下抢答键蜂鸣器短暂响起。

•方案设计与论证嘿嘿!将该任务分成N个模块进行设计,分别为:抢答器鉴别模块、抢答器计时模块、译码模块、报警模块,最后是综合。

1. 抢答器鉴别模块:在这个模块中主要实现抢答过程中的抢答功能,并且能实现当有一路抢答按键按下时,该路抢答信号将其余个绿抢答封锁的功能。

在这个模块输入端有WARN输入(以时间控制系统的WARN输出信号为信号源)、一个和“时间控制系统”公用的CLEAR端、4人抢答输入信号端S0,S1,S2,S3和有一个时钟信号端CLK,这个时钟信号是个高频信号,用以扫描S0,S1,S2,S3是否有信号输入。

输出端有对应于S0,S1,S2,S3编号的4个指示灯LED 和4线2进制输出端STATES(用于锁存当前的状态),还有一个STOP 端用于指示S0,S1,S2,S3按钮状态(控制计时器停止)。

4路抢答器课程设计报告

4路抢答器课程设计报告课程设计报告:4路抢答器一、设计背景和目标抢答器是一种常见的教学装置,用于增强学生参与课堂互动和竞争的积极性。

为了提高现有抢答器的性能和功能,本次设计决定设计一款4路抢答器,以满足现代教育教学的需求。

本设计旨在通过增加抢答器的路数,提高课堂互动和竞争的效果,促进学生参与讨论和思考,培养学生的团队合作和竞争精神。

二、需求分析1.提高路数:既有的抢答器系统只能支持单一路数,不利于多个学生同时参与抢答活动,因此设计4路抢答器,以支持更多学生参与抢答。

2.精准识别:抢答器需要准确识别学生按下按钮的时间顺序,并显示该学生抢答的排名,以减少争议和纠纷。

3.考虑后续扩展:设计的抢答器具备一定的可扩展性,以满足未来可能增加的路数需求。

4.易于使用:抢答器的使用应简单方便,对教师和学生来说操作简单、直观。

三、系统设计1.硬件部分:抢答器由中控主机和多个答题器组成。

中控主机负责控制答题器的启动、暂停和排名显示,答题器则用于学生参与抢答。

中控主机需要具备多路输入和输出接口,以支持多个答题器的同时工作。

2.软件部分:中控主机需要具备按键扫描、计时、显示学生抢答排名等功能。

答题器则需要具备按键输入和与中控主机的通信功能。

四、应用场景本款4路抢答器适用于中小学课堂教学。

教师可以通过抢答器让学生在课堂上积极回答问题,增强学生对知识点的理解和记忆。

在团队竞赛中,抢答器也可以作为评分工具,用于记录团队的答题水平。

五、教学效果和可操作性评价1.教学效果:抢答器可以增强学生的参与度和互动性,培养学生的团队合作和竞争精神,促进学生思考和讨论,提高教学效果。

2.可操作性评价:抢答器的设计考虑到了简单方便的操作,教师和学生只需按下按钮即可完成相应操作,无需复杂的设置和操作过程,易于上手和使用。

六、结论本次设计的4路抢答器满足了现代教育教学的需求,提高了学生参与度和互动性。

通过抢答竞赛,可以培养学生的竞争意识和思考能力。

SOPC四路抢答器设计

本科实验报告题目:四路抢答器设计课程名称:SOPC设计与实践学院(系):信息与通信工程学院专业:电子信息工程班级:学号:学生姓名:成绩:2011 年 5 月14 日题目:四路抢答器设计1 设计要求在娱乐、竞赛类节目中,很多都需要用到抢答器,用来判断是谁第一个抢到答题机会。

本设计是四路抢答器,就是可以四个人一块抢答,并且将抢答结果通过LED、数码管、LCD来进行显示。

即某一个人按下他对应的按钮后,他身前的LED亮,数码管上显示他对应的号码,LCD显示是第几号选手获得了抢答的机会。

并且本设计设有总控制开关,用来控制何时开始抢答。

2 设计分析及系统方案设计对于总开关的设计,我采用的是在判断按键操作之前增加一个if语句,如果总开关开启,按键操作才被响应,如果总开关没有开启,按键操作都不被响应。

对于按键的判断,我采用的按键中断来实现的,某个按键按下后,中断响应,如果总开关开启,则根据键值进行响应的按键响应,即将对应的LED点亮,数码管上显示需要显示的数字,LCD显示第几位选手抢答成功。

为了防止第一位选手抢答后,第二位选手将第一位选手的抢答冲掉,考虑到实际应用,我采用的是在第一位选手按键操作响应后就进行一定时间的延时,从而保证在延时的这段时间,其他的选手不能将第一位选手的按键响应冲掉。

3 各功能模块硬件电路设计(1)总体电路图在此系统图中,包含CPU及外围LED、数码管、LCD的连接及引脚配置。

(2)SOPC builder配置图此SOPC builder中,加入了20K RAM、16K ROM、四位按键(设置下降沿中断)、一位开关、四位LED、一个七段数码管、一片LCD。

4 系统软件设计(1)流程图(2)源代码:#include "system.h"#include "sys/alt_irq.h"#include "altera_avalon_pio_regs.h"#include "alt_types.h"#include "io.h"#include "stdio.h"volatile int edge_capture;unsigned char seg_table[11]={0x40,0x79,0x24,0x30,0x19,0x12,0x02,0x78,0x00,0x10,0x7f};static void handle_key_interrupt(void* context,alt_u32 id){volatile int* edge_capture_ptr=(volatile int*)context;*edge_capture_ptr=IORD(KEY_BASE,3);IOWR(KEY_BASE,3,0);}static void init_key_pio(){void* edge_capture_ptr=(void*)&edge_capture;IOWR(KEY_BASE,2,0xf);IOWR(KEY_BASE,3,0x0);alt_irq_register(KEY_IRQ,edge_capture_ptr,handle_key_interrupt);}int main(void){init_key_pio();char sw;char Text1[15]=" The first one!";char Text2[15]=" The second one";char Text3[15]=" The third one!";char Text4[15]=" The forth one!";char Text5[15]=" Please Wait...";int Initial[5]={0x38,0x0c,0x01,0x06,0x80};for(i=0;i<5;i++){IOWR(LCD_16207_0_BASE,0,Initial[i]);usleep(5000);}while(1){IOWR(LCD_16207_0_BASE,0,0x01);sw=IORD(SW_BASE,0);if(sw==1)switch(edge_capture){case 0x08:{IOWR(LED_BASE,0,0x08);IOWR(SHU_BASE,0,seg_table[1]);for(i=0;i<15;i++){IOWR(LCD_16207_0_BASE,2,Text1[i]);usleep(2000);}usleep(9000000);}break;case 0x04:{IOWR(LED_BASE,0,0x04);IOWR(SHU_BASE,0,seg_table[2]);for(i=0;i<15;i++){IOWR(LCD_16207_0_BASE,2,Text2[i]);usleep(2000);}usleep(9000000);break;case 0x02:{IOWR(LED_BASE,0,0x02);IOWR(SHU_BASE,0,seg_table[3]);for(i=0;i<15;i++){IOWR(LCD_16207_0_BASE,2,Text3[i]);usleep(2000);}usleep(9000000);}break;case 0x01:{IOWR(LED_BASE,0,0x01);IOWR(SHU_BASE,0,seg_table[4]);for(i=0;i<15;i++){IOWR(LCD_16207_0_BASE,2,Text4[i]);usleep(2000);}usleep(9000000);}break;default:{IOWR(LED_BASE,0,0x00);IOWR(SHU_BASE,0,seg_table[10]);}break;}else{edge_capture=0x00;IOWR(LED_BASE,0,0x00);IOWR(SHU_BASE,0,seg_table[10]);for(i=0;i<15;i++){IOWR(LCD_16207_0_BASE,2,Text5[i]);usleep(2000);}usleep(200000);}}}5 系统调试运行结果说明计分析系统运行环境:硬件是Altera公司CycloneII 2C35FPGA DE2开发板,软件是QuartusⅡ6.0和NIOS Ⅱ。

经典四路抢答器课程设计

四路抢答器课程设计设计参考一、数码抢答器1.设计要求(1)8个参赛选手,用0~7号表示,抢答赛中,锁定并显示最先抢答选手号。

(2)报警提醒主持人等功能。

(3)主持人控制电路。

2.课题涵盖的知识点编码器、锁存器、脉冲发生器、译码器、三极管的开关特性应用等知识。

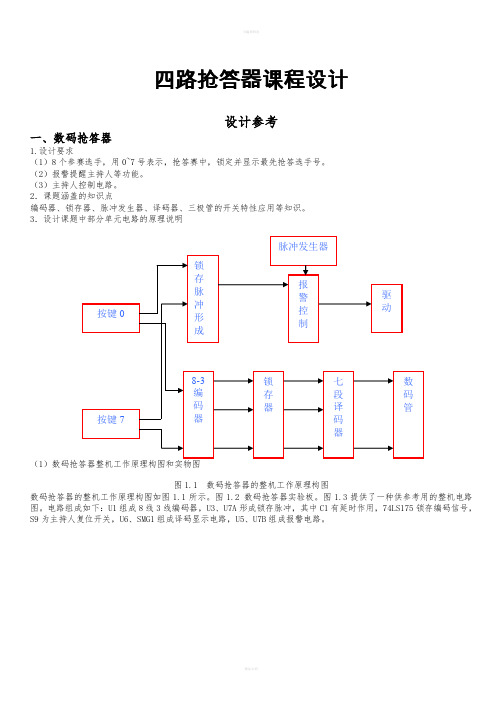

3.设计课题中部分单元电路的原理说明(1图1.1 数码抢答器的整机工作原理构图数码抢答器的整机工作原理构图如图1.1所示。

图1.2 数码抢答器实验板。

图1.3提供了一种供参考用的整机电路图。

电路组成如下:U1组成8线3线编码器,U3、U7A形成锁存脉冲,其中C1有延时作用,74LS175锁存编码信号,S9为主持人复位开关,U6、SMG1组成译码显示电路,U5、U7B组成报警电路。

图1.2 数码抢答器实验板(2)编码器按照预先的约定用文字、数码、图形等字符或图片表示特定对象的过程统称为编码,如学生的学号、考号、邮编等都属于编码,但在数字、微机、单片机等系统中,多利用多位的二进制数码0和1按照某种预先约定的规律排列,组成不同的数码,表示某一具体特定事物或含义,之所以编为二进制码是因为二进制数便于进行存储、运算等各种数字信号处理,而且电路实现简单。

在本项目中为了便于锁存、显示抢答的选手号,可利用二进制编码器将8位选手的按键号编为3信二进制数码。

编码器可以用小规模集成电路设计而成,也可以直接用中规模集成电路如8线-3线编码器74148来实现。

此电路如有74147还可以有10个输入抢答端。

(3)译码显示器本项目可采用七段数码显示译码器。

其作用是将8421BCD码译码后通过数码管显示出来,译码是编码的逆过程。

数码管是由发光二极管显示字段的显示器件,在数字电路和单片机中广泛采用的是七段数码管,这种数码管的显示字段各对应一个发光二极管,根据发光二极管在数码管内部的连接形状不同分为共阴极和共阳极两种。

可编辑修改图1.3 供参考用的整机电路图精品文档驱动共阴数码管的显示译码器可采用MC14511,其功能表如表1.1。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

四路竞赛抢答器设计与仿真。

一、设计题目:四路竞赛抢答设计与仿真二、设计要求设计并仿真能容纳四组参赛队参赛的声光显示抢答器,要求:1)主持人按下复位后,允许开始抢答,2)有人抢答成功,即发出光、声报警信号,并封锁其他参赛队抢答信号的输入主要器件1)74LS175、74LS04;2)发光二极管、蜂鸣器、三极管等。

三、题目分析为达到设计要求可以有两种方案可以选择方案1:采用CD4511芯片作为抢答信号的触发、锁存和译码输出。

这样虽然比较简便,但实际在实现锁存功能时比较繁琐难实现。

方案2:采用集成4D触发器来完成抢答部分。

虽然元件较多,但在实现锁存功能时可以简单的实现。

经过对比两方案的优缺点,决定采用抢答信号锁存简单实现的方案2。

然后利用软件Multisim来进行仿真调试,再进行逐步改进。

智力竞赛是在竞赛中分成几组参加,我设计的为四组,这时针对主持人提出的问题,各组一般进行抢答,对于抢答,需要一种逻辑电路抢答器作为裁判员。

先由主持人控制主电路,各组再进行抢答,优先抢答者抢到并回答问题解除抢答信号后,电路才恢复下一次抢答。

以下是我设计的智力竞赛抢答器的主要设计思路:主持人控制开关接地与四组开关接5V 电压,我集成4D触发器74LS175,起到优先抢答的作用。

利用当其中一组抢答即对应的开关关闭,对应的锁存输入端为高电平,对应的输出端也为高电平,经过与门,实现锁存功能。

这样,当一组抢答时其它组就被屏蔽了。

举个例子来说,若一组得到抢答权,则由于接上电压该组输出高电压,又由于锁存器的锁存原因,其它二组,三组,四组输出的为低电平,与一组相连的发光二极管会发光,同时通过或非门与报警电路相连,使之发出连续响声。

因为由两个或门与译码器连接,译码器是输入高电平有效,而第一组输出高电平时,对应的LED 亮,说明改组拥有回答问题的权利。

当主持人的控制开关复位时,各组的抢答者就开始抢答,当主持人的控制开关清零复位时,开始下一轮抢答。

以上就是我设计的竞赛抢答器的设计思路。

四、总体方案1根据设计要求和题目分析本次设计的四路抢答器总共有2个部分。

第一部分:抢答电路。

:包含(1)四组参赛者用的抢答按钮(2)产生时钟脉冲的电路(3)显示不同灯光的电路(4)主持人使用的清零开关电路。

第二部分:蜂鸣器报警电路。

说明:我们设计的四路竞赛抢答器主要有两部分组成,一部分是抢答电路,二部分是报警电路,第一部分可以实现参赛者的抢答和对其他参赛者信号的封锁作用,还有主持人的清零作用。

第二部分起报警作用。

2原理说明电路中的主要器件是74LS175型四上升沿D触发器,它的清零端和时钟脉冲是四个D触发器公用的。

(1) 按照电路图连接电路。

(2) 抢答前先清零,四个发光二极管LED都不亮扬声器不响。

同时时钟脉冲CP可以经过与门1进入D触发器的CP端。

此时触发器的状态不变。

(3) 抢答开始,若A首先被按下,相应的红光二极管亮;同时扬声器响。

同时,时钟脉冲CP不能进入D触发器。

由于没有时钟脉冲,因此再接着按其他按钮,就不起作用了,触发器的状态不会改变。

(4) 抢答判决完毕,清零,准备下次抢答用。

五、具体实现(1)总体方框图说明:有四组参赛选手A、B、C、D参加竞赛,当主持人用手中的清零开关清零后,宣布四位参赛者开始抢答,一旦A、B、C、D参加竞赛者中的一位首先按下抢答开关后,它所对应的LED变亮,A参赛者对应红色的LED,B对应黄色的LED,C对应绿色的LED,D对应蓝色的LED.在灯亮的同时凤鸣器发出声音说明有参赛者已经抢答。

同时CP时钟脉冲不发出脉冲进入集成4D触发器,其余三位参赛者手中的按钮将不起作用,信号也不再输出,使其他三位参赛者没法抢答。

知道主持人按清零开关并复位宣布下一轮抢答开始为止。

说明(1)A、B、C、D参赛者对应的抢答按钮向下为抢答,在上为没有抢答。

(2)A、B、C、D四位选手对应的LED颜色为红黄绿蓝(3)主持人开关向下为清零,向上为复位,主持人清零复位后四位选手才能开始抢答。

六、各部分定性说明以及定量计算1抢答电路(电路如图2所示)包含(1)四组参赛者用的抢答按钮电路(2)产生时钟脉冲的电路(3)显示不同灯光的电路(4)主持人使用的清零开关电路。

所以该电路有4个功能:一是分辨出选手按键的先后,同时译码显示电路使其对应的LED发亮。

二是要使其他选手随后的按键操作无效。

三是主持人可以对电路清零。

四是由一个CP脉冲产生脉冲电路。

(3)抢答电路图工作原理为:当主持人控制开关处于“清除”时,D触发器的清零端为低电平,使D触发器被强制清零,输入的抢答信号无效。

当主持人将开关拨到“开始”时,D触发器Q非端前一状态为高电平,四个Q非端与在一起为高电平,再和抢答按键信号和借位信号与在一起给D 触发器的脉冲端,当没人抢答时,抢答信号为低电平,与门1输出端为低电平给D触发器脉冲端,当一有人抢答时,抢答信号为高电平,并和U2的输出信号和借位信号与在一起,使得U1输出端为高电平给D触发器,于是D触发器就有一个上升沿,使得抢答信号经D触发器触发锁存再经过译码器74LS175译码,把相应的信号显示在LED上。

另外,当选手按键后,抢答器的锁紧回路发挥作用使CP脉冲停止产生脉冲,从而使得其他选手按键的输入信号不会被接收。

这就保证了抢答者的优先性及抢答电路的准确性。

当选手回答完毕,主持人控制开关S是抢答电路复位,以便进行下一轮抢答。

定量计算:经过对设计要求的分析以及多次的定量计算最后得出选用下列原件能满足设计要求。

(1)非门电路选用74LS04d集成芯片。

(2) 4D触发器选用74LS175D集成4D触发器。

(3)阻值为50欧的电阻。

(4)+5V电压源(5)5V/1KZH的CP时钟脉冲。

2报警电路由非门电路、三极管、电阻和蜂鸣器构成的报警电路,当主持人宣布抢答后当有选手抢答后蜂鸣器发出声响,起报警作用。

(4)报警电路图工作原理:当有抢答者抢答后集成4D触发器发出信号由非门产生一个高频信号1,经过三极管放大该信号使蜂鸣器收到信号,蜂鸣器收到高频信号,并发出一声蜂鸣声,说明有选手按了抢答按钮。

直到下次抢答开始蜂鸣器才能发出蜂鸣声。

定量计算:经过对设计要求的分析以及多次的定量计算最后得出选用下列原件能满足设计要求。

(1)4.7千欧电阻(2)NPN三极管七、实验仿真采用虚拟电子实验室10.0].NI.Multisim.V10.0.1.软件把设计的电路图绘制在软件中,并运行,得到的仿真结果和设计电路的要求一样,当按下清零开关5后红黄绿蓝四个LED都没有亮,蜂鸣器也没有发出声音,清零后恢复。

当A首先按下按钮后红色LED发亮,同时发出蜂鸣声音。

此时B、C、D再按下抢答按钮,黄绿蓝色的LED都不会再亮,直到清零开关清零回复后B、C、D三人第一个按下按钮,它们相对应颜色的LED才会发亮。

同理当按下清零开关又复位后,B或C或者D中的第一个人按下开关所对应的LED 才会亮,并发出蜂鸣声,而其他人随后按下按钮所对应的LED不会发亮也不会发出蜂鸣声。

八、元器件清单九、设计心得体会电子课程设计是本学期最后的一门课程设计,时间安排到接近期末考试前两周,所以时间紧迫任务也十分的艰巨,但不管怎样我们仍然得认真对待,本次设计我选择的是数字智力竞赛抢答器的设计,这个课题用到了数字电路方面的知识,通过这次课程设计,使我对与非门以及集成电路有了一定的了解,对课本上的知识有了近一步的掌握。

完成本次课程设计的过程,是一个从无到有的过程,因为以前没有过类似的课程设计,也没有使用过虚拟电子实验室软件甚至都没有听说过它的存在,所以起初不知该从何下手,后来仔细阅读设计的题目和要求,阅读设计指导书,再到图书馆和网上查找资料,同时对软件的不但熟悉和联系总算是有点眉目了。

慢慢的终于知道了如何下手,后面的工作就容易一些了,万事开头难啊,和同学们在一起,不明白的地方可以随时问,互相帮助,完成课程设计,这样的一段经历,或许是我在完成课程设计的同时,收获的一份财富。

同时这次的设计也激发出了我的刻苦钻研精神,通过刻苦的钻研,我很好的学会了虚拟电子实验室软件而且还把自己设计总电路图用仿真软件绘出来,重要的是最后的仿真结果还达到了设计的要求。

这次设计终于落下了帷幕,虽然时间不长很紧张,但让我真的学到了不少受益终生的知识和认识,它不仅丰富了我的知识,更让我看到了实际上的应用。

在我的成长之路上留下了深深的脚印。

虽然时间紧张,工作量大,身心劳累,但学到的知识和设计的经验确实使自己提高了很多。

而这些经验都会伴随着我今后的学习,也为我们以后完成毕业设计打下基础。

十、参考文献[1] 孙余凯、吴鸣山、项绮明等编.555时基电路识图.北京.电子工业出版社.2006[2] 杨崇志.特殊新型电子元器件手册.沈阳.辽宁科学出版社.2005[3] 董平.电子技术实验.北京.电子工业出版社.2003[4] 熊宝辉.电子技术基础.沈阳.水利电力出版社.1991[5] 付植桐.电子技术.北京.高等教育出版社.2004[6] 戴士弘.模拟电子技术实验与实习.北京.电子公寓出版社.1998[7] 侯大年.数字电子技术.北京.电子工业出版社.1999[8] 施齐云.数字电路实验与课程设计.哈尔滨工程大学.2001[9] 胡汉章.数字电路分析与实践.中国电力出版社.2009[10]李中发.电子技术.中国水利出水电版社.2009十一、总电路图十二、成绩考核。