lattice公司可编程逻辑器件开发软件ispDesignExpert

ISP技术

ISP技术 ISP技术

ABEL-HDL语言 编程软件ispEXPERT

ISP技术

ISP技术

ISP技术的特点 ISP逻辑器件系列 ispLSI器件的结构 在系统编程原理和方法

ISP技术的特点

一、在系统编程

在系统编程(ISP):指用户具有在自己设计的线路板上为 重构逻辑而对逻辑器件进行反复编程改写的能力。 ISP技术是美国Lattice半导体公司首先提出来的一种能 在产品设计、制造过程中的每个环节具有对其器件、电路或 整个数字系统的逻辑和功能随时进行组态或重组能力的最新 技术。在可编程逻辑器件(Programming Logic Device, PLD)及其技术中,ISP是一种新的概念、新的标准。

ISP逻辑器件系列

目前,商品化的在系统可编程逻辑器件有 (1)ISPLSI (2)ISPGAL (3)ISPGDS(Generic Digital Switch).

ISP逻辑器件系列

一、ispLSI系列

美国Lattice公司是世界上第一片GAL诞生地.特别是九十年 代发明并率先推出的ISP技术,开拓了新一代的ttice公 司已将ISP技术应用到高密度可编程逻辑器件(HDPLD)中,形 成ispLSI系列高密度在系统可编程逻辑器件.

可变成逻辑器件厂商

随着可编程逻辑器件应用的赢利吸力和日益广泛,许多IC制 造厂家涉足PLD/FPGA领域。目前世界上有十几家生产 CPLD/FPGA的公司,最大的三家是:ALTERA,XILINX, Lattice,其中ALTERA和XILINX占有了60%以上的市场份额。 3、 Lattice:Lattice是ISP技术的发明者, ISP技术极大的 促进了PLD产品的发展,与ALTERA和XILINX相比,其开发 工具比ALTERA和XILINX略逊一筹。中小规模PLD比较有特 色,不过其大规模PLD、FPGA的竞争力还不够强 1999年 推出可编程模拟器件。99年收购Vantis(原AMD子公司), 成为第三大可编程逻辑器件供应商。2001年12月收购agere 公司(原Lucent微电子部)的FPGA部门。主要产品有 ispLSI2000/5000/8000, MACH4/5,ispMACH4000等

lattice FPGA简介

为什么Lattice在进入FPGA市场的第一年就能取得这么好的成绩?我想这里面可能有三个层次的深层原因:第一,针对Altera和Xilinx在高端有Stratix和Virtex、在低端有Cyclone和Spartan产品的情况下,我们选择了从中端切入的策略,从而在刚进入FPGA应用市场时能够有效地避免与已在高端和低端市场确立了自己领导地位的Altera和Xilinx发生正面冲撞,二年多来的实践证明这一策略是非常正确的;第二,我们在满足市场要求的严格质量前提下做出了自己的产品特色,例如,我们的低端LatticeECP2/M FPGA产品在保持对Cyclone和Spartan价格竞争力的前提下,再增加了一些切合用户实际应用需要而主要竞争对手还没有的功能,如更多的高速串行接口、更多的I/O口、128位AES加密和更大的内部存储空间等;第三,系统制造商心里也期望市场能涌现出较强的第3个FPGA供应商,因为这样才能形成稳定的三足鼎立之势,促进市场的有序竞争,并帮助它们稳定供应链和进一步降低运营成本。

目前FPGA和CPLD在哪些主要应用空间具有不可替代的关键地位?目前FPGA和CPLD的目标应用主要可分为以下三大类:低成本应用、对价格敏感的高性能应用、以及需要极高性能的应用。

第一类应用包括等离子或LCD TV、VoIP、机顶盒、图像渲染、音频处理和控制逻辑,第二类应用包括企业联网、GPON、企业存储、无线基站、协议转换、网络交换、图像滤波和存储器桥接,第三类应用包括光纤联网、SDH线路卡、下一代40G光通道卡、局域网交换机、DDR3存储器测试仪、高端服务器、背板高速接口、数据包成帧和分拆、高速存储器控制和高速信号处理。

Lattice目前主要有哪几条产品线?它们各针对什么目标应用?Lattice目前主要有4条产品线:针对低端市场的低成本FPGA LatticeECP2/M、针对高端市场的系统级高性能FPGA LatticeSC/M、带嵌入式闪存的非易失性FPGA LatticeXP和MachXO、以及混合信号PLD ispClock和Power Manager II,LatticeECP2和LatticeECP2M的主要区别是后者还带有SRAM存储器,LatticeSC和LatticeSCM的主要区别也一样。

第六章 LATTICE系列CPLD_13

第6章Lattice 系列CPLD6.1 概述6.2 CPLD器件系列简介6.1 概述Lattice Semiconductor Corporation 是世界著名的可编程器件厂商,它长期致力于高性能可编程逻辑器件及相关软件的设计、开发和销售。

Lattice可编程器件普遍采用其发明的E2 (电可擦除、电可编程)CMOS工艺和ISP(In System Programmable)技术,具备兼容IEEE 1532标准的在系统可编程性和IEEE 1149.1标准边界扫描可测试性,支持用户直接对安装在电路板上的该类器件进行编程、再编程以及功能与连通性测试,从而在产品的整个生命周期中获得许多利益和方便。

目前,该公司已研制并改进了一系列ISP器件(包括SPLD、CPLD、ispXPLD、FPGA、FPSC)、软件及相关产品,为用户提供了全面的可编程逻辑设计与开发解决方案。

它所提供的ispLEVER设计工具简单易用且支持所有的Lattice可编程逻辑器件,而品种丰富的评估套件/评估板也非常便于用户评估其设计实现,从而加速了其产品开发进程。

ISP 器件及技术的主要优点设计生产用户现场服务,技术支持缩短产品从设计到上市的周期简化系统试制过程提高电路板的可测试性减少器件的实物库存减少生产成本提高系统的质量和可靠性易于在用户现场进行检测和调试经济方便的远程对系统更新和修复6.2 CPLD器件系列简介如表6.1所示,Lattice经过优化的CPLD、XPLD组合包括多种具有不同特点、面向不同应用的器件系列,包括跨越式PLD(MachXO系列)、主流CPLD(ispMACH 4000V/B/C系列)、先进CPLD(ispXPLD5000MV/B/C系列)、5V CPLD(ispMACH4A5系列)、混合信号CPLD (ispPAC-POWR1208/604器件),因而能够提供成本优化和性能领先的解决方案。

表6.1 Lattice CPLD和XPLD器件系列一览表电源系列宏单元t/ns F max/MHz I/O 存储器/Kb PLLPD1.2 V MachXO 128~1140* 3.5 345 73~271 0~27.6 0~2MachXO 128~1140* 3.5 345 73~271 0~27.6 0~25000MC 256~1024 3.5 300 141~381 64~512 2 1.8 V4000C 32~512 2.5 400 30~208 ——4000Z 32~256 3.5 267 32~128 ——MachXO 128~1140* 3.5 345 73~271 0~27.6 0~2 2.5 V5000MB 256~1024 3.5 300 141~381 64~512 24000B 32~512 2.5 400 30~208 ——MachXO 128~1140* 3.5 345 73~271 0~27.6 0~2 3.3 V5000MV 256~1024 3.5 300 141~381 64~512 24000V 32~512 2.5 400 30~208 ——5 V 4A5 32~256 5 182 32~128 ——6.2.1 MachXO跨越式可编程逻辑器件MachXO系列将FPGA的灵活性与CPLD的性能相结合,故被称为跨越式可编程逻辑器件。

莱迪思发布新一代ispLEVERTM设计工具

发者 一个简单而有力的工具 ,用于设计所有莱迪思可编 用者找 出最 适宜 的设 计 编辑器 的 设置 。

强逻辑产品。最新版本的 ispLEVER工具套件支持 莱迪

· ispVMTM 系统 .针 对所 有莱 迪 思 ISP器 件 的编程

思新 的 ispXPGATM 和 ispXPLDTM 产品 系列 ,并集 fj殳了 软件,包括 JEDEC,SVF以及对 IEEE 1532 ISC编程标

布蜀布线的控制。有色编码的图形 用户接 口帮助设计者 ispPACTM可编程模拟产品。 莱迪思继续供应最多的、创

容易地识别并且确定布线的拥挤处,定位及移动设计实 新 性的可编程产品,为系统设计者服务。

例, 并且解决关键的时序问题 。ispLEVER v2.0软件继

获取

承了先前莱迪思设计工具 中强大的特点和工具 。其包括: ispLEVER 设计工具现在即可获得,初始报价为 995美

Z ≤ 1.0(Ill 一

维普资讯

莱迪思 发布新 一代 ispLEVERTMi ̄计工具

': 尔斯波罗市,俄勒冈州~2OO2年 9月 16日一在系

· 具有 SpeedSEARCHTM 挣 }生的 Performance Anal—

币 统可编程(ISP)逻辑产品的发明者——莱迪思半导 ystTM工具.在无需重新编译的情况下,提供使用者灵活

·Constraints Editor工具 .允许经由一个图形用户 元 。进一步的信息请与莱迪 思半导体公司销售代表联 系。

“拖 一放”接 口选择 I/O设M

皿成 群半导体,日前新推出一款 2K x bit的低功率静 HT62L256有一个 内建的自动 power down挣 l生,当它不

ispEXPERT使用方法简介

ispEXPERT使用方法简介3.2.1概述ispEXPERT是美国Data I/O公司推出的一个世界级的强有力的用于可编程逻辑器件的数字系统设计软件,它是一种基于Windows的设计工具,是一套完整的EDA软件。

设计输入可采用原理图、硬件描述语言、混合输入三种方式。

能对所设计的数字电子系统进行功能仿真和时序仿真。

ispEXPERT 编译器是此软件的核心,能进行逻辑优化,将逻辑映射到器件中去,自动完成布局与布线并生成编程所需要的熔丝图(.jed)文件。

软件支持所有Lattice 公司的ispLSI器件、pLSI器件、ispGDS器件、ispGAL器件。

并能实现系统仿真。

ISP技术使用户能够在无需从电路板上拆下芯片的情况下,改变芯片的逻辑内容,实现在系统编程。

这种技术的应用能大大缩短电子系统设计周期,简化生产流程,降低生产成本,并可在现场对系统进行逻辑重构和升级。

ISP技术的发明,使硬件随时能够改变组态,实现了硬件设计软件化,革命性地改变了电子系统设计的传统概念和方法。

ispEXPERT软件的主要特征:1.输入方式* 原理图输入* ABEL-HDL 输入* VHDL 输入* Verilog-HDL 输入2.逻辑模拟* 功能模拟* 时序模拟* 静态时序分析3.编译器* 结构综合、映射、自动布局和布线4.支持的器件* 含有宏库,有500个宏元件可供调用* 支持所有ISP器件5.下载软件* ISP 菊花链下载软件3.2.2原理图输入原理图输入方式是比较简单易学的一种方法,只要按照原理图的形式将图画出,设定一定的输入输出符号,系统即可自动生成编程所需要的熔丝图文件,本章介绍如何使用原理图输入方式完成一个电路的设计。

1. 创建一个新的设计项目可以按照以下步骤创建一个新的设计项目: (1)启动isp Expert System按开始=>程序=>Lattice Semiconductor=>ispEXPERT System ,或者从桌面快捷方式中直接进入,屏幕上出现如图3.16所示的项目管理器窗口。

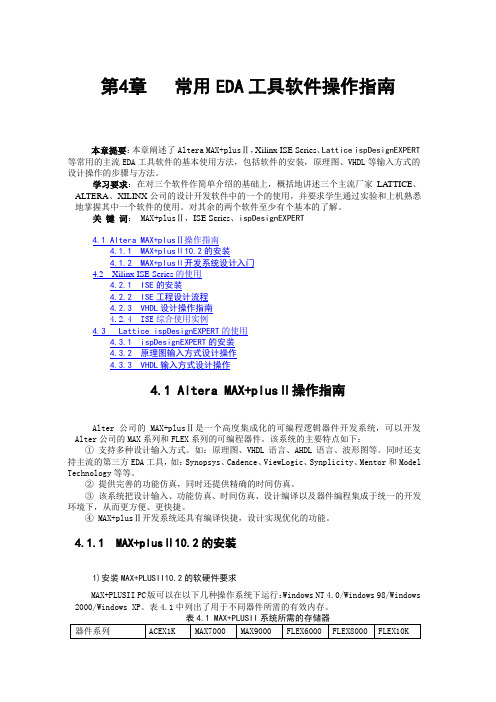

常用EDA工具软件操作指南

第4章常用EDA工具软件操作指南本章提要:本章阐述了Altera MAX+plusⅡ,Xilinx ISE Series、Lattice ispDesignEXPERT 等常用的主流EDA工具软件的基本使用方法,包括软件的安装,原理图、VHDL等输入方式的设计操作的步骤与方法。

学习要求:在对三个软件作简单介绍的基础上,概括地讲述三个主流厂家LATTICE、ALTERA、XILINX公司的设计开发软件中的一个的使用,并要求学生通过实验和上机熟悉地掌握其中一个软件的使用。

对其余的两个软件至少有个基本的了解。

关键词:MAX+plusⅡ,ISE Series、ispDesignEXPERT4.1 Altera MAX+plusⅡ操作指南4.1.1 MAX+plusⅡ10.2的安装4.1.2 MAX+plusⅡ开发系统设计入门4.2 Xilinx ISE Series的使用4.2.1 ISE的安装4.2.2 ISE工程设计流程4.2.3 VHDL设计操作指南4.2.4 ISE综合使用实例4.3 Lattice ispDesignEXPERT的使用4.3.1 ispDesignEXPERT的安装4.3.2 原理图输入方式设计操作4.3.3 VHDL输入方式设计操作4.1 Altera MAX+plusⅡ操作指南Alter公司的MAX+plusⅡ是一个高度集成化的可编程逻辑器件开发系统,可以开发Alter公司的MAX系列和FLEX系列的可编程器件。

该系统的主要特点如下:①支持多种设计输入方式。

如:原理图、VHDL语言、AHDL语言、波形图等。

同时还支持主流的第三方EDA工具,如:Synopsys、Cadence、ViewLogic、Synplicity、Mentor和Model Technology等等。

②提供完善的功能仿真,同时还提供精确的时间仿真。

③该系统把设计输入、功能仿真、时间仿真、设计编译以及器件编程集成于统一的开发环境下,从而更方便、更快捷。

第三章 ISP器件的编程软件

建立由原理图源文件组成的设计

1、进入原理图设计环境 进入原理图设计环境的开始步骤与进入ABEL-HDL语言设计 环境是一致的,如启动ispDesignEXPERT建立新项目、建立一个 新的源文件等工作。在源文件形式选择对话窗中,选择 Schematic(原理图),则出现文件名对话框,键入原理图文件名 (扩展名是sch或者不键入)后,单击保存按钮,则进入原理编辑 器。

建立由原理图源文件组成的设计

启动Add/Net Name命令,在屏幕底下的状态栏内输入连线 名,并按Enter键确认;连线名附在光标上,移动光标到目的地, 单击鼠标左键,连线名标注在连线旁边。如果连线名以数字为 后缀,除键入连线名外,最后多键入一个加号(+),则可命名 一组连续的连线名。例如键入end0+后,则会自动生成end1、 end2……。 ispDesignEXPERT软件对字母大小写敏感,因此在 它处引用连线名时,大小写应注意一致。 用复合名命名一条连线使连线定义为总线。复合名的格式 是:总线名[序号表]。一种序号表是标明起始序号和终止序号的 下标范围。起始序号和终止序号用冒号:)分开,如data[3: 0]。另一种序号表是用逗号分开的序号,如addr(1,3,2,5, 0)。

由ABEL-HDL源文件组成的设计 源文件组成的设计

■ 现在出现了如图所示的ABEL-HDL源文件模板。它是一个具 有屏幕编辑能力的文件编辑器。

建立由原理图源文件组成的设计

ispDesignEXPERT软件包含一个原理图输入系统。一张原 理图可以代表一个简单的逻辑电路(如一个与门)、一个复杂元件 或者一个顶层电路图。原理图是描述硬件结构的一种重要方式, 具有直观、清晰、易于掌握全局信号关系等优点,硬件设计工 程师都熟悉它。一幅原理图相当于ABEL-HDL语言的一个源文件, 绝大多数情况下相当于一个模块(规范设计应当这样做,就像一 个ABEL-HDL源文件最好只包括一个模块一样)。它由以下几部 分构成: 1. 元件 2. 连线 3. I/O标记 4. 图片和文字

2024ispLEVER教程

ispLEVER教程•教程简介与背景•ispLEVER 基础操作•原理图设计与编辑技巧•PCB 布局布线实战演练•仿真测试与验证方法论述•团队协作与版本控制策略分享目录CONTENTS01教程简介与背景ispLEVER概述ispLEVER 是Lattice半导体公司提供的一款集成开发环境(IDE),用于设计、模拟和编程Lattice FPGA和CPLD器件。

它提供了一套完整的工具链,包括设计输入、综合、布局布线、时序分析、仿真和下载等,方便用户进行FPGA/CPLD设计。

ispLEVER支持多种设计输入方式,如原理图、硬件描述语言(HDL)和混合输入等,并提供了丰富的IP核和库函数,以加速设计过程。

教程目标与内容本教程的目标是帮助读者掌握ispLEVER的基本操作和设计流程,能够独立完成简单的FPGA/CPLD设计。

教程内容包括ispLEVER的安装与配置、设计输入、综合与布局布线、时序分析、仿真和下载等关键步骤的详细讲解。

通过本教程的学习,读者将了解FPGA/CPLD设计的基本原理和方法,并具备一定的实践能力和问题解决能力。

1 2 3在学习本教程之前,读者应具备数字电路和计算机组成原理的基本知识,了解FPGA/CPLD的基本概念和原理。

读者需要掌握一种硬件描述语言(如VHDL或Verilog),以便进行FPGA/CPLD设计。

对于初学者,建议具备一定的编程基础,如C/C 或Python等,以便更好地理解和应用ispLEVER 中的相关概念和工具。

预备知识与技能要求本教程采用理论与实践相结合的方法,通过详细的步骤讲解和实例演示,帮助读者逐步掌握ispLEVER的使用方法。

对于遇到的问题和困难,可以通过查阅ispLEVER的官方文档或在线论坛寻求帮助和解决方案。

学习方法与建议在学习过程中,建议读者结合实例进行操作练习,加深对相关概念和工具的理解和掌握。

此外,鼓励读者在学习过程中积极思考和探索,尝试将所学知识应用于实际项目中,以提高学习效果和实践能力。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Lattice 公司的可编程逻辑器件开发软件ispDesignEXPERT

Lattice公司网站的网址:。

Lattice公司是在系统可编程技术(isp)的发明公司,该公司的可编程逻辑器件ispLSI器件具有使用简单,下载次数10000次和数据保存20年的特点,加之软件的开放程度高,所以该公司的产品在全国各个大学中使用很广泛。

(1)IspLSI CPLD产品介绍

Lattice公司的CPLD产品容量可以达到1000个宏单元,速度可以达到350MHz,输入输出引脚可达68个。

这些产品满足各种电子装置的开发

(2)可编程逻辑器件的软件开发工具

(Programmable Logic Software Development Tools)

Lattice 公司的逻辑软件开发工具是ispDesignEXPERT 系统,该系统包含设计输入、综合、仿真、适配设计和下载等功能,可以满足开发要求。

(3)下载ispDesignEXPERT软件

下载需到Lattice公司的网站,首先应该到下载网页,在下载网页选择要下载的软件。

由于软件太大,需要分四个部分下载。

下载网页:

Home / Products / Development Tools / Resources

Development Tools Downloadable Software

(可供下载的软件)

You have retrieved 23 Development Tools Downloadable Software

Software return to top

•

Lattice Macros for Synario (Support for ISP (ver 3 0) and

full Synario (2 3) versions) (April 11, 1997)

493 KB

•

Lattice Macros for Synario (Support for ISP (ver 5 0) and

full Synario (3 0) versions) (October 28, 1997)

467 KB

•

Lattice Macros for Synario (Support for ISP (ver 5 1) and

full Synario (3 1) versions) (June 8, 1998)

155 KB

PALtoGAL v3 12 35 KB

Reform 14 KB

Reform2 13 KB

DSL Macros for MACH 12 KB

•

DSL Macros for MACH 6 KB

•

MACH-Synario 3 1 Patch 320 KB

•

CP001 -- Source File: Behavioral Modeling in VHDL

Simulations (February 1999)

15 KB

ispDesignEXPERT (PC) v8.4 Starter Software (下载这个

软件)

14 KB

•

ispDesignEXPERT 8.4 Starter (Part 1) (下载这个软件)17.81 MB

•

ispDesignEXPERT 8.4 Starter (Part 2) (下载这个软件)22.74 MB

•

ispDesignEXPERT 8.4 Starter (Part 3) (下载这个软件)15.26 MB

•

ispDesignEXPERT 8.4 Starter (Part 4) (下载这个软件) 6.24 MB

•

ispGDX Development System 3.2 12.90 MB

•

ispGDX Development System 2.4.1 13.13 MB

•

GDS Assembler 265 KB

PAC-Designer Software Download (模拟可编程器件开

发软件)

14 KB

•

PAC-Designer Software 1.3 (模拟可编程器件开发软

件)

7.44 MB

•

ispVM System 10.0

ispVM System - the latest in ISP Programming, based on

Virtual Machine Technology

10.60 MB

•

ispVM System 8 2 2

ispVM System includes LatticePRO, ISP Daisy Chain

Download, and ispVM Download

8.84 MB

•

ispVM EMBEDDED v8.1: C Source code for customized or

embedded JTAG programming applications

ispVM Embedded Software has an added level of password

protection. To get the password call 1-888-ISP-PLDS (US

198 KB

residents) or email ispgenapps@. Please

include your name, company name, phone number and

application.

• These files require a user login and password before they can be downloaded.

Need a new account? Please create a new account.

Already have an account? Please login.

(4)申请许可证

使用Lattice 公司的软件需要从该公司的网站上申请许可证,在安装软件的过程中,软件会弹出一个许可证申请窗口,在该窗口填入必要的信息,就可以通过互连网申请许可证,其实许可证就是一个文件,该文件会从Lattice公司用电子邮件有给你。

然后将该文件拷贝到需要放置的子目录中就可以了。

当然也可以直接到Lattice的网站上申请或者到Lattice公司的上海办事处或是代理商北京中泰康公司、金龙公司索要。