数电存储器例题

(完整版)存储器习题及参考答案

习题四参考答案1.某机主存储器有16位地址,字长为8位。

(1)如果用1k×4位的RAM芯片构成该存储器,需要多少片芯片?(2)该存储器能存放多少字节的信息?(3)片选逻辑需要多少位地址?解:需要存储器总容量为:16K×8位,故,(1)需要1k×4位的RAM芯片位32片。

(2)该存储器存放16K字节的信息。

(3)片选逻辑需要4位地址。

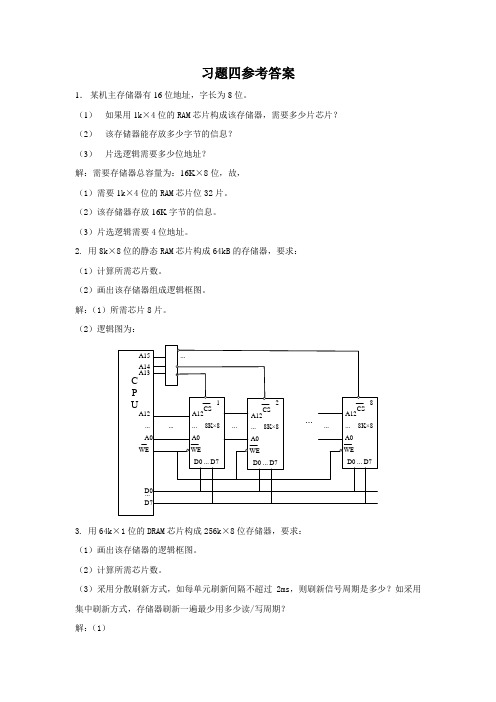

2. 用8k×8位的静态RAM芯片构成64kB的存储器,要求:(1)计算所需芯片数。

(2)画出该存储器组成逻辑框图。

解:(1)所需芯片8片。

(2)逻辑图为:3. 用64k×1位的DRAM芯片构成256k×8位存储器,要求:(1)画出该存储器的逻辑框图。

(2)计算所需芯片数。

(3)采用分散刷新方式,如每单元刷新间隔不超过2ms,则刷新信号周期是多少?如采用集中刷新方式,存储器刷新一遍最少用多少读/写周期?解:(1)(2)所需芯片为32片。

(3)设读写周期为0.5微妙,则采用分散式刷新方式的刷新信号周期为1微妙。

因为64K ×1的存储矩阵是由四个128×128的矩阵构成,刷新时4个存储矩阵同时对128个元素操作,一次刷新就可完成512个元素,整个芯片只有128次刷新操作就可全部完成。

所以存储器刷新一遍最少用128个读/写周期。

4. 用8k×8位的EPROM芯片组成32k×16位的只读存储器,试问:(1)数据寄存器多少位?(2)地址寄存器多少位?(3)共需多少个EPROM芯片?(4)画出该只读存储器的逻辑框图?解:因为只读存储器的容量为:32k×16,所以:(1)数据寄存器16位。

(2)地址寄存器15位。

(3)共需8个EPROM芯片?(4)逻辑框图为:5. 某机器中,已经配有0000H~3FFFH的ROM区域,现在再用8k×8位的RAM芯片形成32k ×8位的存储区域,CPU地址总线为A0~A15,数据总线为D0~D7,控制信号为R/W(读/写)、MREQ(访存),要求:(1)画出地址译码方案。

数电练习题

数电练习题1、(100101.11)2=(_______)10 = (_______)162、逻辑代数有_______、______、______三种基本运算。

3、存储器按存取特性的不同分类,可分为_______、_______两类。

4、0100=⊕⊕⊕Y = _______。

5、TTL 三态门的三种可能输出状态是_______、_______、_______。

6、用4个触发器构成二进制计数器,计数器的最大模为_______。

7、要用n 位二进制数为N 个对象编码,必须满足_______。

8、施密特触发器的应用主要有_______、_______、_______。

9、单稳态触发器有_______个稳定状态;多谐振荡器有_______个稳定状态。

10、CMOS 门电路的闲置输入端不能悬空,对于与门应当接到_______电平,对于或门应当接到_______电平。

11、(26.375)10=(_______)2=(_______)8=(_______)16。

12、逻辑函数常用的表示方法有_______,_______,_______等。

13、时序电路分成_______和 _______两类。

14、逻辑函数表达式A ⊕1=_______。

15、若使JK 触发器异步置0,必须使S D =_______,R D =_______。

16、 D 触发器的特性方程为_______17、TTL 与门的多余输入端应接_______电平,或者与有用端 _______。

18、2n 选1 数据选择器有_______位地址码。

19、晶体三极管作为电子开关时,其工作状态必须为_______状态或_______状态。

20、A/D 转换是指_______转换,它要经过_______、_______两步实现 21、(13.75)10=(_______)2=(_______)8=(_______)16。

22、三种基本逻辑关系有_______,_______,_______。

数电第8章习题答案

习题一、填空题1. 如果一个半导体存储器中有m位地址线,则有2m个存储单元,若输出位数为n位,则其存储容量为n* 2m 位。

2. ROM的电路结构一般由地址译码器、存储矩阵和输出缓冲器等构成。

3. 一片存储容量为4K×1位的ROM芯片应该有12 条地址线。

4. RAM一般由地址译码器、存储矩阵和读写控制电路组成。

5. 将存储容量为2K×4位的RAM扩展成16K×8的存储器,共需要16 片2K×4位的RAM。

二、分析与设计题1. 半导体存储器的特点及分类是什么?半导体存储器分ROM和RAMROM只读存储器只能读,不能写,断电后信息不会丢失,属非易性存储器,ROM又分为1、掩膜ROM:由生产厂商用掩膜技术将程序写入其中,适用于大批量生产2、可编程ROM(PROM或OTP):由用户自行写入程序,一旦写入,不能修改,适用于小批量生产3、可擦除可编程ROM(EPROM ):可由用户自行写入,写入后,可用紫外线光照擦除重新写新的程序,适用于科研4、电可擦除ROM(EEPROM):可用电信号擦除和重新写入的存储器,适用于断电保护RAM 随机存取存储器既能读,又能写,断电后信息会丢失,属易失性存储器RAM用于存放各种现场的输入输出程序,数据,中间结果。

RAM又分为静态RAM,动态RAM1、静态RAM(SRAM):利用半导体触发器两个稳定的状态表示0或1静态RAM又分为双极型的SRAM和MOS管的SRAM双极型的SRAM:用晶体管触发器作为记忆单元MOS管的SRAM:由6个MOS管作为记忆单元双极双极型的SRAM型速度快,MOS管速度慢,不需要刷新2、动态RAM(DRAM):利用MOS管的栅极电容保存信静态RAM息,即电荷的多少表示0和1。

动态RAM需要进行刷新操作2. 某台计算机的内存储器设置有32位的地址线,16位并行数据输入/输出端,试计算它的最大存储量是多少?答: 232 *16位3. 试用4片4K ×4位的RAM 接成16K ×4位的存储器。

数字电子技术第8章存储器与可编程逻辑器件习题及答案

第8章存储器与可编程逻辑器件8.1存储器概述自测练习1.存储器中可以保存的最小数据单位是()。

(a)位(b)字节(c)字2.指出下列存储器各有多少个基本存储单元?多少存储单元?多少字?字长多少?(a) 2K×8位()()()()(b) 256×2位()()()()(c) 1M×4位()()()()3.ROM是()存储器。

(a)非易失性(b)易失性(c)读/写(d)以字节组织的4.数据通过()存储在存储器中。

(a)读操作(b)启动操作(c)写操作(d)寻址操作5.RAM给定地址中存储的数据在()情况下会丢失。

(a)电源关闭(b)数据从该地址读出(c)在该地址写入数据(d)答案(a)和(c)6.具有256个地址的存储器有( )地址线。

(a)256条(b)6条(c)8条(d)16条7.可以存储256字节数据的存储容量是( )。

(a)256×1位(b)256×8位(c)1K×4位 (d)2K×1位答案:1.a2.(a)2048×8;2048;2048;8(b)512;256;256;2(c)1024×1024×4;1024×1024;1024×1024;43.a4.c5.d6.c7.b8.2随机存取存储器(RAM)自测练习1.动态存储器(DRAM)存储单元是利用()存储信息的,静态存储器(SRAM)存储单元是利用()存储信息的。

2.为了不丢失信息,DRAM必须定期进行()操作。

3.半导体存储器按读、写功能可分成()和()两大类。

4.RAM电路通常由()、()和()三部分组成。

5.6116RAM有()根地址线,()根数据线,其存储容量为()位。

答案:1.栅极电容,触发器2.刷新3.只读存储器,读/写存储器4.地址译码,存储矩阵,读/写控制电路5.11,8,2K×8位8.3 只读存储器(ROM)自测练习1.ROM可分为()、()、()和()几种类型。

数字电路与逻辑设计习题7第七章半导体存储器(精)

第七章半导体存储器一、选择题1.一个容量为1K ×8的存储器有个存储单元。

A.8B.8KC.8000D.81922.要构成容量为4K ×8的R AM ,需要片容量为256×4的R AM 。

A.2B.4C.8D. 323.寻址容量为16K ×8的RAM 需要根地址线。

A.4B. 8C.14D. 16E.16K4.若R AM 的地址码有8位,行、列地址译码器的输入端都为4个,则它们的输出线(即字线加位线)共有条。

A.8B.16C.32D.2565.某存储器具有8根地址线和8根双向数据线,则该存储器的容量为。

A.8×3B.8K ×8C. 256×8D. 256×2566. 采用对称双地址结构寻址的1024×1的存储矩阵有。

A.10行10列B.5行5列C.32行32列D. 1024行1024列7.随机存取存储器具有功能。

A. 读/写B. 无读/写C. 只读D. 只写8.欲将容量为128×1的R AM 扩展为1024×8,则需要控制各片选端的辅助译码器的输出端数为。

A.1B.2C.3D. 89.欲将容量为256×1的R AM 扩展为1024×8,则需要控制各片选端的辅助译码器的输入端数为。

A.4B.2C.3D. 810.只读存储器ROM 在运行时具有功能。

A. 读/无写B. 无读/写C. 读/写D. 无读/无写11.只读存储器R OM 中的内容,当电源断掉后又接通,存储器中的内容。

A. 全部改变B. 全部为0C. 不可预料D. 保持不变12.随机存取存储器RAM 中的内容,当电源断掉后又接通,存储器中的内容。

A. 全部改变B. 全部为1C. 不确定D. 保持不变13.一个容量为512×1的静态RAM 具有。

A. 地址线9根,数据线1根B. 地址线1根,数据线9根C. 地址线512根,数据线9根D. 地址线9根,数据线512根14.用若干R AM 实现位扩展时,其方法是将相应地并联在一起。

数电第十一章习题答案

• 13.图题(a)为心律失常报警电路,经放大后的 .图题( )为心律失常报警电路, V 如图( )所示, 的幅值Vm=4V。试 心电信号VI 如图(b)所示,I 的幅值 。 回答以下问题: 回答以下问题: 1)对应分别画出图中的A,B,C三点电压波形 三点电压波形; (1)对应分别画出图中的A,B,C三点电压波形; (2)所明电路的组成及工作原理。 )所明电路的组成及工作原理。

VTRI

VTHRቤተ መጻሕፍቲ ባይዱ

VTRI

为低电平(< 1 VCC

3

时,VC 为高电平,VTHR > 时, VC 为低电 平

2 V CC 3

• 第一级555定时器构成施密特触发器,将心律信 号整形为脉冲信号;第二级的是由单稳态触发器 加上BJT构成可重复触发的单稳态触发器。当心 律正常时,VA的频率较高,周期较短,使得VB不 能充电至

第十一章习题

• 11.下图所示电路是由555定时器构成的锯齿波发 .下图所示电路是由 定时器构成的锯齿波发 生器, 构成恒流源电路, 生器,BJT和电阻 R 1 R R3构成恒流源电路,给定时 和电阻 电容C充电 充电。 输入负脉冲后, 电容 充电。当触发输入端 v1 输入负脉冲后,画出 电容电压 vc及555输出端v0 的波形,并计算电容C 输出端 的波形,并计算电容 充电时间。 充电时间。

C

duc =I dt

,

• 12.由555定时器组成的脉冲宽度鉴别电路及输 . 定时器组成的脉冲宽度鉴别电路及输 VT 波形如图题所示。 入 VI波形如图题所示。集成施密特电路VT + =3V, − , =1.6V,单稳的输出脉宽 TW有 t1 <TW < t2的关系。 的关系。 单稳的输出脉宽 画出电路中B, , , 各点波形 各点波形, 对应 VI 画出电路中 ,C,D,E各点波形,并说 端输出负脉冲的作用。 明D,E端输出负脉冲的作用。 , 端输出负脉冲的作用

数字电子技术存储器与可编程逻辑器件习题及答案

第8章存储器与可编程逻辑器件8.1存储器概述自测练习1.存储器中可以保存的最小数据单位是()。

(a)位(b)字节(c)字2.指出下列存储器各有多少个基本存储单元?多少存储单元?多少字?字长多少?(a)2K×8位()()()()(b)256×2位()()()()(c)1M×4位()()()()3.ROM是()存储器。

(a)非易失性(b)易失性(c)读/写(d)以字节组织的4.数据通过()存储在存储器中。

(a)读操作(b)启动操作(c)写操作(d)寻址操作5.RAM给定地址中存储的数据在()情况下会丢失。

(a)电源关闭(b)数据从该地址读出(c)在该地址写入数据(d)答案(a)和(c)6.具有256个地址的存储器有()地址线。

(a)256条(b)6条(c)8条(d)16条7.可以存储256字节数据的存储容量是()。

(a)256×1位(b)256×8位(c)1K×4位(d)2K×1位答案:1. a2.(a)2048×8;2048;2048;8(b)512;256;256;2(c)1024×1024×4;1024×1024;1024×1024;43.a4.c5.d6.c7.b8.2随机存取存储器(RAM)自测练习1.动态存储器(DRAM)存储单元是利用()存储信息的,静态存储器(SRAM)存储单元是利用()存储信息的。

2.为了不丢失信息,DRAM必须定期进行()操作。

3.半导体存储器按读、写功能可分成()和()两大类。

4.RAM电路通常由()、()和()三部分组成。

5.6116RAM有()根地址线,()根数据线,其存储容量为()位。

答案:1.栅极电容,触发器2.刷新3.只读存储器,读/写存储器4.地址译码,存储矩阵,读/写控制电路5.11,8,2K×8位8.3 只读存储器(ROM)自测练习1.ROM可分为()、()、()和()几种类型。

存储器习题解答

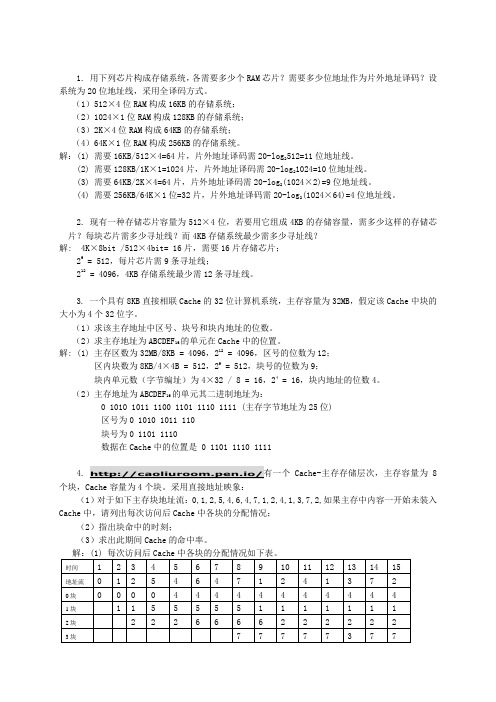

1. 用下列芯片构成存储系统,各需要多少个RAM芯片?需要多少位地址作为片外地址译码?设系统为20位地址线,采用全译码方式。

(1)512×4位RAM构成16KB的存储系统;(2)1024×1位RAM构成128KB的存储系统;(3)2K×4位RAM构成64KB的存储系统;(4)64K×1位RAM构成256KB的存储系统。

解:(1) 需要16KB/512×4=64片,片外地址译码需20-log2512=11位地址线。

(2) 需要128KB/1K×1=1024片,片外地址译码需20-log21024=10位地址线。

(3) 需要64KB/2K×4=64片,片外地址译码需20-log2(1024×2)=9位地址线。

(4) 需要256KB/64K×1位=32片,片外地址译码需20-log2(1024×64)=4位地址线。

2. 现有一种存储芯片容量为512×4位,若要用它组成4KB的存储容量,需多少这样的存储芯片?每块芯片需多少寻址线?而4KB存储系统最少需多少寻址线?解: 4K×8bit /512×4bit= 16片,需要16片存储芯片;29 = 512,每片芯片需9条寻址线;212 = 4096,4KB存储系统最少需12条寻址线。

3. 一个具有8KB直接相联Cache的32位计算机系统,主存容量为32MB,假定该Cache中块的大小为4个32位字。

(1)求该主存地址中区号、块号和块内地址的位数。

(2)求主存地址为ABCDEF16的单元在Cache中的位置。

解: (1) 主存区数为32MB/8KB = 4096,212 = 4096,区号的位数为12;区内块数为8KB/4×4B = 512,29 = 512,块号的位数为9;块内单元数(字节编址)为4×32 / 8 = 16,24 = 16,块内地址的位数4。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.若某一单板机的存储器连线如下图所式,其中地址译码器的输出与输入编码之间的关系如下表所式:

分析图中ROM、PROM1、PROM2和各组RAM(1K为一组)的地址范围;每一种存储器的地址有没有重叠,重叠区是什么?若用2114片子扩展4KRAM有没有可能?片子的各地址、数据、控制线应如何连接。

如果A

15A

14

参加译码(全译码),则每一种存储器的地址没有重叠。

如果A

15A

14

不参加译码(部分译码),则每一种存储器的地址另有3种地址重叠,每种2K。

系统地址总线16条。

3/8译码器的8条译码线,每条寻址2K,共64K.故可以用2114片

子扩展4KRAM,用Y

3、Y

5

、Y

6

中的2条译码线就可以。

其三总线的连接方式如RAM1.

2.参看8088系统的基本ROM图,写出分配给ROM的所有地址(包括重复地址)。

当ABC=110时Y6有效,ABC=111时Y7有效。