数字电路第8章存储器

第八章扩展存储器方案

#1楼

00 01 10 11

常用的存储器地址分配的方法有3种:全译码、部分译码和线选 法。

1. 全译码 利用系统的全部的高位地址线作为存储器芯片(或I/O接口芯 片)的片选信号。 特点:地址与存储单元一一对应,地址空间的利用率高。

例8-1: 利用全译码为80C51扩展16KB的外部数据存储器,存 储芯片选用SRAM6264,要求外部数据存储器占用从0000H开 始的连续地址空间。

读选通、写选通信号。

思考题: 请问执行 MOVX A,@DPTR指令时,RD和WR引脚的状态?

8.3 读写控制、地址空间分配和外部地址锁存器

8.3.1 存储器地址空间分配

存储器空间分配除考虑地址线连接外,还讨论各存储器芯片在整个存 储空间中所占据的地址范围。

单片机地址总线为16条,可寻址的最大空间为64KB,用户可根据系统的 需要确定扩展存储器容量的大小。

使用MOVX A,@Ri和MOVX @Ri,A。这时通过P0口输出Ri中 的内容(低8位地址),而把P2口原有的内容作为高8位地址 输出。

例8-4 将程序存储器中以TAB为首址的32个单元的内容依次传 送到外部RAM以7000H为首地址的区域去。

分析:DPTR指向标号TAB的首地址。R0既指示外部RAM的地址, 又表示数据标号TAB的位移量。本程序的循环次数为32,R0 的值:0~31,R0的值达到32就结束循环。程序如下:

MOV P2,#70H MOV DPTR,#TAB MOV R0,#0 AGIN: MOV A,R0 MOVC A,@A+DPTR MOVX @R0,A INC R0 CJNE R0,#32,AGIN HERE: SJMP HERE TAB: DB ……

第八章 数字集成电路基本单元及版图(续)

漏极开路输出单元

如果希望系统支持多个集成电路的正常逻辑 输出同时到总线以实现某种操作,就必须对集成 电路的输出单元进行特殊的设计以支持“线逻 辑”。同时,总线也将做适当的改变。 漏极开路输出单元结构就是其中的一种。下 图给出了两种漏极开路结构的输出单元,其中 (a)图的内部控制信号是通过反相器反相控制 NMOS管工作的方式,(b)图是同相控制的方 式。

动态存储器DRAM (Dynamic RAM)

主要指标:存储容量、存取速度。

存储容量: 用字数×位数表示,也可只用位数表 示。如,某动态存储器的容量为109位/片。 存取速度:用完成一次存取所需的时间表示。 高速存储器的存取时间仅有10ns左右。

存储单元的等效电路(1)

字线 字线

VP 位线 (a) DRAM 位线 (b) SRAM 位线

漏极开路输出单元

(a)反相器反相控制方式

(b)同相控制的方式

漏极开路结构实现的线逻辑

Vcc bi

A1

A2

目的:减少电 AN

表达式为

路结构和成本

bi A1 A 2 A N A1 A 2 A Nห้องสมุดไป่ตู้

输入、输出双向三态单元(I/O PAD)

在许多应用场合,需要某些数据端同时具有输入、输 出的功能,或者还要求单元具有高阻状态。在总线结构的 电子系统中使用的集成电路常常要求这种I/O PAD。下 图是一个输入、输出双向三态的I/O PAD单元电路。

存储单元的等效电路(2)

字线 Cut 位线 (c) 熔丝型ROM 位线 (d) EROM(EEPROM) 位线 (e) FRAM 字线 浮栅 字线

DRAM

随着高密度存储器的不断发展,存 储单元尺寸逐渐减小,这种趋势使得结 构简单的动态RAM成为首选。 DRAM单元发展过程中出现几个阶 段,这些阶段的发展使得DRAM的单元 面积越来越小。

课后习题答案第8章_存储器和可编程逻辑器件

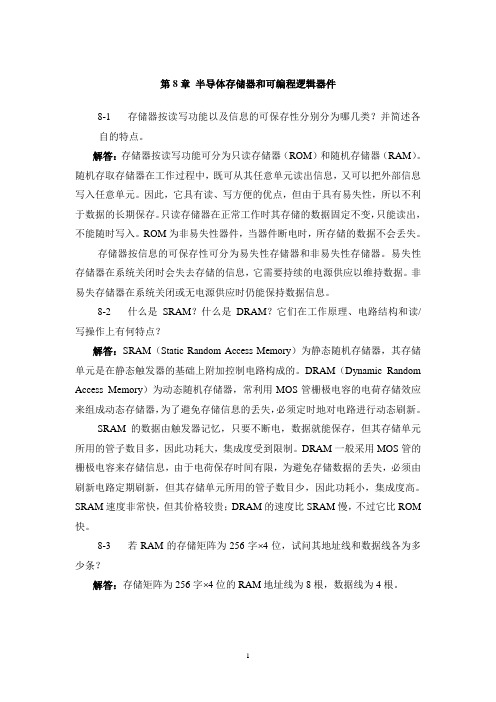

第8章半导体存储器和可编程逻辑器件8-1存储器按读写功能以及信息的可保存性分别分为哪几类?并简述各自的特点。

解答:存储器按读写功能可分为只读存储器(ROM)和随机存储器(RAM)。

随机存取存储器在工作过程中,既可从其任意单元读出信息,又可以把外部信息写入任意单元。

因此,它具有读、写方便的优点,但由于具有易失性,所以不利于数据的长期保存。

只读存储器在正常工作时其存储的数据固定不变,只能读出,不能随时写入。

ROM为非易失性器件,当器件断电时,所存储的数据不会丢失。

存储器按信息的可保存性可分为易失性存储器和非易失性存储器。

易失性存储器在系统关闭时会失去存储的信息,它需要持续的电源供应以维持数据。

非易失存储器在系统关闭或无电源供应时仍能保持数据信息。

8-2什么是SRAM?什么是DRAM?它们在工作原理、电路结构和读/写操作上有何特点?解答:SRAM(Static Random Access Memory)为静态随机存储器,其存储单元是在静态触发器的基础上附加控制电路构成的。

DRAM(Dynamic Random Access Memory)为动态随机存储器,常利用MOS管栅极电容的电荷存储效应来组成动态存储器,为了避免存储信息的丢失,必须定时地对电路进行动态刷新。

SRAM的数据由触发器记忆,只要不断电,数据就能保存,但其存储单元所用的管子数目多,因此功耗大,集成度受到限制。

DRAM一般采用MOS管的栅极电容来存储信息,由于电荷保存时间有限,为避免存储数据的丢失,必须由刷新电路定期刷新,但其存储单元所用的管子数目少,因此功耗小,集成度高。

SRAM速度非常快,但其价格较贵;DRAM的速度比SRAM慢,不过它比ROM 快。

8-3若RAM的存储矩阵为256字⨯4位,试问其地址线和数据线各为多少条?解答:存储矩阵为256字⨯4位的RAM地址线为8根,数据线为4根。

8-4某仪器的存储器有16位地址线,8位数据线,试计算其最大存储容量是多少?解答:最大存储容量为216⨯8=524288=512k bit(位)8-5用多少片256⨯4位的RAM可以组成一片2K⨯8位的RAM?试画出其逻辑图。

数字电子技术基础习题册答案

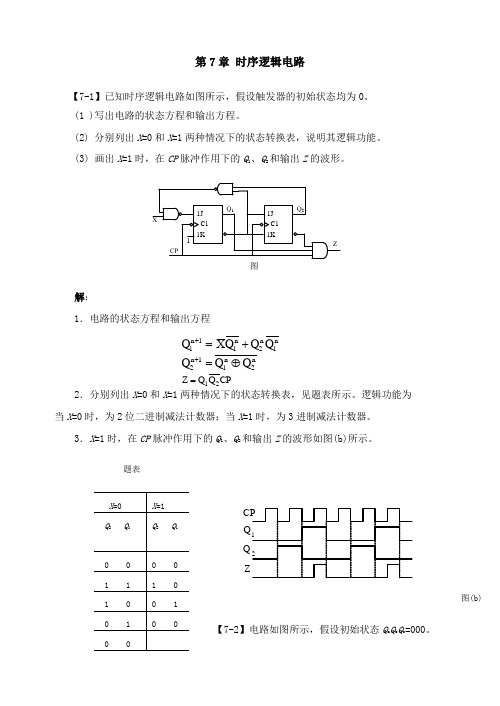

第7章 时序逻辑电路【7-1】已知时序逻辑电路如图所示,假设触发器的初始状态均为0。

(1 )写出电路的状态方程和输出方程。

(2) 分别列出X =0和X =1两种情况下的状态转换表,说明其逻辑功能。

(3) 画出X =1时,在CP 脉冲作用下的Q 1、Q 2和输出Z 的波形。

1J 1KC11J 1KC1Q 1Q 2CPXZ1图解:1.电路的状态方程和输出方程n 1n2n 11n 1Q Q Q X Q +=+n 2n 11n 2Q Q Q ⊕=+ CP Q Q Z 21=2.分别列出X =0和X =1两种情况下的状态转换表,见题表所示。

逻辑功能为 当X =0时,为2位二进制减法计数器;当X =1时,为3进制减法计数器。

3.X =1时,在CP 脉冲作用下的Q 1、Q 2和输出Z 的波形如图(b)所示。

题表Q Q Z图(b)【7-2】电路如图所示,假设初始状态Q a Q b Q c =000。

(1) 写出驱动方程、列出状态转换表、画出完整的状态转换图。

(2) 试分析该电路构成的是几进制的计数器。

Q c图解:1.写出驱动方程1a a ==K J ncn a b b Q Q K J ⋅== n b n a c Q Q J = n a c Q K = 2.写出状态方程n a 1n a Q Q =+ n a n a n a n a n c n a 1n b Q Q Q QQ Q Q +=+ nc n a n c n b n a 1n b Q Q Q Q Q Q +=+3.列出状态转换表见题表,状态转换图如图(b)所示。

图7.2(b)表7.2状态转换表CP na nbc Q Q Q 0 0 0 0 1 0 0 1 2 0 1 0 3 0 1 1 4 1 0 0 5 1 0 16 0 0 0n4.由FF a 、FF b 和FF c 构成的是六进制的计数器。

【7-3】在二进制异步计数器中,请将正确的进位端或借位端(Q 或Q )填入下表解:题表7-3下降沿触发 由 Q 端引出进位 由Q 端引出借位触发方式 加法计数器 减法计数器上升沿触发 由Q 端引出进位 由Q 端引出借位【7-4】电路如图(a)所示,假设初始状态Q 2Q 1Q 0=000。

数字电路第8章存储器

说,它的存储容量为2 n×m位。

存储器的容量=字数×位数 或门阵列来实现。

ROM的容量由

JHR

数字电路第8章存储器

2. 4×4ROM的电路结构和简化框图

JHR

数字电路第8章存储器

JHR

数字电路第8章存储器

单位有位、字节、字、字长等的基本概念。

(1)位

计算机系统中,一个二进制的取值单位称为 二进制位,简称“位”,用b表示(bit的缩写),是表 示信息的最小单位。

JHR

数字电路第8章存储器

(2)字节

通常将8个二进制位称为一个字节,即连续8个 比特,就是一个字节。简称B(Byte的缩写),是 表示的基本单元。在微型计算机中,往往以字节 为单位来表示文件或数据的长度以及存储器容量 的大小。除此之外,还可用K,M,G或T为单位。 例如,一台电脑的内存是128兆字节,就是说这台 电脑有128个百万字节的内存。

3. 4×4ROM电路的工作原理

(1)当使能控制S=1时,A0、A1在“00~11”中 取值,W0~W3中必有一根被选中为“1”。此时,若 位线与该字线交叉点上跨接有二极管,则该二极管 导通,使相应的位线输出为“1”;若位线与字线交叉 点无二极管,则相应的位线输出为“0”。

存储器(Memory ):是数字系统中记忆大量 信息的部件。

存储器的功能:是存放不同程序的操作指令及 各种需要计算、处理的数据,所以它相当于系统存 储信息的仓库。

典型的存储器:由数以千万计的有记忆功能的 存储单元组成,每个存储单元可存放一位二进制数 码和信息。

随着大规模集成电路制作技术的发展,半导体 存储器因其集成度高、体积小、速度快,目前广泛 应用于各种数字系统中。

随机存储器RAM和顺序存储器

自动化学院应用电子教学中心

12

图8.2.9 Flotox管结构图和符号

图8.2.12 闪烁存储器中叠栅 MOS管的结构图和符号

Flotox 管与 SIMOS 管相 似,也是 N 沟道增强型 MOS 管 ,具有隧道效 应。

闪烁存储器由闪烁叠栅 MOS 管 构成,结构与 SIMOS 管相似, 区别在于浮置栅与衬底间氧化层 的厚度不同, EPROM 中的氧化 层厚度一般为 30 ~ 40nm ,而在 闪烁存储器中仅为 10 ~ 15nm 。 功耗低、擦写便捷。

VDD 字线

T

熔丝F 位线 数据线 R D

熔丝的通断状态与是否通电 无关,因为正常工作电压远低 图8.2.5 PROM的基本存储单元 于编程电压。

自动化学院应用电子教学中心 10

8.2.4可擦除的可编程只读存储器

根据擦除手段和条件的不同, EPROM 又可分 为 UVEPROM 、 E2PROM 和 Flash 三 种 , 其 中 UVEPROM常简称为EPROM。

解:(1)

写出各函数的标准与或表达式,按A、B、C、

D顺序排列变量,将Y1、Y2扩展成为四变量逻辑函数。则最 小项表达式为:

Y1 m(2, 3, 4, 5, 8, 9, 14, 15 )

Y2 m(6, 7, 10, 11 , 14, 15 )

脉冲与数字电路第八章 存储器与可编程逻辑器件

阵。

为 了存 取方便 , 给 它们编上号。

32 行 编 号 为 X0 、

X1、…、X31, 32 列 编 号 为 Y0 、

Y1、…、Y31。

这 样每 一个存 储 单 元都有了一个固

定的编号,称为

地址。

2 .地址译码器 —— 将寄存器 地址所对应的二进制数译 成有效的行选信号和列选 信号,从而选中该存储单 元。

8.2 随机存取存储器(RAM)

一. RAM的基本结构

由存储矩阵、地址译码器、读写控制器、输入/输出控制、 片选控制等几部分组成。

地 址 码 输 入 片选 读 /写 控 制 输 入 /输 出 地 址 译 码 器

存 储矩 阵

读 /写 控 制器

1. 存储矩阵

图 中 , 1024 个 字 排 列成 32×32 的矩

1.位扩展

三. RAM的容量扩展

用8片1024(1K)×1位RAM构成的1024×8位RAM系统。

I/O 0 I/O 1024×1R AM A0 A1 A0 A1 A9 R /W CS I/O1 I/O 1024×1R AM A0 A1 I/O7

... A

9

R /WC S

... A

...

I/O 1024×1R AM A0 A 1

tW C

ADD CS

写入单元的地址

R/W

t AS

tW P t

WR

I/O

写入数据

t DW t DH

读出操作过程如下: (1)欲写入单元的地址加到存储器的地址输入端; (2)加入有效的选片信号CS; (3)将待写入的数据加到数据输入端。 (3)在 线上加低电平,进入写工作状态; (4)让选片信号CS无效,I/O端呈高阻态。

数字电子技术第8章存储器与可编程逻辑器件习题及答案

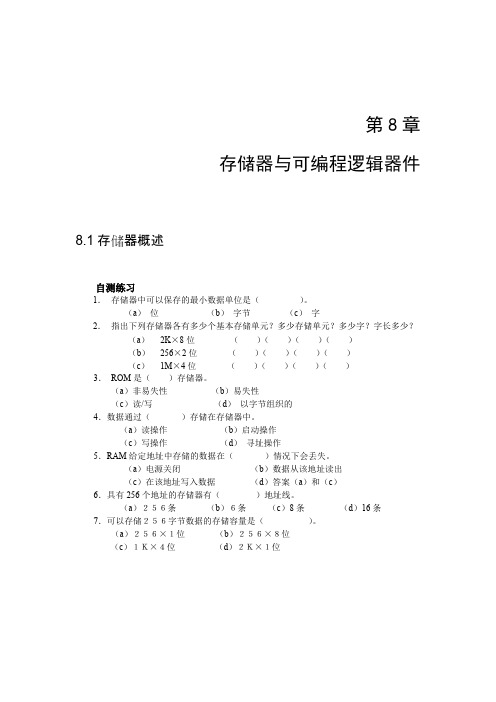

第8章存储器与可编程逻辑器件8.1存储器概述自测练习1.存储器中可以保存的最小数据单位是()。

(a)位(b)字节(c)字2.指出下列存储器各有多少个基本存储单元?多少存储单元?多少字?字长多少?(a) 2K×8位()()()()(b) 256×2位()()()()(c) 1M×4位()()()()3.ROM是()存储器。

(a)非易失性(b)易失性(c)读/写(d)以字节组织的4.数据通过()存储在存储器中。

(a)读操作(b)启动操作(c)写操作(d)寻址操作5.RAM给定地址中存储的数据在()情况下会丢失。

(a)电源关闭(b)数据从该地址读出(c)在该地址写入数据(d)答案(a)和(c)6.具有256个地址的存储器有( )地址线。

(a)256条(b)6条(c)8条(d)16条7.可以存储256字节数据的存储容量是( )。

(a)256×1位(b)256×8位(c)1K×4位 (d)2K×1位答案:1.a2.(a)2048×8;2048;2048;8(b)512;256;256;2(c)1024×1024×4;1024×1024;1024×1024;43.a4.c5.d6.c7.b8.2随机存取存储器(RAM)自测练习1.动态存储器(DRAM)存储单元是利用()存储信息的,静态存储器(SRAM)存储单元是利用()存储信息的。

2.为了不丢失信息,DRAM必须定期进行()操作。

3.半导体存储器按读、写功能可分成()和()两大类。

4.RAM电路通常由()、()和()三部分组成。

5.6116RAM有()根地址线,()根数据线,其存储容量为()位。

答案:1.栅极电容,触发器2.刷新3.只读存储器,读/写存储器4.地址译码,存储矩阵,读/写控制电路5.11,8,2K×8位8.3 只读存储器(ROM)自测练习1.ROM可分为()、()、()和()几种类型。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

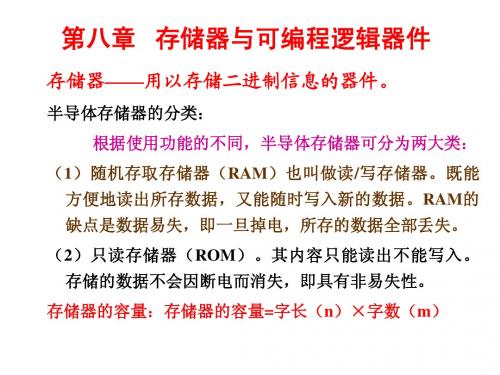

【本章讲授主要内容】

1.存储器的概念 2.只读存储器(ROM) 3.可编程序逻辑阵列(PLA) 4.随机存取存储器(RAM) 【本章重点难点】

1.重点:RAM存储器的工作原理、扩展, ROM的工作原理以及存储器版

1

第一节 存储器的概念 一、存储器的定义

存储器(Memory ):是数字系统中记忆大量 信息的部件。

存储器的功能:是存放不同程序的操作指令及 各种需要计算、处理的数据,所以它相当于系统存 储信息的仓库。

典型的存储器:由数以千万计的有记忆功能的 存储单元组成,每个存储单元可存放一位二进制数 码和信息。

随着大规模集成电路制作技术的发展,半导体 存储器因其集成度高、体积小、速度快,目前广泛 应用于各种数字系统中。

(1)位

计算机系统中,一个二进制的取值单位称为 二进制位,简称“位”,用b表示(bit的缩写),是 表示信息的最小单位。

JHR

可编辑版

6

(2)字节

通常将8个二进制位称为一个字节,即连续8个 比特,就是一个字节。简称B(Byte的缩写),是 表示的基本单元。在微型计算机中,往往以字节 为单位来表示文件或数据的长度以及存储器容量 的大小。除此之外,还可用K,M,G或T为单位。 例如,一台电脑的内存是128兆字节,就是说这台 电脑有128个百万字节的内存。

2. 内存储器(主存储器)

内存储器是数据和代码的临时存放设备,存放 输入/输出数据以及CPU进行计算、处理的数据。

JHR

可编辑版

10

内存储器可分为RAM(Random Access Memory ,随 机存储器)和ROM(Read Only Memory ,只读存储 器)。目前,内存储器一般为半导体存储器。

(1)随机存储器RAM

RAM的特点是可读可写,但关机后存储的信 息将自动消失。RAM又分为动态存储器DRAM (Dynamic Random Access Memory )和静态存储器 SRAM(Static Random Access Memory )。

JHR

可编辑版

11

◆动态存储器DRAM DRAM主要用于主存储器(俗称内存条)的制造。 ◆静态存储器SRAM

JHR

可编辑版

2

二、存储器的分类 从信息的存取情况来分,可分为:

存储器(Memory)

随机存取存储器(RAM) Random Access Memory

只读存储器(ROM) Read Only Memory

JHR

可编辑版

3

1.随机存取存储器(RAM) 在操作过程中能任意“读取”某个单元信息,

或在某个单元“写入”需存储的信息,常称为“读 写存储器”。

JHR

可编辑版

13

3.外存储器

外存储器与内存储器相比,存储容量大,可 靠性高,价格低,在脱机情况下可永久保存信息。 但速度较内存储器慢得多,它属外部设备。

主要有:软盘存储器、硬盘、光盘等。

JHR

可编辑版

14

第二节 只读存储器(ROM)

只读存储器(ROM)中的信息一旦写入,在正常 工作时,只能读出信息而不能修改,其所存信息在 断电后仍能保持,常用于存放固定的信息。

个基本存储电路的位线(D0~Dm-1),即可读出存 储单元的内容。对于有n位地址和m位字长的ROM来

说,它的存储容量为2 n×m位。

存储器的容量=字数×位数 或门阵列来实现。

ROM的容量由

JHR

可编辑版

17

2. 4×4ROM的电路结构和简化框图

JHR

可编辑版

18

JHR

可编辑版

19

3. 4×4ROM电路的工作原理

JHR

可编辑版

7

1KB=210B=1024B 1MB=1024KB 1GB=1024MB 1TB=1024MB

如IBM-PC各微型机的基本内存空间是640KB。 常用的3.5HD软盘容量是1.44MB,硬盘容量有 1GB、4GB、6GB、10GB、20GB、30GB、40GB、 80GB等。

JHR

可编辑版

8

(3)字

计算机在执行存储、传送等操作时,作为一 个整体单位进行操作的一组二进制,称为一个 计算机字,简称字。计算机的存储器中,每个 单元通常存储一个字,因此,每个字都是可以 寻址的。

JHR

可编辑版

9

(4)字长

每个字所包含的位数称为字长。由于字长是计 算机一次可处理的二进制数的位数,所以,它与计 算机处理数据的速率有关,是衡量计算机性能的一 个重要因素。如,APPLEII等微型机的字长是8位, 称为8位机,IBM-PC/AT微机是16位机,486、 586微型机是32位机等。一般计算机的字长越大,其 性能越高。

(1)当使能控制S=1时,A0、A1在“00~11” 中取值,W0~W3中必有一根被选中为“1”。此时, 若位线与该字线交叉点上跨接有二极管,则该二极

管导通,使相应的位线输出为“1”;若位线与字线 交叉点无二极管,则相应的位线输出为“0”。

SRAM主要用于高速缓存,其存取速度比 DRAM分快得多。

JHR

可编辑版

12

(2)只读存储器ROM

ROM中通常用来存放一些不能改写而用于管理 机器本身的监控程序和其它基本的服务程序。它存 储的信息一般由厂商在制造时写入的。如主板上用 以存储基本输入输出系统——BIOS的ROM。 (BIOS是电脑基本输入输出系统),在开机时, CPU首先执行ROM BIOS中的指令来搜索磁盘上的 操作系统文件。早期的ROM不能改写,随着科学技 术的发展,ROM中的数据已经可以更新。

一、功能与结构

JHR

可编辑版

15

JHR

可编辑版

16

1.只读存储器(ROM)的结构

ROM的一般结构,它由地址译码器、存储矩阵

和读出电路三部分组成。图中n位地址(A0~An-1) 经译码器译出后使2n字线

(W0~ W 2n 1 )中的一条有效,从而在存储矩阵2n 个存储单元中选中其中之一。通过被选通单元的m

2.只读存储器(ROM) 在正常工作时,它存储的数据固定不变,存储器

的数据只能读出,不能写入。要在存储器中存入数 据,须具备特定的条件。

JHR

可编辑版

4

JHR

可编辑版

5

三、计算机中信息的表示方法

1.信息单位

计算机系统中,对信息表示的

单位有位、字节、字、字长等,它们是用来表示信

息的量的大小以及信息存储传输方式的基本概念。