电网络分析与综合实验报告(一)

计算机网络综合试验选做

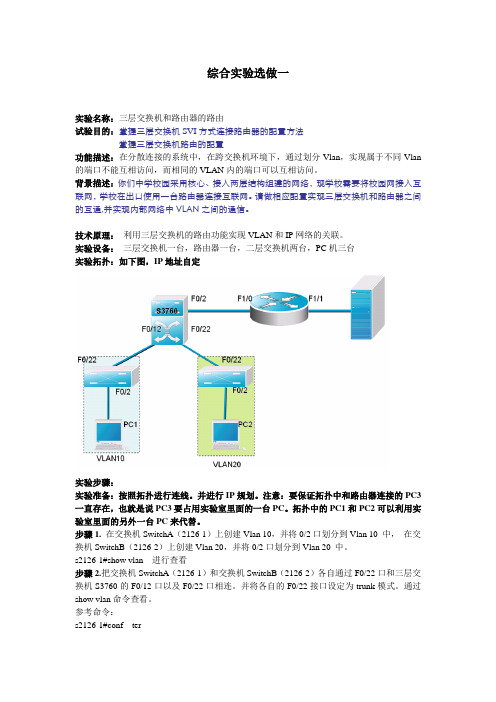

综合实验选做一实验名称:三层交换机和路由器的路由试验目的:掌握三层交换机S V I方式连接路由器的配置方法掌握三层交换机路由的配置功能描述:在分散连接的系统中,在跨交换机环境下,通过划分Vlan,实现属于不同Vlan 的端口不能互相访问,而相同的VLAN内的端口可以互相访问。

背景描述:你们中学校园采用核心、接入两层结构组建的网络,现学校需要将校园网接入互联网,学校在出口使用一台路由器连接互联网。

请做相应配置实现三层交换机和路由器之间的互通,并实现内部网络中V L A N之间的通信。

技术原理:利用三层交换机的路由功能实现VLAN和IP网络的关联。

实验设备:三层交换机一台,路由器一台,二层交换机两台,PC机三台实验拓扑:如下图,IP地址自定实验步骤:实验准备:按照拓扑进行连线。

并进行IP规划。

注意:要保证拓扑中和路由器连接的PC3一直存在,也就是说PC3要占用实验室里面的一台PC。

拓扑中的PC1和PC2可以利用实验室里面的另外一台PC来代替。

步骤1.在交换机SwitchA(2126-1)上创建Vlan 10,并将0/2口划分到Vlan 10 中,在交换机SwitchB(2126-2)上创建Vlan 20,并将0/2口划分到Vlan 20 中。

s2126-1#show vlan 进行查看步骤2.把交换机SwitchA(2126-1)和交换机SwitchB(2126-2)各自通过F0/22口和三层交换机S3760的F0/12口以及F0/22口相连。

并将各自的F0/22接口设定为trunk模式。

通过show vlan命令查看。

参考命令:s2126-1#conf ters2126-1(config)#interface fastethernet0/22s2126-1(config-if)#switch mode trunk步骤3.在三层交换机3760上创建VLAN 10和VLAN 20 和VLAN 30。

将与二层交换机相连接的F0/22和F0/12口,设为trunk模式。

实验报告一 L、C元件上电流电压的相位关系

四川大学网络教育学院实验报告实验名称: 电工电子综合实践9001学习中心万州奥鹏中心姓名刘德春学号************实验内容:一、L、C元件上电流电压的相位关系二、虚拟一阶RC电路三、用数字电桥测交流参数.四、算术运算电路五、计数器六、触发器实验报告一L、C元件上电流电压的相位关系院校:四川大学电气信息学院专业:电气工程及其自动化实验人:刘德春,同组人:戴晓冬时间:2010年2月6日一、实验目的1、在正弦电压激励下研究L、C元件上电流,电压的大小和它们的相位关系,以及输入信号的频率对它们的影响。

2、学习示波器、函数发生器以及数字相位仪的使用二、仪器仪表目录1、交流电流表、交流电压表2、数字相位计三、实验线路、实验原理和操作步骤操作步骤:1、调节ZH-12实验台上的交流电源,使其输出交流电源电压值为220V。

2、按电路图接线,先自行检查接线是否正确,并经教师检查无误后通电3、用示波器观察电感两端电压u L和电阻两端u R的波形,由于电阻上电压与电流同相位,因此从观察相位的角度出发,电阻上电压的波形与电流的波形是相同的,而在数值上要除以“R”。

仔细调节示波器,观察屏幕上显示的波形,并将结果记录操作步骤:1、调节ZH-12实验台上的交流电源,使其输出交流电源电压值为24V。

2、按图电路图接线,先自行检查接线是否正确,并经教师检查无误后通电。

3、用示波器的观察电容两端电压u C和电阻两端电压u R的波形,(原理同上)。

仔细调节示波器,观察屏幕上显示的波形四、实验结果:1、在电感电路中,电感元件电流强度跟电压成正比,即I∝U.用1/(X L)作为比例恒量,写成等式,就得到I=U/(X L)这就是纯电感电路中欧姆定律的表达式。

电压超前电路90°。

分析:当交流电通过线圈时,在线圈中产生感应电动势。

根据电磁感应定律,感应电动势为die L dt=-(负号说明自感电动势的实际方向总是阻碍电流的变化)。

网络系统集成与实践实验报告

实验一路由器交换机综合实验一一、实验目的:掌握NetSim模拟器的安装配置掌握交换机的工作原理以及交换机各项基本配置。

二、实验内容及测试结果:您设计的拓扑图:测试结果:三、算法或核心技术思考体会:在实验的过程中,让我体会到了,不仅仅要熟悉掌握命令,更重要的是在实验的过程中,必须要小心在小心和谨慎在谨慎,必须要注意配置的模式,,不论在其中的任何一个环节脱轨,就意味着你必须重新配置,一个不小心导致的是全部的重新开始,也许造成的就不是重新开始这样的小事故,所以我们必须在学习和工作的时候,打起精神,一定要认真仔细,有耐性。

在实验的时候,应该先分析实训题目,看清楚实训要求,比如,第一个项目要求R1,R2,由于我的不细心没认真审题没有把路由器名字改为R1,R2,导致从做一遍,这就是教训。

四、附件(源代码)(可选)conftRouter(config)#hostnameR1R1(config)#interfacee0R1(config-if)#ipaddressR1(config-if)#ipnatinsideR1(config-if)#noshutdownR1(config-if)#interfaces0R1(config-if)#ipaddressR1(config-if)#clockrate64000R1(config-if)#ipnatoutsideR1(config-if)#noshutdownR1(config-if)#exit实验二路由器交换机综合实验二一、实验目的:掌握NetSim模拟器的使用掌握复杂情况下路由器、交换机的配置。

二、实验内容及测试结果:您设计的拓扑图:测试结果:三、算法或核心技术思考体会:是把自己的配置方法写下来还把拓扑图画下来按题的要求标记好尽可能的不出不必要的错误,按着分析和要求去配置,按着分析和要求去配置时,特别要注意的是每个IP地址配置后要激活才可以生效按着正确的方法和步骤去配置,细心的执行每一个命令,就可以减少因为粗心带来的不必要的麻烦。

电网络分析与综合

《电网络分析与综合》首先电网络理论是研究电网络(即电路)的基本规律及其分析计算方法的科学,是电工和电子科学与技术的重要理论基础。

“网络分析”与“网络综合”是电网络理论包含的两大主要部分。

本书共十章,第一至六章主要内容为网络分析,第七至十章主要内容为网络综合。

网络分析部分在大学本科电路原理课程的基础上,进一步深入研究电路的基本规律和分析计算方法。

其中,第一章(网络元件和网络的基本性质)包含电网络理论的基本概念与基本定义,是全书的理论基础。

第二、三、四、五章(网络图论和网络方程、网络函数、网络分析的状态变量法、线性网络的信号流图分析法)介绍现代电网络理论中的几类分析电网络的方法。

第六章(灵敏度分析)研究评价电路质量的一个重要性能指标——灵敏度的分析计算方法,为电网络的综合与设计提供必要的工具。

在网络综合部分,除介绍网络综合的基础知识、无源滤波器和有源滤波器综合的基本步骤外,侧重研究得到广泛应用的无源滤波器和有源滤波器的综合方法。

其中,第七、八章(无源网络综合基础、滤波器逼近方法)的内容是进行电网络综合所必须具备的基础知识。

第九章(电抗梯形滤波器综合)对无源LC梯形滤波器的综合方法做了详细介绍。

因为这种滤波器不仅具有优良性能、得到广泛应用,而且在有源RC滤波器以及SC滤波器、SI滤波器等现代滤波器设计中,常以其作为原型滤波器。

第十章(有源滤波器综合基础)在综述有源滤波器基本知识的基础上,介绍几类常用的高阶有源滤波器综合方法。

其中,比较深入地研究了用对无源LC梯形的运算模拟法综合有源滤波器的方法。

第一章主要论述网络的基本元件以及网络和网络与安杰的基本性质。

实际的电路有电气装置、器件连接而成。

在电网络理论中所研究的电路则是实际电路的数学模型,他的基本构造单元时电路元件。

每一个电路元件集中地表征电气装置电磁过程某一方面的性能,用反映这一性能的各变量间关系的方程表示。

电网络的基本变量是电流i、电压u、电荷q、磁通Φ,它们分别对应于电磁场的表征量磁场强度H、电场强度E、电位移D和磁感应强度B。

计算机网络综合实验报告参考5篇

计算机网络综合实验报告参考5篇计算机网络综合实验报告参考 (1) ××大学校园网解决方案一、需求分析建设一个以办公自动化、计算机辅助教学、现代计算机校园文化为核心,以现代网络技术为依托,技术先进、扩展性强、能覆盖全校主要楼宇的校园主干网络,将学校的各种pc机、工作站、终端设备和局域网连接起来,并与有关广域网相连,在网上宣传自己和获取Internet网上的教育资源。

形成结构合理,内外沟通的校园计算机系统,在此基础上建立满足教学、研究和管理工作需要的软硬件环境,开发各类信息库和应用系统,为学校各类人员提供充分的网络信息服务。

系统总体设计将本着总体规划、分步实施的原则,充分体现系统的技术先进性、高度的安全可靠性,同时具有良好的开放性、可扩展性、冗余性。

本着为学校着想,合理使用建设资金,使系统经济可行。

具体包括下以几个方面:1、内网络能够高速访问FTP服务器现在或上传文件实现资源共享功能,实现对不同类型的用户划分不同的权限,限制不同类型的用户只能访问特定的服务资源。

可以下载和上传资料文件,访问速度可以对指定的用户进行级别的划分。

2、建设Web服务器对外实现信息发布,对内实现教学教务管理。

网站发布学校新闻、通知、学校的活动等相关内容。

实现学生能够在网上进行成绩查询、网上报名、网上评教等功能;以及教师的信息查询、教学数据上传等。

3、建设邮件服务器以满足校园内部之间和内、外网这间的大量邮件传输的需求。

4、实现内网划分多个VLAN,实现校园内不同校区,不同楼宇,不同楼层的多客户接入。

5、内部实现PC间实现高速互访,同时可以访问互联网。

网络内同一IP段内的PC机可以通过网上邻居实现高速互访,传送资料文件等,解决不同楼宇,不同楼层之间通过移动存储设备传送数据费时、费力的问题。

6、内部用户的QoS管理,实现用户的分级管理功能,对用户下载和上传做相应的带宽限制。

对校园网络中的流量实现有效控制,对校园内的重要数据量可靠、稳定的传输如:语音、视频会议等的延迟和阻塞的敏感。

网络工程专业综合实践报告

竭诚为您提供优质文档/双击可除网络工程专业综合实践报告篇一:网路工程专业综合实验报告专业综合实验报告课程名称:专业综合实验课题名称:校园网—接入层和汇聚层姓名:班级:带教老师:报告日期:20XX.12.9--20XX.12.13电子信息学院目录一、综合实验的目的和意义 (4)二、综合实验的内容 (5)2.1校园网需求分析...........................................................................52.2校园网规划................................................. ....................................72.3网络技术指导与测试分析................................................. ...........9三、综合实验的步骤与方法.. (17)3.1项目需求分析................................................. ............................173.2制定网络工程项目实施目标方案.............................................17四、综合实验的要点.....................................18五、小组分工...........................................19六、结果分析与实验体会..................................19七、问题.. (20)参考文献 (21)前言通过专业综合实验,使学生在掌握了网络工程专业的理论知识和实践知识的前提下,能够完成从网络设备的选型、配置、设计、施工、组建,到测试、管理、维护、应用、开发等一系列贯穿网络工程全过程所有实验任务。

网络综合布线实验报告

桂林航天工业学院电子工程系网络综合布线课程实验报告2013-----2014学年第一学期专业: 电子信息工程技术班级: 二班学号: 13 姓名: 毛安镇同组者:指导教师: 崔艳玲任务一建筑物基本情况与用户需求调查实践一、目的与要求通过实训掌握综合布线总体方案和各子系统的设计方法,熟悉一种施工图的绘制方法(AUTOCAD 或VISIO ),掌握设备材料预算方法、工程费用计算方法。

设计内容符合国家《建筑与建筑群综合布线系统工程设计规范GBT-T-50311-2000 》以桂林航专2号实验楼为综合布线工程的设计目标,通过设计,掌握综合布线总体方案和各子系统的设计方法,熟悉一种施工图的绘制方法(AUTOCAD 或VISIO ),掌握设备材料预算方法、工程费用计算方法。

二、实验内容通过对桂林航专2号实验楼的实地测量和考察,完成下列任务:1、工程概况现场考察,画出项目建筑三视图、平面图(标注尺寸)三、实验步骤1 )、现场勘测大楼,从用户处获取用户需求和建筑结构图等资料,掌握大楼建筑结构;2)、用绘图软件绘制各层平面图和建筑物俯视图。

四、实验结果如图一五、实验心得体会:四、实验结果任务二绘图软件应用基础一、目的与要求1、练习绘图软件的使用2、学习用VISO软件绘制一个简单的楼层平面图、建筑物基本情况三视图二、实验内容通过对桂林航专2号实验楼的实地测量和考察,完成下列任务:1、工程概况现场考察,用绘图软件画出项目建筑俯视图、平面图(标注尺寸)2、用户需求分析:记录每个房间的用途,并通过实验室功能进行用户需求估算三、实验步骤1、根据对建筑物内个房间的调查,列出实验楼系统信息点详细分布情况表2、根据建筑结构图和用户需求绘制综合布线路由图,信息点分布图。

四、实验结果记录(用软件绘制的各平面图用于平面子系统设计,与各组的设计方案合并装订,实验楼信息点分布表记录于下表)五、实验心得体会:(在本页背面手写)任务三综合布线材料设备预算与设计方案文档制定一、目的与要求1、掌握综合布线投标文件的技术方案设计与文档制定二、实验内容通过对桂林航专2号实验楼的实地测量和考察,完成下列任务:1、2、用户需求分析:记录每个房间的用途,并通过实验室功能进行用户需求估算三、实验步骤1、综合布线材料设备预算。

电网络分析与综合学习报告 (1)

基本回路的方向规定为所含连支的方向。

2.2独立的基尔霍夫定律方程

割集:

割集:

割集:

注意:1、2、3为树枝

推广为一般情况:基本割集的基尔霍夫电流定律方程是一组独立方程,方程的数目等于树支数,基本割集是一组独立割集。

电网络理论读书报告

电网络理论主要包括:网络分析、网络综合、模拟电路故障诊断。其中网络分析主要是一致网络结构、网络参数和输入求输出,网络综合主要是已知网络输入和输出去确定网络的结构与参数,模拟电路故障分析是已知网络的输入和输出确定网络结构参数与故障分析。

第一章网络原件和网络的基本性质

1.1实际电路与电路模型

理想变压器:

阻抗匹配:

1.6网络的基本性质

线性和非线性

线性特性指均匀性,叠加性。

均匀性(齐次性):

叠加性:

时变与时不变

一个网络在零初始条件下,其输出响应与输入信号施加于网络的时间起点无关,称为非时变网络,否则称为时变网络。

因果与非因果

因果网络当且仅当输入信号激励时,才会出现输出(响应)。也就是说,因果网络的(响应)不会出现在输入信号激励的以前时刻。也叫做非超前网络。

割集:是一组支路集合。并且满足:

(1)如果移去包含在此集合中的全部支路,则此图变成两个分离的部分;

(2)如果留下该集合中的任一支路,则剩下的图仍是连通的。

基本割集(fundamental cut-set):由数的一条树支与相应的一组连支所构成的割集,称为基本割集。

基本割集的方向规定为所含树支的方向。

电网络理论是建立在电路模型基础上的一门科学,它所研究的直接对象不是实际电路,而是实际电路的模型。实际电路:为了某种目的,把电器件按照一定方式连接起来构成的整体。电路模型:实际电路的科学抽象,由理想化的网络原件连接而成的整体。器件:客观存在的物理实体,是实际电路的组成单元。元件:理想化的模型,其端子上的物理量服从一定的数学规律,是网络的基本构造单元。

电子实验报告分析

电子实验报告分析电子实验报告分析是对某次电子实验报告进行深入分析和总结的过程。

在分析报告时,可以从实验目的、设计方案、实施过程和结果分析等方面进行详细的讨论和评价。

首先,分析实验报告的实验目的是非常重要的。

实验报告的目的通常是明确的,它描述了实验的目标和预期结果。

在分析实验目的时,需要考虑目的是否合理、具体和可操作性。

目的是否明确有助于实验过程的顺利进行和结果的准确解读。

其次,设计方案是实验报告分析的重要部分。

设计方案描述了实验的详细步骤,包括实验所用的器材和仪器,实验操作的步骤和顺序等。

在分析设计方案时,需要考虑方案的科学性、完整性和可行性。

合理的设计方案能够确保实验过程中的准确性和可靠性。

实施过程是实验报告分析中的关键环节。

实施过程描述了实验的具体操作步骤和操作顺序。

在分析实施过程时,需要考虑操作的准确性、规范性和操作顺序的合理性。

实验操作的准确性能够保证实验结果的可靠性和有效性。

最后,结果分析是实验报告分析的最终目标。

结果分析是对实验结果的定量或定性分析,可以通过图表、数据和计算等方式进行。

在分析实验结果时,需要考虑结果的科学性、可靠性和准确性。

结果的科学性和可靠性能够为实验结论的正确性提供有力支持。

在电子实验报告分析时,还可以从实验的意义、存在的问题、改进方向等方面进行讨论和总结。

这些讨论和总结可以进一步促进实验的深入理解和探索。

总之,电子实验报告分析是对实验报告进行深入分析和评价的过程。

通过对实验目的、设计方案、实施过程和结果分析进行详细的讨论和评价,可以进一步促进实验的理解和改进。

同时,在分析实验报告时还可以从实验的意义、存在的问题和改进方向等方面进行讨论和总结,从而进一步提高实验的科学性和可靠性。

电路综合设计实验-设计实验2-实验报告

设计实验2:多功能函数信号发生器一、摘要任意波形发生器是不断发展的数字信号处理技术和大规模集成电路工艺孕育出来的一种新型测量仪器,能够满足人们对各种复杂信号或特殊信号的需求,代表了信号源的发展方向。

可编程门阵列(FPGA)具有髙集成度、髙速度、可重构等特性。

使用FPGA来开发数字电路, 可以大大缩短设计时间,减小印制电路板的面积,提高系统的可靠性和灵活性。

此次实验我们采用DEO-CV开发板,实现函数信号发生器,根据按键选择生产正弦波信号、方波信号、三角信号。

频率范围为10KHz~300KHz,频率稳定度W10-4,频率最小不进10kHz。

提供DAC0832, LM358o二、正文1.方案论证基于实验要求,我们选择了老师提供的数模转换芯片DAC0832,运算放大器LM358以及DEO-CV开发板来实现函数信号发生器。

DAC0832是基于先进CMOS/Si-Cr技术的八位乘法数模转换器,它被设计用来与8080, 8048,8085, Z80和其他的主流的微处理器进行直接交互。

一个沉积硅辂R-2R电阻梯形网络将参考电流进行分流同时为这个电路提供一个非常完美的温度期望的跟踪特性(0. 05%的全温度范围过温最大线性误差)。

该电路使用互补金属氧化物半导体电流开关和控制逻辑来实现低功率消耗和较低的输出泄露电流误差。

在一些特殊的电路系统中,一般会使用晶体管晶体管逻辑电路(TTL) 提高逻辑输入电压电平的兼容性。

另外,双缓冲区的存在允许这些DAC 数模转换器在保持一下个数字 词的同时输出一个与当时的数字词对应的电压。

DAC0830系列数模转 换器是八位可兼容微处理器为核心的DAC 数模转换器大家族的一员。

LM358是双运算放大器。

内部包括有两个独立的、高增益、内部频 率补偿的双运算放大器,适合于电源电压范围很宽的单电源使用,也 适用于双电源工作模式,在推荐的工作条件下,电源电流与电源电压 无关。

它的使用范围包括传感放大器、直流增益模块和其他所有可用 单电源供电的使用运算放大器的场合。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电网络分析与综合实验报告

电路与系统ZZH

实验一:Capture CIS软件及其电路设计方法

一、实验目的

1.学习Cadence/OrCAD软件的安装。

2.学习用Cadence/OrCAD软件进行电路原理图输入。

3.熟悉现代电路设计的软件环境,为实验二做准备。

二、实验内容

1.安装Cadence/OrCAD 10.5软件。

注意:需要设置环境变量。

2.行Capture CIS软件,进行电路原理图输入环境状态,熟悉相关菜单和按

钮的功能与使用方法。

3.建立一个设计项目(工程),设置图纸属性等。

4.以一个简单的电源设计和CCD视频信号前置放大器为例,进行电路元器件

的查找、输入、摆放和导线联接等。

(1)电源设计要求:外部输入 20V,产生放大器要求的电压。

(2)前置放大器设计要求:使用AD8099同相放大,输入CCD信号(如下

图虚线所示),去除直流后再放大一倍(如下图实线所示)。

5.修改进而创建元器件图形符号。

6.修改元器件属性。

7.进行电气设计规则检查并创建网络联接表。

三、实验要求

1.通过Internet网络查找、收集相关资料。

2.自学OrCAD Capture的相关教程或资料。

3.可以相互讨论,但最后必须独立完成。

4.写出并提交电子版实验报告。

四、实验设备

1.PC机一台,最低配置:P4

2.0GHz CPU/512M内存/80G硬盘。

2.一套Cadence/OrCAD电路设计软件。

五、实验过程:

1.实验准备,知道Cadence的安装使用。

本软件的安装求注意的是环境变

量的设置。

右击“我的电脑”→“属性”→弹出“系统属性”对话框→“高级”选项卡→“环境变量”。

弹出“环境变量”对话框。

在用户变量中选择“新建”,在下面对话框中输入变量名和变量值

变量名是“CDS_LIC_FILE”,变量值是“D:\Cadence\SPB_15.5”(变量值视具体安装路径而定)。

建立一个项目工程,设置图纸属性,准备前置放大器的电路设计实验

2.电路设计

根据要求设计总的电路图如下:

整个电路由电源电路、信号发生电路和放大电路三大部分组成。

i.电源电路:

,由于外部供电为20V的电压,而AD8099和LM675的供电电压要求为V5

这里采用MC7805C和MC7905两个稳压集成电路,分别输出+5V和-5V的电压。

ii.信号发生电路

工作原理:采用两个矩形波发生器输入不同幅度,但频率相同的信号,通过LM675集成运放组成的同相加法电路对两个信号和一个直流信号进行叠加,在电路设计时处理好同相加法电路的阻值,使输出信号达到设计的要求。

'321R

V R V V R V V R V V i c i b i a ++++=-+-+- -=⨯+V V R R R o f 1

1111 集成运放在线性放大状态下V +=V - ,且根据电路中所取阻值,V o =(V a +V b +V c ) (集成运放三个输入信号的电压波形)

(叠加后的输出电压波形)

疑惑

..:叠加后输出波形并不完全符合公式情况,理论上未能解释这个现象。

难点:本电路为了得到为达到所需波形,两个叠加电源要保证周期一样,然后再调整脉冲宽度及初始值和脉动值,使CCD信号经电路放大后的波形与所要求的波形吻合。

这个在理论上可行,本电路也是这样设计。

但是在实际的电路中如何保证两个独立的信号发生器输出频率完全一致,且初相相同。

要知道频率有一点误差,随时间推移,两信号相差越来越大,根本不能同步,也就不可能达到所要求的周期性的信号。

iii.信号放大电路

信号放大模块采用AD8099运算放大器,它是美国模拟器件公司推出一种新的高速运算放大器,它能大大降低放大器设计中两个基本的误差源(电压噪声和谐波失真)。

AD8099采用一种先进电路结构专利技术,使其满足传统运算放大器差分输入级的基本性能的同时又不牺牲其固有性能。

这使得AD8099既能提供极低的电压噪声(0.95 nV/√Hz)又能提供极低的失真(-90 dB,在10 MHz基频条件下)。

另外,这种新器件在增益为10的条件下具有1600V/ s转换速率和5 GHz 增益带宽乘积。

当增益降为2时,其转换速率为600V/ s。

AD8099采用一种优于传统放大器的先进引脚排列以提高性能和稳定性。

另外,AD8099 提供两个输出引脚以降低反馈寄生效应,这样简化了PCB布线设计并且提高了放大器的稳定性。

AD8099提供两种封装选择:一种是微小的3 mm 3 mm LFCSP封装,它能够节省PCB面积并且改善器件热特性;另一种是传统的小外形8引脚小外形集成电路(SOIC)封装。

本实验中放大电路采用figure 1.8-lead CSP(CP-8)封装,由于Cadence PSpice 中没有此器件的仿真模型,所以在ADI公司网站上下载了生产厂家所提供的PSpice仿真模型,并将其在Cadence中转化为PSpice库中的仿真模型。

操作步骤如下。

打开Cadence PSpice中的一个程序文件,程序文件的地址是“D:\Cadence\SPB_15.5\tools\pspice\modeled.exe”(路径根目录视具体安装情况而定)。

在程序窗口中打开下载的模型文件(打开类型选所有类型文件),并另存为lib类型文件.然后“文件”→“Export to Capture Part Library”

在“Creat Part for library”的对话框中导入Model Library文件(lib文件),导出Part Library。

电路组成参考ADI公司的产品技术资料提供的典型电路设计,如下图。

电压放大倍数+2,符合此实验设计要求。

实验效果:

图中绿色虚线是放大电路的上级信号电压波形,红色实线是输出电压波形。

输入信号经电容C6,滤去直流成分,通过放大电路,电压放大2倍。

六、实验小结:

通过本次实验,初步熟悉了Candence PSpice的使用,并掌握如何设计一个实际的电路。

本次实验在设计时还有不足,在设计时没有考虑元件的封装问题,比如AD8099的模型管脚编号与实际芯片不一样,虽说不影响模拟分析,但在后续PCB 设计时就存在了隐患,因此以后设计时要对元件模型封装进行设计调整。