集成电路版图基础知识练习

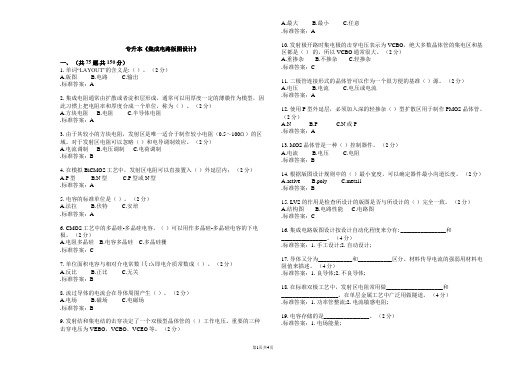

专升本《集成电路版图设计》_试卷_答案

专升本《集成电路版图设计》一、(共75题,共150分)1. 单词“LAYOUT”的含义是:()。

(2分)A.版图B.电路C.输出.标准答案:A2. 集成电阻通常由扩散或者淀积层形成,通常可以用厚度一定的薄膜作为模型,因此习惯上把电阻率和厚度合成一个单位,称为()。

(2分)A.方块电阻B.电阻C.半导体电阻.标准答案:A3. 由于其较小的方块电阻,发射区是唯一适合于制作较小电阻(0.5~100)的区域。

对于发射区电阻可以忽略()和电导调制效应。

(2分)A.电流调制B.电压调制C.电荷调制.标准答案:B4. 在模拟BiCMOS工艺中,发射区电阻可以直接置入()外延层内;(2分)A.P型B.N型C.P型或N型.标准答案:A5. 电容的标准单位是()。

(2分)A.法拉B.伏特C.安培.标准答案:A6. CMOS工艺中的多晶硅-多晶硅电容,()可以用作多晶硅-多晶硅电容的下电极。

(2分)A.电阻多晶硅B.电容多晶硅C.多晶硅栅.标准答案:C7. 单位面积电容与相对介电常数即电介质常数成()。

(2分)A.反比B.正比C.无关.标准答案:B8. 流过导体的电流会在导体周围产生()。

(2分)A.电场B.磁场C.电磁场.标准答案:B9. 发射结和集电结的击穿决定了一个双极型晶体管的()工作电压。

重要的三种击穿电压为VEBO,VCBO,VCEO等。

(2分)A.最大 B.最小 C.任意.标准答案:A10. 发射极开路时集电极的击穿电压表示为VCBO,绝大多数晶体管的集电区和基区都是()的,所以VCBO通常很大。

(2分)A.重掺杂B.不掺杂C.轻掺杂.标准答案:C11. 二极管连接形式的晶体管可以作为一个很方便的基准()源。

(2分)A.电压B.电流C.电压或电流.标准答案:A12. 使用P型外延层,必须加入深的轻掺杂()型扩散区用于制作PMOS晶体管。

(2分)A.NB.PC.N或P.标准答案:A13. MOS晶体管是一种()控制器件。

集成电路CAD期末复习题

图形转移技术 制版技术 6. 版图设计规则检查时,可以全部单元检查,也可以( 多晶硅检查 金属检查 有源区检查 区域检查 7. MOS 晶体管的( 精度 形状 间距 层次 8. 版图( 提取 仿真 测试 检查 9. 版图提取定义文件可以用来识别元件和元件( 端口 管脚 导线 电极 10. 版图设计中各图层颜色是不同的,通常兰色代表( ) 。 金属1 多晶硅 有源区 接触孔 二、判断题 11. CMOS 倒相器工作时,电路没有瞬态功耗,但存在静态功耗。 ( 是 否 12.CMOS 倒相器版图中,需要在 N 阱中放置 N 有源区的原因是将 PMOS 管的衬底接地。 ( ) 是 否 13.CMOS 倒相器版图中, 需要在 P 型衬底中部分放置 P 有源区的原因是, 与 N 阱中的 N 有源区相互对称。 ( 是 否 14.半导体掺杂的扩散工艺,通常分为预淀积和再分布两个工艺步骤,在再分布过程中,扩散层的结深会增 ) ) )的连接关系。 )是验证版图设计的主要方法。 )越大,则晶体管呈现的电阻越小。 ) 。

是 否 18. 光刻胶显影后,光照区域的光刻胶被去掉了,这个过程被称作为负胶处理。 是 否 19. 版图中的 active 是指晶体管的有源区。 是 否 20. 版图中的 poly_contact,作用是有源区与金属的接题:CMOS 倒相器版图设计

一、单选题 1. CMOS 倒相器是将 NMOS 负载倒相器进行了改进, 负载管用了 PMOS 管, 这样改进的好处是电路( 速度快 功耗低 易制造 体积小 2. PN 结二极管的电容,除了势垒电容外,还有扩散电容;对于势垒电容,PN 结二极管无论如何偏置均存 在,而对于扩散电容,则是当二极管( 零偏 反偏 正偏 任意偏置 3. CMOS 倒相器电路的所有的电接触都是在芯片的( 反面 正面 侧面 任意面 4. 如果将一个 CMOS 倒相器的 W/L 设计的越大,那么它的容性驱动能力( 越差 越好 不变 前面三个答案都不对 5. 现代集成电路制作工艺有三个主要的工艺技术, 下述工艺技术中, 不是这三个主要工艺技术的是 ( 掺杂技术 薄膜制作技术 ) 。 ) 。 )实现的。 )时存在。 )。

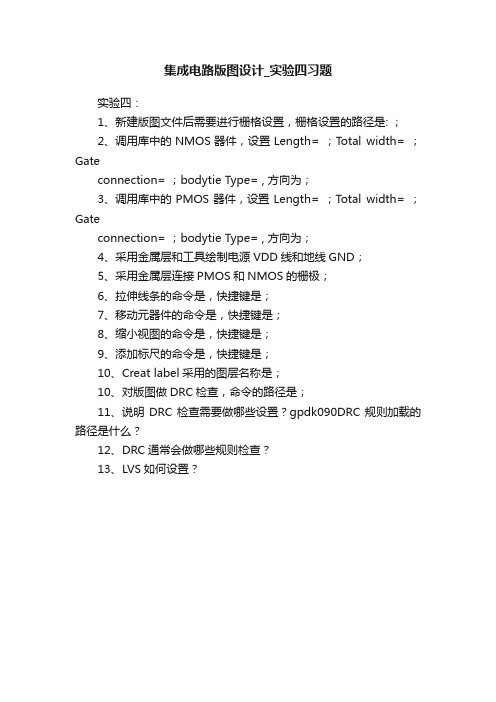

集成电路版图设计_实验四习题

集成电路版图设计_实验四习题

实验四:

1、新建版图文件后需要进行栅格设置,栅格设置的路径是: ;

2、调用库中的NMOS器件,设置Length= ;Total width= ;Gate

connection= ;bodytie Type= , 方向为;

3、调用库中的PMOS器件,设置Length= ;Total width= ;Gate

connection= ;bodytie Type= , 方向为;

4、采用金属层和工具绘制电源VDD线和地线GND;

5、采用金属层连接PMOS和NMOS的栅极;

6、拉伸线条的命令是,快捷键是;

7、移动元器件的命令是,快捷键是;

8、缩小视图的命令是,快捷键是;

9、添加标尺的命令是,快捷键是;

10、Creat label采用的图层名称是;

10、对版图做DRC检查,命令的路径是;

11、说明DRC检查需要做哪些设置?gpdk090DRC规则加载的路径是什么?

12、DRC通常会做哪些规则检查?

13、LVS如何设置?。

版图复习题-解答(1)

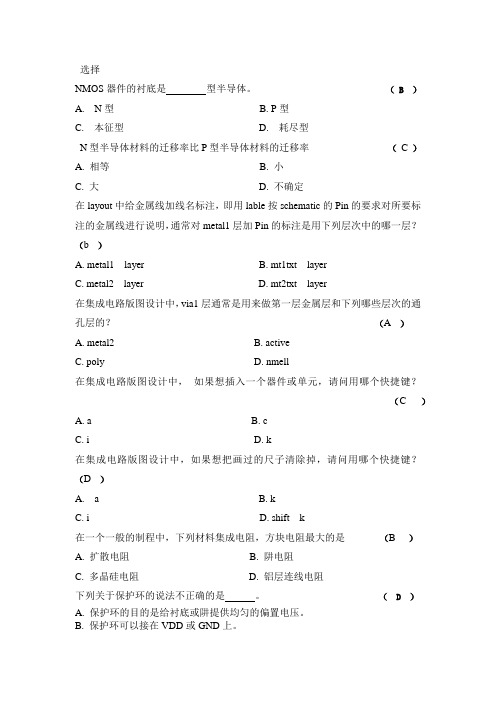

选择NMOS器件的衬底是型半导体。

( B )A. N型 B. P型C. 本征型D. 耗尽型N型半导体材料的迁移率比P型半导体材料的迁移率(C)A. 相等 B. 小C. 大D. 不确定在layout中给金属线加线名标注,即用lable按schematic的Pin的要求对所要标注的金属线进行说明,通常对metal1层加Pin的标注是用下列层次中的哪一层?(b)A. metal1 layerB. mt1txt layerC. metal2 layerD. mt2txt layer在集成电路版图设计中,via1层通常是用来做第一层金属层和下列哪些层次的通孔层的?(A)A. metal2B. activeC. polyD. nmell在集成电路版图设计中,如果想插入一个器件或单元,请问用哪个快捷键?(C)A. a B. cC. iD. k在集成电路版图设计中,如果想把画过的尺子清除掉,请问用哪个快捷键?(D)A. aB. kC. iD. shift k在一个一般的制程中,下列材料集成电阻,方块电阻最大的是(B)A. 扩散电阻 B. 阱电阻C. 多晶硅电阻D. 铝层连线电阻下列关于保护环的说法不正确的是。

( D )A. 保护环的目的是给衬底或阱提供均匀的偏置电压。

B. 保护环可以接在VDD或GND上。

C. 保护环可以减少衬底耦合噪声对敏感电路的影响。

D. 保护环无助于闩锁效应的避免。

设计模拟版图时,要考虑的问题比作数字版图多,下列哪个方面不要考虑?(a )A. 面积要小B.寄生效应(parasitics)C.对称(matching)D.噪声问题(noise issues)关于集成电路中的无源器件说法不正确的是。

( C )A. 集成电路无法高效的实现高值无源器件。

B.要精确实现某一特定阻值的电阻几乎是不可能的。

C.由于制造工艺的偏差,无源器件的比例容差(Ratio Tolerance)也必定很大。

D.尽管存在制造工艺上的偏差,但是无源器件的比例容差(Ratio Tolerance)可以控制在很小的范围内。

集成电路版图设计习题答案第九章集成电路版图设计实例

第9章集成电路版图设计实例【习题答案】1.版图设计关于数字地和模拟地的考虑事项是什么?答:一般的模拟集成电路中,通常既有数字信号又有模拟信号,数字信号和模拟信号之间容易发生干扰。

在版图设计过程中,还要考虑地噪声对电路的影响。

即在整体版图的设计中,需着重考虑电路噪声问题,按照尽量降低噪声的原则进行电路的整体布局。

首先,在总体版图的布局上,尽量将数字部分远离模拟部分,如果总体电路中模拟部分偏多,则在版图设计中将数字部分放在靠边的位置,而且把模拟部分中最容易被数字干扰的部分放到离数字部分最远的位置,同时在数字部分和模拟部分中间用接地的衬底接触来进行隔离,反之亦然。

其次,采用隔离环设计,对每个单元模块都用一层接地的衬底接触,一层接电源的N阱构成的隔离环来进行隔离。

对于整个模拟部分和数字也分别采用相同的隔离环隔离,数字电路的隔离环可以吸收数字电路的衬底噪声,从而可以减少通过衬底串扰到模拟电路的衬底噪声。

隔离环包的层数越多,理论上吸收衬底噪声效果越好。

但是要避免数字电路的p隔离环紧靠模拟电路的p型隔离环,因为在这种情况下数字地的噪声会串扰到模拟地。

从而使模拟地受到干扰。

最后,除了数字模块之外的其它单元模块尽量将距离缩短,这样一方面能尽量地减少互连线经过别的区域引入噪声,同时也能降低引线过长引起电压信号的衰减。

2.总结自己的版图设计技巧和经验。

3. 共质心MOS管设计时的注意事项是什么?答:低精度要求可采用一维共质心,高精度要求必须采用二维共质心。

共质心设计时需保证MO管的对称性和电流通路的对称性。

4. 静电保护的种类以及版图设计注意事项。

答:常用的二极管式的静电保护分为两种方式,一种是用MOS晶体管连接成二极管形式的静电保护,一种利用CMOS工艺中二极管的静电保护。

在MOS型静电保护版图设计中,主要考虑以下几点:●MOS管要分成多个管,叉指结构,以便形成多支路共同放电。

●因为放电瞬间流经MOS管的电流特别大,构成整个放电通路的任何导线的宽度一定要有足够保证,而且CMOS工艺对于每个接触孔能通过的电流密度还有要求,因此还要保证放电通路导线上孔的数目应尽量多。

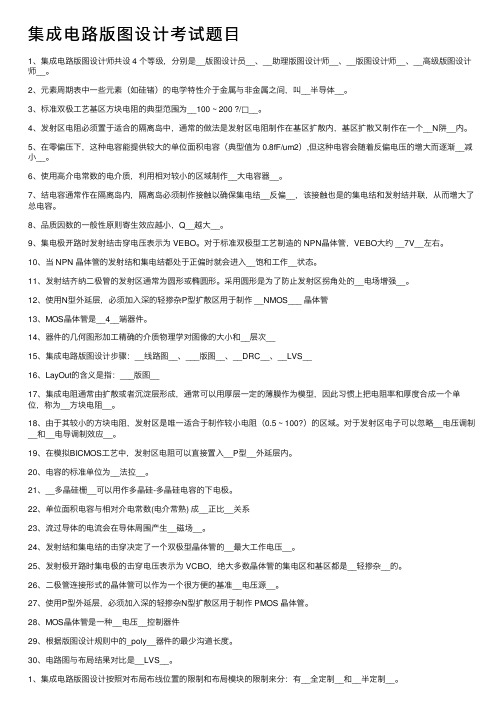

集成电路版图设计考试题目

集成电路版图设计考试题⽬1、集成电路版图设计师共设 4 个等级,分别是__版图设计员__、__助理版图设计师__、__版图设计师__、__⾼级版图设计师__。

2、元素周期表中⼀些元素(如硅锗)的电学特性介于⾦属与⾮⾦属之间,叫__半导体__。

3、标准双极⼯艺基区⽅块电阻的典型范围为__100 ~ 200 ?/□__。

4、发射区电阻必须置于适合的隔离岛中,通常的做法是发射区电阻制作在基区扩散内,基区扩散⼜制作在⼀个__N阱__内。

5、在零偏压下,这种电容能提供较⼤的单位⾯积电容(典型值为 0.8fF/um2),但这种电容会随着反偏电压的增⼤⽽逐渐__减⼩__。

6、使⽤⾼介电常数的电介质,利⽤相对较⼩的区域制作__⼤电容器__。

7、结电容通常作在隔离岛内,隔离岛必须制作接触以确保集电结__反偏__,该接触也是的集电结和发射结并联,从⽽增⼤了总电容。

8、品质因数的⼀般性原则寄⽣效应越⼩,Q__越⼤__。

9、集电极开路时发射结击穿电压表⽰为 VEBO。

对于标准双极型⼯艺制造的 NPN晶体管,VEBO⼤约 __7V__左右。

10、当 NPN 晶体管的发射结和集电结都处于正偏时就会进⼊__饱和⼯作__状态。

11、发射结齐纳⼆极管的发射区通常为圆形或椭圆形。

采⽤圆形是为了防⽌发射区拐⾓处的__电场增强__。

12、使⽤N型外延层,必须加⼊深的轻掺杂P型扩散区⽤于制作 __NMOS___ 晶体管13、MOS晶体管是__4__端器件。

14、器件的⼏何图形加⼯精确的介质物理学对图像的⼤⼩和__层次__15、集成电路版图设计步骤:__线路图__、___版图__、__DRC__、__LVS__16、LayOut的含义是指:___版图__17、集成电阻通常由扩散或者沉淀层形成,通常可以⽤厚层⼀定的薄膜作为模型,因此习惯上把电阻率和厚度合成⼀个单位,称为__⽅块电阻__。

18、由于其较⼩的⽅块电阻,发射区是唯⼀适合于制作较⼩电阻(0.5 ~ 100?)的区域。

集成电路版图设计习题答案第八章MOS场效应晶体管

集成电路版图设计习题答案第8章 MOS场效应晶体管【习题答案】1.请画出MOS晶体管的结构示意图。

答:2.请简述MOS晶体管各个版图层的作用。

●答:阱层(Well):阱层定义在衬底上制备阱的区域。

NMOS管制备在P型衬底上,PMOS管制备在N型衬底上。

一块原始的半导体材料,掺入的杂质类型只能有一种,即该衬底不是N型就是P型。

如果不对衬底进行加工处理的话,该衬底只能制备一种MOS晶体管。

CMOS集成电路是把NMOS晶体管和PMOS晶体管制备在同一个硅片衬底上,为了能够制造CMOS集成电路,需要对衬底进行处理,利用掺杂工艺在衬底上形成一个区域,该区域的掺杂类型和衬底的掺杂类型相反,这个区域就称为阱。

●有源区层(Active):有源区层的作用是在衬底上定义制作有源区的区域,该区域包括源区、漏区和沟道。

在衬底上淀积厚氧化层,利用光刻和刻蚀工艺在衬底上开窗口并把厚氧化层除去就可形成有源区,有源区之外的区域是场区。

显然,MOS管必须而且只能制备在有源区内。

●多晶硅层(Poly):多晶硅层的作用是定义制作多晶硅材料的区域。

最早的MOS集成电路制造工艺只能制备一层多晶硅,而现在已经有能够制备两层多晶硅的工艺了。

对于双层多晶硅工艺,第一层多晶硅主要用来制作栅极、导线和多晶硅—多晶硅电容的下极板,第二层多晶硅主要用来制作多晶硅电阻和多晶硅-多晶硅电容的上极板。

双层多晶硅工艺具有多晶硅1和多晶硅2这两个版图层。

●P+注入层和N+注入层(P+implant和N+ implant):P+注入层定义注入P+杂质离子的区域,而N+注入层定义注入N+杂质离子的区域。

由于NMOS晶体管和PMOS晶体管的结构相同,只是源漏区的掺杂类型相反。

同时,有源区层只是定义了源区、漏区和沟道的区域,却没有说明源区和漏区的掺杂类型。

P+注入层和N+注入层说明了注入杂质的类型,也就是说明了有源区的导电类型,实现了NMOS晶体管和PMOS晶体管的区分。

集成电路版图设计习题答案第四章电阻

第4章电阻【习题答案】1.请解释方块电阻及其使用方块电阻的意义。

答:电阻的阻值可以用方块电阻乘以方块数得到,其中方块电阻与工艺有关,可通过查工艺手册或设计手册得到。

长和宽相等的电阻包含一个方块,其电阻值为一个方块电阻;长是宽两倍的电阻包含两个方块,其电阻值为两个方块电阻。

方块电阻也称为薄层电阻。

对于相同的集成电路工艺,同一材料的方块电阻是相同的。

有了方块电阻的概念,我们就不必再考虑材料的厚度了,只需关心材料的长度和宽度就可以了。

由于版图设计是利用平面作图方法,因此只考虑长和宽对于电阻的版图设计是非常方便的。

2.集成电路中的电阻主要包括(有源电阻)和(无源电阻)。

3.集成电路中的无源电阻主要包括(多晶硅电阻)、(阱电阻)、(有源区电阻)和(金属电阻)。

4.集成电路中电阻的设计依据主要考虑(误差控制)和(电流密度)两方面。

5. 请解释集成电路中电阻的设计依据。

答:电阻的设计依据主要包括两个方面:误差控制和电流密度。

电阻的误差分析:由于制造工艺误差会导致电阻发生变化,而且总电阻应包括体区电阻、头区电阻和接触电阻。

由于芯片制造厂商能够很好地控制体电阻,而对于头区电阻和接触区电阻的控制却并不理想,因此我们希望,对于一个电阻,体电阻应该在总电阻中起到支配作用,即总电阻应远大于头区电阻和接触电阻。

如果一个电阻体材料的长度接近甚至小于头区材料长度和接触区长度,那么将很难控制该电阻的阻值。

关于电阻尺寸的经验法则为:体区材料的长度至少应为光刻和刻蚀工艺误差的100倍,宽度至少应该为光刻和刻蚀工艺的50倍。

如果需要进一步提高精度,那么长和宽还应该增加,因为线宽控制是不变的,长和宽的增加会提高精度。

电流密度也是电阻设计的一个重要依据。

在这里,电流密度指的是电阻中能够安全可靠通过的电流。

当电阻通过低于电流密度的电流时,电阻能够长期稳定地工作。

在集成电路中电阻的电流密度是比较保守的,可靠性系数通常要达到数万个小时。

有关电流密度的经验法则为:每微米宽度电阻的电流密度为0.5mA。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一、填空1.ls (填写参数)命令用于显示隐藏文件。

(-a)2.进入当前目录的父目录的命令为 (%cd ..)3.查看当前工作目录的命令为:(%pwd)4.目录/home//uuu已建立,当前工作目录为/home/,采用绝对路径进入/home//uuu的命令为:(%cd /home//uuu)5.假设对letter文件有操作权限,命令%chmod a+rw letter会产生什么结果:(对所有的用户增加读写权限。

)6.显示当前时间的命令为:(%date)7.打开系统管理窗口的命令为:(%admintool)8.与IP地址为166.111.4.80的主机建立FTP连接的命令为:(%ftp166.111.4.80 or %ftp %open 166.111.4.80)9.建立FTP连接后,接收单个文件的命令为:(%get)10.建立FTP连接后,发送多个文件的命令为:(%mput)11.有一种称为0.13um 2P5M CMOS单井工艺, 它的特征线宽为______,互连层共有_____层,其电路类型为_______。

0.13um 7 CMOS12.请根据实际的制造过程排列如下各选项的顺序:a.生成多晶硅b.确定井的位置和大小c.定义扩散区,生成源漏区d.确定有源区的位置和大小e.确定过孔位置正确的顺序为:___ _________________。

bdace13.集成电路中的电阻主要有__________, ____________, _____________三种。

井电阻,扩散电阻,多晶电阻14.为方便版图绘制,通常将Contact独立做成一个单元,并以实例的方式调用。

若该Contact单元称为P型Contact,由4个层次构成,则该四个层次分别为:_________,_________, _________, ___________. active, P+ diffusion, contact, metal.15.CMOS工艺中,之所以要将衬底或井接到电源或地上,是因为___________________________________。

报证PN结反偏,使MOS器件能够正常工作。

16.版图验证主要包括三方面:________,__________,__________; 完成该功能的Cadence工具主要有(列举出两个):_________,_________。

DRC, LVS, ERC, Diva,Dracula17.造成版图不匹配的因数主要来自两个方面:一是制造工艺引起的,另一个是__________;后者又可以进一步细分为两个方面:_______________,_____________。

片上环境波动,温度波动,电压波动。

18.DRC包括几种常见的类型,如最大面积(Maximum Dimension),最小延伸(MinimumExtension),此外还有_________,_________,_________。

最小间距,最小宽度,最小包围(Minimum Enclosure)。

19.减少天线效应的三种方法有:____________,____________,__________。

插入二极管,插入缓冲器,Jumper (或者,通过不同的金属层绕线)。

20.由于EDA工具的不统一,出现了各种不同的文件格式,如LEF, DEF等,业界公认的Tape out的文件格式为 _______,它不可以通过文本编辑器查看,因为它是______(文件类型)。

GDSII , 流文件。

21. 根据的.诺依曼的“101页报告”,计算机的五大部件是:输入装置、_________、_________、_________、输出装置。

逻辑部件、运算部件、存储器22. 流水线中可能存在三种冲突,它们是:_________、_________、_________,从而造成流水线停顿,使流水线无法达到最高性能。

资源冲突、数据冲突、控制冲突23. 写出JK 触发器的特性方程:__________________。

( )24. 随着1000M 网卡等高速设备的出现,传统的PCI 总线无法满足PC 系统的数据传输需求,INTEL 于2001年提出了第三代局部总线技术_________。

3GIO 或 PCIExpress25. AMBA 是为了设计高性能的嵌入式微控制器系统而推出的片上通信标准,它包括ASB 、_________、_________等三套总线。

AHB 、APB26. SoC 的设计基于IP Core 的复用,IP Core 包括三种:_________、_________、_________。

软核、固核、硬核27. RISC CPU 的三大特点是:_________、_________、_________。

ALU 的数据源自Register 、只用LD/ST 指令可以访问MEMORY 、指令定长28. ARM 处理器包含两种指令集:_________、_________。

Arm 指令、thumb 指令29. MCS80C51是CISC CPU ,属于哈佛结构,arm 属于_________CPU 。

RISC30. Arm7TDMI 中,T 代表_________、D 代表_________、M 代表_________、I 代表_________。

Thumbm 、debug 、multiplier 、ise31. 固体分为 晶体 和 非晶体 两大类。

32. 半导体材料中锗和硅属于 金刚石 结构,砷化镓属于 闪锌矿 结构。

33. 施主杂质电离后成为不可移动的带正电的施主离子,同时向导带提供电子,使半导体成为电子导电的n 型半导体。

受主杂离后成为不可移动的带负电的受主离子,同时向价带提供空穴.使半导体成为空穴导电的p 型半导体。

34. 晶体中电子的能量状态是量子化的。

电子在各状态上的分布遵守费米分布规律。

35. 电子在热运动时不断受到晶格振动和杂质的散射作用,因而不断地改变运动方向。

半导体中的主要散射机构是电离杂质散射和晶格振动散射。

36. pn 结有电容效应,分为势垒电容和扩散电容。

37. 在放大模式偏置下,双极型晶体管的EB 结 正向偏置,CB 结反向偏置。

38. CMOS 的英文全称是 Complementary Metal Oxide Semiconductor 。

39. MOS 场效应晶体管分为四种基本类型:N 沟增强型、N 沟耗尽型、P 沟增强型、P 沟耗尽型。

40. 衬底偏置电压会影响MOS 器件的阈值电压,反向偏置电压增大,则MOS 器件的阈值电压也随之增大,这种效应称为体效应。

41. 用Cadence 软件设计集成电路版图的输出数据的格式是(GDSII 格式)。

42. 在nwell 上画pmos 器件时需要在nwell 上加(n+接触孔),并用金属线把这个(n+接触孔)与nwell 的(最高)电位相连接。

43. 在P 型衬底上画nmos 器件时需要在P 型衬底上加(p+接触孔),并用金属线把这个(p+接触孔)与P 型衬底的(最低)电位相连接。

44. 建立一个新的layout library 时需要(Compile a new techfile ),或者(Attachedto an existing techfile ), 或(Don ’t need a techfile )。

45. 在layout 编辑命令中,Hierachy 命令一栏下,有两个相反的操作命令他们分别是 make cell 和( flatten )。

nn n Q K Q J Q +=+146.用DRACULA 做layout 的LVS检查时,首先要把schematic转成CDL 的netlist, 并对这个netlist做(LOGLVS)。

47.用DRACULA做layout 的DRC检查时,先要运行PDRACULA命令,然后再执行( jxrun.)文件。

48.用DRACULA做layout 的LVS检查时,先要运行PDRACULA命令,然后再执行( jxrun.)文件。

49.用DRACULA 做layout 的DRC检查后,修改完所有错误的标志是用vi命令在后缀名为(sum)的文件里看到ERRORS WINDOW SIZE 是(0)。

50.用DRACULA 做layout 的LVS检查后,修改完所有错误的标志是用vi命令在名为(lvspr.lvs)的文件里看到unmatching devices 是(0),以及没有(size error)的描述。

51.集成电路产业包括:IC设计、IC制造、IC封装、IC测试。

52.现代主流的集成电路加工技术为CMOS工艺,即最基本的器件是由PMOS和NMOS组成。

53.PMOS是在N阱上形成P型沟道的MOSFET晶体管。

54.对于CMOS集成电路,通常器件间的电性绝缘采用介质绝缘的方式,如LOCOS(局部场氧隔离)或STI(浅沟道隔离)。

55.集成电路制造与集成电路设计相关纽带是光刻掩膜版。

56.集成电路制造工艺技术主要包括:热工艺、离子注入、光刻、清洗与刻蚀、金属化、表面平坦化。

57.集成电路制造中最为重要的工序是光刻。

58.现在,主流的掺杂技术是离子注入。

59.光刻的图形曝光方式有:接触式曝光、接近式曝光和投影式曝光。

60.集成电路金属薄膜的沉积通常采用溅射物理气相沉积。

二、判断1.标准Solaris操作系统中,普通用户只能在自己的宿主目录下创建新的目录。

√2.Solaris是SUN公司推出的在工作站上运行的操作系统。

√3.Solaris系统只支持单用户。

×4.Solaris是多进程、多任务的分时操作系统。

√5.%ls –l 命令是连续列出文件的名称。

×6.%echo 命令是将用户在该命令之后放置的任何命令行复制到屏幕上。

√7.%id 是显示用户正在使用的计算机名称。

×hostname8.FTP是本地或者远程主机之间传输文件的工具。

√9.vi是文本编辑器。

√10.vi命令方式下,字母I是打开新行命令。

×11.过孔上往往有较大的寄生电阻,因此为了减少因此产生的IR Drop,单个过孔的面积应该尽可能的大。

×12.Bi-CMOS工艺就是用标准的Bipolar工艺来制造MOS器件。

×13.对于N型衬底的单井CMOS工艺,NMOS的衬底应该接到高电位上。

×14.尽管版图中各个层次大致对应于相应的工艺步骤,但划版图时,各个层次划的先后顺序是无关紧要的,它不会影响芯片最后的制造。

√15.在采用标准单元镜像的布图中,绕线是通过绕线通道(Routing Channel)进行的。