基于VHDL语言的EDA实验报告(附源码)

VHDL语言设计信号发生器实验报告

实验四用VHDL设计多功能信号发生器一、设计任务基于《VHDL语言》,通过给定的仪器(EDA6000试验箱)设计一个多功能信号发生器,要求:(1)能产生周期性正弦波、方波、三角波、锯齿波以及用户自己编辑的特定波形(选作);(2)输出信号的频率范围为100Hz~200KHz,且输出频率可以调节;(3)具有显示输出波形、频率的功能。

(选作)二、系统顶层框图弦波的数字幅度信息,每个查找表的地址对应正(余)弦波幅度信号,同时输出到数模转换器(DAC)输入端,DAC输出的模拟信号经过低通滤波器(LPF),可以得到一个频谱纯净的正(余)弦波。

二、设计步骤用VHDL语言结合原理图设计实现一个函数信号发生器,输出正弦波、方波和三角波三种波形。

将频率控制、分频、三角波、正弦波、方波发生邓各个模块分别用VHDL语言编程为一个子程序,并把每一个模块转换成图形文件,然后在原理图编辑框调用这些图形模块,连接电路如上图系统顶层框图所示。

通过按键1到按键8控制频率调节f〔7...0〕,用按键6、按键7、按键8控制dlt 、sin 、sqr 波形选通,最后把八位输出接DAC0832通过D/A 转换,从示波器上就能看到波形输出。

按下不同的按键输出不同的波形及频率。

三、系统设计(1)数控分频器模块在时钟的作用下,通过预置分频数DIN ,来改变输出频率。

假如分频系数为N ,波形存储模块存储一个周期的波形,实验里按照一个周期波形采样64个点存储在波形存储模块里。

则输出频率N f f clkout .64=(2).数据存储模块 (存储波形数据)数据存储模块主要存的是正弦波、三角波、锯齿波等一个周期的采样点。

三角波模块可设计一个可逆计数器实现,设计时设置一变量作为工作状态标志,在此变量为0时,当检测到时钟的上升沿进行加同一个数操作;为1时,进行减同一个数操作。

DA 转换采用的DA0832,输入有8个数据端,范围是0到255;而且设置64个时钟周期为一个三角波周期,所有每次加、减为8.锯齿波的存储数据与三角波类似。

EDA实验报告 (4)

实验四VHDL组合逻辑电路设计

一实验目的:

在学习了VHDL语言的语句,语法以及利用VHDL语言设计逻辑电路的基本方法之后,进行本次试验。

通过本次试验,使学生了解常见组合逻辑电路的VHDL描述,并且通过仿真,深入了解一种组合逻辑电路的功能和特性。

通过编辑VHDL程序熟悉VHDL 语言结构和词法元素的规则,了解常见的语法错误,学习利用QUARTUSII文本编辑器对VHDL语言程序进行编译,调试,并利用波形编辑器进行逻辑关系验证。

二实验内容:

本实验是一个设计型实验,利用所学VHDL语言,设计实现8421BCD码十进制转换。

通过本次试验,使学生能够熟练使用VHDL语言描述设计简单的组合逻辑电路。

进一步掌握VHDL描述的结构以及语法规则。

三实验仪器:

1.PC机一台

2.QUARTUSII软件

3.EDA实验箱

四实验原理:

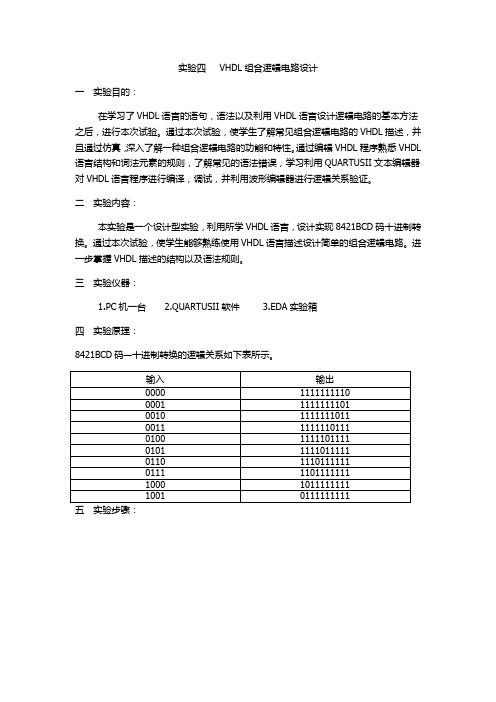

8421BCD码—十进制转换的逻辑关系如下表所示。

输入输出

0000 1111111110

0001 1111111101

0010 1111111011

0011 1111110111

0100 1111101111

0101 1111011111

0110 1110111111

0111 1101111111

1000 1011111111

1001 0111111111

五实验步骤:

1.编译得到如图4.1所示。

图4.1 2.仿真得到如4.2所示波形。

图4.2

六实验总结。

通过本次试验,加深了我对常见组合逻辑电路的VHDL描述的了解,并且通过仿真,深入了解一种组合逻辑电路的功能和特性。

EDA实验报告

实验一:QUARTUS II 软件使用及组合电路设计仿真实验目得:学习QUARTUS II 软件得使用,掌握软件工程得建立,VHDL源文件得设计与波形仿真等基本内容。

实验内容:1.四选一多路选择器得设计基本功能及原理:选择器常用于信号得切换,四选一选择器常用于信号得切换,四选一选择器可以用于4路信号得切换。

四选一选择器有四个输入端a,b,c,d,两个信号选择端s(0)与s(1)及一个信号输出端y。

当s输入不同得选择信号时,就可以使a,b,c,d中某一个相应得输入信号与输出y端接通。

逻辑符号如下:程序设计:软件编译:在编辑器中输入并保存了以上四选一选择器得VHDL源程序后就可以对它进行编译了,编译得最终目得就是为了生成可以进行仿真、定时分析及下载到可编程器件得相关文件。

仿真分析:仿真结果如下图所示分析:由仿真图可以得到以下结论:当s=0(00)时y=a;当s=1(01)时y=b;当 s=2(10)时y=c;当s=3(11)时y=d。

符合我们最开始设想得功能设计,这说明源程序正确。

2.七段译码器程序设计基本功能及原理:七段译码器就是用来显示数字得,7段数码就是纯组合电路,通常得小规模专用IC,如74或4000系列得器件只能作十进制BCD码译码,然而数字系统中得数据处理与运算都就是2进制得,所以输出表达都就是16进制得,为了满足16进制数得译码显示,最方便得方法就就是利用VHDL译码程序在FPGA或CPLD中实现。

本项实验很容易实现这一目得。

输出信号得7位分别接到数码管得7个段,本实验中用得数码管为共阳极得,接有低电平得段发亮。

数码管得图形如下七段译码器得逻辑符号:程序设计:软件编译:在编辑器中输入并保存了以上七段译码器得VHDL源程序后就可以对它进行编译了,编译得最终目得就是为了生成可以进行仿真、定时分析及下载到可编程器件得相关文件。

仿真分析:仿真结果如下图所示:分析:由仿真得结果可以得到以下结论:当a=0(0000)时led7=1000000 此时数码管显示0;当a=1(0001)时led7=1111001 此时数码管显示1;当a=2(0010)时led7=0100100此时数码管显示2;当a=3(0011)时led7=0110000此时数码管显示3;当a=4(0100)时led7=0011001此时数码管显示4; 当a=5(0101)时led7=0010010此时数码管显示5; 当a=6(0110)时led7=0000010此时数码管显示6;当a=7(0111)时led7=1111000 此时数码管显示7; 当a=8(1000)时led7=0000000 此时数码管显示8; 当a=9(1001)时led7=0010000 此时数码管显示9;当a=10(1010)时led7=0001000 此时数码管显示A;当a=11(1011)时led7=0000011 此时数码管显示B;当a=12(1100)时led7=1000110 此时数码管显示C;当a=13(1101)时led7=0100001此时数码管显示D;当a=14(1110)时led7=0000110此时数码管显示E;当a=15(1111)时led7=0001110 此时数码管显示F;这完全符合我们最开始得功能设计,所以可以说明源VHDL程序就是正确得。

EDA实验报告

实验一:QUARTUS II 软件使用及组合电路设计仿真页脚内容1实验目的:学习QUARTUS II 软件的使用,掌握软件工程的建立,VHDL源文件的设计和波形仿真等基本内容。

实验内容:1.四选一多路选择器的设计基本功能及原理:选择器常用于信号的切换,四选一选择器常用于信号的切换,四选一选择器可以用于4路信号的切换。

四选一选择器有四个输入端a,b,c,d,两个信号选择端s(0)和s(1)及一个信号输出端y。

当s输入不同的选择信号时,就可以使a,b,c,d中某一个相应的输入信号与输出y端接通。

逻辑符号如下:页脚内容2程序设计:软件编译:在编辑器中输入并保存了以上四选一选择器的VHDL源程序后就可以对它进行编译了,编译的最终目的是为了生成可以进行仿真、定时分析及下载到可编程器件的相关文件。

仿真分析:仿真结果如下图所示页脚内容3分析:由仿真图可以得到以下结论:当s=0(00)时y=a;当s=1(01)时y=b;当s=2(10)时y=c;当s=3(11)时y=d。

符合我们最开始设想的功能设计,这说明源程序正确。

2.七段译码器程序设计基本功能及原理:七段译码器是用来显示数字的,7段数码是纯组合电路,通常的小规模专用IC,如74或4000系列的器件只能作十进制BCD码译码,然而数字系统中的数据处理和运算都是2进制的,所以输出表达都是16进制的,为了满足16进制数的译码显示,最方便的方法就是利用VHDL译码程序在FPGA或CPLD 中实现。

本项实验很容易实现这一目的。

输出信号的7位分别接到数码管的7个段,本实验中用的数码管为共阳极的,接有低电平的段发亮。

数码管的图形如下页脚内容4七段译码器的逻辑符号:程序设计:页脚内容5软件编译:在编辑器中输入并保存了以上七段译码器的VHDL源程序后就可以对它进行编译了,编译的最终目的是为了生成可以进行仿真、定时分析及下载到可编程器件的相关文件。

仿真分析:仿真结果如下图所示:页脚内容6分析:由仿真的结果可以得到以下结论:当a=0(0000)时led7=1000000 此时数码管显示0;当a=1(0001)时led7=1111001 此时数码管显示1;当a=2(0010)时led7=0100100 此时数码管显示2;当a=3(0011)时led7=0110000 此时数码管显示3;当a=4(0100)时led7=0011001 此时数码管显示4;当a=5(0101)时led7=0010010 此时数码管显示5;当a=6(0110)时led7=0000010 此时数码管显示6;当a=7(0111)时led7=1111000 此时数码管显示7;当a=8(1000)时led7=0000000 此时数码管显示8;页脚内容7当a=9(1001)时led7=0010000 此时数码管显示9;当a=10(1010)时led7=0001000 此时数码管显示A;当a=11(1011)时led7=0000011 此时数码管显示B;当a=12(1100)时led7=1000110 此时数码管显示C;当a=13(1101)时led7=0100001 此时数码管显示D;当a=14(1110)时led7=0000110 此时数码管显示E;当a=15(1111)时led7=0001110 此时数码管显示F;这完全符合我们最开始的功能设计,所以可以说明源VHDL程序是正确的。

基于VHDL的交通灯设计(EDA课程设计报告)!!

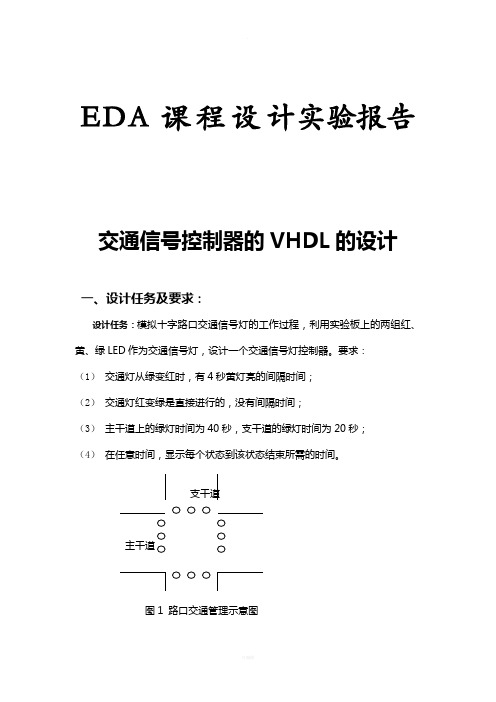

EDA课程设计实验报告交通信号控制器的VHDL的设计一、设计任务及要求:设计任务:模拟十字路口交通信号灯的工作过程,利用实验板上的两组红、黄、绿LED作为交通信号灯,设计一个交通信号灯控制器。

要求:(1)交通灯从绿变红时,有4秒黄灯亮的间隔时间;(2)交通灯红变绿是直接进行的,没有间隔时间;(3)主干道上的绿灯时间为40秒,支干道的绿灯时间为20秒;(4)在任意时间,显示每个状态到该状态结束所需的时间。

支干道主干道图1 路口交通管理示意图表1 交通信号灯的4种状态设计要求:(1)采用VHDL语言编写程序,并在QUARTUSII工具平台中进行仿真,下载到EDA实验箱进行验证。

(2)编写设计报告,要求包括方案选择、程序清单、调试过程、测试结果及心得体会。

二设计原理1、设计目的:学习DEA开发软件和QuartusII的使用方法,熟悉可编程逻辑器件的使用。

通过制作来了解交通灯控制系统,交通灯控制系统主要是实现城市十字交叉路口红绿灯的控制2’设计说明(1)第一模块:clk时钟秒脉冲发生电路在红绿灯交通信号系统中,大多数情况是通过自动控制的方式指挥交通的。

因此为了避免意外事件的发生,电路必须给一个稳定的时钟(clock)才能让系统正常运作。

模块说明:系统输入信号:Clk: 由外接信号发生器提供256的时钟信号;系统输出信号:full:产生每秒一个脉冲的信号;(2)第二模块:计数秒数选择电路计数电路最主要的功能就是记数负责显示倒数的计数值,对下一个模块提供状态转换信号。

模块说明:系统输入:full: 接收由clk电路的提供的1hz的时钟脉冲信号;系统输出信号:tm:产生显示电路状态转换信号tl:倒计数值秒数个位变化控制信号th:倒计数值秒数十位变化控制信号(3)第三模块:红绿灯状态转换电路本电路负责红绿灯的转换。

模块说明:系统输入信号:full: 接收由clk电路的提供的1hz的时钟脉冲信号;tm: 接收计数秒数选择电路状态转换信号;系统输出信号:comb_out: 负责红绿灯的状态显示。

基于VHDL语言的EDA设计——交通灯功能设计

北京XX大学《数字电路逻辑设计》实训报告基于VHDL语言的EDA设计——交通灯控制系统课程名称:数字电路逻辑设计课程实训学院:信息学院专业:电子信息工程姓名:班级:200908030301学号:2009080303132 2009080303101指导教师:成绩:2011年12 月22日目录目录 ................................................................................................................................................ - 1 - 概述 .. (1)第一章交通灯控制系统工程设计要求 (2)1、基础功能要求 (2)2、拓展功能要求 (2)第二章基础功能模块电路设计 (3)1、南北方向控制模块设计 (3)2、东西方向控制模块设计 (5)3、顶层设计 (8)第三章电路基础功能时序仿真验证 (9)1、南北方向控制模块功能仿真验证 (9)2、东西方向控制模块功能仿真验证 (9)3、顶层设计整体功能仿真验证 (10)第四章电路拓展功能设计 (11)1、“左转向”指示灯功能设计 (11)2、“左转向”指示功能设计 (12)附录 (13)附录1-小组成员与成员分工 (13)附录2-参考资料 (13)概述1、EDA技术的概念EDA技术就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言VHDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

EDA技术的出现,极大地提高了电路设计的效率和可操作性,减轻了设计者的劳动强度。

利用EDA工具,电子设计师可以从概念、算法、协议等开始设计电子系统,大量工作可以通过计算机完成,并可以将电子产品从电路设计、性能分析到设计出IC 版图或PCB版图的整个过程的计算机上自动处理完成。

EDA实验报告:基于VHDL语言的交通灯控制系统设计与实现

图为k1=0时的输出状态s1,输出恒为011110。即亮灯为R1,y2。保持时间1S。

(k2=0)

上图为k2=0时的输出状态s2,输出恒为101011。即亮灯为G1,R2。保持时间2S。

(k3=0)

上图为k3=0时的输出状态s3,输出恒为110011。即亮灯为R1,G2。保持时间1S。

四、小结及心得体会

else

if counter<5 then

next_state<=s3;

else

next_state<=s0;

end if;

end if;

end if;

end if;

end if;

end case;

end process;

ouput:process(current_state)

begin ——显示程序

begin

u1: jiaotongdeng port map(

clk=>clki,

k0=>k0,

k1=>k1,

k2=>k2,

k3=>k3,

r1=>r1,r2=>r2,g1=>g1,g2=>g2,y1=>y1,y2=>y2

);

u2: div port map(clk=>clk1,clk_out=>clki);

end if;

end if;

end if;

when s3=>

if k0='0' then

next_state<=s0;

else

if k1='0' then

next_state<=s1;

EDA实验报告

EDA实验报告EDA(VHDL编程)实验报告一、引言EDA (Electronic Design Automation) 是一种用于电子设计和验证的自动化工具。

VHDL(VHSIC Hardware Description Language)是一种硬件描述语言,用于描述和建模数字系统。

本实验旨在使用VHDL编程并使用EDA工具进行设计和验证。

二、实验目的1.理解并熟悉VHDL编程2.学会使用EDA工具进行设计和验证3.实践数字系统的建模和仿真三、实验过程1.VHDL编程根据实验要求,我们使用VHDL编程来实现一个4位2选1多路器。

首先,我们定义输入端口和输出端口,并声明所需的信号和变量。

然后,我们编写组合逻辑和时序逻辑以实现所需的功能。

最后,我们将实例化该多路器并指定其输入和输出端口。

2.EDA工具设计和验证我们选择了 Xilinx ISE Design Suite 作为我们的 EDA 工具。

首先,我们创建一个新的项目并选择相应的 FPGA 芯片。

然后,我们添加我们的VHDL 设计文件到项目中,并进行综合、布局和路由。

最后,我们使用仿真工具验证我们的设计。

四、实验结果经过实验,我们成功地编写并实例化了一个4位2选1多路器。

我们使用 Xilinx ISE Design Suite 进行综合、布局和路由,并成功验证了我们的设计。

五、实验总结通过本实验,我们掌握了VHDL编程和EDA工具的使用。

我们学会了使用VHDL描述数字系统,并使用EDA工具进行设计和验证。

这些技能对于电子设计和验证非常重要,并将有助于我们更好地理解和应用数字系统的原理和方法。

在实验过程中,我们也遇到了一些困难和挑战。

例如,我们可能需要更深入地了解VHDL编程的语法和方法,以及如何使用EDA工具的高级功能。

此外,我们还需要更多的实践来提高我们的设计和仿真技能。

总之,本实验有助于我们深入学习和理解数字系统的设计和验证。

通过实践和使用EDA工具,我们能够更好地应用所学知识,提高我们的设计和验证能力。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

EDA 实验报告——多功能电子钟姓名:张红义班级:10级电科五班学号:1008101143指导老师:贾树恒电子钟包括:主控模块,计时模块,闹钟模块,辅控模块,显示模块,蜂鸣器模块,分频器模块。

1.主控模块:主要功能:控制整个系统,输出现在的状态,以及按键信息。

源代码:libraryieee;use ieee.std_logic_1164.all;useieee.std_logic_arith.all;useieee.std_logic_unsigned.all;entity mc isport(functionswitch,k,set,lightkey: in std_logic;chose21,setout: out std_logic;lightswitch:bufferstd_logic;modeout,kmodeout : out std_logic_vector(1 downto 0);setcs,setcm,setch,setas,setam,setah:outstd_logic);end mc;architecture work of mc issignalmode,kmode:std_logic_vector(1 downto 0);signal light,chose21buf:std_logic;signalsetcount:std_logic_vector(5 downto 0);beginprocess(functionswitch,k,set,lightkey)beginiffunctionswitch'event and functionswitch='1' thenmode<=mode+'1';end if;iflightkey'event and lightkey='1' thenlightswitch<=not lightswitch;end if;if mode="01" thenchose21buf<='0';else chose21buf<='1';end if;ifk'event and k='1' thenif mode="01" or mode="11" thenkmode<=kmode+'1';end if;end if;if set='1' thenif mode = "01" thenifkmode="01" then setcount<="000001";elsifkmode="10" thensetcount<="000010";elsifkmode="11" thensetcount<="000100";elsesetcount<="000000";end if;elsif mode = "11" thenifkmode="01" thensetcount<="001000";elsifkmode="10" thensetcount<="010000";elsifkmode="11" thensetcount<="100000";elsesetcount<="000000";end if;end if;end if;if set='0' thensetcount<="00000”;end if;setout<=set;modeout<=mode;kmodeout<=kmode;chose21<=chose21buf;setcs<=setcount(0);setcm<=setcount(1);setch<=setcount(2); setas<=setcount(3);setam<=setcount(4);setah<=setcount(5); end process;end work;仿真波形:2. 计时模块主要功能:记录时间,正常计时。

60进制libraryieee;use ieee.std_logic_1164.all;useieee.std_logic_arith.all;useieee.std_logic_unsigned.all;entity count60 isport(clk ,clr :in std_logic;co : out std_logic;outh :out std_logic_vector(7 downto 4);outl :out std_logic_vector(3 downto 0));end count60 ;architecture work of count60 issignal bufh:std_logic_vector(7 downto 4);signal bufl:std_logic_vector(3 downto 0);beginprocess(clk)beginifclr='0' thenbufh<="0000";bufl<="0000";elsif(clk'event and clk='1')thenif(bufh="0101"and bufl="1001")then co<='1';bufh<="0000";bufl<="0000";elsif(bufl="1001")thenbufl<="0000";bufh<=bufh+1;elsebufl<=bufl+1;co<='0'; end if;end if;outh<=bufh;outl<=bufl;end process;end work;24进制libraryieee;use ieee.std_logic_1164.all;useieee.std_logic_arith.all;useieee.std_logic_unsigned.all;entity count24 isport(clk :in std_logic; co: out std_logic;outh :out std_logic_vector(7 downto 4);outl :out std_logic_vector(3 downto 0));end count24 ;architecture a of count24 issignal bufh:std_logic_vector(7 downto 4);signal bufl:std_logic_vector(3 downto 0);beginprocess(clk)beginif(clk'event and clk='1')thenif(bufh="0010"and bufl="0011")thenco<='1';bufh<="0000";bufl<="0000";elsif(bufl="1001")thenbufl<="0000";bufh<=bufh+1;elsebufl<=bufl+1;co<='0';end if;end if;outh<=bufh;outl<=bufl;end process;end a;keyen.vhdlibraryieee;use ieee.std_logic_1164.all;entitykeyen isport(en, keyin:instd_logic;keyout: out std_logic);endkeyen;architecture work of keyen isbeginprocess(en,keyin)beginif en='1' then keyout<=keyin;elsekeyout<='0';end if;end process;end work;chose21.vhdlibraryieee;use ieee.std_logic_1164.all;entity chose21 isport(clk,add,chose : in std_logic;co : out std_logic);end chose21;architecture work of chose21 isbeginprocess(chose,clk,add)beginif chose='1' then co<=clk;elseco<=add;end if;end process;end work;3. 闹钟模块:主要功能记录闹钟时间信息,输出闹钟时间信息源代码:同上:keyen.vhdcount60.vhdcount24.vhd4. 辅控模块:主要功能处理显示,以及蜂鸣器的信号。

时钟输入与闹钟输入相比较,组成闹钟功能,以及整点报时功能。

源代码Ac.vhdlibraryieee;use ieee.std_logic_1164.all;useieee.std_logic_unsigned.all;entity ac isport(clk,lightonoff:instd_logic;mode,kmode:instd_logic_vector(1 downto 0);csh,csl,cmh,cml,chh,chl,ash,asl,amh,aml,ahh,ahl:instd_logic_vector(3 downto 0);q0,q1,q2,q3,q4,q5,q6,q7:outstd_logic_vector(3 downto 0);lightswitch,sound512,sound1024,timeok:out std_logic);end ac;architecture work of ac issignal q0b,q1b,q2b,q3b,q4b,q5b,q6b,q7b: std_logic_vector(3 downto 0);beginprocess(chh,cmh,csh,ash,ahh,amh,chl,cml,csl,asl,ahl,aml,mode,km ode,clk)beginif mode="00" or mode="01" then --闪烁功能开始q0b<=csl;q1b<=csh;q2b<="1010";q3b<=cml;q4b<=cmh;q5b<="1010";q6b<=chl;q7b<=chh;elsif mode="10" or mode="11" then q0b<=asl;q1b<=ash;q2b<="1010";q3b<=aml;q4b<=amh;q5b<="1010";q6b<=ahl;q7b<=ahh;end if;ifclk ='1' thenif mode="00" or mode="10" then q0<=q0b;q1<=q1b;q2<=q2b;q3<=q3b;q4<=q4b;q5<=q5b;q6<=q6b;q7<=q7b;elsecasekmode iswhen "01" =>q0<="1111";q1<="1111";q2<=q2b;q3<=q3b;q4<=q4b;q5<=q5b;q6<=q6b;q7<=q7b;when "10" =>q0<=q0b;q1<=q1b;q2<=q2b;q3<="1111";q4<="1111";q5<=q5b;q6<=q6b;q7<=q7b;when "11" =>q0<=q0b;q1<=q1b;q2<=q2b;q3<=q3b;q4<=q4b;q5<=q5b;q6<="1111";q7<="1111";when others =>q0<="1111";q1<="1111";q2<="1111";q3<="1111";q4<="1111";q5<="1111";q6<="1111";q7<="1111";end case;end if;elseq0<=q0b;q1<=q1b;q2<=q2b;q3<=q3b;q4<=q4b;q5<=q5b;q6<=q6b;q7<=q7b;end if;--闪烁功能完毕--整点报时功能开始ifcmh="0101" and cml="1001" thenifcsh="0101" thenifcsl="0001" or csl="0010" or csl="0101" orcsl="0111" thensound512<='1' ;elsifcsl="1001" thensound1024<='1';elsesound512<='0';sound1024<='0';end if;end if;end if;--正点报时功能完--显示开关功能开始iflightonoff='1' thenlightswitch<='0';elselightswitch<='1';end if;--显示开关功能完毕--闹钟功能开始ifchh=ahh and cmh=amh and chl=ahl and cml=aml then timeok<='1';elsetimeok<='0';end if;--闹钟功能完毕end process;end work;5. 显示模块:主要功能处理辅控传来的显示信号,在数码管上直接的显示数字。