VHDL实验报告一2选1多路选择器

(新)实验二组合逻辑电路设计

实验二组合逻辑电路设计一、实验目的1、了解和逐步掌握一般组合逻辑电路的设计方法;2、熟练掌握QuartusⅡ软件原理图输入方式的操作步骤;3、熟练掌握QuartusⅡ软件中底层和顶层电路模块的设计方法;4、熟练掌握Quartus Ⅱ软件常见操作的设置方法。

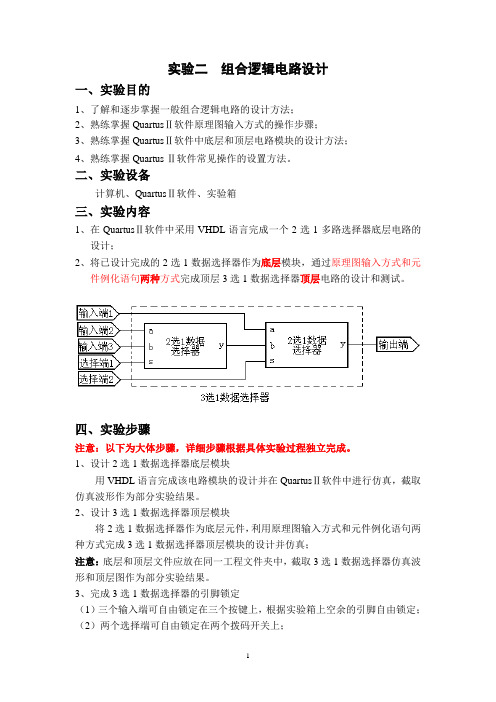

二、实验设备计算机、QuartusⅡ软件、实验箱三、实验内容1、在QuartusⅡ软件中采用VHDL语言完成一个2选1多路选择器底层电路的设计;2、将已设计完成的2选1数据选择器作为底层模块,通过原理图输入方式和元件例化语句两种方式完成顶层3选1数据选择器顶层电路的设计和测试。

四、实验步骤注意:以下为大体步骤,详细步骤根据具体实验过程独立完成。

1、设计2选1数据选择器底层模块用VHDL语言完成该电路模块的设计并在QuartusⅡ软件中进行仿真,截取仿真波形作为部分实验结果。

2、设计3选1数据选择器顶层模块将2选1数据选择器作为底层元件,利用原理图输入方式和元件例化语句两种方式完成3选1数据选择器顶层模块的设计并仿真;注意:底层和顶层文件应放在同一工程文件夹中,截取3选1数据选择器仿真波形和顶层图作为部分实验结果。

3、完成3选1数据选择器的引脚锁定(1)三个输入端可自由锁定在三个按键上,根据实验箱上空余的引脚自由锁定;(2)两个选择端可自由锁定在两个拨码开关上;(3)输出端可自由锁定在一个LED 灯上,通过灯的亮灭判断是否有输出。

为了清楚区分三个输入端,测试时可设置三个不同的LED 灯来判断。

图-1 开关量输入输出模块S1—s8是带自锁的单刀单执拨码开关,在开关未拨动时是低电平,拨动时J1为高电平并保持高电平不变,只有回拨开关时J1才恢复低电平输入。

图-2 按键模块此模块共有8个按键,BUTTON1—BUTTON8是轻触按键;在按键未按下时JP6为高电平输入,按键按下后JP6对FPGA 输入低电平,松开按键后恢复高电平输入。

图-3 LED 灯指示模块该模块有8个LED 指示灯,在使用时候只需要用排线连接JP5和FPGA 连接,FPGA 输出低电平时指示灯亮。

计算机组成与结构实验报告1 实验一: EDA入门

大学实验报告2018年5月21日课程名称:计算机组成与结构实验实验名称:实验一: EDA入门班级及学号:姓名:同组人:签名:指导教师:指导教师评定:一、实验目的:了解并初步掌握使用QuartusⅡ软件集成开发工具进行专用硬件电路设计的工作过程;了解并初步掌握使用硬件描述语言(VHDL)表述电路功能设计;了解并初步掌握使用时序仿真方法验证电路逻辑功能;了解并初步掌握使用GW48实验台对设计电路进行硬件下载配置和测试。

二、实验任务:1.首先利用QuartusⅡ完成“2选1多路选择器”电路的VHDL语言表达描述;2.设计时序仿真测试激励波形信号并进行电路功能的仿真测试;3.完成“2选1多路选择器”电路的硬件下载编程;4.设计硬件测试方案,配置试验台测试环境,进行硬件测试;5.实验完成,写出实验报告三、实验原理:本实验通过Quartus II软件,编程设计硬件电路功能,在一片FPGA(型号EP1C6Q240C8)可编程芯片上,制作成一块具有“二选一多路选择器”功能的专用电路器件。

测试验证设计电路功能是在GW48实验系统上进行,该实验系统通过改变连线和软件配置可支持多种电路试验。

本实验选用电路模式NO.5。

“2选1多路选择器”电路原理图及逻辑表达式如下:四、实验步骤:第一阶段:建立工程,输入设计文件该电路可用硬件描述语言VHDL表达如下:ENTITY mux21a ISPORT(a,b,s:IN BIT;y:OUT BIT);END ENTITY mux21a;ARCHITECTURE one OF mux21a ISBEGIN图3.1 “2选1多路选择器”原理图和逻辑表达PROCESS(a,b,s)BEGINIF s ='0' THEN y<= a;ELSE y<=b;END IF;END PROCESS;END ARCHITECTURE one;第二阶段:编译第三阶段:时序仿真仿真解释:a,b输入端,s是控制端,y是输出端。

EDA实验报告

EDA 实验报告实验一:组合电路的设计实验内容是对2选1多路选择器VHDL 设计,它的程序如下:ENTITY mux21a ISPORT ( a, b : IN BIT; s : IN BIT; y : OUT BIT ); END ENTITY mux21a;ARCHITECTURE one OF mux21a IS SIGNAL d,e : BIT; BEGIN d <= a AND (NOT S) ; e <= b AND s ; y <= d OR e ;END ARCHITECTURE one ;Mux21a 仿真波形图以上便是2选1多路选择器的VHDL 完整描述,即可以看成一个元件mux21a 。

mux21a 实体是描述对应的逻辑图或者器件图,图中a 和b 分别是两个数据输入端的端口名,s 为通道选择控制信号输入端的端口名,y 为输出端的端口名。

Mux21a 结构体可以看成是元件的内部电路图。

最后是对仿真得出的mux21a 仿真波形图。

Mux21a 实体Mux21a 结构体实验二:时序电路的设计实验内容D触发器的VHDL语言描述,它的程序如下:LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL ;ENTITY DFF1 ISPORT (CLK : IN STD_LOGIC ;D : IN STD_LOGIC ;Q : OUT STD_LOGIC );END ;D触发器ARCHITECTURE bhv OF DFF1 ISBEGINPROCESS (CLK)BEGINIF CLK'EVENT AND CLK = '1'THEN Q <= D ;END IF;END PROCESS ;END bhv;D触发器的仿真波形图最简单并最具代表性的时序电路是D触发器,它是现代可编程ASIC设计中最基本的时序元件和底层元件。

实验六二选一数据选择器的VHDL设计

将设计实体内的处理结果向定 义的信号或界面端口进行赋值

用以调用过程或函数,并将获 得的结果赋值于信号。 元件调用,用来调用另一个 实体所描述的电路。

实体和结构体之间的关系

Input 1

Input n

实 体

Output 1

Output n

A B C D Se l 2

MUX_Out

结构体三种描述方法

VHDL结构体术语

说明语句:用于定义结构体中所用的数据对象(常量 和信号)和子程序,并对所引用的元件加以说明,但 不能定义变量。 功能描述语句:有五种类型,可以把它们看成结构体 的五种子结构。这五种语句结构本身是并行语句,但 内部可能含有并行运行的逻辑描述语句或顺序运行的

逻辑描述语句,如进程内部包含的即为顺序语句。

★数据类型必须一致

★表达式中有多个运算符时一般要加括号,但 and、or等除外 6、运算符的优先

级

VHDL操作符优先级

signal d1,d2,s : integer; SIGNAL a ,b,c : STD_LOGIC_VECTOR (3 DOWNTO 0) ; SIGNAL d,e,f,g : STD_LOGIC_VECTOR (1 DOWNTO 0) ; SIGNAL h,i,j,k : STD_LOGIC ; SIGNAL l,m,n,o,p : BOOLEAN ; ... s<=a and b; -- integer 不能进行逻辑运算 a<=b AND c; -- a、b、c的数据类型同属4位长的位矢量 d<=e OR f OR g ; -- 两个操作符OR相同,不需括号 h<=(i NAND j)NAND k ; -- NAND必须加括号 l<=(m XOR n)AND(o XOR p); -- 操作符不同,必须加括号 h<=i AND j AND k ; -- 两个操作符都是AND,不必加括号 h<=i AND j OR k ; -- 两个操作符不同,未加括号,表达错误

EDA实验报告

E D A实验报告实验一、QuartusⅡ软件使用一、试验目的学习QUARTUS II软件的使用,掌握软件工程的建立、VHDL源文件的设计和波形仿真等基本内容;二、试验内容利用QuartusⅡ完成2选1多路选择器的文本编辑输入(mux21a.vhd)和仿真测试等步骤,给出仿真波形。

设计含有异步清零和计数使能的4位二进制加减可控计数器。

三、设计过程VHDL设计程序如下二选一:LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL ;USE IEEE.STD_LOGIC_UNSIGNED.ALL ;ENTITY mux21 ISPORT ( a, b : IN BIT;s : IN BIT;y : OUT BIT );END ENTITY mux21;-- behave descriptionARCHITECTURE one OF mux21 ISBEGINy <= a WHEN s = '0' ELSE b ;END ARCHITECTURE one ;四位二进制计数器:LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL ;USE IEEE.STD_LOGIC_UNSIGNED.ALL ; -- 运算符重载ENTITY mycounter ISPORT ( ena,clr,d_ctr,clk : IN STD_LOGIC ;q : OUT STD_LOGIC_VECTOR(3 DOWNTO 0 )) ;END ENTITY mycounter;ARCHITECTURE bhv OF mycounter ISSIGNAL q1 : STD_LOGIC_VECTOR(3 DOWNTO 0 );BEGINq <= q1 ;PROCESS (clk,clr,ena,d_ctr)BEGINIF clr='1' THEN q1<="0000";ELSIF clk'EVENT AND clk = '1' THENIF ena='1' THENIF d_ctr='1' THENq1 <= q1 + '1';ELSEq1<=q1-'1';END IF;ELSEq1<=q1;END IF;END IF;END PROCESS ;END ARCHITECTURE bhv;四、仿真波形与分析二选一:四位二进制计数器:实验二、原理图输入设计方法一、试验目的熟悉利用QUARTUS II中的原理图输入法设计组合电路,掌握层次化设计的方法,并通过一个4位全减器的设计把握文本和原理图输入方式设计的详细流程。

2选1选择器的VHDL设计课件

3.1 多路①可以使用26个英文字母,数字0-9以及下划线“_”,且 只能以英文字母开头;

②不区分大小写;最长不超过64个字符;

③必须是单一下划线,且下划线前后都必须有英文字母 或数字;

6、端口定义语句port和端口模式 端口模式

IN 输入端口,定义的通道为单向只读模 OUT 式输出端口,定义的通道为单向输出模 INOUT 式 定义的通道确定为输入输出双向端口 BUFFER 缓冲端口,其功能与INOUT类似

3、界符 标点符号“;”表示VHDL中语句的结束;

3.1 多路选择器的VHDL描述

4、实体和结构体

实体和结构体是VHDL程序的两个基本组成部分;其中 实体主要用于定义电路或系统的外部端口;结构体用于定义 内部逻辑功能或电路结构。

ENTITY e_name IS PORT ( p_name : port_m

-- 注意,赋值条件的数据类型必须是boolean

3.1 多路选择器的VHDL描述

思考 ❖还有没有其它方法实现二选一? ❖n选一的多路选择器怎么设计?

3.1 多路选择器的VHDL描述

9、赋值符号<=

信号赋值符号“<=”,表示将符号右端的值赋值给左端的 信号; 10、关系运算符=

等号“=”没有赋值的含义,也不是相等的意思,而是 关系运算符,只是一种数据比较符号,其结果只有两种情况, 要么为真true,条件成立;要么为假false,条件不成立。 表达式 WHEN 赋值条件 ELSE

END ARCHITECTURE one ;

3.1 多路选择器的VHDL描述

3.1 多路选择器的VHDL描述

entity 实体

architecture 结构体

实体 mux21a1

基于VHDL的数字多路选择器教学模式的探索

基于VHDL的数字多路选择器教学模式的探索王静怡,孙旭华,卜宏博,付 旭(西安石油大学,陕西 西安 710065)- 32 -1.设计目标课前发送授课小视频、网页等自学资源,学生自主学习,并完成给定的设计及学习要求。

2.小组互动通过给定系统功能、设计构思、编程实现等阶段,采取集中讲解的方式,让学生对自己的成果进行介绍并进行互动提问。

3.协作讨论在教师的指导下,学生以2~3人为小组进行自由探讨,并深入研究程序语言中的新手段及实施要领,鼓励学生积极发言,教师给予评价,实现师生交流。

五、课件设计(一)重要性随着信息的不断更新,各类教学资源层出不穷。

可以将文句、幻灯片、语音等很好地融汇在一起,同时通过课堂教学活动演示给学生。

现代课堂教学注重学生的主体地位,提倡学生自己学习、独立思考。

课件可以给学生展现的学习定位明确、思路清晰、层次合理。

学生可以在实际课堂时间内吸收到大量的理论知识,同时挤出更多的时间和精力专注于提高动手能力,进一步提升课堂效率。

(二)原则需要遵循科学合理性的原则:1.紧扣教学大纲课件是传递知识的重要途径,更是大纲的扩展和延伸。

因此,以大纲为框架,延伸知识为枝叶,这样整个课件是一个有逻辑性的整体。

2.重难点突出避免平铺直叙,重点凸显。

教学思路清楚,层次鲜明。

3.提高学生注意力课件需搭配图表等。

选用感兴趣的话题,如讲到多路选择器,可以联想游戏中角色选择等。

制作课件模板和文字色调对比凸显,带动学习热情,促使学生养成学习自主的好习惯。

六、教学效果评价(一)理论分析整个教学活动贯彻学校的教学方针,以学生为主体,重视学习能力的培养,提倡学生的个性化发展,努力提高学生实践创新性。

课堂之外的作业,帮助学生把原理和实践协调起来,构成一个完整的知识体系,使学生做到学有所得,并将所学基础知识灵活地应用到解决具体的问题中[4]。

通过学生的课堂表现展开过程性评价,鼓励学生认真学习、积极探索。

(二)实践证明这门课有具体的课堂教学方向、合理的知识架构、明确的实验教学导向和现代化的教学模式和手段,形成了学生独立自主式、深入分析式的学习方式,唤起学生浓厚的兴趣。

EDA:实验六2选1和4选1多路选择实验

实验六 2选1和4选1多路选择实验班级:通信1121 姓名:王密学号:1121302230一、实验目的:1、了解2选1和4选1的工作原理和实现的方法。

2、实现两个多路选择器,一个2选1,一个4选1。

3、学会用于VHDL语言进行程序设计。

二、实验原理:2选1当选择输入S为L时,Y输出A, 当S为H时,Y输出B。

当选择输入AB为LL时,Y输出D0, 当AB为LH时,Y输出D1, 当AB为HL时,Y输出D2,当AB为HH时,Y输出D3。

说明:sw1选择是控制4选1,还是2选1,sw1=1,为4选1,sw1=0,为2选1。

sw3,sw2为4选1的地址,sw4为2选1的地址。

三、实验连线:1、将EP2C5适配板左下角的JTAG用十芯排线和万用下载区左下角的SOPC JTAG口连接起来,万用下载区右下角的电源开关拨到 SOPC下载的一边。

2、请将JPLED1短路帽右插,JPLED的短路帽全部上插。

3、将实验板左端的JP103全部用短路帽接上(共八个)。

四、实验内容与步骤:(程序:EP2C5\muxsel\muxsel.sof)1、打开Quartus II 6.0软件,点击“File→OpenP roject”出现如下的对话框(图9.1),选中muxsel,点打开即可;图9.12、点击“Tools-Programmer”后出现如下的对话窗口,3、在点”Edit→Add File………”出现如下对话框(图9.2),在图9.3对话框中,选中EP2C5/muxsel/muxsel.sof项目后点击打开回到Programmer对话框, 在下载对话窗口中“选中Program/ Configure”,点击“Start”即进行下载。

图9.2图9.3现将muxsel.vhd原程序作如下说明:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;USE IEEE.STD_LOGIC_SIGNED.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY liu123 ISPORT (SW1:IN BOOLEAN;SW2:IN STD_LOGIC;SW3:IN STD_LOGIC;SW4:IN BOOLEAN;LED:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END liu123;ARCHITECTURE ADO OF liu123 ISSIGNAL RST_MUXSEL: STD_LOGIC_VECTOR(7 DOWNTO 0);SIGNAL RST_MUXSEL2: STD_LOGIC_VECTOR(7 DOWNTO 0);BEGINPROCESS(SW1,SW2,SW3)beginIF (SW2='0' AND SW3 ='0') THEN RST_MUXSEL<="10101010";ELSIF (SW2='0' AND SW3='1' )THEN RST_MUXSEL<="01010101";ELSIF (SW2='1' AND SW3='0')THEN RST_MUXSEL<="10001000";ELSIF (SW2='1' AND SW3='1') THEN RST_MUXSEL<="01110111";ELSE RST_MUXSEL<="XXXXXXXX";END IF;E ND PROCESS;PROCESS (SW4)BEGINIF SW4 THENRST_MUXSEL2<="10100101";ELSERST_MUXSEL2<="01011010";END IF;END PROCESS;PROCESS(SW1,RST_MUXSEL,RST_MUXSEL2)BEGINcase sw1 iswhen true => LED<=RST_MUXSEL;when false => LED<=RST_MUXSEL2;END case;END PROCESS;END ADO;引脚分配(Cyclone EP2C5Q208C8):sw1-P43,sw2-P44,sw3-P45,sw4-P46,led0-P13,led1-P14,led2-P15,led3-P30,led4-P3 1,led5-P33,led6-P34,led7-P35,管脚标号led0到led7分别接到8位的LED流水灯上,使用高低电平观察输出的结果,sw1到sw4接到拨码开关上,。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验一

实验目的:

熟悉quartus的vhdl文本设计流程全过程,学习简单的组合电路的设计,多层次的电路设计,仿真和硬件测试

二、实验内容

内容(一)用vhdl语言设计2选1多路选择器

参考例3-1程序设计如下:

library ieee;

use mux21a is

port (a,b,s:in bit;

y: out bit);

end entity mux21a;

architecture one of mux21a is

begin

y<=a when s='0' else b;

end architecture one

全程编译后软件提示0错误,3警告,可以继续下面仿真操作。

程序分析:

这是一个2选1多路选择器,a和b分别为两个数字输入端的端口名,s为通道选择控制信号输入端的端口名,y为输出端的端口名。

时序仿真及分析:

时序仿真输入图:

时序仿真输出图:

时序分析:

由上面两图可以得知:当s=0时,y口输出a,当s=1时,y口输出b

下载和硬件测试:

引脚锁定图:

程序下载完成后,选择实验电路模式5,通过短路帽选择clock0接256Hz 信号,clock2接8Hz信号。

通过键一控制s,当键一进行切换时,明显能听到扬声器发出两种不同音调的声音。

实验内容(二)双二选一多路选择器设计

程序设计:

library ieee;

use mux21a is

port (a,b,s:in bit;

y: out bit);

end entity mux21a;

architecture one of mux21a is

begin

y<=a when s='0' else b;

end architecture one;

entity muxk is

port (a1,a2,a3,s0,s1:in bit;

outy:out bit);

end entity muxk;

architecture bhv of muxk is

component mux21a

port (a,b,s:in bit;

y:out bit);

end component;

signal tmp: bit;

begin

u1:mux21a port map(a=>a2,b=>a3,s=>s0,y=>tmp);

u2:mux21a port map(a=>a1,b=>tmp,s=>s1,y=>outy);

end architecture bhv;

全程编译后软件提示0错误,2警告

程序分析:

这是一个双2选1多路选择器,a1、a2和a3分别为两个数字输入端的端口名,s0、s1为通道选择控制信号输入端的端口名,outy为输出端的端口名。

实体mux21a是一个2选一选通电路,实体muxk是元件的例化,其作用是将两个mux21a组合成一个3选1多路选择器。

时序仿真及分析:

时序仿真输入图

时序仿真输出图

时序分析:

从仿真出来的结果,我们不难发现,s0和s1做为a1、a2、a3的选通控制信号。

当s0=0.、s1=0时,outy输出a1;当s0=0.、s1=1时,outy输出a2;当s0=1.、s1=0时,outy输出a1;当s1=1.、s2=1时,outy输出a3;

下载和硬件测试:

引脚锁定图

程序下载完成后,选择实验电路模式5,通过短路帽选择clock0接256Hz 信号,clock2接8Hz信号,clock5接1024Hz。

通过键一、键二分别控制s1、s2,当键一、键二进行切换时,明显能听到扬声器发出三种不同音调率的声音。

实验结果:

在实验一中内容一和内容二编译,仿真都没问题,除了有两三个警告以外,并无其他错误,但是在下载过程中,由于设置编程器处出现一点问题,导致下载失败,经过请教,调整后成功运行

四、实验过程所出现的问题及其解决

首先,仿真结果出现延时,应该将a,b,s的周期增大些,且要保证单位为us,刚开始做实验内容(一)时,文件夹名字与程序中所用的实体名不一致,导致程序运行时无法找到文件夹,无法正常工作,经更改后,正常运行,同时文件夹名字不用汉字和数字,以免出错。

每次修改过程都应该注意保存,才能将修改的结果反映到所输出的波形中,刚开始常常忘记,经过多次操作后才能够熟练运用。

HDL程序设计

—组合逻辑电路设计

班级:08级通信工程二班

学号:

姓名:。