最新-闪速存储器芯片K9F642019系列的典型应用 精品

I.MX6开发板四核E9卡片电脑

可连接多种外部设备:如USB接口、SD卡插槽等,方便扩展和使用。 支持多种操作系统:如Windows、Android等,满足不同用户的需求。 可通过无线网络连接互联网:方便用户进行网络浏览、邮件收发等操作。 支持多种应用程序:如办公软件、图形处理软件等,提高工作效率。

I.MX6开发板 四核E9卡片电 脑的硬件配置

和性能特点

操作系统和应 用软件的使用 体验和功能介

绍

开发板在嵌入 式系统、物联 网、智能家居 等领域的应用

案例和优势

总结I.MX6开 发板四核E9卡 片电脑的优缺 点和未来发展

趋势

未来发展趋势:预测I.MX6开发板四核E9卡片电脑未来的发展状况 技术创新:探讨未来可能出现的与I.MX6开发板四核E9卡片电脑相关的技术创新 应用领域拓展:分析I.MX6开发板四核E9卡片电脑在未来的应用领域拓展情况 市场竞争:预测未来I.MX6开发板四核E9卡片电脑市场的竞争格局

添加文档副标题

目录

01.

02.

03.

04.

05.

06.

四核处理器:高性能,满足多任务处理需求 精美的外观设计:小巧轻便,易于携带 大容量存储:提供足够的存储空间,满足各种应用需求 丰富的接口:方便连接各种外设,扩展性良好 低功耗设计:延长电池寿命,减少能源消耗

工业控制:I.MX6开发板四核E9卡片电脑可用于工业控制系统中,实现自动化控制和监测。

型号:I.MX6四核处理器 主频:1.2GHz 核心数:四核 制程:40nm

内存类型: DDR3

内存大小:2GB

内存频率: 800MHz

内存扩展:最大 支持32GB

内存:2GB DDR3

存储:16GB eMMC

扩展:支持 MicroSD卡

MEMORY存储芯片K9F1G08U0B-PCB0中文规格书

Product IntroductionThe K9F1G08U0B is a 1,056Mbit(1,107,296,256 bit) memory organized as 65,536 rows(pages) by 2,112x8 columns. Spare 64x8 col-umns are located from column address of 2,048~2,111. A 2,112-byte data register is connected to memory cell arrays accommodat-ing data transfer between the I/O buffers and memory during page read and page program operations. The memory array is made up of 32 cells that are serially connected to form a NAND structure. Each of the 32 cells resides in a different page. A block consists of two NAND structured strings. A NAND structure consists of 32 cells. Total 1,081,344 NAND cells reside in a block. The program and read operations are executed on a page basis, while the erase operation is executed on a block basis. The memory array consists of 1,024 separately erasable 128K-byte blocks. It indicates that the bit by bit erase operation is prohibited on the K9F1G08U0B.The K9F1G08U0B has addresses multiplexed into 8 I/Os. This scheme dramatically reduces pin counts and allows system upgrades to future densities by maintaining consistency in system board design. Command, address and data are all written through I/O's by bringing WE to low while CE is low. Those are latched on the rising edge of WE. Command Latch Enable(CLE) and Address Latch Enable(ALE) are used to multiplex command and address respectively, via the I/O pins. Some commands require one bus cycle. For example, Reset Command, Status Read Command, etc require just one cycle bus. Some other commands, like page read and block erase and page program, require two cycles: one cycle for setup and the other cycle for execution. The 132M byte physical space requires 28 addresses, thereby requiring four cycles for addressing : 2 cycles of column address, 2 cycles of row address, in that order. Page Read and Page Program need the same four address cycles following the required command input. In Block Erase oper-ation, however, only the two row address cycles are used. Device operations are selected by writing specific commands into the com-mand register. Table 1 defines the specific commands of the K9F1G08U0B.In addition to the enhanced architecture and interface, the device incorporates copy-back program feature from one page to another page without need for transporting the data to and from the external buffer memory. Since the time-consuming serial access and data-input cycles are removed, system performance for solid-state disk application is significantly increased.Table 1. Command SetsNOTE : 1. Random Data Input/Output can be executed in a page.2. Read EDC Status is only available on Copy Back operation.Caution : Any undefined command inputs are prohibited except for above command set of Table 1.Function1st Cycle 2nd CycleAcceptable Command during BusyRead00h 30h Read for Copy Back 00h 35h Read ID 90h -Reset FFh -OPage Program 80h 10h Copy-Back Program 85h 10h Block Erase60h D0h Random Data Input (1)85h -Random Data Output (1)05h E0hRead Status 70h O Read EDC Status (2)7BhODC AND OPERATING CHARACTERISTICS (Recommended operating conditions otherwise noted.)NOTE : 1. V IL can undershoot to -0.4V and V IH can overshoot to V CC +0.4V for durations of 20 ns or less.2. Typical value is measured at Vcc=3.3V, T A =25°C. Not 100% tested.ParameterSymbol Test ConditionsK9F1G08U0B(3.3V)UnitMinTypMaxOperating CurrentPage Read with Serial Access I CC 1tRC=25nsCE=V IL, I OUT =0mA-1530mAProgram I CC 2-EraseI CC 3-Stand-by Current(TTL)I SB 1CE=V IH , WP=0V/V CC --1Stand-by Current(CMOS)I SB 2CE=V CC -0.2, WP=0V/V CC -1050µAInput Leakage Current I LI V IN =0 to Vcc(max)--±10Output Leakage Current I LO V OUT =0 to Vcc(max)--±10Input High VoltageV IH (1)-0.8xVcc -V CC +0.3V Input Low Voltage, All inputs V IL (1)--0.3-0.2xVccOutput High Voltage Level V OH K9F1G08U0A :I OH =-400µA 2.4--Output Low Voltage Level V OLK9F1G08U0A :I OL =2.1mA--0.4Output Low Current(R/B)I OL (R/B)K9F1G08U0A :V OL =0.4V810-mA RECOMMENDED OPERATING CONDITIONS(Voltage reference to GND, K9F1G08U0B-XCB0 :T A =0 to 70°C, K9F1G0808B-XIB0:T A =-40 to 85°C)ParameterSymbol K9F1G08U0B(3.3V)UnitMin Typ.Max Supply Voltage V CC 2.7 3.3 3.6V Supply VoltageV SSV ABSOLUTE MAXIMUM RATINGSNOTE :1. Minimum DC voltage is -0.6V on input/output pins. During transitions, this level may undershoot to -2.0V for periods <30ns. Maximum DC voltage on input/output pins is V CC +0.3V which, during transitions, may overshoot to V CC +2.0V for periods <20ns.2. Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect reliability.ParameterSymbol Rating Unit3.3V Device Voltage on any pin relative to VSSV CC-0.6 to + 4.6VV IN -0.6 to + 4.6V I/O-0.6 to Vcc + 0.3 (< 4.6V)Temperature Under BiasK9XXG08XXB-XCB0T BIAS -10 to +125°C K9XXG08XXB-XIB0-40 to +125Storage Tempera-tureK9XXG08XXB-XCB0T STG-65 to +150°CK9XXG08XXB-XIB0Short Circuit CurrentI OS5mACAPACITANCE (T A =25°C, V CC =3.3V, f=1.0MHz)NOTE : Capacitance is periodically sampled and not 100% tested.ItemSymbol Test ConditionMin Max Unit Input/Output Capacitance C I/O V IL =0V -10pF Input CapacitanceC INV IN =0V-10pFVALID BLOCKNOTE :1. The device may include initial invalid blocks when first shipped. Additional invalid blocks may develop while being used. The number of valid blocks is presented with both cases of invalid blocks considered. Invalid blocks are defined as blocks that contain one or more bad bits. Do not erase or pro-gram factory-marked bad blocks. Refer to the attached technical notes for appropriate management of invalid blocks.2. The 1st block, which is placed on 00h block address, is guaranteed to be a valid block up to 1K program/erase cycles with 1bit/512Byte ECC.ParameterSymbol Min Typ.Max Unit K9F1G08U0BN VB1,004-1,024BlocksMODE SELECTIONNOTE : 1. X can be V IL or V IH.2. WP should be biased to CMOS high or CMOS low for standby.CLE ALE CE WERE WP ModeH L L H X Read Mode Command Input L H L H X Address Input(4clock)H L L H H Write ModeCommand Input L H L H H Address Input(4clock)L L L HH Data Input L L L H XData Output X X X X H X During Read(Busy)X X X X X H During Program(Busy)X X X X X H During Erase(Busy)X X (1)X X X L Write Protect XXHXX0V/V CC (2)Stand-byAC TEST CONDITION(K9F1G08U0B-XCB0 :TA=0 to 70°C, K9F1G08U0B-XIB0:TA=-40 to 85°C, K9F1G08U0B : Vcc=2.7V~3.6V unless otherwise noted)ParameterK9F1G08U0B Input Pulse Levels 0V to Vcc Input Rise and Fall Times 5ns Input and Output Timing Levels Vcc/2Output Load1 TTL GATE and CL=50pF。

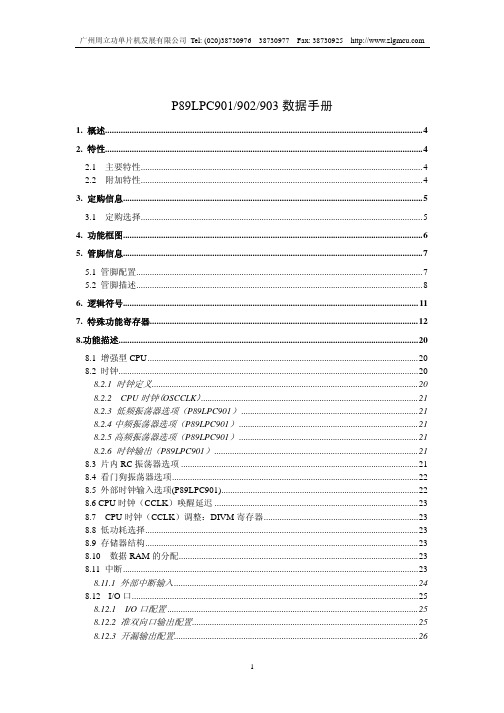

P89LPC901_902_903中文数据完整手册

3. 定购信息......................................................................................................................................5 3.1 定购选择..............................................................................................................................5

4. 功能框图......................................................................................................................................6 5. 管脚信息......................................................................................................................................7 5.1 管脚配置................................................................................................................................7 5.2 管脚描述................................................................................................................................8 6. 逻辑符号.................................................................................................................................... 11 7. 特殊功能寄存器........................................................................................................................12 8.功能描述......................................................................................................................................20 8.1 增强型 CPU.........................................................................................................................20 8.2 时钟......................................................................................................................................20 8.2.1 时钟定义 .......................................................................................................................20 8.2.2 CPU 时钟(OSCCLK) .................................................................................................21 8.2.3 低频振荡器选项(P89LPC901) ...............................................................................21 8.2.4 中频振荡器选项(P89LPC901) ................................................................................21 8.2.5 高频振荡器选项(P89LPC901) ................................................................................21 8.2.6 时钟输出(P89LPC901) ...........................................................................................21 8.3 片内 RC 振荡器选项 ..........................................................................................................21 8.4 看门狗振荡器选项 ..............................................................................................................22 8.5 外部时钟输入选项(P89LPC901)........................................................................................22 8.6 CPU 时钟(CCLK)唤醒延迟 ...........................................................................................23 8.7 CPU 时钟(CCLK)调整:DIVM 寄存器 .....................................................................23 8.8 低功耗选择 ..........................................................................................................................23 8.9 存储器结构 ..........................................................................................................................23 8.10 数据 RAM 的分配...........................................................................................................23 8.11 中断 ....................................................................................................................................23 8.11.1 外部中断输入 .............................................................................................................24 8.12 I/O 口 ................................................................................................................................25 8.12.1 I/O 口配置 ................................................................................................................25 8.12.2 准双向口输出配置 .....................................................................................................25 8.12.3 开漏输出配置 .............................................................................................................26

MEMORY存储芯片MT29F1G08ABAEAWP_E中文规格书

General DescriptionMicron NAND Flash devices include an asynchronous data interface for high-perform-ance I/O operations. These devices use a highly multiplexed 8-bit bus (I/Ox) to transfercommands, address, and data. There are five control signals used to implement theasynchronous data interface: CE#, CLE, ALE, WE#, and RE#. Additional signals controlhardware write protection and monitor device status (R/B#).This hardware interface creates a low pin-count device with a standard pinout that re-mains the same from one density to another, enabling future upgrades to higher densi-ties with no board redesign.A target is the unit of memory accessed by a chip enable signal. A target contains one ormore NAND Flash die. A NAND Flash die is the minimum unit that can independentlyexecute commands and report status. A NAND Flash die, in the ONFI specification, isreferred to as a logical unit (LUN). There is at least one NAND Flash die per chip enablesignal. For further details, see Device and Array Organization.Signal Descriptions and AssignmentsTable 1: Asynchronous Signal DefinitionsNotes: 1.See Device and Array Organization for detailed signal connections.2.See Asynchronous Interface Bus Operation for detailed asynchronous interface signaldescriptions.PROGRAM PAGE TWO-PLANE (80h-11h)The PROGRAM PAGE TWO-PLANE (80h-11h) command enables the host to input datato the addressed plane's cache register and queue the cache register to ultimately bemoved to the NAND Flash array. This command can be issued one or more times. Eachtime a new plane address is specified that plane is also queued for data transfer. To in-put data for the final plane and to begin the program operation for all previouslyqueued planes, issue either the PROGRAM PAGE (80h-10h) command or the PROGRAMPAGE CACHE (80h-15h) command. All of the queued planes will move the data to theNAND Flash array. This command is accepted by the die (LUN) when it is ready(RDY = 1).To input a page to the cache register and queue it to be moved to the NAND Flash arrayat the block and page address specified, write 80h to the command register. Unless thiscommand has been preceded by a PROGRAM PAGE TWO-PLANE (80h-11h) command,issuing the 80h to the command register clears all of the cache registers' contents on theselected target. Write five address cycles containing the column address and row ad-dress; data input cycles follow. Serial data is input beginning at the column addressspecified. At any time during the data input cycle, the RANDOM DATA INPUT (85h) andPROGRAM FOR INTERNAL DATA INPUT (85h) commands can be issued. When datainput is complete, write 11h to the command register. The selected die (LUN) will gobusy (RDY = 0, ARDY = 0) for t DBSY.To determine the progress of t DBSY, the host can monitor the target's R/B# signal or,alternatively, the status operations (70h, 78h) can be used. When the LUN's statusshows that it is ready (RDY = 1), additional PROGRAM PAGE TWO-PLANE (80h-11h)commands can be issued to queue additional planes for data transfer. Alternatively, thePROGRAM PAGE (80h-10h) or PROGRAM PAGE CACHE (80h-15h) commands can be is-sued.When the PROGRAM PAGE (80h-10h) command is used as the final command of a two-plane program operation, data is transferred from the cache registers to the NANDFlash array for all of the addressed planes during t PROG. When the die (LUN) is ready(RDY = 1, ARDY = 1), the host should check the status of the FAIL bit for each of theplanes to verify that programming completed successfully.When the PROGRAM PAGE CACHE (80h-15h) command is used as the final commandof a program cache two-plane operation, data is transferred from the cache registers tothe data registers after the previous array operations finish. The data is then movedfrom the data registers to the NAND Flash array for all of the addressed planes. This oc-curs during t CBSY. After t CBSY, the host should check the status of the FAILC bit foreach of the planes from the previous program cache operation, if any, to verify that pro-gramming completed successfully.For the PROGRAM PAGE TWO-PLANE (80h-11h), PROGRAM PAGE (80h-10h), and PRO-GRAM PAGE CACHE (80h-15h) commands, see Two-Plane Operations for two-plane ad-dressing requirements.Erase OperationsErase operations are used to clear the contents of a block in the NAND Flash array toprepare its pages for program operations.Erase OperationsThe ERASE BLOCK (60h-D0h) command, when not preceded by the ERASE BLOCKTWO-PLANE (60h-D1h) command, erases one block in the NAND Flash array. When thedie (LUN) is ready (RDY = 1, ARDY = 1), the host should check the FAIL bit to verify thatthis operation completed successfully.TWO-PLANE ERASE OperationsThe ERASE BLOCK TWO-PLANE (60h-D1h) command can be used to further systemperformance of erase operations by allowing more than one block to be erased in theNAND array. This is done by prepending one or more ERASE BLOCK TWO-PLANE (60h-D1h) commands in front of the ERASE BLOCK (60h-D0h) command. See Two-PlaneOperations for details.ERASE BLOCK (60h-D0h)The ERASE BLOCK (60h-D0h) command erases the specified block in the NAND Flasharray. This command is accepted by the die (LUN) when it is ready (RDY = 1, ARDY = 1).To erase a block, write 60h to the command register. Then write three address cyclescontaining the row address; the page address is ignored. Conclude by writing D0h to thecommand register. The selected die (LUN) will go busy (RDY = 0, ARDY = 0) for t BERSwhile the block is erased.To determine the progress of an ERASE operation, the host can monitor the target'sR/B# signal, or alternatively, the status operations (70h, 78h) can be used. When the die(LUN) is ready (RDY = 1, ARDY = 1) the host should check the status of the FAIL bit.In devices that have more than one die (LUN) per target, during and following inter-leaved die (multi-LUN) operations, the READ STATUS ENHANCED (78h) commandmust be used to select only one die (LUN) for status output. Use of the READ STATUS(70h) command could cause more than one die (LUN) to respond, resulting in bus con-tention.The ERASE BLOCK (60h-D0h) command is used as the final command of an erase two-plane operation. It is preceded by one or more ERASE BLOCK TWO-PLANE (60h-D1h)commands. All blocks in the addressed planes are erased. The host should check thestatus of the operation by using the status operations (70h, 78h). See Two-Plane Opera-tions for two-plane addressing requirements.Figure 46: ERASE BLOCK (60h-D0h) OperationI/O[7:0]RDYInternal Data Move OperationsInternal data move operations make it possible to transfer data within a device fromone page to another using the cache register. This is particularly useful for block man-agement and wear leveling. The INTERNAL DATA MOVE operation is restricted to onlywithin even blocks or only within odd blocks.The INTERNAL DATA MOVE operation is a two-step process consisting of a READ FORINTERNAL DATA MOVE (00h-35h) and a PROGRAM FOR INTERNAL DATA MOVE(85h-10h) command. To move data from one page to another, first issue the READ FORINTERNAL DATA MOVE (00h-35h) command. When the die (LUN) is ready (RDY = 1,ARDY = 1), the host can transfer the data to a new page by issuing the PROGRAM FORINTERNAL DATA MOVE (85h-10h) command. When the die (LUN) is again ready (RDY= 1, ARDY = 1), the host should check the FAIL bit to verify that this operation comple-ted successfully.To prevent bit errors from accumulating over multiple INTERNAL DATA MOVE opera-tions, it is recommended that the host read the data out of the cache register after theREAD FOR INTERNAL DATA MOVE (00h-35h) completes and prior to issuing the PRO-GRAM FOR INTERNAL DATA MOVE (85h-10h) command. The RANDOM DATA READ(05h-E0h) command can be used to change the column address. The host should checkthe data for ECC errors and correct them. When the PROGRAM FOR INTERNAL DATAMOVE (85h-10h) command is issued, any corrected data can be input. The PROGRAMFOR INTERNAL DATA INPUT (85h) command can be used to change the column ad-dress.Between the READ FOR INTERNAL DATA MOVE (00h-35h) and PROGRAM FOR INTER-NAL DATA MOVE (85h-10h) commands, the following commands are supported: statusoperation (70h) and column address operations (05h-E0h, 85h). The RESET operation(FFh) can be issued after READ FOR INTERNAL DATA MOVE (00h-35h), but the con-tents of the cache registers on the target are not valid.READ FOR INTERNAL DATA MOVE (00h-35h)The READ FOR INTERNAL DATA MOVE (00h-35h) command is functionally identical tothe READ PAGE (00h-30h) command, except that 35h is written to the command regis-ter instead of 30h.It is recommended that the host read the data out of the device to verify the data priorto issuing the PROGRAM FOR INTERNAL DATA MOVE (85h-10h) command to preventthe propagation of data errors.。

K9产品资料

1080P全高清视频播放,支持RMVB/RM/AVI/MP4/MKV/FLV等全格式解码,无需转换,直播无忧,掌上影院随身行。

●10、特色音乐厅

震撼独享个人音乐厅,天籁般的美妙音质与完美的音效组合,,全面支持MP3/WMA/APE/FLAC/AAC/OGG/WAV主流音乐格式播放

●11、个人图书馆

我的专属书房、私家图书馆,尽在掌握间。全面支持PDF、EPUB、FB2、PDB、TXT多种主流电子书格式,图书杂志期刊,轻轻松松阅读,完美真实感受!

●12、HOST功能(通过USB转接线实现)

USB2.0高速传输接口,USB HOST功能,PC、U盘、3G上网卡设备随意连接。

●13、海量应用软件支持

技术规格

显示屏

8英寸1280x768TFT显示屏, 5点电容触摸屏

CPU

ROCKCHIP 2918ARM CortexA8,主频1.2GHz

GPU:Vivante GC800

内存

DDR3-512MB

操作系统

Android2.3

内置WiFi 802.11b/g,支持3G Dongle上网卡,支持USB转ADSL线支持以太网。

完美支持FLASH 10.3、WebM VP8解码,更精彩网页浏览,更多网络游戏选择,更便利网页视频直播。

●6、多点触控

领先的触控屏技术,支持多点触摸操控,更加灵敏的响应速度,更加流畅更加完美的操控体验。

●7、视频聊天

前置摄像头设计,可视会议、可视聊天全能,带来更多精彩更多应用体验。

●8、重力感应

内置3轴重力感应技术,屏幕方向随心转动,游戏操控畅快感受,各种应用中无微不至的人性化设计,给您带来全新视觉、操控、应用等更多更强体验。

EM643FV16F系列256K x16位低功耗低电压全CMOS静态RAM产品说明书

Document Title256K x16 bit Super Low Power and Low Voltage Full CMOS Static RAMRevision HistoryRevision No. History Date Remark0.0-.Initial Draft May262003Preliminary0.1-.Add Pb-free part number Feb.1320040.2-.I SB1(Max.) changed from 12uA to 6uA.Mar.3120080.3-.Add 45ns part specification.Apr.22009-.I SB1(Typ.) changed from 1uA to 0.25uA.-.I SB1(Max.) changed from 6uA to 4uA.-.Memory Function Guide updated in the last page.Apr.72009Release1.0-.EM643FV16F(KGD), EM643FV16F series & EM643FV16FUseries are unified to EM643FV16F Family.Emerging Memory & Logic Solutions Inc.3F Korea Construction Financial Cooperative B/D, 301-1 Yeon-Dong, Jeju-Si, Jeju-Do, Rep.of Korea Zip Code : 690-717Tel : +82-64-740-1700 Fax : +82-64-740-1750 / Homepage : The attached datasheets are provided by EMLSI reserve the right to change the specifications and products. EMLSI will answer to your questions about device. If you have any questions, please contact the EMLSI office.PRODUCT FAMILY1. “xx” represents speed.2. Typical values are measured at Vcc=3.3V, T A =25o C and not 100% tested.Product FamilyOperating Temperature Vcc RangeSpeedPower DissipationPKG Type Standby (I SB1, Typ.)Operating (I CC1.Max.)EM643FV16F Industrial (-40 ~ 85o C)2.7 ~3.6 V 45/55/70 ns0.25 µA 2)3 mAKGDEM643FV16F - xx 1)LF VFBGA-48 EM643FV16FU - xx 1)LF44-TSOP2FEATURES•Process Technology : 0.18µm Full CMOS •Organization : 256K x 16 bit•Power Supply Voltage : 2.7V ~ 3.6V •Low Data Retention Voltage : 1.5V(Min.)•Three state output and TTL Compatible •Package Type : VFBGA-48, 44-TSOP2GENERAL DESCRIPTIONThe EM643FV16F families are fabricated by EMLSI’s advanced full CMOS process technology. The families support industrial temperature range and Chip Scale Package for user flexibility of system design. The families also supports low data retention voltage for battery back-up operation with low data retention current.R o w S e l e c tI/O Circuit Column SelectData ContData ContPre-charge CircuitMemory Array 2048 x 2048A1A2A3A4A5A6A7A0A8A9A11A12A13A14A15A16A17WE OE UB LB CSDQ0 ~ DQ7DQ8 ~ DQ15VCCVSSControl LogicA10FUNCTIONAL BLOCK DIAGRAMPIN DESCRIPTIONName FunctionName FunctionCS Chip Select input VCC Power Supply OE Output Enable input VSS GroundWE Write Enable input UB Upper Byte (DQ8~DQ15)A0~A17 Address inputs LB Lower Byte (DQ0~DQ7)DQ0~DQ15Data inputs/outputsNCNo ConnectionPIN CONFIGURATIONSVFBGA-48 : Top view(ball down)123456A LB OE A0A1A2NC B DQ8UB A3A4CS DQ0C DQ9DQ10A5A6DQ1DQ2D VSS DQ11A17A7DQ3VCCE VCC DQ12 NC A16DQ4VSSF DQ14DQ13A14A15DQ5DQ6G DQ15NC A12A13WE DQ7HNCA8A9A10A11NC1234567891011121314151644434241403938373635343332313029A4A3A2A1A0CS DQ0DQ1DQ2DQ3VCC VSS DQ4DQ5DQ6DQ7A5A6A7OE UB LB DQ15DQ14DQ13DQ12VSS VCC DQ11DQ10DQ9DQ844 - TSOP2171819202122282726252423WE A17A16A15A14A13NC A8A9A10A11A1244 - TSOP2 : Top viewABSOLUTE MAXIMUM RATINGS 1)1. Stresses greater than those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. Functional operation should be restricted to recommended operating condition. Exposure to absolute maximum rating conditions for extended periods may affect reliability.FUNCTIONAL DESCRIPTIONNOTE : X means don’t care. (Must be low or high state)ParameterSymbol Ratings Unit Voltage on Any Pin Relative to Vss V IN , V OUT-0.2 to 4.0V Voltage on Vcc supply relative to Vss V CC -0.2 to 4.0V Power Dissipation P D 1.0WOperating TemperatureT A-40 to 85oCCS OE WE LB UB DQ0~7DQ8~15Mode Power H X X X X High-Z High-Z Deselected Stand by X X X H H High-Z High-Z Deselected Stand by L H H L X High-Z High-Z Output Disabled Active L H H X L High-Z High-Z Output Disabled Active L L H L H Data Out High-Z Lower Byte Read Active L L H H L High-Z Data Out Upper Byte Read Active L L H L L Data Out Data Out Word Read Active L X L L H Data In High-Z Lower Byte Write Active L X L H L High-Z Data In Upper Byte Write Active LXLLLData InData InWord WriteActiveRECOMMENDED DC OPERATING CONDITIONS 1)1. TA= -40 to 85o C, otherwise specified2. Overshoot: VCC +2.0 V in case of pulse width < 20ns3. Undershoot: -2.0 V in case of pulse width < 20ns4. Overshoot and undershoot are sampled, not 100% tested.CAPACITANCE 1) (f =1MHz, T A =25o C)1. Capacitance is sampled, not 100% tested.DC AND OPERATING CHARACTERISTICS1. Typical values are measured at Vcc=3.3V, T A =25o C and not 100% tested.ParameterSymbol Min Typ Max Unit Supply voltage V CC 2.7 3.3 3.6V GroundV SS 000V Input high voltage V IH 2.2 -V CC + 0.22)V Input low voltageV IL-0.23)-0.6VItemSymbol Test ConditionMin Max Unit Input capacitance C IN V IN =0V -8pF Input/Ouput capacitanceC IOV IO =0V-10pFParameterSymbol Test Conditions Min Typ Max Unit Input leakage current I LI V IN =V SS to V CC-1-1µA Output leakage current I LO CS=V IH or OE=V IH or WE=V IL or LB=UB=V IH V IO =V SS to V CC-1-1µA Operating power supplyI CC I IO =0mA, CS=V IL , V IN =V IH or V IL --3mA Average operating currentI CC1Cycle time=1µs, 100% duty, I IO =0mA, CS<0.2V, LB<0.2V or/and UB<0.2V, V IN <0.2V or V IN >V CC -0.2V--3mAI CC2Cycle time = Min, I IO =0mA, 100% duty, CS=V IL , LB=V IL or/and UB=V IL , V IN =V IL or V IH 45ns --35mA55ns --3070ns--25 Output low voltage V OL I OL = 2.1mA--0.4V Output high voltage V OH I OH = -1.0mA2.4--V Standby Current (TTL)I SB CS=V IH , Other inputs=V IH or V IL--0.3mAStandby Current (CMOS)I SB1CS>V CC -0.2V , Other inputs = 0~V CC(Typ. condition : V CC =3.3V @ 25o C) (Max. condition : V CC =3.6V @ 85o C)LL LF-0.25 1)4µAAC OPERATING CONDITIONSTest Conditions (Test Load and Test Input/Output Reference)Input Pulse Level : 0.4 to 2.2V Input Rise and Fall Time : 5nsInput and Output reference Voltage : 1.5VOutput Load (See right) : CL 1) = 100pF+ 1 TTL(70ns) CL 1) = 30pF + 1 TTL(45ns/55ns)1. Including scope and Jig capacitance2. R 1=3070Ω, R 2=3150Ω3. V TM =2.8V4. CL = 5pF + 1 TTL (measurement with tLZ, tOLZ, tHZ, tOHZ, tWHZ)READ CYCLE (V cc =2.7 to 3.6V, Gnd = 0V, T A = -40o C to +85o C)WRITE CYCLE (V cc =2.7 to 3.6V, Gnd = 0V, T A = -40o C to +85o C)ParameterSymbol45ns 55ns70nsUnitMin Max Min Max Min Max Read cycle time t RC 45-55-70-ns Address access time t AA -45-55-70ns Chip select to output t CO -45-55-70ns Output enable to valid output t OE -20-25-35ns UB, LB acess time t BA 20 25 35ns Chip select to low-Z output t LZ 10-10-10-ns UB, LB enable to low-Z output t BLZ 5-5-5-ns Output enable to low-Z output t OLZ 5-5-5-ns Chip disable to high-Z output t HZ 020020025ns UB, LB disable to high-Z output t BHZ 020020025ns Output disable to high-Z output t OHZ 020020025ns Output hold from address changet OH10-10-10-nsParameterSymbol45ns 55ns70nsUnitMin Max Min Max Min Max Write cycle timet WC 45-55-70-ns Chip select to end of write t CW 35-45-60-ns Address setup time t AS 0-0-0-ns Address valid to end of write t AW 35-45-60-ns UB, LB valid to end of write t BW 35-45-60-ns Write pulse width t WP 35-40-55-ns Write recovery time t WR 0-0-0-ns Write to ouput high-Z t WHZ 0202025nsData to write time overlap t DW 25 25 30 ns Data hold from write time t DH 0-0-0-ns End write to output low-Zt OW5-5-5-nsCL 1)V TM 3)R 12)R 22)t RCAddressCSUB,LBOEData Outt COt OHt BAt OEHigh-Zt BHZt OHZTIMING WAVEFORM OF READ CYCLE(2) (WE = V IH )Data Validt OLZt BLZ t LZt AAt HZt RCAddresst AA Data Validt OHPrevious Data ValidTIMING WAVEFORM OF READ CYCLE(1) (Address Controlled, CS=OE=V IL , WE=V IH, UB or/and LB =V IL )Data OutTIMING DIAGRAMSNOTES (READ CYCLE)1. t HZ and t OHZ are defined as the outputs achieve the open circuit conditions and are not referenced to output voltage levels.2. At any given temperature and voltage condition, t HZ (Max.) is less than t LZ (Min.) both for a given device and from device to device interconnection.t WR (4)t WCAddressCSUB,LBWEData inData outt CW (2)t AW t BWt WP (1)t AS (3)High-Zt DWt DHHigh-Z t OWt WHZData UndefinedTIMING WAVEFORM OF WRITE CYCLE(1) (WE Controlled)Data Validt WCAddressCSUB,LBWEData inData outt CW (2)t WR (4)t BWt WP (1)t DWt DHTIMING WAVEFORM OF WRITE CYCLE(2) (CS Controlled)tAS(3)High-Z High-ZData Validt AWt WCAddressCSUB,LBWEData in Data outt CW (2)t WR (4)t BWt WP (1)t DWt DHTIMING WAVEFORM OF WRITE CYCLE(3) (UB, LB Controlled)High-ZHigh-ZData Validt AS (3)NOTES (WRITE CYCLE)1. A write occurs during the overlap(t WP ) of low CS and low WE. A write begins when CS goes low and WE goes low with asserting UB or LB for single byte operation or simultaneously asserting UB and LB for double byte operation. A write ends at the earliest transition when CS goes high and WE goes high. The t WP is measured from the beginning of write to the end of write.2. t CW is measured from the CS going low to end of write.3. t AS is measured from the address valid to the beginning of write.4. t WR is measured from the end or write to the address change. t WR applied in case a write ends as CS or WE going high.t AWDATA RETENTION CHARACTERISTICSNOTES1. See the I SB1 measurement condition of datasheet page 5.2. Typical values are measured at T A =25o C and not 100% tested.ParameterSymbolTest ConditionMinTyp 2)MaxUnitV CC for Data Retention V DR I SB1 Test Condition (Chip Disabled) 1)1.5- 3.6V Data Retention CurrentI DR V CC =1.5V, I SB1 Test Condition (Chip Disabled) 1)-0.5-µAChip Deselect to Data Retention Time t SDR See data retention wave form0--nsOperation Recovery Timet RDRt RC--t SDRt RDRData Retention ModeCS > Vcc-0.2VV cc 2.7V2.2V V DRCS GNDDATA RETENTION WAVE FORMPACKAGE DIMENSION44 - TSOP2 (0.8mm pin pitch)Unit : millimeters / inchesAB CD E F G H654321DVFBGA 48 BALLS (6X7X1 0.75mm ball pitch)M Min.NOR.Max.A ---1A10.220.32A20.21 REF A30.45 REF b 0.32 5.250.42D 6 BSCE 7 BSC e 0.75 BSC D10.35 BSC E15.25 BSCNOTES.1). DIMENSION b IS MEASURED AT THE MAXIMUM SOLDER BALL DIAMETER, PARALLEL TO DATUM PLANE Z.2). DATUM Z (SEATING PLANE) IS DEFINED BY THE SPHERICAL CROWNS OF THE SOLDER BALLS.3). PARALLELISM MESUREMENT SHALL EXCLUDE ANY EFFECT OF MARK ON TOP SURFACE OF PACKAGE.DETAIL KA1 CORNERUnit: millimetersA1 CORNERXE Y0.1 ZE17X ee/2e/25X eD148X b 1)0.15 M Z X Y 0.08 M ZDETAIL KM0.08 ZZ0.1 ZAA1(A2)(A3)SEATING PLANE2)3)MEMORY FUNCTION GUIDE1. Memory Component8. VersionBlank---------------Mother die2. Device Type A ---------------2 nd generation 6---------------Low Power SRAM B ---------------3 rd generation 7---------------STRAM C ---------------4 th generation C ---------------CellularRAM D ---------------5 th generation E ---------------6 th generation3. Density F ---------------7 th generation 1--------------- 1MG ---------------8 th generation 2--------------- 2M 4--------------- 4M 9. Package8--------------- 8M Blank---------------KGD, FBGA 16--------------- 16M S ---------------32 sTSOP132--------------- 32M T ---------------32 TSOP164--------------- 64M U ---------------44 TSOP228---------------128MV ---------------32 SOP 4. Option 10. Speed 0---------------Dual CS (x8)45--------------- 45ns 1---------------Single CS (x8)55--------------- 55ns 3---------------Single CS / tBA=tOE (x16)60--------------- 60ns 4---------------Single CS / tBA=tCO (x16)70--------------- 70ns 5---------------Dual CS / tBA=tOE (x16)85--------------- 85ns 6---------------Dual CS / tBA=tCO (x16)90--------------- 90ns 10---------------100ns 5. Technology 12---------------120nsF ---------------Full CMOS 11. Power 6. Operating Voltage LL ---------------Low Low PowerT ---------------5.0V LF ---------------Low Low Power(Pb-free & Green)V ---------------3.3V L ---------------Low PowerU ---------------3.0V S ---------------Standard PowerS ---------------2.5V R ---------------2.0V P ---------------1.8V 7. Organization 8--------------- X8 bit 16---------------X16 bit 32---------------X32 bitEMX XX XXX XX XX -XX XX1. EMLSI Memory2. Device Type 11. Power3. Density 10. Speed4. Function 9. Package5. Technology 8. Version6. Operating Voltage7. Organization。

立拍即享!新一代东芝FlashAir体验

对于看一款SD卡产品而言,最好的升级莫过于读写性能的提升,全新第四代FlashAir SD卡在读写性能上的表现是相当出色的,这对于喜欢拍摄高清视频的玩家而言绝对是非常好的消息。

同时,全新的Eyefi连接技术可有效避免无线传输时相机自动关闭,保证稳定快捷的数据传输,也具有非常不错的实用性,的确是非常不错的数码伴侣。

工程师点评DETAILS 参数表存储容量:32GB 读取速度:90MB/s 写入速度:70MB/s 参考价格:179元东芝存储400-699-9925EXPERIENCE立拍即享!新一代东芝Flash Air体验118119清爽的蓝白CP东芝FlashAir SD卡的意义在于为单反相机等设备自主提供WiFi无线传输能力,便于使用智能手机或平板电脑等设备来直接查看、传输并分享所拍摄的照片。

从2012年推出第一代产品至今已经有六个年头,新一代东芝Flash Air 32GB准确地说应该算是第四代产品,成熟的产品系列让市场消费者对于这款产品颇感熟悉,依旧是蓝白CP的经典外观设计,而我们拿到这款产品时,才刚刚进行了APP的升级。

第四代FlashAir SD卡改用全新包装,包装盒以及SD卡本体都是以深蓝白色为主色调,清爽的设计风格非常养眼。

包装设计上提供了一个透明卡壳,便于用户在日常使用放置产品时保护好SD卡金手指。

除了蓝白色调和细心的保护壳设计外,东芝FlashAir SD卡的外包装上印有产品重要的资料信息:支持USH-I速度规格,全新第四代FlashAir SD卡写入速度升级至70MB/s,读取速度升级至90MB/s,这样的性能规格已经能够同EXCERIA PRO极至超速SD卡看齐了。

而在蓝白相间的SD卡上,最显眼的就是FlashAir字样,同时,还标明该产品支持UHS-I传输规格并具有U3高速等级和class 10的速度等级。

显然,对于产品性能是非常有信心的。

多种规格可选作为一款通用性SD卡产品,东芝FlashAir SD卡在体积上与普通SD卡并没有任何区别,该卡提供16GB、32GB和64GB三种规格可选,用户可根据个人使用情况选择相应容量的产品,而作为全新升级产品,此存储卡的读取速度已经提升至90MB/s,写入速度提升至70MB/s,它支持4K视频拍摄。

飞思卡尔K60入门资料课件

将JTAG调试器连接到计算 机,并下载和安装相应的 驱动程序。

打开Keil MDK-ARM软件 ,创建一个新项目,选择 正确的芯片型号(K60), 并配置项目属性,如工作 空间、工具链等。

使用串口通信线将开发板 与计算机连接起来,以便 在开发过程中进行调试和 数据传输。

使用Keil MDK-ARM软件 编写代码,并进行编译和 调试。

K60在图像处理中的应用

K60芯片具有高速的图像处理能力,可以用于实现各种图像处理算 法,如图像增强、目标检测、人脸识别等。

图像处理实例代码

提供一些基于K60芯片的图像处理实例代码,包括图像增强、目标 检测等。

通信系统实例

通信系统概述

通信系统是实现信息传输和交换的技术体系,包括无线通信、有 线通信、卫星通信等。

软件问题及解决方案

总结词

软件问题通常涉及到编程环境、编译错误、烧录程序等,需要检查软 件配置和代码错误。

编程环境配置

确保你使用的编程环境(如IAR Embedded Workbench、Keil uVision等)已正确配置,包括驱动程序安装、工具链设置等。

编译错误

检查代码是否有语法错误或逻辑错误,仔细阅读编译器给出的错误提 示,定位并修复问题。

K60在通信系统中的应用

K60芯片具有高速的通信接口和强大的数据处理能力,可以用于实 现各种通信系统,如无线通信网络、卫星通信系统等。

通信系统实例代码

提供一些基于K60芯片的通信系统实例代码,包括无线通信网络协 议栈的实现、卫星通信系统的数据处理等。

05

K60芯片常见问题及解决方案

硬件问题及解决方案

开发环境常见问题及解决方案

1. Keil MDK-ARM软件安装问题:确保从官方网 站下载正确的版本,并按照安装向导进行操作。 如果遇到问题,可以查阅Keil官方文档或寻求技 术支持。

(NXPowerLite) 闪存培训ppt -514

精美水晶视觉外壳,挂饰更显个性 清新的造型为工作学习注入活力 COB封装,深度防水防摔

苹果型

幸运草型

手机小U

旋彩型

安全系列

安全系列 个人与企业信息数据移动

存储全方位安全解决方案

数据加密

防病毒、防木马

安全备份

国密安全U盘

首款采用国密认证硬件加密芯片的安全U盘

国密标准,限次锁定——高强度国密标准加密技术, 10次密码输入错误U盘将被自动锁定,无法暴力破解。 10次密码问题输入错误,文件自毁。 高速引擎,硬件加密——强力加密,加密芯片、主控 芯片与Flash芯片ID号绑定,全数据流加密。 即插即用,操作简易——无需安装任何软件或驱动, 连接电脑自动进入加密界面,界面亲和易懂好操作。

加密算法 加密速度 安全性

易用性

爱国者国密U盘

普通软件加密型U盘

国密算法,256bit硬件加密引擎, 全数据流加密

低级算法,部分数据加密

普通认证型U盘(认证型) 仅做扇区保护处理,数据不加密

快(与U盘正常传输速度一致)

极慢(一般1G文件约30分钟) 无加密

国密级,密码限次锁盘 OTP因子,主控、flash、加密引擎 相互绑定,更换主控无法识别 防探针攻击,读USB数据流也无法 分析

价比首选品牌”、“最喜爱品牌”。

爱国者U盘荣获《电脑报》读者调查“市场占有率第一”和“读者首选品牌”奖。

爱国者U盘荣获《消费电子世界》“明星产品奖”、“编辑推荐奖”、“闪存盘最佳服

务品牌”、“读者首选闪存盘品牌”。

爱国者U盘荣获《中国计算机报》“读者首选品牌” 爱国者U盘荣获《T3世界发明》“我最喜爱的电子产品”奖。

可通过不断尝试密码暴力破解

mk9019f的规格书

mk9019f的规格书MK9019F芯片是一款高性能的微控制器芯片,具有广泛的应用范围和出色的功能特性。

本文将从MK9019F的概述、技术规格、应用领域和未来发展趋势等方面进行详细介绍,以帮助读者更全面地了解这款产品。

一、概述MK9019F是一款基于ARM架构的32位微控制器芯片,由一家知名芯片设计公司研发生产。

该芯片采用先进的制造工艺和设计理念,具有高性能、低功耗、稳定性好等特点,适用于各种嵌入式系统和智能设备。

MK9019F作为一款通用型的芯片,可以广泛应用于工业控制、智能家居、汽车电子、物联网等领域。

二、技术规格1.处理器核心:ARM Cortex-M4F2.主频:100MHz3.存储器:Flash存储器32KB,RAM存储器8KB4.通信接口:UART、SPI、I2C5. ADC/DAC:12位ADC,8位DAC6.工作温度:-40℃~85℃7.电源电压:3.3V8.封装形式:LQFP48MK9019F的技术规格表明了其在处理能力、存储容量、通信能力等方面的优势,能够满足各种复杂应用场景的需求。

三、应用领域1.工业控制:MK9019F在工业控制领域应用广泛,可以作为PLC、电机控制器、传感器接口等设备的核心控制单元,实现工业自动化生产。

2.智能家居:MK9019F支持多种通信接口,可用于智能家居设备的控制与联网,如智能门锁、智能插座、智能照明等。

3.汽车电子:MK9019F具有高速处理能力和丰富的接口资源,可用于汽车电子系统中的控制器、仪表盘、车载娱乐等功能。

4.物联网:MK9019F小巧灵活,适合用于物联网设备中,如智能传感器、智能监控、智能终端等应用。

MK9019F在各个领域都有广泛的应用前景,其强大的性能和可靠性为各种智能设备的研发提供了强大的支持。

四、未来发展趋势随着科技的不断进步和市场的快速发展,MK9019F芯片将不断优化和升级,以满足新一代智能设备对性能和功能的需求。

未来,MK9019F 可能会加强功耗管理、数据处理速度、通信稳定性等方面的能力,以应对日益复杂的应用场景。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

闪速存储器芯片K9F6408系列的典型应用

摘要96408系列是8×8的型闪速存储器。

它以其快速读写循环,数据硬件保护,可擦除,口命令地址数据线复用和接口便利等特点,正成为大型数据如语音、数字图像、文件等系统数据的载体。

本文给出了9640800与单片机8752的硬件连接电路及闪速存储器操作的软件应用程序。

关键词存储器;扇区;操作;应用程序

1、概述

存储器是计算机外围产品的重要组成部分,在经历了,和和如今已到了闪速存储器的时代。

存储器以其低成本,高可靠性的读写,非易失性,可擦写性和操作简便而成为一系列程序代码应用软件和数据用户文件存储的理想媒体,从而受到到嵌入式系统开发者的欢迎。

存储器的应用范围极广,从现代计算机优盘到嵌入式系统中取代的地位,可谓占尽风流。

正因为的应用广泛,了解和掌握的相关操作和管理技术就极为重要。

大致说来操作包括检错对内部坏扇区的检测、写操作写入数据、读操作从中读出数据、空间管理和擦除操作。

在系统中我们选用8752单片机,它有24个口,其中8个作为有特殊功能的口,因此只剩16个口可供一般的输入输出使用。

我们选用9640800闪存的主要原因是它能节约口,即它的地址线和数据线可复用。

而其他许多闪存的地址线和数据线是分开使用的。

因此,本文以公司的9640800为例,介绍的操作技术。

2、9640800芯片的性能特点

·供电电压27~36

·该芯片容量为66,由1024块组成,每块又由16页组成,一页共有512+16×8。

使用64,另外还有2的闲置储存空间。

·写和读以页为单位,而擦除以块为单位。

读、写和擦除操作均通过命令完成,非常方便。

参见图3

·此芯片可擦写1百万次,掉电数据不丢失,数据可保存十年。

·有8位串行口,且可复用,既可作为地址和数据的输入输出引脚,又可作命令的输入引脚,根据时序采用分时循环。

见时序图5

·写入每页的时间为200,平均每写一个字节约400,即约20。

·该的每一个扇区又分为三个区256字节,256字节和16字节,如果需要对这三个区独立操作,则通过00,01和50命令分别选中。

参见图3

·快速的读写循环和数据硬件保护。

引脚分布、功能及操作命令如图1所示

3、8752与964080的应用电路

我们设计了一个系统,所需实现的功能是,由8752单片机将接收到的芯片发送的数据,按一定的格式处理后,存储到芯片上。

当上位机发出读命令时,8752再从中取出数据,发给上位机。

在此,我们给出了964080的芯片与8752单片机连接图图2。

4、964080的软件编程

964080的软件编程是采用语言中嵌入汇编来完成。

主要包括扇区检错,读,写,擦除和管理空间。

1检错刚出厂的中可能存在坏扇区,用久的好扇区也可能变坏。

为了保证读写数据的可靠性,必须对扇区进行检测。

扇区的好坏标志存在于第3区中的第6,若扇区已坏,则标志位数据不是。

设置一错误扇区的表,扫描检错,将坏扇区的号依次填入表中,将此表保存于存储器中的第一个块中因为确保第一个块能正确使用。

流程图图四

2读分三个区,命令000,001和050可分别读取第一,二,三区中的数据。

过程为选中,通过口写入读命令字,写入所读数据地址,置读信号有效下跳

沿有效。

读写时序图如下

具体程序如下

{

;

_=0;片选

000;写读的命令

000,0;写读的地址

=0;!=2;++一次读两页

{

=528;每个扇区有528个字节

!_当读信号无效时,等待

{

}

当不为0时,就继读;否则就停止读

{

_=0;准备好读入

#嵌入汇编,插入2个机器周期

#结束汇编

=0;把0口读出的值存入寄存器

#嵌入汇编,插入2个机器周期

#结束汇编

_=1;不再读入

;串口发送数据

--;

}

}

_=1;不再片选

}

3写和读操作不一样的是,写操作有两个命令字080和010,写入080后,表示将向寄存器中写入数据,如果再键入010则中的控制器将寄存器的数据存储到数据存储器中。

写操作时,将欲写入数据的地址与错误扇区表相对照,看是否在表中。

如果在表中,则将页指针地址加十六即换到下一个中,再对照,循环操作直到找到不在表中的地址。

以此保证所写的地址都是有效地址。

具体过程选中,通过口写入写命令字,写入所要编程数据地址,置写信号有效。

写时序见图五

*与记录坏块的表相对照的子程序

{

=0;

!=+1是无效块的总数

{

!=*++当未遍历到最后一个无效块时,就继续核对

{

++;

}

}

!=+2

1;无效的块

0;有效的块

}

写操作

{

;

当开始对一页进行写操作时,=1,否则为0

{

_=0;片选

080;写命令080

*16与记录坏块的表相对照

000,;写地址

=0;

}

=0;!=16;++

[];写入寄存器处理好的数据

当寄存器中数据满528字节1页时,=1,否则为0 {

010;将数据写入

!_等待读信号有效

>

{

}

070;读状态量

10;

_=0;准备好读入

#嵌入汇编,插入两个机器周期

#结束汇编

=0;

=&001;

_=1;

!=0若最后一位不为零

{

*+=16;存储无效块空间的首地址

=+16;读下一个块的第一个扇区看是否是有效的扇区}

_=1;结束片选

++;写下一页

=1;

}

}

4擦除以块为单位进行擦除。

前后有两条擦除命令以保证不会被意外擦除。

{

;

_=0;片选

=0;!=;++寻找被擦除的块

{

060;块擦除预命令

16*;

00;块擦除确认命令

_!=1

{

}

070;读擦除状态命令

10;

_=0;

#嵌入汇编,插入3个机器周期

#结束汇编

=0;

#嵌入汇编,插入1个机器周期

#结束汇编

_=1;

=&001;

!=0擦除失败

{

*=;记录坏的块

++;

++;

}

}

_=1;不再片选

}

5管理主要包括记录无效的块,空间检测以及空间的整理。

在此以整理流程图为例

1开始整理程序;2扫描整个物理空间,取得已使用的扇区数;3从第个已使用的扇区读起,初始化=1;4看扇区的地址是否连续;5如果连续就读下一个扇区,如果读到最后一个已使用的扇区就结束;6如果不是最后一个已使用的扇区,就跳到步骤3;7如果物理扇区不连续,则取得此扇区所在块的地址指针;8扫描到空闲块并取得其地址指针;9将中所有的已写扇区移至中,擦除块;10擦除有效吗11若无效则将此块记为无效块,并进行12步;12若有效则判断读到最后一个扇区了吗?13若没有跳至步骤3;14若是最后一个已写扇区,则结束整理程序。