实验五VerilogHDL设计简单门电路

中文版VerilogHDL简明教程

Verilog HDL是一种硬件描述语言,用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模。

被建模的数字系统对象的复杂性可以介于简单的门和完整的电子数字系统之间。

数字系统能够按层次描述,并可在相同描述中显式地进行时序建模。

Verilog HDL 语言具有下述描述能力:设计的行为特性、设计的数据流特性、设计的结构组成以及包含响应监控和设计验证方面的时延和波形产生机制。

所有这些都使用同一种建模语言。

此外,Verilog HDL 语言提供了编程语言接口,通过该接口可以在模拟、验证期间从设计外部访问设计,包括模拟的具体控制和运行。

Verilog HDL语言不仅定义了语法,而且对每个语法结构都定义了清晰的模拟、仿真语义。

因此,用这种语言编写的模型能够使用Verilog仿真器进行验证。

语言从C编程语言中继承了多种操作符和结构。

Verilog HDL提供了扩展的建模能力,其中许多扩展最初很难理解。

但是,Verilog HDL语言的核心子集非常易于学习和使用,这对大多数建模应用来说已经足够。

当然,完整的硬件描述语言足以对从最复杂的芯片到完整的电子系统进行描述。

历史Verilog HDL语言最初是于1983年由Gateway Design Automation公司为其模拟器产品开发的硬件建模语言。

那时它只是一种专用语言。

由于他们的模拟、仿真器产品的广泛使用,Verilog HDL 作为一种便于使用且实用的语言逐渐为众多设计者所接受。

在一次努力增加语言普及性的活动中,Verilog HDL语言于1990年被推向公众领域。

Open Verilog International (OVI)是促进Verilog发展的国际性组织。

1992年,OVI决定致力于推广Verilog OVI标准成为IEEE标准。

这一努力最后获得成功,Verilog 语言于1995年成为IEEE标准,称为IEEE Std 1364-1995。

基于VerilogHDL的通信系统设计第4章简单逻辑电路实现.ppt

在数据结构中,线性结构主要有线性表、栈和队列。FIFO (先进先出)队列是一种常见的内存单元,其特点是:写入操 作在队列的一端,而读出操作要在队列的另一端进行。

基于Verilog HDL的通信系统设计

4-4 本章小结

本章通过对一些简单的组合逻辑电路和时序逻辑电路的介绍, 使读者对简单数字电路实现有了一定的认识,为后续章节复杂数 字逻辑电路的设计打下了基础。本章的例子具有一定的参考价值, 可以直接引用到其它数字系统设计中,读者应该从本章的范例中 体会数字电路的描述方法,熟悉简单的数字电路的实现原理。

4-2-5 串并转换电路

在数字元通信系统中常常需要将串行数据流转化成并行数据流 或将并行数据流转化成串行数据流来处理,常常需要串并或并串电 路完成以上转换过程。串并转换电路就主要用于将多位串行输入数 据转换为一路并行输出数据,它的实现方式有很多种,可以采用移 位寄存器或采用状态机来实现串并转换功能。

基于Verilog HDL的通信系统设计

4-1-5 全加器

全加器与半加器的区别是:全加器有三个输入埠,其中, 有两个输入埠和半加器相同,唯一不同的是增加了低位二进制 数相加输出到本位的进位信号。全加器可以通过真值表化简获 得输入信号和输出信号的逻辑表达式,利用基本门电路实现; 可以通过半加器的级联方式实现,本例采用半加器的级联实现 全加器的功能。

基于Verilog HDL的通信系统设计

4-2-4 计数器

在数字系统中,计数器不但可以统计输入脉冲个数,进行计时 和计数,而且还可以实现信号分频、定时、产生节拍脉冲和脉冲序 列等,其应用极其广泛。一般计数器包含:同步计数器、异步计数 器、加法减法计数器以及可逆计数器等。一般的时序逻辑很容易实 现计数功能。

可编程逻辑器件实验报告

一、实验目的通过本次实验,使学生掌握可编程逻辑器件(FPGA)的基本原理和操作方法,了解其结构特点和应用领域。

通过实验,培养学生动手实践能力和创新意识,提高学生运用FPGA进行数字系统设计和验证的能力。

二、实验原理可编程逻辑器件(FPGA)是一种高度集成的数字电路,具有可编程性、可扩展性和可重用性。

FPGA主要由可编程逻辑单元、可编程互连资源、时钟管理单元、I/O单元等组成。

通过编程,用户可以根据自己的需求定制FPGA内部逻辑结构,实现各种数字电路功能。

FPGA编程通常采用硬件描述语言(HDL),如VHDL或Verilog。

HDL描述了电路的功能和结构,通过编译和综合,生成FPGA内部的逻辑资源分配和互连关系。

实验中,我们将使用Quartus II软件进行FPGA编程和仿真。

三、实验内容1. FPGA基础操作(1)安装Quartus II软件,熟悉软件界面和基本操作。

(2)搭建FPGA实验平台,包括FPGA开发板、电源、连接线等。

(3)将FPGA开发板连接到计算机,进行硬件初始化和配置。

2. FPGA编程(1)使用VHDL或Verilog语言编写实验程序,实现简单的数字电路功能,如全加器、编码器、译码器等。

(2)将编写好的程序导入Quartus II软件,进行编译和综合。

(3)观察编译报告,检查程序语法错误和资源占用情况。

(4)进行仿真,验证程序功能是否正确。

3. FPGA下载与验证(1)将编译后的程序下载到FPGA芯片中。

(2)使用示波器或逻辑分析仪等工具,观察FPGA输出的波形,验证程序功能。

(3)根据实验要求,修改程序参数,优化电路性能。

四、实验步骤1. 搭建实验平台(1)将FPGA开发板连接到计算机,确保所有连接线正确。

(2)检查电源电压,确保FPGA芯片供电正常。

2. 编写程序(1)打开Quartus II软件,创建新工程。

(2)选择合适的HDL语言,编写实验程序。

(3)保存程序,并添加到工程中。

verilog中一些基本的门电路如pmos和nmos等

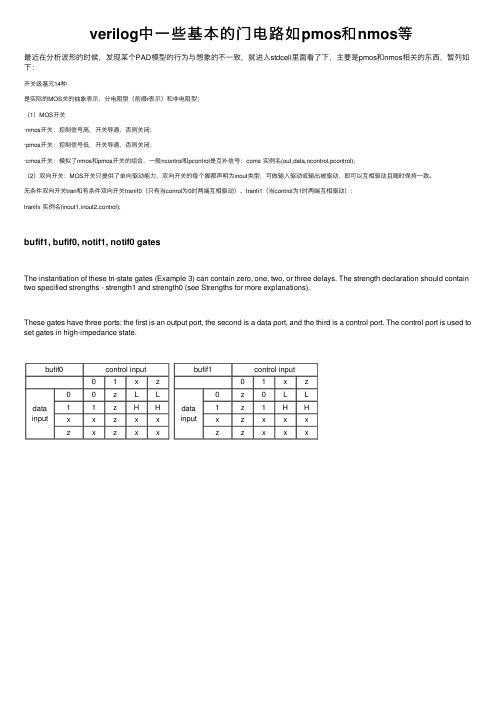

verilog中⼀些基本的门电路如pmos和nmos等最近在分析波形的时候,发现某个PAD模型的⾏为与想象的不⼀致,就进⼊stdcell⾥⾯看了下,主要是pmos和nmos相关的东西,暂列如下:开关级基元14种是实际的MOS关的抽象表⽰,分电阻型(前缀r表⽰)和⾮电阻型;(1)MOS开关·nmos开关:控制信号⾼,开关导通,否则关闭;·pmos开关:控制信号低,开关导通,否则关闭;·cmos开关:模拟了nmos和pmos开关的组合,⼀般ncontrol和pcontrol是互补信号:coms 实例名(out,data,ncontrol,pcontrol);(2)双向开关:MOS开关只提供了单向驱动能⼒,双向开关的每个脚都声明为inout类型,可做输⼊驱动或输出被驱动,即可以互相驱动且随时保持⼀致。

⽆条件双向开关tran和有条件双向开关tranif0(只有当conrol为0时两端互相驱动)、tranfi1(当control为1时两端互相驱动):tranifx 实例名(inout1,inout2,control);bufif1, bufif0, notif1, notif0 gatesThe instantiation of these tri-state gates (Example 3) can contain zero, one, two, or three delays. The strength declaration should contain two specified strengths - strength1 and strength0 (see Strengths for more explanations).These gates have three ports: the first is an output port, the second is a data port, and the third is a control port. The control port is used to set gates in high-impedance state.bufif0control input01x zdata input 00z L L11z H Hx x z x xz x z x xbufif1control input01x zdatainput0z0L L1z1H Hx z x x xz z x x x。

verilog实验报告

verilog实验报告Verilog实验报告引言:Verilog是一种硬件描述语言(HDL),用于设计和模拟数字电路。

它是一种高级语言,能够描述电路的行为和结构,方便工程师进行数字电路设计和验证。

本实验报告将介绍我在学习Verilog过程中进行的实验内容和所获得的结果。

实验一:基本门电路设计在这个实验中,我使用Verilog设计了基本的逻辑门电路,包括与门、或门和非门。

通过使用Verilog的模块化设计,我能够轻松地创建和组合这些门电路,以实现更复杂的功能。

我首先创建了一个与门电路的模块,定义了输入和输出端口,并使用逻辑运算符和条件语句实现了与门的功能。

然后,我创建了一个测试模块,用于验证与门的正确性。

通过输入不同的组合,我能够验证与门的输出是否符合预期。

接下来,我按照同样的方法设计了或门和非门电路,并进行了相应的测试。

通过这个实验,我不仅学会了使用Verilog进行基本门电路的设计,还加深了对逻辑电路的理解。

实验二:时序电路设计在这个实验中,我学习了如何使用Verilog设计时序电路,例如寄存器和计数器。

时序电路是一种具有状态和时钟输入的电路,能够根据时钟信号的变化来改变其输出。

我首先设计了一个简单的寄存器模块,使用触发器和组合逻辑电路实现了数据的存储和传输功能。

然后,我创建了一个测试模块,用于验证寄存器的正确性。

通过输入不同的数据和时钟信号,我能够观察到寄存器的输出是否正确。

接下来,我设计了一个计数器模块,使用寄存器和加法电路实现了计数功能。

我还添加了一个复位输入,用于将计数器的值重置为初始状态。

通过测试模块,我能够验证计数器在不同的时钟周期内是否正确地进行计数。

通过这个实验,我不仅学会了使用Verilog设计时序电路,还加深了对触发器、寄存器和计数器的理解。

实验三:组合电路设计在这个实验中,我学习了如何使用Verilog设计组合电路,例如多路选择器和加法器。

组合电路是一种没有状态和时钟输入的电路,其输出只取决于当前的输入。

合工大FPGA实验报告

《电子工程师基本硬件实践技能训练(下)》实验报告系(院):计算机与信息学院专业:通信工程班级:姓名:学号:指导教师:许良凤吴从中周红平学年学期: 2018 ~ 2019 学年第一学期2018年12月23日实验一 7段数码显示译码器设计一、实验目的(1)学习使用Verilog HDL语言设计简单组合逻辑电路。

(2)学习使用case语句来描述真值表。

二、实验设备与器材GW-PK2 EDA实验箱一台。

三、实验内容及实验步骤(1)用Verilog HDL设计一个共阴数码管的译码电路,用case语句描述7段译码器的真值表。

(2)编译、综合、适配、下载,验证结果。

(3)进行功能仿真。

(4)设计提示:建议选实验电路模式6,用数码8显示译码输出(PIO46~PIO40),键8、键7、键6、键5四位控制输入,硬件验证译码器的工作性能。

注意,在仿真中,4位输入都必须用总线方式给数据。

具体步骤:(1)用文本方式输入设计文件并存盘。

(2)选择目标器件并编译、综合。

(3)进行时序仿真。

(4)锁定引脚,并编译、综合。

(5)在实验箱上选择模式6。

(6)将数据下载到实验箱。

(7)在实验箱上验证7段显示数码器的功能。

实验代码如下module DECL7S (A,LED7S);input[3:0] A; output[6:0] LED7S;reg[6:0] LED7S;always@(A)case(A)4'b0000 : LED7S <= 7'B0111111;4'b0001 : LED7S <= 7'B0000110;4'b0010 : LED7S <= 7'B1011011;4'b0011 : LED7S <= 7'B1001111;4'b0100 : LED7S <= 7'B1100110;4'b0101 : LED7S <= 7'B1101101;4'b0110 : LED7S <= 7'B1111101;4'b0111 : LED7S <= 7'B0000111;4'b1000 : LED7S <= 7'B1111111;4'b1001 : LED7S <= 7'B1101111;4'b1010 : LED7S <= 7'B1110111;4'b1011 : LED7S <= 7'B1111100;4'b1100 : LED7S <= 7'B0111001;4'b1110 : LED7S <= 7'B1111001;4'b1111 : LED7S <= 7'B1110001;default : LED7S <= 7'B0111111;endcaseEndmodule2.编译、综合、适配、下载,验证结果。

Verilog-HDL电路设计

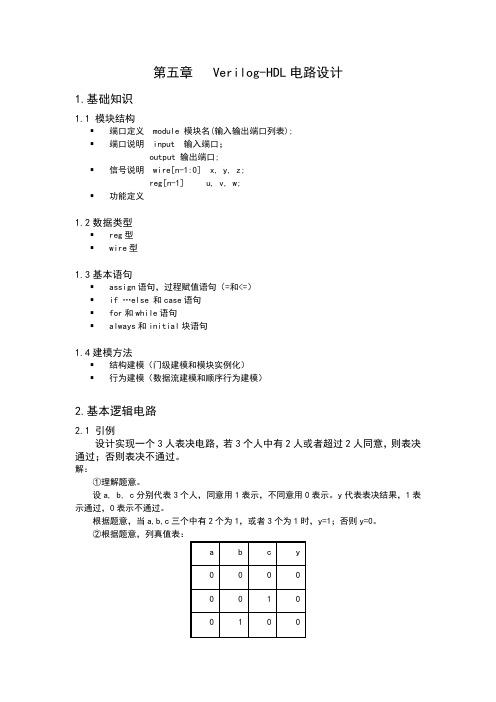

第五章 Verilog-HDL电路设计1.基础知识1.1 模块结构▪端口定义 module 模块名(输入输出端口列表);▪端口说明 input 输入端口;output 输出端口;▪信号说明 wire[n-1:0] x, y, z;reg[n-1] u, v, w;▪功能定义1.2数据类型▪ reg型▪ wire型1.3基本语句▪ assign语句,过程赋值语句(=和<=)▪if …else 和case语句▪ for和while语句▪ always和initial块语句1.4建模方法▪结构建模(门级建模和模块实例化)▪行为建模(数据流建模和顺序行为建模)2.基本逻辑电路2.1 引例设计实现一个3人表决电路,若3个人中有2人或者超过2人同意,则表决通过;否则表决不通过。

解:①理解题意。

设a, b, c分别代表3个人,同意用1表示,不同意用0表示。

y代表表决结果,1表示通过,0表示不通过。

根据题意,当a,b,c三个中有2个为1,或者3个为1时,y=1;否则y=0。

③根据真值表,列输出方程:④化简方程⑤根据化简后的方程画出电路图2.1.1 对应①建模①当a, b ,c三个中有2个为1,或者3个为1时,y=1;否则y=0. module decision_1(a,b,c,y);input a,b,c;output y;reg y;always @(a, b, c)if ((a&b==1)|(b&c==1)|(c&a==1)|(a&b&c==1))y = 1;elsey = 0;endmodule2.1.2 对应②建模②真值表module decision_2(a,b,c,y); input a,b,c;output y;reg y;always @(a, b, c)case ({a, b, c})3'b000:y = 0; 3'b001:y = 0; 3'b010:y = 0;3'b011:y = 1;3'b100:y = 0;3'b101:y = 1;3'b110:y = 1;3'b111:y = 1;endcaseendmodule2.1.3 对应③建模③根据真值表,列输出方程module decision_3(a,b,c,y);input a,b,c;output y;assign y = (~a&b&c)|(a&~b&c)|(a&b&~c)|(a&b&c);endmodule2.1.4对应④建模④化简方程module decision_4(a,b,c,y);input a,b,c;output y;assign y = (b&c)|(a&c)|(a&b);endmodule2.1.5对应⑤建模module decision_5(a,b,c,y);input a,b,c;output y;wire ab, bc, ca;and (ab, a, b),(bc, b, c),(ca ,c, a);or (y, ab, bc, ca);endmodule2.2基本组合逻辑电路数字逻辑电路就本质而言,分为组合逻辑和时序逻辑两大类。

verilog编程实例

verilog编程实例我们需要明确这个电路的功能和设计要求。

假设我们需要实现一个4位二进制加法器,即输入两个4位的二进制数,输出它们的和。

为了简化问题,我们先考虑只有无符号整数的加法,即只需要实现两个正整数的相加。

接下来,我们可以使用Verilog语言来描述这个电路的结构和行为。

我们首先声明输入端口和输出端口的位宽,即4位。

然后,我们定义一个module,命名为"binary_adder"。

在这个module中,我们定义了两个4位的输入信号a和b,以及一个4位的输出信号sum。

同时,我们还定义了一个内部信号carry,用于记录进位信息。

在module的主体部分,我们使用assign语句来实现信号之间的逻辑关系。

具体地,我们可以通过逐位相加的方式,将输入信号a和b的每一位与进位carry相加,并将结果存储在输出信号sum的对应位上。

同时,我们还需要更新进位carry的值,以确保加法运算的正确性。

为了实现这个逻辑,我们可以使用Verilog中的加法运算符"+"和逻辑与运算符"&"。

通过对输入信号的每一位进行逐位运算,我们可以得到输出信号sum的每一位的值。

同时,我们还需要根据输入信号和进位carry的值,计算出新的进位carry的值。

在实际的Verilog编程中,我们需要注意信号的声明和赋值的顺序。

一般而言,我们需要先声明信号,然后再通过assign语句对信号进行赋值。

这样可以确保信号的值能够正确传递和计算。

完成Verilog代码的编写后,我们需要使用相应的仿真工具来验证电路的功能。

常用的仿真工具有ModelSim和Xilinx ISE等。

通过仿真工具,我们可以为输入信号a和b设置不同的值,并观察输出信号sum的变化。

通过比较输出信号sum和预期的结果,我们可以验证电路的正确性。

除了验证电路的正确性外,我们还可以通过综合工具将Verilog代码转换成对应的门级电路。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验五VerilogHDL设计简单门电路

一、实验目的

1、学习非门、与门、与非门、或门、或非门、异或门和异或非门的Verilog HDL描述;

2、学习Verilog HDL程序书写方法和QuartusII功能仿真;

3、学习VerilogHDL的行为级电路设计的编写方法;

4、组合电路和时序电路的行为级描述。

二、实验内容

1、参考教材4.2,5.4节,用Verilog HDL分别设计并仿真基本门电路1位全加器f_adder.v,基本门电路如下图所示。

(分别数据流描述方式、结构描述方式或行为描述方式)

图1 1位全加器电路原理图

2、分析比较输出的波形仿真图并验证程序的正确性。

3、参考4.9,5.6节,用Verilog HDL的行为级描述方式描述如下电路图,图中MUX2为2选1数据选择器,FD11为一D触发器。

D

三、实验步骤

1、建立电路的VerilogHDL文件,进行编译,直到编译无误。

2、建立电路的波形文件,编辑输入信号。

3、运行仿真器,并验证仿真。

四、实验报告

1、编写程序

2、调试过程问题分析与解决

3、仿真结果分析。