软件总体架构图

平台架构图-产品架构图

合同管理

结算管理 数据交互

支付管理 数据分析

仓储管理

基础支撑

邮件服务 日志服务

搜索服务 消息服务

运输管理 方案推荐

安全服务 队列服务

资源层

关系型数据库

资源统一管控

非关系型数据库

分布式存储

……

服务器、网络等

数据采集层 2021/1/27

各种数据采集设备

外部系统

铁路相关系统

仓储、物流系统

开

水运、公运系统

开放平台

港务系统

质检服务

铁路内部系统 保险服务

业务服务中心

运营管控中心

仓储管理 客服管理

运输管理 多式联运 智能调度 智能改单 智能配载

业务支撑平台

物流贸易

运力调度

会员管理

结算管理

订单管理 支付管理

合同管理 运营管理

平台层

大 数 据

可 视 化 交 互

商 业 智 能

物 联 网 管 理

计算 人工智能

容器 虚拟机

操作监控 应用监控 监控大屏展示

2021/1/27

业务应用层 接口服务

客户服务中心

用户管理 权限管理 合同管理 会员管理 智能客服

运输API

资源服务中心

订单管理中心

业务服务中心

准入管理 运输交易 作业管理

信息搜索 交易撮合 订单生成 回单管理

需求发布 运输方案推荐

订单追踪

运输管理 任务指派 仓储管理 对账管理

APP

Native/H5

运营后台

HTML+JSP+Jquery +Boootstrap+CSS

层

物流电商

软件架构图编写模版

商品下单 订单管理 物流跟踪 支付结算 订单审核

订单管理 支付结算管理

震元业务人员

外部系统对接

销售渠道企业ERP

(代理商/销售商/医院)

震元企业ERP 邮政速递

邮政储蓄银行

Click to add title

资金结算流向

ThemeGallery is creating high standards of design template on the web. This professional quality design templates are made by Guild Design which has offered web design template, PowerPoint for effective presentation and flash movie. Customized to meet your needs.

潜在消 费者

汽车网上商城&

购车消 费者

汽车资讯服务平台

汽车服

汽车经 销商

汽车贷 款机构

务消费 者

支付机

构

汽车保

汽车售

后服务 商

汽车行业O2O运营平台 险机构

获取资 讯用户

运营机构

二手汽 车经销

商

用户群体

依托O2O模式下的汽车电子商服务平台实现汽车相关消费 者、汽车经销商、售后服务商、贷款、保险、金融支付

事后统计分析 实时监控

运营管理

前端表现区

PC浏览器

WEB2.0客户端

手机APP 平板电脑

POS

自助设备

手机客户端 平板电脑客户端

POS客户端 MISPOS客户端 自助设备客户端

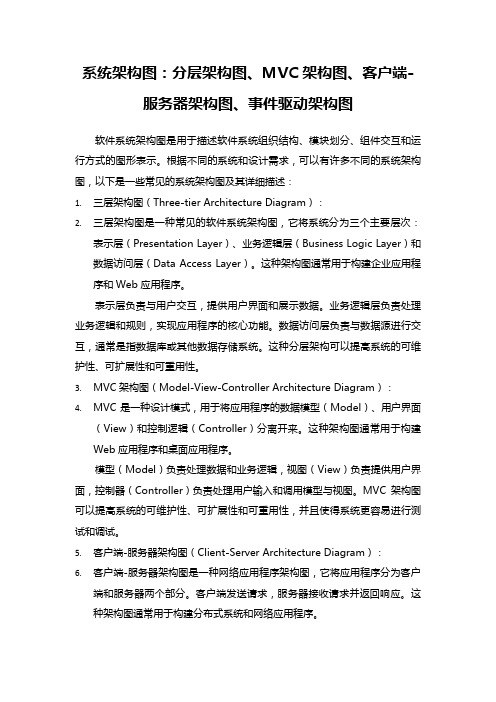

软件版本管理平台层次架构图

配置报警

报警内容 手动预警查询

自动预警 报警报表导出

基于不同数据库

SM配置 错误记录

及分析

基

标准化数据

础

数

据

数据转化层

层

全球监控数 指标工具数据 SM配置信息数 风机管家数

据源

源

据源

据源

软件版本管理平台业务数据

软件版本管理平台层次架构图

实验看板

测试结果分析 代码测试 功能测试

发布通知单管理

通知单 查询

系统 通知

线上导出 功能

回执统计

会签流程管理

标准化数据接口层

软件版本监控

机组配置管理

通用版本监控 软件版本标准

特殊版本监控

测试版本 特殊配置版

本版本

风机软件版本 映射表

版本报警

手动预警查询 自动预警

风机配置标准

风机配置文 件管理

风机基础参 数管理 配置查询

终

端 展

WEB端/介入OA管理系

示

统

层

应 用 层

业 务 逻 辑 层

回归测试管理

软件需求 管理

工单综合管理

创建 修改 续约

评审 查询 取消

ቤተ መጻሕፍቲ ባይዱ

软件版本管理

版本迭代管理

查询 下载/权限

回溯 代码上传

PC端

Android端

Ios端

综合分析

需求测试管理

软件发布管理

仿真实验管理

实验室信息 用例管理

仿真实验 预约

PLC信息

软件系统架构图-参考案例

各种软件开发系统架构图案例介绍v1.0 可编辑可修改第一章【荐】共享平台架构图与详细说明1.1.【荐】共享平台逻辑架构设计(逻辑指的是业务逻辑)注:逻辑架构图--主要突出子系统/模块间的业务关系, 这里的逻辑指的是业务逻辑如上图所示为本次共享资源平台逻辑架构图,上图整体展现说明包括以下几个方面:1 应用系统建设本次项目的一项重点就是实现原有应用系统的全面升级以及新的应用系统的开发,从而建立行业的全面的应用系统架构群。

整体应用系统通过SOA面向服务管理架构模式实现应用组件的有效整合,完成应用系统的统一化管理与维护。

2 应用资源采集整体应用系统资源统一分为两类,具体包括结构化资源和非机构化资源。

本次项目就要实现对这两类资源的有效采集和管理。

对于非结构化资源,我们将通过相应的资源采集工具完成数据的统一管理与维护。

对于结构化资源,我们将通过全面的接口管理体系进行相应资源采集模板的搭建,采集后的数据经过有效的资源审核和分析处理后进入到数据交换平台进行有效管理。

3 数据分析与展现采集完成的数据将通过有效的资源分析管理机制实现资源的有效管理与展现,具体包括了对资源的查询、分析、统计、汇总、报表、预测、决策等功能模块的搭建。

4 数据的应用最终数据将通过内外网门户对外进行发布,相关人员包括局内各个部门人员、区各委办局、用人单位以及广大公众将可以通过不同的权限登录不同门户进行相关资源的查询,从而有效提升了我局整体应用服务质量。

综上,我们对本次项目整体逻辑架构进行了有效的构建,下面我们将从技术角度对相关架构进行描述。

1.2.【荐】技术架构设计注:技术架构图 --主要突出子系统/模块自身使用的技术和模块接口关联方式如上图对本次项目整体技术架构进行了设计,从上图我们可以看出,本次项目整体建设内容应当包含了相关体系架构的搭建、应用功能完善可开发、应用资源全面共享与管理。

下面我们将分别进行说明。

1.3.【荐】系统整体架构设计(也称为系统总体架构)上述两节,我们对共享平台整体逻辑架构以及项目搭建整体技术架构进行了分别的设计说明,通过上述设计,我们对整体项目的架构图进行了归纳如下:注:系统整体/总体架构图 --主要突出从物理硬件(物理层/基础层)、数据库(数据层)、后台底层(支撑层)、业务逻辑(业务层/应用层)、UI描述(展示层)、系统用户分类(用户层),项目实施与运维管理,标准与规范体系和安全保障体系(贯穿各层的保障系统)一般我们只画大虚框内的部分就行了,外面的是说明与其他系统的对接描述,可以省略综上,我们对整体应用系统架构图进行了设计,下面我们将分别进行说明。

软件系统架构图-参考案例

各种软件开发系统架构图案例介绍第一章【荐】共享平台架构图与详细说明1.1.【荐】共享平台逻辑架构设计(逻辑指的是业务逻辑)注:逻辑架构图--主要突出子系统/模块间的业务关系, 这里的逻辑指的是业务逻辑如上图所示为本次共享资源平台逻辑架构图,上图整体展现说明包括以下几个方面:1 应用系统建设本次项目的一项重点就是实现原有应用系统的全面升级以及新的应用系统的开发,从而建立行业的全面的应用系统架构群。

整体应用系统通过SOA面向服务管理架构模式实现应用组件的有效整合,完成应用系统的统一化管理与维护。

2 应用资源采集整体应用系统资源统一分为两类,具体包括结构化资源和非机构化资源。

本次项目就要实现对这两类资源的有效采集和管理。

对于非结构化资源,我们将通过相应的资源采集工具完成数据的统一管理与维护。

对于结构化资源,我们将通过全面的接口管理体系进行相应资源采集模板的搭建,采集后的数据经过有效的资源审核和分析处理后进入到数据交换平台进行有效管理。

3 数据分析与展现采集完成的数据将通过有效的资源分析管理机制实现资源的有效管理与展现,具体包括了对资源的查询、分析、统计、汇总、报表、预测、决策等功能模块的搭建。

4 数据的应用最终数据将通过内外网门户对外进行发布,相关人员包括局内各个部门人员、区各委办局、用人单位以及广大公众将可以通过不同的权限登录不同门户进行相关资源的查询,从而有效提升了我局整体应用服务质量。

综上,我们对本次项目整体逻辑架构进行了有效的构建,下面我们将从技术角度对相关架构进行描述。

1.2.【荐】技术架构设计注:技术架构图--主要突出子系统/模块自身使用的技术和模块接口关联方式如上图对本次项目整体技术架构进行了设计,从上图我们可以看出,本次项目整体建设内容应当包含了相关体系架构的搭建、应用功能完善可开发、应用资源全面共享与管理。

下面我们将分别进行说明。

1.3.【荐】系统整体架构设计(也称为系统总体架构)上述两节,我们对共享平台整体逻辑架构以及项目搭建整体技术架构进行了分别的设计说明,通过上述设计,我们对整体项目的架构图进行了归纳如下:注:系统整体/总体架构图--主要突出从物理硬件(物理层/基础层)、数据库(数据层)、后台底层(支撑层)、业务逻辑(业务层/应用层)、UI描述(展示层)、系统用户分类(用户层),项目实施与运维管理,标准与规范体系和安全保障体系(贯穿各层的保障系统)一般我们只画大虚框内的部分就行了,外面的是说明与其他系统的对接描述,可以省略综上,我们对整体应用系统架构图进行了设计,下面我们将分别进行说明。

软件项目系统架构图

系统架构图:分层架构图、MVC架构图、客户端-服务器架构图、事件驱动架构图软件系统架构图是用于描述软件系统组织结构、模块划分、组件交互和运行方式的图形表示。

根据不同的系统和设计需求,可以有许多不同的系统架构图,以下是一些常见的系统架构图及其详细描述:1.三层架构图(Three-tier Architecture Diagram):2.三层架构图是一种常见的软件系统架构图,它将系统分为三个主要层次:表示层(Presentation Layer)、业务逻辑层(Business Logic Layer)和数据访问层(Data Access Layer)。

这种架构图通常用于构建企业应用程序和Web应用程序。

表示层负责与用户交互,提供用户界面和展示数据。

业务逻辑层负责处理业务逻辑和规则,实现应用程序的核心功能。

数据访问层负责与数据源进行交互,通常是指数据库或其他数据存储系统。

这种分层架构可以提高系统的可维护性、可扩展性和可重用性。

3.MVC架构图(Model-View-Controller Architecture Diagram):4.MVC是一种设计模式,用于将应用程序的数据模型(Model)、用户界面(View)和控制逻辑(Controller)分离开来。

这种架构图通常用于构建Web应用程序和桌面应用程序。

模型(Model)负责处理数据和业务逻辑,视图(View)负责提供用户界面,控制器(Controller)负责处理用户输入和调用模型与视图。

MVC架构图可以提高系统的可维护性、可扩展性和可重用性,并且使得系统更容易进行测试和调试。

5.客户端-服务器架构图(Client-Server Architecture Diagram):6.客户端-服务器架构图是一种网络应用程序架构图,它将应用程序分为客户端和服务器两个部分。

客户端发送请求,服务器接收请求并返回响应。

这种架构图通常用于构建分布式系统和网络应用程序。

软件总体架构图

1软件总体架构图软件结构如图1.1所示:大容量数据采集与处理程序工业以太网网关路由程序CGIBOATCP/IP操作系统界面ucLinux 内核MicroBlaze Ip 设计图1.1 FPGA 数据采集软件架构图以上是系统的软件结构框图,我们下面将就具体每一个步骤的设计进行一个简要的描述:2 MicroBlaze IP 核设计IP 字面意思是知识产权,在微电子领域,具有知识产权的功能模块成为IP Core 或IP 核。

IP 可以用来生成ASIC 和PLD 逻辑功能块,又称为虚拟器件VC 。

IP 核可以有很多种,比如UART 、CPU 、以太网控制器、PCI 接口等。

根据IP 核描述的所在集成电路的设计层次,IP 可以分为硬IP 、软IP 、固IP 。

硬IP 的芯片中物理掩膜布局已经得到证明,所有的验证和仿真工作都已经完成,用它可以直接生产硅片,系统设计者不能再对它进行修改。

而软IP 是以行为级和RTL 级的Verilog 或VHDL 代码的形式存在,它要经过逻辑综合和版图综合才能最终实现在硅片上。

固IP 则介于两者之间。

Xilinx 公司的MicroBlaze32位软处理器核是支持CoreConnect 总线的标准外设集合。

MicroBlaze 处理器运行在150MHz 时钟下,可提供125 D-MIPS 的性能,非常适合设计针对网络、电信、数据通信和消费市场的复杂嵌入式系统。

1.MicroBlaze 的体系结构MicroBlaze 是基于Xilinx 公司FPGA 的微处理器IP 核,和其它外设IP 核一起,可以完成可编程系统芯片(SOPC)的设计。

MicroBlaze 处理器采用RISC 架构和哈佛结构的32位指令和数据总线, 可以全速执行存储在片上存储器和外部存储器中的程序, 并访问其中的数据, 如图4.1所示指令端总线接口程序指针(PC )运算器通用寄存器组32x32Bit指 令 缓冲指 令 译码数 据 端 总 线 接口DLMBDOP B图2.1 MicroBlaze 内核结构框图(1)内部结构MicroBlaze内部有32个32位通用寄存器和2个32位特殊寄存器—— PC 指针和MSR 状态标志寄存器。

软件体系结构 PPT

•

1.1what is SA ?

• 这种全局结构的设计和规划问题包括 全局组织 结构;全局控制结构;通信和同步以及数据存 取协议;规定设计元素的功能;设计元素的组 合;物理分布;规模和性能;演化的维度;设 计方案的选择等。 • 1随着软件系统的规模和复杂性不断增加,系 统的全局结构的设计和规划变得比算法的选择 以及数据结构的设计更加重要。 • 2人们普遍认为,为系统设计一个合适的体系 结构是系统取得长远的成功的关键因素。 • 3非形式化的。

1.1what is SA ?

e.g. 每个Filter都有输入端和输出端,例如一个MPEG-1解码Filter它的输入是MPEG编码的 流数据,它的输出端是一解码过的流数据。DirectShow正是通过将不同的Filter连接在一起 完成特定的功能的,我们将这些Filter的连接叫做Filter Graph,如下图A给出是播放AVI的 Filter Graph:

1概述

• 它是一种简单的、清楚的、完善的方式 形成的 • 软件工程师需要一种更好的视角来理解 软件,并试图找到一种新的方法来构建 更复杂的大型软件系统 • SA (software architecture) • 一个简单程序到复杂系统软件的距离是 十年

1概述-需求开发的主要困难

1概述-软件危机的原因

• 软件规模越来越大 • 随着软件应用范围的增广,软件规模愈来愈大。 随着软件应用范围的增广,软件规模愈来愈大。大 型软件项目需要组织一定的人力共同完成, 型软件项目需要组织一定的人力共同完成,而多数管 理人员缺乏开发大型软件系统的经验, 理人员缺乏开发大型软件系统的经验,而多数软件开 发人员又缺乏管理方面的经验。 发人员又缺乏管理方面的经验。各类人员的信息交流 不及时、不准确、有时还会产生误解。 不及时、不准确、有时还会产生误解。 软件项目开发人员不能有效地、 软件项目开发人员不能有效地、独立自主地处理大 型软件的全部关系和各个分支, 型软件的全部关系和各个分支,因此容易产生疏漏和 错误。 错误。

软件系统架构图-参考案例

各种软件开发系统架构图案例介绍第一章【荐】共享平台架构图与详细说明1.1.【荐】共享平台逻辑架构设计(逻辑指的是业务逻辑)注:逻辑架构图--主要突出子系统/模块间的业务关系, 这里的逻辑指的是业务逻辑如上图所示为本次共享资源平台逻辑架构图,上图整体展现说明包括以下几个方面:1 应用系统建设本次项目的一项重点就是实现原有应用系统的全面升级以及新的应用系统的开发,从而建立行业的全面的应用系统架构群。

整体应用系统通过SOA面向服务管理架构模式实现应用组件的有效整合,完成应用系统的统一化管理与维护。

2 应用资源采集整体应用系统资源统一分为两类,具体包括结构化资源和非机构化资源。

本次项目就要实现对这两类资源的有效采集和管理。

对于非结构化资源,我们将通过相应的资源采集工具完成数据的统一管理与维护。

对于结构化资源,我们将通过全面的接口管理体系进行相应资源采集模板的搭建,采集后的数据经过有效的资源审核和分析处理后进入到数据交换平台进行有效管理。

3 数据分析与展现采集完成的数据将通过有效的资源分析管理机制实现资源的有效管理与展现,具体包括了对资源的查询、分析、统计、汇总、报表、预测、决策等功能模块的搭建。

4 数据的应用最终数据将通过内外网门户对外进行发布,相关人员包括局内各个部门人员、区各委办局、用人单位以及广大公众将可以通过不同的权限登录不同门户进行相关资源的查询,从而有效提升了我局整体应用服务质量。

综上,我们对本次项目整体逻辑架构进行了有效的构建,下面我们将从技术角度对相关架构进行描述。

1.2.【荐】技术架构设计注:技术架构图--主要突出子系统/模块自身使用的技术和模块接口关联方式如上图对本次项目整体技术架构进行了设计,从上图我们可以看出,本次项目整体建设内容应当包含了相关体系架构的搭建、应用功能完善可开发、应用资源全面共享与管理。

下面我们将分别进行说明。

1.3.【荐】系统整体架构设计(也称为系统总体架构)上述两节,我们对共享平台整体逻辑架构以及项目搭建整体技术架构进行了分别的设计说明,通过上述设计,我们对整体项目的架构图进行了归纳如下:注:系统整体/总体架构图--主要突出从物理硬件(物理层/基础层)、数据库(数据层)、后台底层(支撑层)、业务逻辑(业务层/应用层)、UI描述(展示层)、系统用户分类(用户层),项目实施与运维管理,标准与规范体系和安全保障体系(贯穿各层的保障系统)一般我们只画大虚框内的部分就行了,外面的是说明与其他系统的对接描述,可以省略综上,我们对整体应用系统架构图进行了设计,下面我们将分别进行说明。

软件总体架构图

1软件总体架构图软件结构如图1.1所示:大容量数据采集与处理程序工业以太网网关路由程序CGIBOATCP/IP操作系统界面ucLinux 内核MicroBlaze Ip 设计图1.1 FPGA 数据采集软件架构图以上是系统的软件结构框图,我们下面将就具体每一个步骤的设计进行一个简要的描述:2 MicroBlaze IP 核设计IP 字面意思是知识产权,在微电子领域,具有知识产权的功能模块成为IP Core 或IP 核。

IP 可以用来生成ASIC 和PLD 逻辑功能块,又称为虚拟器件VC 。

IP 核可以有很多种,比如UART 、CPU 、以太网控制器、PCI 接口等。

根据IP 核描述的所在集成电路的设计层次,IP 可以分为硬IP 、软IP 、固IP 。

硬IP 的芯片中物理掩膜布局已经得到证明,所有的验证和仿真工作都已经完成,用它可以直接生产硅片,系统设计者不能再对它进行修改。

而软IP 是以行为级和RTL 级的Verilog 或VHDL 代码的形式存在,它要经过逻辑综合和版图综合才能最终实现在硅片上。

固IP 则介于两者之间。

Xilinx 公司的MicroBlaze32位软处理器核是支持CoreConnect 总线的标准外设集合。

MicroBlaze 处理器运行在150MHz 时钟下,可提供125 D-MIPS 的性能,非常适合设计针对网络、电信、数据通信和消费市场的复杂嵌入式系统。

1.MicroBlaze 的体系结构MicroBlaze 是基于Xilinx 公司FPGA 的微处理器IP 核,和其它外设IP 核一起,可以完成可编程系统芯片(SOPC)的设计。

MicroBlaze 处理器采用RISC 架构和哈佛结构的32位指令和数据总线, 可以全速执行存储在片上存储器和外部存储器中的程序, 并访问其中的数据, 如图4.1所示指令端总线接口程序指针(PC )运算器通用寄存器组32x32Bit指 令 缓冲指 令 译码数 据 端 总 线 接口DLMBDOP B图2.1 MicroBlaze 内核结构框图(1)内部结构MicroBlaze内部有32个32位通用寄存器和2个32位特殊寄存器—— PC 指针和MSR 状态标志寄存器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1软件总体架构图

软件结构如图1.1所示:

大容量数据采集与处理程序

工业以太网

网关路由程序

CGI

BOA

TCP/IP

操作系统界面

ucLinux 内核

MicroBlaze Ip 设计

图1.1 FPGA 数据采集软件架构图

以上是系统的软件结构框图,我们下面将就具体每一个步骤的设计进行一个简要的描述:

2 MicroBlaze IP 核设计

IP 字面意思是知识产权,在微电子领域,具有知识产权的功能模块成为IP Core 或IP 核。

IP 可以用来生成ASIC 和PLD 逻辑功能块,又称为虚拟器件VC 。

IP 核可以有很多种,比如UART 、CPU 、以太网控制器、PCI 接口等。

根据IP 核描述的所在集成电路的设计层次,IP 可以分为硬IP 、软IP 、固IP 。

硬IP 的芯片中物理掩膜布局已经得到证明,所有的验证和仿真工作都已经完成,用它可以直接生产硅片,系统设计者不能再对它进行修改。

而软IP 是以行为级和RTL 级的Verilog 或VHDL 代码的形式存在,它要经过逻辑综合和版图综合才能最终实现在硅片上。

固IP 则介于两者之间。

Xilinx 公司的MicroBlaze32位软处理器核是支持CoreConnect 总线的标准外设集合。

MicroBlaze 处理器运行在150MHz 时钟下,可提供125 D-MIPS 的性能,非常适合设计针对网络、电信、数据通信和消费市场的复杂嵌入式系统。

1.MicroBlaze 的体系结构

MicroBlaze 是基于Xilinx 公司FPGA 的微处理器IP 核,和其它外设IP 核一起,可以完成可编程系统芯片(SOPC)的设计。

MicroBlaze 处理器采用RISC 架构和哈佛结构的32位指令和数据总线, 可以全速执行存储在片上存储器和外部存储器中的程序, 并访问其中的数据, 如图4.1所示

指令端总线接口

程序指针(PC )

运算器

通用寄存器组32x32Bit

指 令 缓

冲指 令 译

码

数 据 端 总 线 接

口

DLMB

DOP B

图2.1 MicroBlaze 内核结构框图

(1)内部结构

MicroBlaze

内部有32个32位通用寄存器和2个32位特殊寄存器—— PC 指针和MSR 状态标志寄存器。

为了提高性能,MicroBlaze 还具有指令和数据缓存。

所有的指令字长都是32位,有3个操作数和2 种寻址模式。

指令按功能划分有逻辑运算、算术运算、分支、存储器读/写和特殊指令等。

指令执行的流水线是并行流水线, 它分为3级流水:取指、译码和执行,如图4.2所示。

指令1指令2指令3

指令周期4指令周期3

指令周期2指令周期1指令周期5

图2.2 MicroBlaze 的流水线

(2)存储结构

MicroBlaze 是一种大端存储系统处理器,使用如图4.3所式的格式来访问存储器。

31

7

8

151623240

图2.3 大端数据格式

(3)中断控制和调试接口

MicroBlaze 可以响应软件和硬件中断,进行异常处理, 通过外加控制逻辑, 可以扩展外部中断。

利用微处理器调试模块(MDM)IP 核,可通过JTAG 接口来调试处理器系统。

多个MicroBlaze 处理器可以用1个MDM 来完成多处理器调试。

(4)快速单一链路接口

MicroBlaze 处理器具有8个输入和8个输出快速单一链路接口(FSL)。

FSL 通道是专用于单一方向的点到点的数据流传输口。

FLS 和MicroBlaze 的接口宽度是32位。

每一个FSL 通道都可以发送和接收控制或数据字。

2. CoreConnect 技术

CoreConnect是由IBM开发的片上总线通信链,它使多个芯片核相互连接成为一个完整的新芯片成为可能。

CoreConnect技术使整合变得更为容易,而且在标准产品平台设计中,处理器、系统以及外围的核可以重复使用,以达到更高的整体系统性能。

Xilinx将为所有嵌入式处理器用户提供IBM CoreConnect许可,因为它是所有Xilinx 嵌入式处理器设计的基础。

MicroBlaze处理器使用了与IBM PowerPC 相同的总线,用作外设。

虽然MicroBlaze软处理器完全独立于PowerPC,但它让设计者可以选择芯片上的运行方式,包括一个嵌入式PowerPC,并共享它的外设。

CoreConnect总线架构如图4.4所示。

它包括片上外围总线(OPB),处理器本机总线(PLB),设备控制寄存器(DCR)总线以及1个总线桥和2个判优器。

图2.4 CoreConnect 总线架构

(1)片上外设总线(OPB)

内核通过片上外设总线(OPB)来访问低速和低性能的系统资源。

OPB是一种完全同步总线,它的功能处于一个单独的总线层级。

它不是直接连接到处理器内核的。

OPB接口提供分离的32 位地址总线和32位数据总线。

处理器内核可以借助“PLB to OPB”桥,通过OPB访问从外设。

作为OPB总线控制器的外设可以借助“OPB to PLB”桥,通过PLB访问存储器。

(2)处理器本机总线(PLB)

PLB接口为指令和数据一侧提供独立的32位地址和64位数据总线。

PLB支持具有PLB总线接口的主机和从机通过PLB信号连接来进行读写数据的传输。

总线架构支持多主从设备。

每一个PLB主机通过独立的地址总线、读数据总线和写数据总线与PLB连接。

PLB从机通过共享但分离的地址总线、读数据总线和写数据总线与PLB连接,对于每一个数据总线都有一个复杂的传输控制和状态信号。

为了允许主机通过竞争来获得总线的所有权,有一个中央判决机构来授权对PLB的访问。

(3)设备控制寄存器总线(DCR)

设备控制寄存器总线(DCR)是为在CPU通用寄存器(GPRs)和DCR的从逻辑设。