杭电计组实验4-寄存器堆设计实验

计算机组成原理寄存器堆实验报告

实验七-八寄存器堆实验姓名:陈衍席学号:1205110125 网工1202【实验环境】1. Windows 2000 或 Windows XP2. QuartusII9.1 sp2、DE2-115计算机组成原理教学实验系统一台,排线若干。

【实验目的】本次实验要求掌握触发器的基本原理,掌握寄存器和寄存器堆的组成原理。

【实验要求】本次实验只需要设计并实现8位触发器和32位触发器。

【实验原理】寄存器是数字电路中的基本模块,许多复杂的时序逻辑电路都是由它构成的。

在数字系统中,寄存器是一种在某一特定信号的控制下用于存储一组二进制数据的时序逻辑电路。

通常使用触发器构成寄存器,把多个D触发器的时钟连接起来就可以构成一个存储多位二进制的寄存器。

寄存器中二进制数的位可以用两种方式移入或移出寄存器。

第一种方法是以串行的方式将数据每次移动一位,这种方法称之为串行移位(Serial Shifting),线路较少,但耗费时间较多。

第二种方法是以并行的方式将数据同时移动,这种方法称之为并行移位(Parallel Shifting),线路较为复杂,但是数据传送的速度较快。

因此,按照数据进出移位寄存器的方式,可以将移位寄存器分为四种类型:串行输入串行输出移位寄存器(Serial In- Serial Out)、串行输入并行输出移位寄存器(Serial In- Parallel Out)、并行输入串行输出移位寄存器(Parallel In- Serial Out)、并行输入并行输出移位寄存器(Parallel In-ParallelOut)。

在CPU设计中,寄存器堆是一个可以保存指令和数据的必不可少的器件,是RISC微处理器的核心,所有内部、外部数据的读取都直接和它发生关系。

它由一组寄存器组成,只要给出寄存器堆中该寄存器的编号,则其中的内容都可以读或者写。

【实验步骤】1、8位触发器设计8位触发器中包括,输入信号:一个8位数据源D,1位CLRN复位信号,1位EN使能信号,1位CLK时钟信号;输出信号:8位Q。

计算机组成原理--实验报告

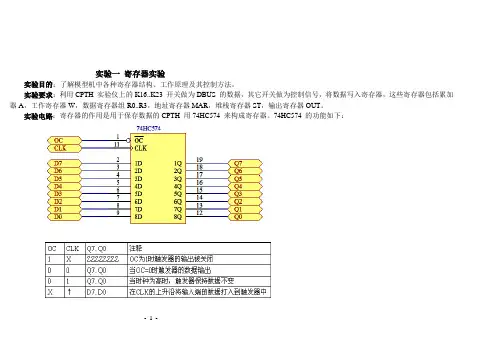

实验一寄存器实验实验目的:了解模型机中各种寄存器结构、工作原理及其控制方法。

实验要求:利用CPTH 实验仪上的K16..K23 开关做为DBUS 的数据,其它开关做为控制信号,将数据写入寄存器,这些寄存器包括累加器A,工作寄存器W,数据寄存器组R0..R3,地址寄存器MAR,堆栈寄存器ST,输出寄存器OUT。

实验电路:寄存器的作用是用于保存数据的CPTH 用74HC574 来构成寄存器。

74HC574 的功能如下:- 1 -实验1:A,W 寄存器实验原理图寄存器A原理图寄存器W 原理图连接线表:- 2 -系统清零和手动状态设定:K23-K16开关置零,按[RST]钮,按[TV/ME]键三次,进入"Hand......"手动状态。

在后面实验中实验模式为手动的操作方法不再详述.将55H写入A寄存器二进制开关K23-K16用于DBUS[7:0]的数据输入,置数据55H置控制信号为:按住STEP脉冲键,CK由高变低,这时寄存器A的黄色选择指示灯亮,表明选择A寄存器。

放开STEP键,CK由低变高,产生一个上升沿,数据55H被写入A寄存器。

将66H写入W寄存器二进制开关K23-K16用于DBUS[7:0]的数据输入,置数据66H- 3 -置控制信号为:按住STEP脉冲键,CK由高变低,这时寄存器W 的黄色选择指示灯亮,表明选择W寄存器。

放开STEP 键,CK 由低变高,产生一个上升沿,数据66H 被写入W 寄存器。

注意观察:1.数据是在放开STEP键后改变的,也就是CK的上升沿数据被打入。

2.WEN,AEN为高时,即使CK有上升沿,寄存器的数据也不会改变。

实验2:R0,R1,R2,R3 寄存器实验连接线表- 4 -将11H、22H、33H、44H写入R0、R1、R2、R3寄存器将二进制开关K23-K16,置数据分别为11H、22H、33H、44H置控制信号为:K11、K10为10,K1、k0分别为00、01、10、11并分别按住STEP 脉冲键,CK 由高变低,这时寄存器R0、R1\R2\R3 的黄色选择指示灯分别亮,放开STEP键,CK由低变高,产生一个上升沿,数据被写入寄存器。

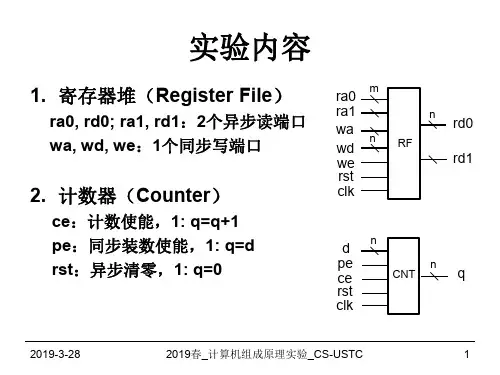

实验内容寄存器堆(RegisterFile)ra0,rd0;ra1,rd1

• 检查下载测试是否正确

• 检查代码设计,代码是否独立完成

2019-3-28

2019春_计算机组成原理实验_CS-USTC

3

实验报告

• 内容包括但不限于:逻辑设计(数据通路和状态 图)、核心代码、仿真/下载结果、结果分析、实 验总结、意见/建议等,附设计和仿真代码

• 实验检查后一周内提交实验报告

2019春_计算机组成原理实验_CS-USTC

2

实验要求和检查

• 完成1和3的的逻辑设计、仿真和下载测试

– 逻辑设计采用模块化设计 – 仿真3时忽略display – 下载测试时,时钟采用板载100MHz时钟,其他输入

由拨动开关和按钮开关设置,结果输出至LED指示灯 或7段数码管

• 查看1和2的电路性能和资源使用情况

rst

FIFO

16

display

4

out empty

- out, in:出/入队列数据

clk

full

- full, empty:队列空/满, 空/满时忽略出/入队操作

- display:8个数码管的控 制信号,显示队列状态

.

1. 2 3 2. 3

复位 数据1, 2, 3依次入队 列

数据1出队列

2019-3-28

– ftp://202.38.79.134/ 相应文件夹 – 文件名格式:Labn_学号_姓名.pdf (其中n为第几次

实验,不满足该格式的视为未提交实验报告)

• 严禁抄袭,否则作零分处理

2019-3-28

2019春_计算机组成原理实验_CS-USTC

4

The End

2019-3-28

2019春_计算机组成原理实验_CS-USTC

杭电计组实验-存储器设计实验

杭电计组实验-存储器设计实验————————————————————————————————作者:————————————————————————————————日期:实验报告2018 年 5 月 5 日成绩:姓名阳光男学号16041321 班级16052317专业计算机科学与技术课程名称《计算机组成原理与系统结构试验》任课老师张翔老师指导老师张翔老师机位号默认实验序号5实验名称《实验五存储器设计实验》实验时间2018/5/12实验地点1教211实验设备号个人电脑、Nexys3开发板一、实验程序源代码存储器顶层电路代码:module top_RAM_B(Mem_Addr,C,Mem_Write,Clk,LED);input [7:2]Mem_Addr;//开关的3、4、5、6、7、8位input Mem_Write,Clk;//clk为按键C9,读写使能信号为按键C4,0为读,1为写input [1:0]C;//选择写入数据+读操作时选择显示字节,为开关1、2位output reg [7:0]LED;wire [31:0]M_R_Data;//存在存储器里的32位读出数据reg [31:0]M_W_Data;//寄存在暂存器的32位写入数据RAM_B test_ram (.clka(Clk), //输入时钟信号.wea(Mem_Write), //输入读写信号.addra(Mem_Addr[7:2]), //输入5位地址信号.dina(M_W_Data), //写入32位数据.douta(M_R_Data) //读出32位数据);always@(*)beginLED=0;//初始化M_W_Data=0;//初始化if(!Mem_Write)//读操作begincase(C)2'b00:LED=M_R_Data[7:0];//读出数据的0-7位2'b01:LED=M_R_Data[15:8];//读出数据的8-15位2'b10:LED=M_R_Data[23:16];//读出数据的16-23位2'b11:LED=M_R_Data[31:24];//读出数据的24-31位endcaseendelsebegincase(C)2'b00:M_W_Data=32'h0055_7523;//写入第一个数据2'b01:M_W_Data=32'h1234_5678;//写入第二个数据2'b10:M_W_Data=32'h8765_4321;//写入第三个数据2'b11:M_W_Data=32'hffff_ffff;//写入第四个数据endcaseendendendmodule测试代码:module test;// Inputsreg clka;reg [0:0] wea;reg [5:0] addra;reg [31:0] dina;// Outputswire [31:0] douta;// Instantiate the Unit Under Test (UUT)RAM_B uut (.clka(clka),.wea(wea),.addra(addra),.dina(dina),.douta(douta));initial begin// Initialize Inputsclka = 0;wea = 0;addra = 0;dina = 0;// Wait 100 ns for global reset to finish #100;// Add stimulus hereclka = 1;wea = 0;addra = 6'b000001;dina = 32'h0000_0003;#100;clka = 0;wea = 0;addra = 6'b000001;dina = 32'h0000_0607;#100;clka = 1;wea = 1;addra = 6'b000001;dina = 32'hFFFF_FFFF;#100;clka = 0;wea = 1;addra = 6'b000001;dina = 32'hFFFF_FFFF;endendmodule二、仿真波形三、电路图顶层电路模块顶层电路内部结构:四、引脚配置(约束文件)NET "Clk" LOC = C9;NET "LED[4]" LOC = M11;NET "LED[3]" LOC = V15;NET "LED[2]" LOC = U15;NET "LED[1]" LOC = V16;NET "LED[0]" LOC = U16;NET "Mem_Addr[7]" LOC = U8;NET "Mem_Addr[6]" LOC = N8;NET "Mem_Addr[5]" LOC = M8;NET "Mem_Addr[4]" LOC = V9;NET "Mem_Addr[2]" LOC = T10;NET "Mem_Write" LOC = C4;NET "Mem_Addr[3]" LOC = T9;NET "C[1]" LOC = T5;NET "C[0]" LOC = V8;NET "LED[7]" LOC = T11;NET "LED[5]" LOC = N11;NET "LED[6]" LOC = R11;五、思考与探索(1)读操作实验结果记录表存储器地址初始化数据读出数据写入新数据读出数据5’b000000 32’b0000000032’b0000000032'h0055_752332'h0055_7523 5’b000001 32’b0000000132’b0000000132'h0055_752332'h0055_7523 5’b000002 32’b0000000232’b0000000232'h0055_752332'h0055_7523 5’b000003 32’b0000000332’b0000000332'h0055_752332'h0055_7523 5’b000004 32’b0000000432’b0000000432'h0055_752332'h0055_7523 5’b000005 32’b0000000532’b0000000532'h0055_752332'h0055_7523 5’b000006 32’b0000000632’b0000000632'h0055_752332'h0055_7523 5’b000007 32’b0000000732’b0000000732'h0055_752332'h0055_7523 (2)答:这些单元的数据已经被改写了。

杭电计算机组成原理寄存器堆设计实验

杭电计算机组成原理寄存器堆设计实验计算机组成原理是计算机科学与技术的基础课程之一,它涉及到计算机的基本组成部分和原理。

在这门课程中,学生通常需要进行一系列的实验来加深对计算机组成原理的理解和应用。

其中之一是关于寄存器堆的设计实验。

寄存器堆是计算机中重要的组成部分之一,它用于存储、读取和写入数据。

在计算机中,数据通常被存储在寄存器中,然后进行各种操作。

因此,设计一个高效可靠的寄存器堆对于计算机的性能至关重要。

根据实验要求,我们需要设计一个8位的寄存器堆,并实现读取、写入和清零等操作。

以下是针对该实验的设计思路和实施步骤。

首先,我们需要确定寄存器堆的结构。

由于该寄存器堆为8位宽度,我们选择使用一个8x8的存储单元阵列。

每个存储单元都可以存储一个8位的数据。

整个寄存器堆由8个存储单元组成,每个存储单元对应一个地址,即0~7接下来,我们需要设计寄存器堆的读写电路。

对于读操作,我们需要通过地址线来选择要读取的存储单元,并将其输出到数据线。

对于写操作,我们同样需要通过地址线来选择要写入的存储单元,并将数据线上的数据写入该存储单元。

为了实现这些操作,我们需要使用多路选择器和数据解码器。

在设计中,我们还需要考虑到时钟信号的输入,以确保读写操作在时钟的上升沿或下降沿进行。

此外,我们还需要添加清零功能,以便将寄存器堆的值重置为零。

为实现清零功能,我们可以将一个额外的输入线与所有存储单元的清零输入连接。

在实施阶段,我们需要使用Verilog或其他硬件描述语言来实现设计。

在代码中,我们首先声明一个8位宽的存储单元阵列作为寄存器堆的基本组成部分。

然后,我们定义读写电路,包括地址线、数据线、多路选择器和数据解码器。

最后,我们添加时钟信号和清零功能。

在完成设计后,我们可以通过仿真工具进行验证。

通过输入不同的数据和地址,观察输出结果是否符合预期。

如果存在问题,我们可以进行调试并进行必要的修改。

一旦仿真结果正确无误,我们就可以开始进行硬件实验了。

计算机组成原理堆栈寄存器实验报告

计算机组成原理实验三堆栈寄存器实验一、实验目的:1、熟悉堆栈概念。

2、熟悉堆栈寄存器的组成和硬件电路。

二、实验要求:完成3个堆栈寄存器的数据写入与读出。

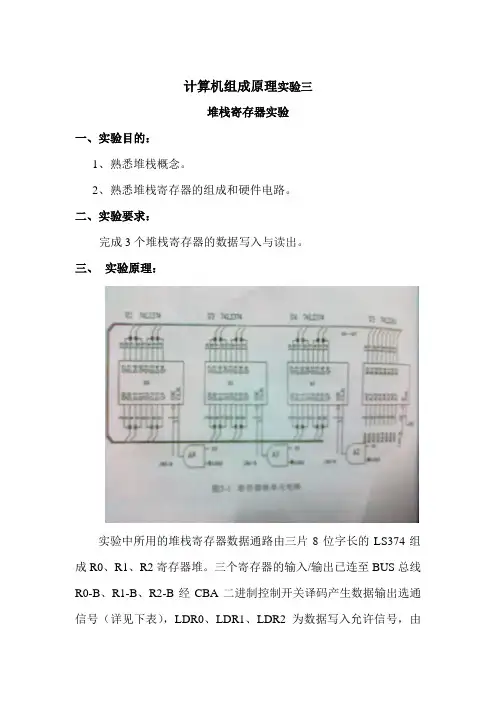

三、实验原理:实验中所用的堆栈寄存器数据通路由三片8位字长的LS374组成R0、R1、R2寄存器堆。

三个寄存器的输入/输出已连至BUS总线R0-B、R1-B、R2-B经CBA二进制控制开关译码产生数据输出选通信号(详见下表),LDR0、LDR1、LDR2为数据写入允许信号,由二进制控制开关来模拟,均为高电平有效;T4信号为寄存器数据写入脉冲,上升沿有效。

在手动实验状态(即“H”装态)每按动一次“单步”命令键,产生一个T4信号。

下表为寄存器单元选通真值表:四、实验连接:1.连接实验线路,把位于实验装置左上方的CTR-OUT UNIT (LDR0、LDR1、LDR2、/SW-B)与实验装置右中央的CTR-OUT unit (LDR0、LDR1、LDR2)及实验装置左下方INPUT-UNIT(/SW-B)中的控制信号作对应连接。

2.具体连接信号:/SW-B,/R0-B,/R1-B ,/R2-B ,LDR0,LDR1,LDR2五、实验仪器状态设定:在闪动的“P.”状态下按动“增址”命令键,使LED显示器自左向右第一位显示提示符“H”,表示本装置已进入手动单元实验状态。

五、实验项目:(一)堆栈寄存器的写入拨动二进制数据开关(INPUT-UNIT)向R0和R1寄存器置数(置数灯亮表示它所对应的数据位为“1”、反之为“0”)。

具体操作步骤图示如下:[CBA=001] [LDR0=1] [LDR=1][LDR1=0] [LDR1=1][LDR2=0] [LDR2=0][按“STEP”] [按“STEP”] (二)堆栈寄存器的读出关闭数据输入三态门(CBA=000),分别打开通用寄存器R0、R1、R2输出控制位,当CBA=100时,总线指示灯(BUS-DISP UNIT)显示R0中的数据01H;当CBA=101时,总线指示灯显示R1中的数据80H;当CBA=110时,总线指示灯显示R2中等的数据(随机),可以观察到,显示的随机数为11111111.(六)实验总结通过本次实验的数据和理论分析进行比较、验证,我们熟悉了堆栈概念,熟悉了堆栈寄存器的组成和硬件电路等。

杭电计算机组成原理多功能ALU设计实验

评议

成绩评定: 指导教师签名:

(7)记录测试结果。

(接上)

实验内容(算法、程序、步骤和方法)

(1)ALU模块代码,利用三八译码器,将我们将要操作的对象,进行分别的处理。

module ALU_TOP(A,B,F,ZF,OF,ALU_OP);

input [31:0] A,B;

input [2:0] ALU_OP;

output ZF,OF;

3'b010:begin CF=A^B; end

3'b011:begin CF=A~^B; end

3'b100:begin CF=A+B; end

3'b101:begin CF=A-B; end

3'b110:begin CF=(A<B); end

3'b111:begin CF=B<<A; end

endcase

end

endmodule

(3)输出数据选择模块代码,根据实验指导书上的对于32位数据的处理方式。

module CLED(F_LED_SW,LED,F,ZF,OF);

input [31:0] F;

input ZF,OF;

input [2:0] F_LED_SW;

output [7:0] LED;

reg [7:0] LED;

output [31:0] F;

reg [31:0] F;

reg ZF,OF;

reg [5:0] i;

reg C;

reg [32:0] CF;

always @ (ALU_OP or A or B)

begin

case(ALU_OP)

杭电单片机实验报告四

单片机原理与应用技术实验报告实验题目:定时/计数器应用姓名:* * *学号:********实验日期: 2017.5.28指导教师:高惠芳1.实验内容1、已知震荡频率为12MHz,用定时/计数器T0,实现从P2.0口产生周期为100ms的方波。

要求用汇编语言和C语言编程实现,编程方法分别用中断方法和查询方法。

用中断方式:C语言代码://从P2.0引脚输出周期为100ms的方波//由定时器T0产生50ms的定时//T0工作于方式1可以实现50ms的定时//X=65536-50/0.001=15536=3CB0H#include <reg51.h>sbit p2_0 = P2^0;void main(void){TMOD=0X01;EA=1;ET0=1;TH0=(65536-50000)/256;//TH0=0x3C;TL0=(65536-50000)%256;//TL0=0xB0;TR0=1;while(1);}void timer0(void) interrupt 1 using 1{TH0=(65536-50000)/256;//TH0=0x3C;TL0=(65536-50000)%256;//TL0=0xB0;p2_0=!p2_0;}汇编语言代码:ORG 0000HLJMP MAINORG 000BHAJMP SER_T0ORG 0100HMAIN: MOV TMOD,#01HMOV TH0,#3CHMOV TL0,#0B0HSETB E T0SETB TR0SJMP $SER_T0: MOV TH0,#3CHMOV TL0,#0B0HCPL P2.0RETIEND用查询方式:C语言程序代码://从P2.0引脚输出周期为100ms的方波//由定时器T0产生50ms的定时//T0工作于方式1可以实现50ms的定时//X=65536-50/0.001=15536=3CB0H#include <reg51.h>sbit p2_0 = P2^0;void main(void){TMOD=0X01;TH0=(65536-50000)/256;//TH0=0x3C;TL0=(65536-50000)%256;//TL0=0xB0;TR0=1;while(1){TH0=(65536-50000)/256;TL0=(65536-50000)%256;while(!TF0);p2_0=!p2_0;}}汇编语言:ORG 0000HLJMP MAINORG 0100HMAIN: MOV TMOD,#01HMOV TH0,#3CHMOV TL0,#0B0HLOOP: JBC TF0,NEXTSJMP LOOPNEXT: MOV TH0,#3CHMOV TL0,#0B0HCPL P2.0SJMP LOOPEND2、已知震荡频率为6MHz,用定时/计数器T0,实现从P1.0口产生周期为1s,占空比为30%波形。

移位寄存器、计数器设计

一、实验目的

1.用D触发器组成左移移位寄存器,并测试其工作状态。

2.熟悉集成单元计数器的使用,掌握各种进制的设计方法。

二、原理简述见实验指导书

三、实验内容与步骤

1.用D触发器组成四位左移移位寄存器

Q4

Q3

9 Q2

5 Q1

RD T4 CP D4

RD T3 CP D3

RD

T2 CP

10u 22u 47u D1 D2 DW1 DW2

+Ec

+5 v L8 L7 L6 L5 L4 L3 L2 L1

74248

RL

74248

74248

74248

51K +5 v

+5 v 1Hz

CP1

CP2

K8 K7 K6 K5 K4 K3 K2 K1

十进制设计电路图

U3

V1

50 Hz 5V

U1

14 1

实验机介绍

ON

OFF

+12v

模

-12V

拟

部

+6V

分

GND

直流信号

I

直流信号

II

+5V

数

GND

字

部 分

1KHz

1Hz

逻辑笔 高电平 高阻态 低电平

1M

220K

T1

T2

Ui

10K 10K 10K

10K

0.1u

15K

0.5u

20K

10u

10K 10K 10K 2K 3.31K 5.1K 6.8K

20K 50K 30K 50K 100K 470K 7.5K

4 堆栈寄存器实验

堆栈寄存器实验一、实验目的1、熟悉堆栈概念2、熟悉堆栈寄存器的组成和硬件电路二、实验要求按照实验步骤完成实验项目,对4个堆栈寄存器进行读出、写入数据操作。

三、实验原理1、堆栈寄存器组实验构成(图2-5-1)本系统内有4个寄存器R0~R3,寄存器组由4个74LS374组成,由1片74LS139(2-4译码器)来选择4个74LS374,并且由2片74LS32来组成控制线。

8芯插座R-IN、R-OUT作为数据输入、输出端,可通过短8芯扁平电缆把数据输入、输出端连接到数据总线上。

图2-5-12、堆栈寄存器组原理由SA、SB两根控制线通过74LS139译码来选择4个寄存器(74LS374)。

当WR=0时,表示数据总线向寄存器写入数据,RCK为寄存器的工作脉冲,在有上升沿时把总线上数据打入74LS139选择的那个寄存器。

当RR=0时,74LS139所选择的寄存器上的数据输出至数据总线。

在本系统内使用了WR=0作为写入允许,RCK信号为上升沿时打入数据、RR=0时数据输出。

3、控制信号说明四、实验步骤实验1 对4个寄存器进行写入操作将R-IN(8芯盒形插座)与CPT-B板上的二进制开关单元中J03插座相连(对应二进制开关H0~H7),R-OUT可通过短8芯扁平电缆与数据总线上DJ4相连。

把RR、WR、SA、SB接入二进制拨动开关(SA,SB借用X0,X1的H12,1、把数据写入寄存器R0)按启停单元中的运行按钮,置实验平台为运行状态。

置WR=0、RR=1按脉冲单元中的PLS1脉冲按键,在RCK上产生一个上升沿的脉冲,把11H 打入R0寄存器。

2、把数据写入寄存器R1置二进制开关H0~H7(D0~D7)为22H,各控制信号对应开关如下表。

按脉冲单元中的PLS1脉冲按键,在RCK上产生一个上升沿的脉冲,把22H 打入R1寄存器。

3、把数据写入寄存器R2按脉冲单元中的PLS1脉冲按键,在RCK上产生一个上升沿的脉冲,把33H 打入R2寄存器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

杭州电子科技大学计算机学院

实验报告

实验项目:

课程名称:计算机组成原理与系统结构设计 姓名: 学号: 同组姓名: 学号

: 实

验

位

置

(

机

号

)

: 实验日期:

指

导

教

师:

实验 内容

(算

法、

程

序、

步骤 和

方 法)

一、 实验目的

(1 )学会使用Verilog HDL 进行时序电路的设计方法。

(2)掌握灵活应用Verilog HDL 进行各种描述与建模的技巧和方法。

(3 )学习寄存器堆的数据传送与读 /写工作原理,掌握寄存器堆得设计方法。

二、 实验仪器

ISE 工具软件 三、 步骤、方法 (1) 启动Xilinx ISE 软件,选择File->New Project,输入工程名shiyan2,默认选择后,点

击Next 按钮,确认工程信息后点击 Finish 按钮,创建一个完整的工程。

(2) 在工程管理区的任意位置右击,选择 New Source 命令。

弹出 New Source Wizard 对 话框,

选择Verilog Module,并输入Verilog 文件名,点击Next 按钮进入下一步, 点击Finish 完成创建。

(3) 编辑程序源代码,然后编译,综合;选择 Synthesize--XST 项中的Check Syntax 右击 选择

Run 命令,并查看RTL 视图;如果编译出错,则需要修改程序代码,直至正确。

(4) 在工程管理区将 View 类型设置成 Simulation ,在任意位置右击,选择 New Source 命 令,选择Verilog Test Fixture 选项。

点击Next ,点击Finish ,完成。

编写激励代码,观察仿 真波形,如果验证逻辑有误,则修改代码,重新编译,仿真,直至正确。

(5) 由于实验四并未链接实验板,所以后面的链接实验板的步骤此处没有。

begin

if(Reset)

begin

for(i=0;i<=31;i=i+1) REG_Files[i]<=32'bO;

end

else

begin if(Write_reg) REG_Files[W_Addr]<=W_Data;

end

end

assig n R_Data_A=REG_Files[R_Addr_A]; assig n R_Data_B=REG_Files[R_Addr_B]; en dmodule

仿真代码

module shiya n4_test;

//In puts

reg [4:0] R_Addr_A;

reg [4:0] R_Addr_B;

reg Clk;

reg [4:0] W_Addr;

reg [32:0] W_Data;

reg Reset;

reg Write_reg;

// Outputs

wire [0:31] R_Data_A;

wire [0:31] R_Data_B;

//In sta ntiate the Unit Un der Test (UUT)

shiya n4 uut (

•R_Addr_A(R_Addr_A),

•R_Addr_B(R_Addr_B),

.Clk(Clk),

.W_Addr(W_Addr),

.W_Data(W_Data),

.R_Data_A(R_Data_A),

.R_Data_B(R_Data_B),

.Reset(Reset),

.Write_reg(Write_reg)

);

in itial beg in

//I nitialize In puts

R_Addr_A = 0;

R_Addr_B = 0;

Clk = 0;

W_Addr = 0;

W_Data = 0;

Reset = 0;

Write_reg = 0;

// Wait 100 ns for global reset to finish #100;

// Add stimulus here

#100;

Clk = 1;

Reset = 0;

R_Addr_A = 0;

R_Addr_B = 0;

W_Addr = 5'b00001;

Write_reg = 1;

W_Data = 32'h1111_1111;

#100;

Clk = 0;

Reset = 0;

R_Addr_A = 0;

R_Addr_B = 0;

W_Addr = 5'b00001;

Write_reg = 1;

W_Data = 32'h1111_1111;

#100;

Clk = 1;

Reset = 0;

R_Addr_A = 0;

R_Addr_B = 0;

W_Addr = 5'b00010;

Write_reg = 1;

W_Data = 32'h2222_2222;

#100;

Clk = 0; Reset = 0;

R_Addr_A = 5'b00001;

R_Addr_B = 5'b00010;

W_Addr = 0;

Write_reg = 0;

W_Data = 0;

Clk = 0;

Reset = 1;

R_Addr_A = 5'b00001;

R_Addr_B = 5'b00010;

W_Addr = 0;

Write_reg = 0;

W_Data = 0;

end en dmodule

RTL图

思考题:(1)根据8个寄存器执行读、写操作,实验结果符合预期 (2) always@(posedge Clk or posedge Reset) begin

if(Reset) begin

for(i=0;i<=31;i=i+1) REG_Files[i]<=32'bO; end

£

o

结果

-儿沁屈DBS 丽面麵0面

r

i :^zXCi

J DC 0003-3 2 DC

<

2 DC 01 □0030 ::::!

X

:3DC10

JfrZJC

Kg

AddrfAS I flDOOO QOC®

C-MC1

W ;3

[krtap2:01 >W1MC

ISOWMCMMOWMCgq

iwooo 加咒

WtB

R Data.BOtSl] 3 DC 000301211

C-W1Q X ■00 lit i i i

i L

(畑十财OMOOCKM。