爱普生晶振RX-4803LC实时时钟模块规格书

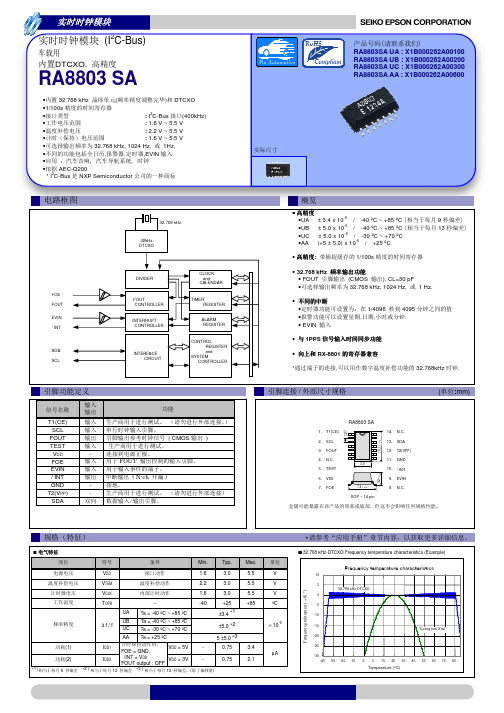

爱普生(EPSON)实时时钟模块RA8803SA规格书

DTCXO,

RA8803 SA

• 32.768 kHz

(

) DTCXO

•1/100s •

: I2C-Bus (400kHz)

•

: 1.6 V ~ 5.5 V

•

: 2.2 V ~ 5.5 V

•

: 1.6 V ~ 5.5 V

•

32.768 kHz, 1024 Hz, 1Hz.

•

,

,

,EVIN

FOE FOUT EVIN / INT

SDA SCL

32.768 kHz

32kHz DTCXO

DIVIDER

FOUT CONTROLLER

INTERRUPT CONTROLLER

INTERFACE CIRCUIT

CLOCK and

CALENDAR

TIMER REGISTER

ALARM REGISTER

5 32.768 kHz DTCXO

0

-5

-10

-15 Tuning fork X'tal

-20

-25

-30 -45 -35 -25 -15 -5 5 15 25 35 45 55 65 75 85 Temperature (ºC)

推进环境管理体系 符合国际标准

在环境管理体系的运行方面,使用 ISO14001 国际环境标准,通过“计 划-实施-检查-验证(PDCA)的循环来实现持续改进。公司位于日本和 海外的主要制造基地已取得了 ISO14001 资格认证。

CONTROL REGISTER and

SYSTEM CONTROLLER

T1(CE)

SCL

FOUT

TEST

EPSON 实时时钟芯片RX-8010SJ Application Manual介绍

根据实际功能设置 1F[h]寄存器 使 STOP=‘0’

继续其它操作

RX-8010SJ 13

13.1

通过 I2C 总线接口读写数据

器件地址(Device Address/Slave Address) 所有的通讯操作都是以 [START 条件] + [从设备地址 + (R/W 读写选择)开始的。 从设备地址如下:

RX-8010SJ

12.3.2 固定周期定时中断寄存器 相关寄存器:

* 在进入操作设定之前,建议将 TE 位 清 0。 * 在不用该功能的时候,计数器 0,1 可以作为 RAM 来使用,但需要将 TE 和 TIE 清 0。 1)用于固定定时器的递减计数器 0,1 该寄存器用来设定定时器的默认值, 从 0 到 65535。 在写入预设值之前请确认 TE 位 为’0’。 *TE 为‘0’时读出来的值是预设值, ‘1’时读出来的值是计数值。 2)TSEL0,TSEL1,TSEL2 这三个位的组合用来设置倒数计数的周期(时钟源)

爱普生 EPSON 温补晶振 TG-5006CE-39L 32.000000MHz规格参数、数据手册、规格书信息

*2 Measured in the elapse of 24 hours after reflow soldering.

*3 Vcc +/- 5% must be in operating supply voltage range (1.7 V to 3.465 V)

2

[ 5 ] Electrical characteristics

3

[ 6 ] Test circuit

1) Output Load : Load_R // Load_C = 10 kΩ // 10 pF

Supply Voltage

By-pass Capacitor

0.01 to 0.1 F

Vcc N.C.

OUT

DC-cut Capacitor

GND

Load_C

fo

-

32

-

MHz

Frequency tolerance

f_tol

-1.0

-

+1.0

x10⁻⁶

T_use=+25°C+/-2°C Before reflow

Frequency tolerance *1

f_tol

-2.0

-

+2.0

x10⁻⁶

T_use=+25°C+/-2°C After 2 reflows *2

To maintain stable operation, provide a 0.01 to 0.1 μF by-pass capacitor at a location as near as possible to the power source terminal of the crystal product (between Vcc - GND).

爱普生(EPSON)实时时钟模块RA4803SA规格书

DIVIDER

FOUT CONTROLLER

INTERRUPT CONTROLLER

INTERFACE CIRCUIT

CLOCK and CALENDAR

TIMER REGISTER

ALARM REGISTER

SYSTEM CONTROLLER

and CONTROL REGISTER

• •UA •UB •UC •AA

± 3.4 x 10-6 / -40 ºC ~ +85 ºC 商

± 5.0 x 10-6 / -40 ºC ~ +85 ºC 商 ± 5.0 x 10-6 / -30 ºC ~ +70 ºC (+5 ± 5.0) x 10-6 / +25 ºC

9

器

13

器

•

:

1/100s

●为汽车行驶安全方面的应用(引擎控制单元、气囊、电子稳定程序控制系统)。

注意事项

·本材料如有变更,恕不另行通知。量产设计时请确认最新信息。 ·未经 Seiko Epson 公司书面授权,禁止以任何形式或任何方式复制或者发布本材料中任何部分的信息内容。 ·本材料中的书面信息、应用电路、编程、使用等内容仅供参考。Seiko Epson 公司对第三方专利或版权的侵权行为不负有任何责任。本材料

0

-5

-10

-15 Tuning fork X'tal

-20

-25

-30 -45 -35 -25 -15 -5 5 15 25 35 45 55 65 75 85 Temperature (ºC)

推进环境管理体系 符合国际标准

在环境管理体系的运行方面,使用 ISO14001 国际环境标准,通过“计 划-实施-检查-验证(PDCA)的循环来实现持续改进。公司位于日本和 海外的主要制造基地已取得了 ISO14001 资格认证。

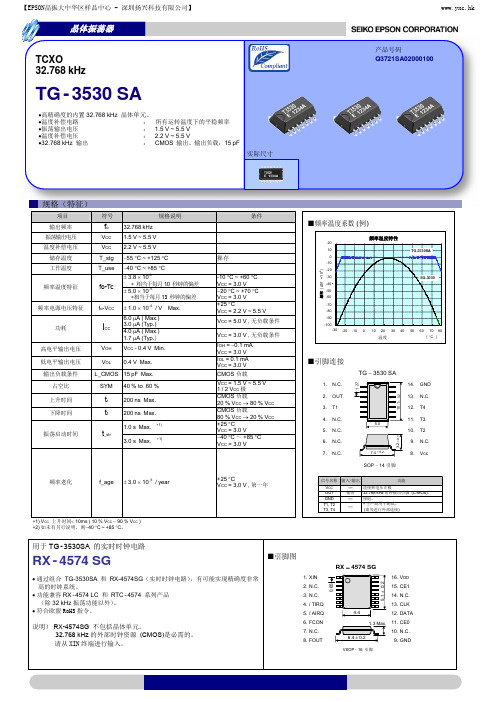

爱普生TG-3530SA晶体振荡器(TCXO)规格书

实际尺寸

规格(特征)

项目 输出频率 振荡输出电压 温度补偿电压 储存温度 工作温度 频率温度特征 符号 规格说明 32.768kHz 1.5V~5.5V 2.2V~5.5V 55C~+125C 40C~+85C 3.810-6 相当于每月 10 秒钟的偏差 5.0106 相当于每月 13 秒钟的偏差 1.010 /V Max.

关于在目录内使用的记号

●无铅。 ●符合欧盟 RoHS 指令。 欧盟 RoHS 指令免检的含铅产品。 (密封玻璃、高温熔化性焊料或其他材料中包含铅。 ) ●适合车用途开发了,高可靠性的产品

注意事项

·本材料如有变更,恕不另行通知。量产设计时请确认最新信息。 ·未经 Seiko Epson 公司书面授权,禁止以任何形式或任何方式复制或者发布本材料中任何部分的信息内容。 ·本材料中的书面信息、应用电路、编程、使用等内容仅供参考。Seiko Epson 公司对第三方专利或版权的侵权行为不负有任何责任。本材料 未对任何专利或知识版权的许可权进行授权。 ·本材料中规格表中的数值大小通过数值线上的大小关系表示。 ·当出口此材料中描述的产品或技术时,你应该遵守相应的出口管制法律和法规,并按照这些法律和法规的要求执行。 请不要将产品(以及任何情况下提供任何的技术信息)用于开发或制造大规模杀伤性武器或其他军事用途。还要求,不要将产品提供给任何 将产品用于此类违禁用途的第三方。 ·此类产品是基于在一般电子机械内使用而设计开发的,如将产品应用于需要极高可靠性的特定用途,必须实现得到弊公司的事前许可。若 无许可弊公司将不负任何责任。 1.太空设备(人造卫星、火箭等) 2.运输车辆机器控制装置(汽车、飞机、火车、船舶等) 3.用于维持生命的医疗器械 4.海底中转设备 5.发电站控制机器 6.防灾防盗装置 7.交通设备 8.其他,用于与 1~7 具有同等可靠性的用途。

epson晶振选型手册

Epson晶振选型手册引言概述:Epson晶振选型手册是一本提供关于Epson晶振选型的专业指导手册。

晶振作为一种重要的电子钟振装置,广泛应用于各类电子设备中,对于设备的稳定性和精准性起到关键作用。

本手册将从多个方面介绍Epson晶振的选型原则和方法,以帮助读者准确选型和应用。

正文内容:1. 晶振的基本原理1.1 晶振的作用与功能1.1.1 提供时钟信号1.1.2 稳定电子设备的工作频率1.1.3 控制和同步各设备之间的通信1.1.4 精确计时和定时功能1.2 晶振的工作原理1.2.1 晶体振荡原理1.2.2 纯谐振条件与频率稳定性1.2.3 晶振的构造与材料选择2. Epson晶振的特点与优势2.1 高稳定性和低功耗2.1.1 稳定性与频率偏移2.1.2 低功耗对电池寿命的影响2.2 宽温度范围和长寿命2.2.1 温度对晶振频率的影响2.2.2 长期使用的可靠性和稳定性2.3 大容量和小封装尺寸2.3.1 容量对数据传输速率的影响2.3.2 封装尺寸对电路板设计的要求3. Epson晶振选型原则3.1 需求分析和参数确定3.1.1 设备类型和用途3.1.2 工作频率和精度要求3.1.3 温度范围和环境影响3.2 选择适合的晶振类型3.2.1 晶振频率范围和精度等级3.2.2 温度补偿和温度响应特性3.2.3 封装尺寸和安装要求3.3 参考设计和测试验证3.3.1 参考电路设计3.3.2 振荡电路测试和频率测量3.3.3 选型结果评估和优化4. Epson晶振选型案例分析4.1 移动方式晶振选型4.1.1 高稳定性和小封装尺寸的需求4.1.2 多频段应用的选择考虑4.2 电子表计晶振选型4.2.1 长期使用和温度范围要求4.2.2 低功耗和电池寿命的平衡4.3 工业自动化控制晶振选型4.3.1 高频率和精度要求4.3.2 多通道同步和控制4.3.3 长寿命和可靠性的考虑5. Epson晶振应用注意事项5.1 环境温度和封装要求5.2 抗振动和抗干扰性能5.3 防静电措施和电源干扰5.4 长期使用和老化问题结语:本手册全面介绍了Epson晶振的选型原则和方法,包括晶振的基本原理、Epson晶振的特点与优势、选型原则、案例分析以及应用注意事项。

Seiko Epson RTC-4543SA SB实时时钟模块应用手册说明书

ETM09E-03Real Time Clock ModuleRTC-4543SA/SB•These products are intended for general use in electronic equipment. When using them in specific applications that require extremelyobtain permission from Seiko Epson in advance./ Space equipment (artificial satellites, rockets, etc.) / Transportation vehicles and related(automobiles, aircraft,Submarine transmitters / Power stations and related / Fire work equipment and securityequipment / traffic control equipment / and others requiring equivalent reliability.•All brands or product names mentioned herein are trademarks and/or registered trademarks of their respective.CONTENTS1. OVERVIEW (1)2. BLOCK DIAGRAM (1)3. PIN CONNECTIONS (2)4. PIN FUNCTIONS (2)5. ELECTRICAL CHARACTERISTICS (3)5-1.A BSOLUTE M AXIMUM R ATINGS (3)5-2.O PERATING C ONDITION (3)5-3.F REQUENCY C HARACTERISTICS (3)5-4.DC C HARACTERISTICS (3)5-5.AC C HARACTERISTICS (4)5-6.T IMING C HARTS (5)6. TIMER DATA ORGANIZATION (6)7. DESCRIPTION OF OPERATION (7)7-1.D ATA READS (7)7-2.D ATA WRITES (7)7-3.D ATA WRITES (D IVIDER R ESET) (8)7-4.FOUT OUTPUT AND 1H Z CARRIES (8)8. EXAMPLES OF EXTERNAL CIRCUITS (9)9. EXTERNAL DIMENSIONS (10)10. LAYOUT OF PACKAGE MARKINGS (10)11. REFERENCE DATA (11)12. APPLICATION NOTES (12)32-kHz Output Serial RTC ModuleRTC - 4543 SA/SBBuilt-in crystal permits operation without requiring adjustmentBuilt-in time counters (seconds, minutes, hours) and calendar counters (days, days of the week months, years)Operating voltage range: 2.5 V to 5.5 VSupply voltage detection voltage: 1.7 ±0.3 VLow current consumption: 1.0 µA/2.0 V (Max.)Automatic processing for leap yearsOutput selectable between 32.768 kHz/1 Hz1. OverviewThis module is a real-time clock with a serial interface and a built-in crystal oscillator. This module is also equipped with clock and calendar circuits, an automatic leap year compensation function, and a supply voltage detection function.In addition, this module has a 32.768 kHz/1 Hz selectable output function for hardware control that is independent of the RTC circuit.This module is available in a compact SOP 14-pin package (RTC-4543SA) and a thin SOP 18-pin package (RTC-4543SB).4. Pin FunctionsSignalPin No.SOP-14pin(SOP-18pin)I/O FunctionGND1( 9 )Connects to negative (-) side (ground) of the power supply.CE3( 8 )InputChip enable input pin.When high,the chip is enabled. When low,the DATA pin goes tohigh impedance and the CLK,DATA,and WR pins are not able toaccept input.In addition, when low,the TM bit is cleared.FSEL4( 7 )InputSerect the frequency that is output from the FOUT pin.High : 1 HzLow : 32.768 kHzWR5( 6 )InputDATA pin input/output switching pin.High : DATA input (when writing the RTC)Low : DATA output (when reading the RTC)FOE6( 5 )InputWhen high, the frequency selected by the FSEL pin is output fromthe FOUT pin.When low, the FOUT pin goes to high impedance.V DD9( 14 )Connects to positive (+) side of the power supply.CLK10( 12 )InputSerial clock input pin.Data is gotten at the rising edge during a write, and data is outputat the rising edge during a read.DATA11( 11 )Bi-directional Input/outout pin that is used for writing and reading data.FOUT14( 10 )OutputOutputs the frequency selected by the FSEL pin. 1 Hz output issynchronized with the internal one-second signal.This output is not affected by the CE pin.N.C.2,7,8,12,13( 1,2,3,4,13,15,16,17,18 )Although these pins are not connected internally,they shouldalways be left open in order to obtain the most stable oscillationpossible.* Always connect a passthrough capacitor of at least 0.1 µF as close as possible between V DD and GND.5. Electrical Characteristics5-1. Absolute Maximum RatingsItem Symbol Conditions Min. Max. Unit Supply voltage V DD-0.3 7.0 VInput voltage V I Ta=+25 °C GND-0.3 V DD+0.3 VOutput voltage V O GND-0.3 V DD+0.3 V Storage temperature T STG- -55 +125 °C5-2. Operating ConditionItem Symbol Conditions Min. Max. Unit Operating supplyV DD- 2.5 5.5 V voltageData holding voltage V CLK- 1.4 5.5 VOperating temperature T OPR No condensation-40 +85 °C5-3. Frequency CharacteristicsItem Symbol Conditions Max. Unit Frequency tolerance ∆f/f O Ta=+25 °C , V DD=5.0 V 5 ± 23 * ×10-6Frequency temperatureT op-10to+70 °C +25 °C ref + 10 / - 120 ×10-6 characteristicsFrequency voltagef/V Ta=+25 °C , V DD=2.0 to 5.5 V ± 2 ×10-6/V characteristicsOscillation start time t STA Ta=+25 °C , V DD=2.5 V 3 s Aging fa Ta=+25 °C , V DD=5 V , first year ± 5 ×10-6 * Monthly deviation: Approx. 1 min.5-4. DC CharacteristicsUnless specified otherwise: V DD = 5 V ± 10 %, Ta = - 40 to +85 °C Item Symbol Conditions Min. Typ. Max. Unit Current consumption(1) I DD1 V DD=5.0 V CE=L , FOE=L 1.5 3.0 µA Current consumption(2) I DD2 V DD=3.0 V FSEL=H 1.0 2.0 µA Current consumption(3) I DD3 V DD=2.0 V 0.5 1.0 µA Current consumption(4) I DD4 V DD=5.0 V CE=L , FOE=H 4.0 10.0 µA Current consumption(5) I DD5 V DD=3.0 V FSEL=L 2.5 6.5 µA Current consumption(6) I DD6 V DD=2.0 V No load on the1.5 4.0 µAFOUT pinInput voltage V IH WR,DATA,CE,CLK, 0.8 V DD VV IL FOE,FSEL pins 0.2 V DD V0.5 µAInput off/leak current I OFF WR,CE,CLK,FOE,FSEL pinsV IN = V DD or GNDV OH(1)V DD=5.0 V I OH=-1.0 mA 4.5 V Output voltage V OH(2)V DD=3.0 V DATA , FOUT pins 2.0 VV OL(1)V DD=5.0 V I OL= 1.0 mA 0.5 VV OL(2)V DD=3.0 V DATA , FOUT pins0.8 VOutput load conditionN / CL FOUT pin 2 LSTTL / 30 pF Max.( fanout )Output leak current I OZH V OUT=5.5 V DATA , FOUT pins-1.0 1.0 µAI OZL V OUT=0 V DATA , FOUT pins-1.0 1.0 µASupply voltage detectionV DT- 1.4 1.7 2.0 V voltage5-5. AC CharacteristicsUnless specified otherwise: Ta = - 40 to +85 °C, CL = 50 pF Item Symbol V DD=5 V ± 10 % V DD=3 V ± 10 % UnitMin. Max. Min. Max.CLK clock cycle t CLK0.75 7800 1.5 7800 µsCLK low pulse width t CLKL0.375 3900 0.75 3900 µsCLK high pulse width t CLKH0.375 3900 0.75 3900 µs CLK setup time t CLKS25 50 nsCE setup time t CES0.375 3900 0.75 3900 µsCE hold time t CEH0.375 0.75 µsCE enable time t CE0.9 0.9 s Write data setup time t SD0.1 0.2 µsWrite data hold time t HD0.1 0.1 µs WR setup time t WRS100 100 nsWR hold time t WRH100 100 ns DATA output delay time t DATD0.2 0.4 µsDATA output floating time t DZ0.1 0.2 µs Clock input rise time t r150 100 nsClock input fall time t f150 100 ns FOUT rise time (CL=30 pF) t r2100 200 ns FOUT fall time (CL=30 pF) t f2100 200 ns Disable time (CL=30 pF) t XZ100 200 nsEnable time (CL=30 pF) t ZX100 200 nsFOUT duty ratio (CL=30 pF) Duty 40 60 40 60 % Wait time t RCV0.95 1.9 µs5-6. Timing Charts[]Duty t t100%H=×( 4 ) Disable/enable6. Timer Data Organization• The counter data is BCD code.• Writes and reads are both performed on an LSB-first basis.MSBLSBSecond ( 0 to 59 )FDTs40s20s10s8s4s2s1Minutes ( 0 to 59 ) * mi40mi20mi10mi8mi4mi2mi1Hour ( 0 to 23 ) * *h20h10h8h4h2h1Day of the week( 1 to 7 )*w4w2w1Day ( 1 to 31 ) * *d20d10d8d4d2d1Month ( 1 to 12 ) TM **mo10mo8mo4mo2mo1Year ( 0 to 99 )y80y40y20y10y8y4y2y1• Calendar counter. From 1 Jan 2001 to 31 Dec 2099, it is updated by an automatic calendar function.If a year is 4 multiples, it is a leap year, then date is updatedin order to 28 Feb, 29 Feb, Mar 1.Because there is the case that a leap year does not match when using data of year of except the Christian era, please be careful.Data of a day of the week run in cycles with 7 from 1.A recommended example are 1=Sun, 2=Mon,,,6=Fri, 7=Sat.• Clock counter. Only 24 hours system is supported. • ∗bits. These bits are used as memory.• TM bit. This is a test bit for shipping test. Always clear this bit to “0”.• FDT bit: Supply voltage detection bit• This bit is set to “1” when voltage of 1.7 ±0.3 V or less is detected between V DD and GND. • The FDT bit is cleared if all of the digits up to the year digits are read.• Although this bit can be both read and written, clear this bit to "0" in case of the write cycle.if the supply voltage is lower than the detection voltage value, the FDT bit is set to “1”.7. Description of Operation2) At the first rising edge of the CLK signal, the clock and calendar data are loaded into the shiftregister and the LSB of the seconds digits is output from the DATA pin.3) The remaining seconds, minutes, hour, day of the week, day, month, and year data is shifted out,in sequence and in synchronization with the rising edge of the CLK signal, so that the data isoutput from the DATA pin.The output data is valid until the rising edge of the 52nd clock pulse; even if more than 52 clockpulses are input,the output data does not change.4) If data is required in less than 52 clock pulses, that part of the data can be gotten by setting theCE pin low after the necessary number of clock pulses have been output.Example: If only the data from “seconds” to “day of the week” is needed:After 28 clock pulses, set the CE pin low in order to get the data from “seconds” to “day ofthe week.”5) When performing successive data read operations, a wait (tRCV) is necessary after the CE pinis set low.6) Note that if an update operation (a one-second carry) occurs during a data read operation,the data that is read will have an error of -1 second.7) Complete data read operations within tCE (Max.) = 0.9 seconds, as described earlier.1) RTC 4543 shifts to data input state by condition of WR terminal ="H",CE terminal ="H".2) Writing-data synchronize to a rising edge of CLK, and it inputs into an RTC from LSB of sec.3) Inside counter less than second is reset between falling edges of first CLK from a rising edge of next CLK.And update of Clock register is prohibited by the first falling edge of CLK.4) In writing of data to RTC, all 52 clock is necessary.When CE goes to LOW before the 52 bits transmission is completed, there is the possibilitythat * ,FDT and a year digit were destroyed.If a serial communication break occurs, do verify 8 bits of* bit andFDTbit and year data.5) In a rising edge of 52 clock, all data is written to RTC. Data after 53 bits is ignored.6) When CE goes to LOW, RTC re-starts update.Please finish write access within 0.9 second = tCE (Max.).7) Between write access and read access, recovery timing(tRCV) is necessary.Please do not set the time and date which is non-existence.7-3. Data writes (Divider Reset)After the counter is reset, carries to the seconds digit are halted.After the data write operation,the prohibition on carries to the seconds counter is lifted by setting the CE pin low.Complete data write operations within tCE (Max.) = 0.9 seconds, as described earlier.7-4. FOUT output and 1 Hz carriesDuring a data write operation, because a reset is applied to the Devider counter (from the 128 Hzlevel to the 1 Hz level) after the CE pin goes high during the time between the falling edge of the first clock cycle and the rising edge of the second clock cycle, the length of the first 1 Hz cycle after thedata write operation is 1.0 s +0 / −7.8ms +t CES+t CLK. Subsequent cycles are output at1.0-second intervals.The 1-Hz signal that is output on FOUT is the internal 1-Hz signal with a 15.6-ms shift applied.8. Examples of External Circuits11. Reference DataNote : This data shows values obtained from a sample lot.12. Application notes1) Notes on handlingThis module uses a C-MOS IC to realize low power consumption. Carefully note the following cautions when handling.(1) Static electricityWhile this module has built-in circuitry designed to protect it against electrostatic discharge, the chip could still be damaged bya large discharge of static electricity. Containers used for packing and transport should be constructed of conductive materials.In addition, only soldering irons, measurement circuits, and other such devices which do not leak high voltage should be used with this module, which should also be grounded when such devices are being used.(2) NoiseIf a signal with excessive external noise is applied to the power supply or input pins, the device may malfunction or "latch up."In order to ensure stable operation, connect a filter capacitor (preferably ceramic) of greater that 0.1 µF as close as possible to the power supply pins (between VDD and GNDs). Also, avoid placing any device that generates high level of electronic noise near this module.* Do not connect signal lines to the shaded area in the figure shown in Fig. 1 and, if possible, embed this area in a GND land.(3) Voltage levels of input pinsWhen the input pins are at the mid-level, this will cause increased current consumption and a reduced noise margin, and can impair the functioning of the device. Therefore, try as much as possible to apply the voltage level close to VDD or GND.(4) Handling of unused pinsSince the input impedance of the input pins is extremely high, operating the device with these pins in the open circuit state can lead to unstable voltage level and malfunctions due to noise. Therefore, pull-up or pull-down resistors should be provided for all unused input pins.2) Notes on packaging(1) Soldering heat resistance.If the temperature within the package exceeds +260 °C, the characteristics of the crystal oscillator will be degraded and it may be damaged. The reflow conditions within our reflow profile is recommended. Therefore, always check the mounting temperature and time before mounting this device. Also, check again if the mounting conditions are later changed.* See Fig. 2 profile for our evaluation of Soldering heat resistance for reference.(2) Mounting equipmentWhile this module can be used with general-purpose mounting equipment, the internal crystal oscillator may be damaged in some circumstances, depending on the equipment and conditions. Therefore, be sure to check this. In addition, if the mounting conditions are later changed, the same check should be performed again.(3) Ultrasonic cleaningDepending on the usage conditions, there is a possibility that the crystal oscillator will be damaged by resonance during ultrasonic cleaning. Since the conditions under which ultrasonic cleaning is carried out (the type of cleaner, power level, time, state of the inside of the cleaning vessel, etc.) vary widely, this device is not warranted against damage during ultrasonic cleaning.(4) Mounting orientationThis device can be damaged if it is mounted in the wrong orientation. Always confirm the orientation of the device before mounting.(5) Leakage between pinsLeakage between pins may occur if the power is turned on while the device has condensation or dirt on it. Make sure the device is dry and clean before supplying power to it.Application ManualElectronic devices information on WWW serverDistributor/en/quartz/index.html。

使用实时时钟模块的高精度对时

·低于 1 秒计时器重置待命

[扩充寄存器②]

*1

Reg(2F)h←(41)h Write

(ECP=0,EHL=1,ET1=0,ET0=0,ERST=1)

·年月日的设定

[Bank1]

Reg(6)h←(14)h Write[年]

Reg(5)h←(04)h Write[月]

*2

Reg(4)h←(18)h Write[日]

很多爱普生的实时时钟模块搭载了 RESET 功能,可使用软件对上述低于 1 秒的误差进行调节。但是,使用软件调节时间的方 法会因软件处理时间而产生时间偏差。这对需要以精确时间实现同步的用户来说,这个误差也须解决。为此,4803 系列和 8803 系列又搭载了使用硬件调节时间的 ERST 功能。

本次说明内建 TCXO 数字式实时时钟模块 4803 系列与 8803 系列所搭载的用于调节低于 1 秒时间的 RESET 功能及 ERST 功 能,并使用时序图等以具体实例进行说明。

技术说明

使用实时时钟模块的高精度对时

搭载秒以下时间调节功能的爱普生实时时钟模块之解说

【序文】 近年,随着电波手表的普及以及可从 NTP 时间服务器获取标准时间等,获取极为准确的时间已不再繁琐劳神。因此,用于金

融、交通管理、电力控制、安全及体育等应用系统设计一般均以可参照正确时间为基础。这类处理系统在数据输入、输出部分必 须设置为数众多的终端设备,且这些终端设备也需要有正确的时间。为了回应上述需求,爱普生向市场提供了内建以高稳定频率 振荡的石英晶体单元的实时时钟模块。

·SEC 寄存器的设定(清除进位信息) [Bank1] Reg(0)h←(00)h Write[秒]

·低于 1 秒计时器重置待命

[Bank3]

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

× 10-6

AA Ta = +25 ºC

5 ± 5.0∗3

(1)

IDD1

, VDD = 5V

-

0.75

3.4

(2)

FOE = GND,output : OFF

VDD = 3V

-

0.75

2.1

µA

∗1 )

9

∗2 )

13

∗3 )

13

(

)

Frequency tolerance ( ×10-6 )

【EPSON晶振大中华区样品中心 - 深圳扬兴科技有限公司】

www.yxc.hk

(SPI-Bus)

DTCXO多

RX - 4803 SA / LC

• 32.768 kHz •1/100s • • • • • •

(

) DTCXO

:4

: 1.6 V ~ 5.5 V

: 2.2 V ~ 5.5 V

: 1.6 V ~ 5.5 V

5 32.768 kHz DTCXO

0

-5

-10

-15 Tuning fork X'tal

-20

-25

-30 -45 -35 -25 -15 -5

5 15 25 35 45 55 65 75 85

Temperature (ºC)

【EPSON晶振大中华区样品中心 - 深圳扬兴科技有限公司】

www.yxc.hk

1.太空设备(人造卫星、火箭等) 2.运输车辆机器控制装置(汽车、飞机、火车、船舶等) 3.用于维持生命的医疗器械 4.海底中转设备 5.发电站控制机器 6.防灾防盗装置 7.交通设备 8.其他,用于与 1~7 具有同等可靠性的用途。

本材料中记载的品牌名称或产品名称是其所有人的商标或注册商标。

Seiko Epson Corporation

3.2 ± 0.1

10.1 ± 0.2

14. DI 13. DO 12. T2(VPP) 11. GND 10. / INT

9. EVIN 8. N.C.

1. N.C. 2. FOE 3. VDD 4. FOUT 5. CLK 6. CE

0.5

( :mm)

RX − 4803 LC

12. EVIN

3.6

VDD

1.6

3.0

5.5

V

10

VTEM

2.2

3.0

5.5

V

VCLK

1.6

3.0

5.5

V

TOPR

−

-40

+25

+85

ºC

UA UB ∆ f / f UC

Ta = -40 ºC ~ +85 ºC Ta = -40 ºC ~ +85 ºC Ta = -30 ºC ~ +70 ºC

±3.4 ∗1 ±5.0 ∗2

出的环境管理国际标准。

追求高品质

Seiko Epson 为了向顾客提供高品质、卓越信赖性的产品、服务,迅 速着手通过 ISO 9000 系列资格认证的工作,其日本和海外工厂也在通 过 ISO 9001 认证。同时,也在通过大型汽车制造厂商要求规格的 ISO/TS 16949 认证。

ISO/TS16949 是一项国际标准,是在 ISO9001 的基础上增 加了对汽车工业的特殊要求部分。

推进环境管理体系 符合国际标准

在环境管理体系的运行方面,使用 ISO14001 国际环境标准,通过“计 划-实施-检查-验证(PDCA)的循环来实现持续改进。公司位于日本和 海外的主要制造基地已取得了 ISO14001 资格认证。

ISO 14000 是国际标准化组织于 1996 年在全球化变暖、臭 氧层破坏、以及全球毁林等环境问题日益严重的背景下提

9

器

13

器

•

:

1/100s

.

• 32.768 kHz • FOUT •

(C-MOS ), CL=30 pF 32.768 kHz, 1024 Hz, 1 Hz.

• • • • EVIN

1/4096 ,,

4095 .

• 1PPS

•

RX-4801

*

,

32.768kHz .

CE CLK FOUT

TEST

VDD

INTERFACE CIRCUIT

CLOCK and CALENDAR

TIMER REGISTER

ALARM REGISTER

SYSTEM CONTROLLER

and CONTROL REGISTER

• •UA •UB •UC •AA

± 3.4 x 10-6 / -40 ºC ~ +85 ºC 商

± 5.0 x 10-6 / -40 ºC ~ +85 ºC 商 ± 5.0 x 10-6 / -30 ºC ~ +70 ºC (+5 ± 5.0) x 10-6 / +25 ºC

11. /INT

10. GND

2.4

9. T2(Vpp)

1.2 Max.

8. DO

2.8

7. DI

VSOJ − 12pin

型 LC

多 LC

∗

32.768 kHz-DTCXO Frequency temperature characteristics (Example)

Min.

Typ.

Max.

Frequency temperature characteristics

未对任何专利或知识版权的许可权进行授权。 ·本材料中规格表中的数值大小通过数值线上的大小关系表示。 ·当出口此材料中描述的产品或技术时,你应该遵守相应的出口管制法律和法规,并按照这些法律和法规的要求执行。

请不要将产品(以及任何情况下提供任何的技术信息)用于开发或制造大规模杀伤性武器或其他军事用途。还要求,不要将产品提供给任何 将产品用于此类违禁用途的第三方。 ·此类产品是基于在一般电子机械内使用而设计开发的,如将产品应用于需要极高可靠性的特定用途,必须实现得到弊公司的事前许可。若 无许可弊公司将不负任何责任。

32.768 kHz, 1024 Hz, 1Hz.

,

,

,EVIN

Linux

(/cn/information/support/linux_rtc/)

LMI(Linux Mark Institute)

Linux®

商

器

RX-4803SA : X1B000131xxxx00

关于在目录内使用的记号

●无铅。

●符合欧盟 RoHS 指令。 欧盟 RoHS 指令免检的含铅产品。 (密封玻璃、高温熔化性焊料或其他材料中包含铅。)

●为汽车方面的应用,如汽车多媒体、车身电子、遥控无钥门锁等。

●为汽车行驶安全方面的应用(引擎控制单元、气囊、电子稳定程序控制系统)。

注意事项

·本材料如有变更,恕不另行通知。量产设计时请确认最新信息。 ·未经 Seiko Epson 公司书面授权,禁止以任何形式或任何方式复制或者发布本材料中任何部分的信息内容。 ·本材料中的书面信息、应用电路、编程、使用等内容仅供参考。Seiko Epson 公司对第三方专利或版权的侵权行为不负有任何责任。本材料

RX-4803LC : X1B000122xxxx00

RX-4803LC UB : X1B000122000200

RX-4803SA

RX-4803LC

FOE FOUT

EVIN / INT

DI DO CLK CE

32.768 kHz

32kHz DTCXO

DIVIDER

FOUT CONTROLLER

INTERRUPT CONTROLLER

-

FOE

EVIN

/ INT

GND

-

T2(VPP)

-

DO

DI

FOUT 商 N-ch

( CMOS

)

RX-4803SA

器

/

1. CE 2. CLK 3. FOUT 4. N.C. 5. TEST 6. VDD 7. FOE

1.27

RX − 4803 SA

5.0 7.4 ± 0.2 SOP − 14 pin