2001年北京科技大学电路及数字电子技术考研试题

北京科技大学计算机组成原理历年考研真题汇编附答案

北京科技大学计算机组成原理历年考研真题汇编最新资料,WORD格式,可编辑修改!目录2014年北京科技大学869计算机组成原理考研真题 ................................. 2013年北京科技大学869计算机组成原理考研真题 ................................. 2009年北京科技大学829计算机组成原理考研真题 ................................. 2001年北京科技大学计算机组成原理考研真题...................................... 2000年北京科技大学计算机组成原理考研真题...................................... 1999年北京科技大学计算机组成原理考研真题...................................... 说明:北京科技大学计算机组成原理专业的科目代码2009年为829,,之后改为869。

北京科技大学计算机与通信工程学院、国家材料服役安全科学中心、冶金工程研究院均考此科目。

2014年北京科技大学869计算机组成原理考研真题试题编号:869______试题名称:计算机组成原理(共9页)适用专业:计算机科学与技术、软件工程、计算机技术(专业学位)、 软件工程(专业学位)______说明:所有答案必须写在答题纸上,做在试题或草稿纸上无效。

一、填空(满分40分,每题2分)1.存储程序原理是指______,它是______型计算机体系结构的核心思想。

2.设浮点数长16位,高8位是阶码,含1位阶符,低8位是尾数,含1位数符,阶码和尾数均用补码表示,基值(底)为2,尾数为规格化、无隐藏位,机器数为FC .60H 的十进制真值是______,十进制真值ll/128的规格化浮点编码是______(16进制助记形式)。

3.已知[x]补=x 0.x 1x 2...x n ,则[-x]补=______。

数字电子技术试卷试题答案汇总-数字电子考试

数字电子技术基础试卷试题答案汇总一、 填空题(每空1分,共20分)1、逻辑代数中3种基本运算是(与运算、或运算、非运算)2、逻辑代数中三个基本运算规则 (代入规则、反演规则、对偶规则)3、逻辑函数的化简有 公式法 , 卡诺图 两种方法。

4、A+B+C= A ’B ’C ’ 。

5、TTL 与非门的u I ≤U OFF 时,与非门 关闭 ,输出 高电平 ,u I ≥U ON 时,与非门 导通 ,输出 低电平 。

6、组合逻辑电路没有 记忆 功能。

7、竞争冒险的判断方法 代数方法 , 卡诺图法 。

8、触发器它2 稳态,主从RS 触发器的特性方程Q ’’=S+RQ ’ SR=0 ,主从JK 触发器的特性方Q ’’=JQ ’+K ’Q ,D 触发器的特性方程 Q ’’=D 。

二、 选择题(每题1分,共10分)1、相同为“0”不同为“1”它的逻辑关系是 ( C ) A 、或逻辑 B 、与逻辑 C 、异或逻辑2、Y (A ,B ,C ,)=∑m (0,1,2,3)逻辑函数的化简式 ( C ) A 、Y=AB+BC+ABC B 、Y=A+B C 、Y=A (A)3、A 、Y=AB B 、Y 处于悬浮状态C 、Y=B A +4、下列图中的逻辑关系正确的是 ( A )A.Y=B A +B.Y=B A +C.Y=AB5、下列说法正确的是 ( A ) A 、主从JK 触发器没有空翻现象 B 、JK 之间有约束 C 、主从JK 触发器的特性方程是CP 上升沿有效。

6、下列说法正确的是 ( C )A 、同步触发器没有空翻现象B 、同步触发器能用于组成计数器、移位寄存器。

C 、同步触发器不能用于组成计数器、移位寄存器。

7、下列说法是正确的是 ( A )A 、异步计数器的计数脉冲只加到部分触发器上B 、异步计数器的计数脉冲同时加到所有触发器上C 、异步计数器不需要计数脉冲的控制8、下列说法是正确的是 ( A )A 、施密特触发器的回差电压ΔU=U T+-U T-B 、施密特触发器的回差电压越大,电路的抗干扰能力越弱C 、施密特触发器的回差电压越小,电路的抗干扰能力越强9、下列说法正确的是( C )A、多谐振荡器有两个稳态B、多谐振荡器有一个稳态和一个暂稳态C、多谐振荡器有两个暂稳态10、下列说法正确的是( A )A、555定时器在工作时清零端应接高电平B、555定时器在工作时清零端应接低电平C、555定时器没有清零端三、判断题(每题1分,共10分)1、A+AB=A+B (错)2、当输入9个信号时,需要3位的二进制代码输出。

历年北京科技大学硕士学位研究生入学考试试题

-1-

硕士学位研究生入学考试试题

一、选择题(每题3分,共30分)

1、以下五种运动形式中,a 保持不变的运动是

(A) 单摆的运动. (B) 匀速率圆周运动.

(C) 行星的椭圆轨道运动. (D) 抛体运动.

(E) 圆锥摆运动. [ ]

2、人造地球卫星绕地球作椭圆轨道运动,卫星轨道近地点和远地点分别为A 和

B .用L 和E K 分别表示卫星对地心的角动量及其动能的瞬时值,则应有

(A) L A >L B ,E KA >E kB . (B) L A =L B ,E KA <E KB .

(C) L A =L B ,E KA >E KB . (D) L A <L B ,E KA <E KB . [ ]

3、一质量为m 的滑块,由静止开始沿着1/4圆弧形光滑

的木槽滑下.设木槽的质量也是m .槽的圆半径为R ,放在光滑水平地面上,如图所示.则滑块离开槽时的速度是

(A) Rg 2.

(B) Rg . (C) Rg 2 (D) Rg 21. (E) Rg 22

1 . [ ] 4、均匀细棒OA 可绕通过其一端O 而与棒垂直的水平固定光滑轴转动,如图所示.今使棒从水平位置由静止开始自由下落,在棒摆动到竖直位置的过程中,下述说法哪一种是正确的?

(A) 角速度从小到大,角加速度从大到小.

(B) 角速度从小到大,角加速度从小到大.

(C) 角速度从大到小,角加速度从大到小.

(D) 角速度从大到小,角加速度从小到大. [ ]。

北京科技大学(已有10试题)

北京科技大学土木与环境工程学院地质学2003——2010工程流体力学2003——2005,2007——2010结构力学2004,2007——2010安全原理2008——2010生物化学2005岩石力学2000——2005,2007——2010晶体光学2004——2006,2008——2010普通化学2006——2010普通化学(A)2004——2005结晶学及矿物学2003——2005,2008材料力学2003(注:试卷上面标注的是:材料加工工程专业)材料力学B 2004——2005(注:试卷上面标注的是:材料加工工程、材料科学与工程专业)材料力学2003(注:试卷上面标注的是:车辆工程、机械制造及自动化、机械电子工程、机械设计及理论、固体力学专业)材料力学C 2010(注:试卷上面标注的是:车辆工程、物流工程、机械工程专业)材料力学C 2004——2008(注:试卷上面标注的是:车辆工程、机械制造及自动化、机械电子工程、机械设计及理论、机械工程、物流工程、机械装备及控制专业)材料力学D 2004——2005,2007——2010(注:试卷上面标注的是:固体力学专业)电工技术2003——2005,2008——2010化工原理2003——2005普通地质学2003,2005,2007,2010流体力学2003——2008水处理原理2003——2010钢筋混凝土结构2003——2005工程地质学2003——2005微生物学A 2008——2010微生物学B 2008——2010微生物学2007环境微生物学2004——2005环境规划与管理2007——2010有机化学A(分析化学专业)2004有机化学(分析化学专业)2005有机化学(生物化工、环境科学专业)2004有机化学(生物化工专业)2003有机化学B(生物化工、环境科学、环境工程专业)2005有机化学(B)(化学专业)2010有机化学(B)(分析化学、无机化学、有机化学、物理化学专业)2007——2008 建筑材料学2004——2005矿床学2003——2004矿山岩石力学2007——2010浮选原理2008——2010土力学2004——2005土力学与地基基础2003液压与液力传动2003——2005环境学2004——2005单考数学2003——2004,2008——2010单考俄语2008——2010单考英语2008——2010单考政治2008——2010冶金与生态工程学院传输原理2003——2010冶金物理化学2003——2010普通生态学2006——2010普通物理2008——2010普通物理(A)2004——2005普通化学2006——2010普通化学(A)2004——2005物理化学(A)2003——2010物理化学(B)2005——2010综合科技史2003——2010文物保护基础2004——2006,2008——2010中国古代史2004——2010社会学理论2010社会学2003——2008材料力学2003(注:试卷上面标注的是:材料加工工程专业)材料力学B 2004——2005(注:试卷上面标注的是:材料加工工程、材料科学与工程专业)材料力学2003(注:试卷上面标注的是:车辆工程、机械制造及自动化、机械电子工程、机械设计及理论、固体力学专业)材料力学C 2010(注:试卷上面标注的是:车辆工程、物流工程、机械工程专业)材料力学C 2004——2008(注:试卷上面标注的是:车辆工程、机械制造及自动化、机械电子工程、机械设计及理论、机械工程、物流工程、机械装备及控制专业)材料力学D 2004——2005,2007——2010(注:试卷上面标注的是:固体力学专业)钢筋混凝土结构2003——2005微生物学A 2008——2010微生物学B 2008——2010微生物学2007环境微生物学2004——2005生物化学2005统计物理2003——2005,2010单考数学2003——2004,2008——2010单考俄语2008——2010单考英语2008——2010单考政治2008——2010材料科学与工程学院物理化学(A)2003——2010物理化学(B)2005——2010材料化学2005金属学2003——2005,2007——2010材料力学2003(注:试卷上面标注的是:材料加工工程专业)材料力学B 2004——2005(注:试卷上面标注的是:材料加工工程、材料科学与工程专业)材料力学2003(注:试卷上面标注的是:车辆工程、机械制造及自动化、机械电子工程、机械设计及理论、固体力学专业)材料力学C 2010(注:试卷上面标注的是:车辆工程、物流工程、机械工程专业)材料力学C 2004——2008(注:试卷上面标注的是:车辆工程、机械制造及自动化、机械电子工程、机械设计及理论、机械工程、物流工程、机械装备及控制专业)材料力学D 2004——2005,2007——2010(注:试卷上面标注的是:固体力学专业)钢筋混凝土结构2003——2005统计物理2003——2005,2010传输原理2003——2010冶金物理化学2003——2010普通化学2006——2010普通化学(A)2004——2005综合科技史2003——2010文物保护基础2004——2006,2008——2010社会学理论2010社会学2003——2008设计基础2004——2006,2008——2010设计理论2004——2010传热学2003——2005,2007——2010工程热力学2003——2005,2007——2010生产运作与管理2003——2004现代生产管理2005,2007——2010电路及数字电子技术2003——2010通信原理2004——2010计算机组成原理及数据结构2006——2008计算机组成原理2003计算机组成原理及计算机网络2004——2005计算机组成原理及计算机系统结构2004——2005数据结构1999——2000,2003(2003有答案)数据结构及软件工程2004——2005高等代数2003——2010数学分析2004——2010常微分方程2003——2005概率统计2004——2005概率与数理统计2003——2005普通物理2008——2010普通物理(A)2004——2005固体物理2007——2010固体物理(A)2003——2005量子力学2007——2010量子力学(B)2003——2005(2004有答案)热力学与统计物理(B)2003——2005基础化学2003——2005无机化学2003——2010有机化学A(分析化学专业)2004有机化学(分析化学专业)2005有机化学(生物化工、环境科学专业)2004有机化学(生物化工专业)2003有机化学B(生物化工、环境科学、环境工程专业)2005有机化学(B)(化学专业)2010有机化学(B)(分析化学、无机化学、有机化学、物理化学专业)2007——2008 综合化学(含有机化学、分析化学)2004模拟电子技术与数字电子技术基础2004——2010(注:2007年试卷共4页,缺P4)理论力学(A)2005,2007——2010理论力学(B)2003——2005微生物学A 2008——2010微生物学B 2008——2010微生物学2007环境微生物学2004——2005单考数学2003——2004,2008——2010单考俄语2008——2010单考英语2008——2010单考政治2008——2010机械工程学院设计基础2004——2006,2008——2010设计理论2004——2010材料力学2003(注:试卷上面标注的是:材料加工工程专业)材料力学B 2004——2005(注:试卷上面标注的是:材料加工工程、材料科学与工程专业)材料力学2003(注:试卷上面标注的是:车辆工程、机械制造及自动化、机械电子工程、机械设计及理论、固体力学专业)材料力学C 2010(注:试卷上面标注的是:车辆工程、物流工程、机械工程专业)材料力学C 2004——2008(注:试卷上面标注的是:车辆工程、机械制造及自动化、机械电子工程、机械设计及理论、机械工程、物流工程、机械装备及控制专业)材料力学D 2004——2005,2007——2010(注:试卷上面标注的是:固体力学专业)理论力学(A)2005,2007——2010理论力学(B)2003——2005传热学2003——2005,2007——2010工程热力学2003——2005,2007——2010工程流体力学2003——2005,2007——2010生产运作与管理2003——2004现代生产管理2005,2007——2010单考数学2003——2004,2008——2010单考俄语2008——2010单考英语2008——2010单考政治2008——2010信息工程学院自动检测技术2007——2010电路及数字电子技术2003——2010通信原理2004——2010概率统计2004——2005计算机组成原理及数据结构2006——2008计算机组成原理2003计算机组成原理及计算机网络2004——2005计算机组成原理及计算机系统结构2004——2005数据结构1999——2000,2003(2003有答案)数据结构及软件工程2004——2005信号系统与数字电路2008——2010单考数学2003——2004,2008——2010单考俄语2008——2010单考英语2008——2010单考政治2008——2010经济管理学院管理学与经济学基础2006——2010(注:2006年缺页)管理学原理2004——2010(2004——2005有答案)数据库原理与管理系统2003单考数学2003——2004,2008——2010单考俄语2008——2010单考英语2008——2010单考政治2008——2010应用科学学院高等代数2003——2010数学分析2004——2010常微分方程2003——2005概率统计2004——2005概率与数理统计2003——2005普通物理2008——2010普通物理(A)2004——2005固体物理2007——2010固体物理(A)2003——2005量子力学2007——2010量子力学(B)2003——2005(2004有答案)热力学与统计物理(B)2003——2005基础化学2003——2005无机化学2003——2010分析化学2006——2010物理化学(A)2003——2010物理化学(B)2005——2010有机化学A(分析化学专业)2004有机化学(分析化学专业)2005有机化学(生物化工、环境科学专业)2004有机化学(生物化工专业)2003有机化学B(生物化工、环境科学、环境工程专业)2005有机化学(B)(化学专业)2010有机化学(B)(分析化学、无机化学、有机化学、物理化学专业)2007——2008 综合化学(含有机化学、分析化学)2004模拟电子技术与数字电子技术基础2004——2010(注:2007年试卷共4页,缺P4)材料力学2003(注:试卷上面标注的是:材料加工工程专业)材料力学B 2004——2005(注:试卷上面标注的是:材料加工工程、材料科学与工程专业)材料力学2003(注:试卷上面标注的是:车辆工程、机械制造及自动化、机械电子工程、机械设计及理论、固体力学专业)材料力学C 2010(注:试卷上面标注的是:车辆工程、物流工程、机械工程专业)材料力学C 2004——2008(注:试卷上面标注的是:车辆工程、机械制造及自动化、机械电子工程、机械设计及理论、机械工程、物流工程、机械装备及控制专业)材料力学D 2004——2005,2007——2010(注:试卷上面标注的是:固体力学专业)理论力学(A)2005,2007——2010理论力学(B)2003——2005生物化学与分子生物学2008——2010细胞生物学2007——2010微生物学A 2008——2010微生物学B 2008——2010微生物学2007环境微生物学2004——2005运筹学2007——2008单考数学2003——2004,2008——2010单考俄语2008——2010单考英语2008——2010单考政治2008——2010文法学院文学原理2010中国语言文学2010民法学2004——2010综合考试(民商法学、经济法学专业)2005——2010合同法2004民事诉讼法2004知识产权法2004社会学研究方法2007——2010社会学理论2010社会学2003——2008马克思主义哲学原理2007——2010马克思主义政治经济学原理2007——2010文艺美学2004文艺学原理2004——2005,2007——2008中国文论史2005,2007——2008历史唯物主义2004——2005思想政治教育原理2003——2010科学技术史2007——2010科学技术概论2007——2010现代科学技术概论2005综合科技史2003——2010行政管理学2003——2010政治经济学2003——2005教育史2005(2005有答案)普通教育学2003——2005,2007——2010(2004——2005有答案)管理学原理2004——2010(2004——2005有答案)普通心理学2003——2005,2007——2010计算机基础2003——2005,2007——2010教育学专业基础综合(全国统考试卷)2007——2008单考数学2003——2004,2008——2010单考俄语2008——2010单考英语2008——2010单考政治2008——2010外国语学院二外法语2004——2010二外日语2004——2010二外俄语2004——2010二外德语2004——2008综合英语2003——2006,2008——2010基础英语2004——2010新金属材料国家重点实验室物理化学(A)2003——2010物理化学(B)2005——2010金属学2003——2005,2007——2010材料力学2003(注:试卷上面标注的是:材料加工工程专业)材料力学B 2004——2005(注:试卷上面标注的是:材料加工工程、材料科学与工程专业)材料力学2003(注:试卷上面标注的是:车辆工程、机械制造及自动化、机械电子工程、机械设计及理论、固体力学专业)材料力学C 2010(注:试卷上面标注的是:车辆工程、物流工程、机械工程专业)材料力学C 2004——2008(注:试卷上面标注的是:车辆工程、机械制造及自动化、机械电子工程、机械设计及理论、机械工程、物流工程、机械装备及控制专业)材料力学D 2004——2005,2007——2010(注:试卷上面标注的是:固体力学专业)钢筋混凝土结构2003——2005单考数学2003——2004,2008——2010单考俄语2008——2010单考英语2008——2010单考政治2008——2010下面是余秋雨经典励志语录,欢迎阅读。

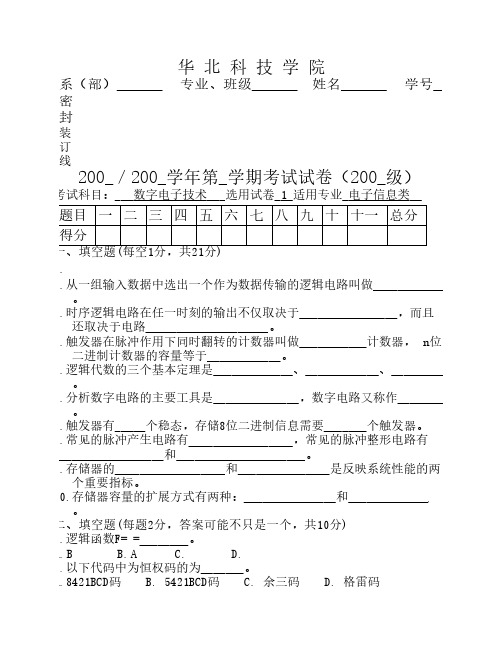

《数字电子技术》第一套试题

华 北 科 技 学 院系(部)专业、班级姓名学号密封装订线200 /200 学年第 学期考试试卷(200 级)考试科目: 数字电子技术 选用试卷 1 适用专业 电子信息类题目一二三四五六七八九十十一总分得分一、填空题(每空1分,共21分)1.2.从一组输入数据中选出一个作为数据传输的逻辑电路叫做。

3.时序逻辑电路在任一时刻的输出不仅取决于 ,而且还取决于电路 。

4.触发器在脉冲作用下同时翻转的计数器叫做 计数器, n位二进制计数器的容量等于 。

5.逻辑代数的三个基本定理是 、 、。

6.分析数字电路的主要工具是 ,数字电路又称作。

7.触发器有 个稳态,存储8位二进制信息需要 个触发器。

8.常见的脉冲产生电路有 ,常见的脉冲整形电路有和 。

9.存储器的 和 是反映系统性能的两个重要指标。

10.存储器容量的扩展方式有两种: 和。

二、填空题(每题2分,答案可能不只是一个,共10分)1.逻辑函数F= = 。

A.BB.AC.D.2.以下代码中为恒权码的为 。

A.8421BCD码B. 5421BCD码C. 余三码D. 格雷码题号12345678910答案 3.CMOS数字集成电路与TTL数字集成电路相比突出的优点是 。

A.微功耗B.高速度C.高抗干扰能力D.电源范围宽4.对于T触发器,若原态Q n =0,欲使新态Q n +1=1,应使输入T= 。

A.0B.1C.QD.5.为实现将JK触发器转换为D触发器,应使 。

A.J=D,K=B. K=D,J=C.J=K=DD.J=K=三、判断题(每题1分,共10分,正确的用T表示,错误的用F表示,请将答案填在下面的方格内)1.因为逻辑表达式A+B+AB=A+B成立,所以AB=0成立。

2.若两个函数具有相同的真值表,则两个逻辑函数必然相等。

3.格雷码具有任何相邻码只有一位码元不同的特性。

4.一般TTL门电路的输出端可以直接相连,实现线与。

5.TTL与非门的多余输入端可以接固定高电平。

(完整word版)数字电子技术试题及答案(题库)

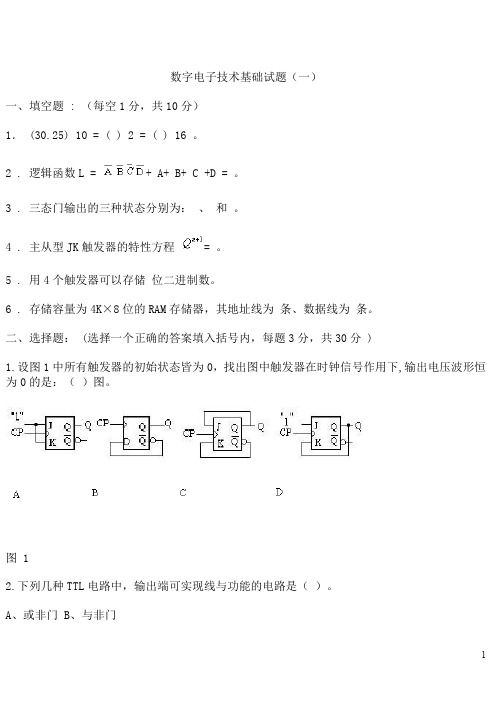

数字电子技术基础试题(一)一、填空题 : (每空1分,共10分)1. (30.25) 10 = ( ) 2 = ( ) 16 。

2 . 逻辑函数L = + A+ B+ C +D = 。

3 . 三态门输出的三种状态分别为:、和。

4 . 主从型JK触发器的特性方程= 。

5 . 用4个触发器可以存储位二进制数。

6 . 存储容量为4K×8位的RAM存储器,其地址线为条、数据线为条。

二、选择题: (选择一个正确的答案填入括号内,每题3分,共30分 )1.设图1中所有触发器的初始状态皆为0,找出图中触发器在时钟信号作用下,输出电压波形恒为0的是:()图。

图 12.下列几种TTL电路中,输出端可实现线与功能的电路是()。

A、或非门B、与非门C、异或门D、OC门3.对CMOS与非门电路,其多余输入端正确的处理方法是()。

A、通过大电阻接地(>1.5KΩ)B、悬空C、通过小电阻接地(<1KΩ)D、通过电阻接V CC4.图2所示电路为由555定时器构成的()。

A、施密特触发器B、多谐振荡器C、单稳态触发器D、T触发器5.请判断以下哪个电路不是时序逻辑电路()。

图2A、计数器B、寄存器C、译码器D、触发器6.下列几种A/D转换器中,转换速度最快的是()。

图2A、并行A/D转换器B、计数型A/D转换器C、逐次渐进型A/D转换器D、双积分A/D转换器7.某电路的输入波形 u I 和输出波形 u O 如图 3所示,则该电路为()。

图3A、施密特触发器B、反相器C、单稳态触发器D、JK触发器8.要将方波脉冲的周期扩展10倍,可采用()。

A、10级施密特触发器B、10位二进制计数器C、十进制计数器D、10位D/A转换器9、已知逻辑函数与其相等的函数为()。

A、B、C、D、10、一个数据选择器的地址输入端有3个时,最多可以有()个数据信号输出。

A、4B、6C、8D、16三、逻辑函数化简(每题5分,共10分)1、用代数法化简为最简与或式Y= A +2、用卡诺图法化简为最简或与式Y= + C +A D,约束条件:A C + A CD+AB=0四、分析下列电路。

北京科技大学817模拟电子技术与数字电子技术基础2004-2014历年考研真题汇编

北京科技大学2011年硕士学位研究生入学考试试题=============================================================================================================试题编号: 817 试题名称:模拟电子技术与数字电子技术基础(共10页)适用专业:物理电子学说明:所有答案必须写在答题纸上,做在试题或草稿纸上无效。

=============================================================================================================一、(23分)选择填空,将正确答案写在答题纸上。

1.二极管的主要特点是具有()。

A 电流放大作用B 单向导电性C 稳压作用2.电路如图1,设 D Z1的稳定电压为 6 V,D Z2的稳定电压为 12V,设稳压管的正向压降为 0.7 V,则输出电压U o等于()。

图1 第2题图A. 18V; B 6.7V;C 12.7V; D 6V3.微变等效电路法适用于放大电路的()。

A 动态分析B 静态分析C 静态和动态分析4.对图2所示电路的描述,正确的是()。

A 可以构成复合管,等效成NPN管;B 可以构成复合管,等效成PNP管;C 不能构成复合管图2 第4题图5.图3电路中,电阻R E的作用是()。

图3 第5题图A 仅对共模信号起负反馈作用;B 仅对差模信号起负反馈作用;C 对共模、差模信号都起负反馈作用;D 对共模、差模信号都无负反馈作用;6.集成运放电路采用直接耦合方式是因为()。

A 可获得很大的放大倍数B 可使温漂减小C 集成工艺难于制造大容量电容7.直接耦合放大电路在高频时,其放大倍数与中频时相比会()。

A 增大B 降低C 不变8.在输入量不变的情况下,若引入反馈后(),则说明引入的反馈是负反馈。

数字电子技术复习题 (1)

目录

简答题 ........................................................................................................................................... 2 计算题 ........................................................................................................................................... 3 分析题 ........................................................................................................................................... 6 设计题 ......................................................................................................................................... 13

答案:

F1 = ( A B) AB + AB + AB

= ( AB + AB)( AB + AB) + AB

1)

;

= AB + AB + AB

= A+B

F 2 = A + B + CD + AD B 2) = A + BCD + AD + B