ADI征文_ADF4360-9使用笔记

基于ADF4360-1的本振源设计

基于ADF4360-1的本振源设计作者:邹玲石小磊来源:《现代电子技术》2009年第21期摘要:结合锁相频率合成基本原理以及高集成锁相频率合成芯片ADF4360-1工作特性,设计一个稳定的2.33 GHz本振源电路模块,应用于中频射频发信机中。

详细介绍了核心芯片的结构、原理及应用,并给出完整的硬件电路。

经仿真测试,该电路的性能指标基本符合要求。

关键词:锁相环频率合成;ADF4360-1;本振;环路滤波器中图分类号:TN742 文献标识码:A文章编号:1004-373X(2009)21-071-03Design of Clock Signal Generator Based on ADF4360-1ZOU Ling,SHI Xiaolei(School of Electrical and Electronic Engineering,Hubei University ofTechnology,Wuhan,430068,China)Abstract:The principle of phase locked loop and the performance characteristics of fully integrated voltage-controlled oscillator ADF4360-1 are analyzed.A design of a stedy 2.33 GHz local oscillator signal generator circuit module is applied to the system of Intermediate Frequency(IF).The paper elaborates on the structure,performance and application of the core chip,designs the hardware circuit.The simulation and measure of the system show that the result is correct basically.Keywords:PLL frequency synthesis;ADF4360-1;local oscillation;loop filter0 引言在无线通信领域,本振信号性能的优劣是影响混频器输出频谱纯度的主要因素。

ADF4360使用

ADF4360-x是ADI公司推出的一系列的锁相环(Complete Phase Locked Loop)。

和其他锁相环芯片如ADF4106相比,ADF4360-x在片内集成了VCO(V oltage Controlled Oscillator)。

这一点非常重要,因为一般情况下我们要使用一个外置的VCO,这些模块有可能是自己使用三极管、调谐二极管、电感等器件自己搭建的。

但更多情况下,为了降低设计难度,提高各种性能,我们则是购买集成VCO 模块。

这些模块非常昂贵,小批量的情况下单颗价格往往在300元以上,而且体积已经有指甲片般大了。

那些对成本、空间要求很高的通信电子产品往往无法接受这样的VCO。

近几年,随着MMIC技术的发展,基于MMIC的VCO技术已经变得非常成熟。

其中Maxim很早就推出了相关的产品,比如MAX2753和MAX2624。

而Analog Devices并没有单独推出VCO MMIC的产品,而是将VCO 和锁相环的其他部分(除了环路滤波器以外)集成在了一起,针对不同的频段推出了一系列的锁相环,从ADF4360-0 ~ ADF4360-8。

这些芯片几乎相同的引脚定义,同时内部控制寄存器每一位的定义也完全相同。

由于将VCO集成到了芯片内部,使得整个PLL系统的面积大大减小(至少50%以上),而且成本也得到了有效控制。

ADF4360系列锁相环中,ADF4360-7和-8需要在片外设置两个电感来确定VCO所处的频段,相当于将VCO的电感部分移出至片外。

两个0603的电感并没有占据太大体积,但有两点必须注意:一个是电感到ADF4360芯片之间以及到接地平面之间的连线必须尽可能的短,而且电感必须使用线绕试的(比如使用Coilcraft 0603CS系列的RF电感。

如果使用普通叠层电感的话,VCO基本上不能起振)。

另一个问题就是ADF4360的每一个电源引脚一定要分别使用102和104的瓷片电容去偶。

ADF中文教程:ADF参数设置详解

费米科技

费米科技

Model

Constraint DFT:如果正确的设置了片段(设置片段的方式,参考费米科技 WIKI 中“ADF 知识库” :如何进行分区计算:QMMM、QUILD 的使用中对应的部分) , 那么在此处可以为每个片段单独设置电荷。点击 Change Constraints 之后,在 Region 下拉框选择要设置的区域,然后在 Charge 里面为该区域指定电荷。

Minimum Energy Crossing Point:计算 MECP 的设置 Nudged Elastic Band:使用 NEB 方法搜索过渡态。ADF 原先有更为精确的过渡 态搜索方法。 此处的 NEB 方法是一种比较粗糙的过渡态搜索方法。 但该方法很流行。

Region:设置片段。参考费米科技 WIKI 中“ADF 知识库” :如何进行分区计算: QMMM、QUILD 的使用中对应的部分。

Geometry Opt & Freqs:对分子进行结构优化,完成之后,自动计算优化好的那 个结构的频率。如此就可以检查是不是存在负的频率(也就是所谓的虚频)

Linear Transit:线性过渡。其用途参考费米科技 WIKI 中“ADF 知识库” :ADF 搜 索过渡态典型案例

Transition State Search:过渡态搜索。其用途参考费米科技 WIKI 中“ADF 知识 库” :ADF 搜索过渡态典型案例

Single Point:计算某一种分子结构的性质(比如计算 HOMO、LUMO,或者吸收 光谱、NMR 性质等等) ,之所以叫做单点,是指这种性质只由当前的这种结构就可 以计算出来。其他选项,例如 Fragment Analysis、Properties Only、Strict 选项 实际上等同于选择 Single Point,具体可以参考费米科技 WIKI 中“ADF 知识库” : 如何计算 HOMO、LUMO、文献重现:锌酞菁的基态与激发态计算(第二部分) 、 如何计算 NMR Shielding 化学位移

基于ADF4360-1的2.4G频率合成器设计

基于ADF4360-1的2.4G频率合成器设计作者:杨婧来源:《科技创新导报》 2013年第1期杨婧(中北大学信息探测与处理技术研究所山西太原 030051)摘?要:该文通过高性能、低功耗的8位ATmega8微处理器产生控制信号,利用美国ADI公司生产的锁相环芯片ADF4360-1,设计了一个稳定的2.4?GHz本振信号源电路模块,可广泛应用于电视,仪器,通信等领域。

文中详细介绍了系统中核心芯片的性能、结构以及应用方法,设计出了完整的硬件电路并对电路的各个参数进行了评估,结果基本上符合要求。

关键词:ATmega8 ADF4360-1?锁相环频率合成?本振信号源中图分类号:TN742 文献标识码:A 文章编号:1674-098X(2013)01(a)-00-01在现代无线电通信及相关领域中,为确保通信的稳定和可靠,对通信设备的频率准确度和稳定度提出了越来越高的要求。

与LC振荡电路“跑频”严重相比,晶体振荡电路具有可微调的稳定频率,但变化范围小,频率值不高。

频率合成技术是指将一个或少量的高稳定度、高准确度的标准频率作为参考频率,经过相应的信号处理过程,从而获得大量离散的具有同一稳定度和准确度的信号频率。

主要有三种合成方法:直接模拟合成、锁相环合成以及直接数字合成。

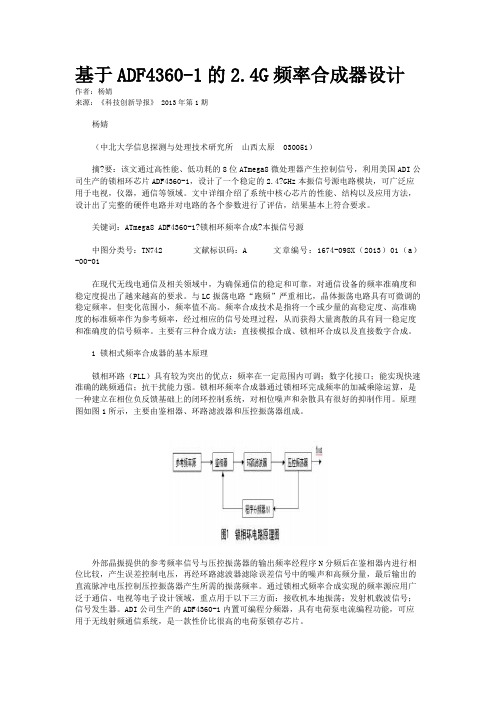

1 锁相式频率合成器的基本原理锁相环路(PLL)具有较为突出的优点:频率在一定范围内可调;数字化接口;能实现快速准确的跳频通信;抗干扰能力强。

锁相环频率合成器通过锁相环完成频率的加减乘除运算,是一种建立在相位负反馈基础上的闭环控制系统,对相位噪声和杂散具有很好的抑制作用。

原理图如图1所示,主要由鉴相器、环路滤波器和压控振荡器组成。

外部晶振提供的参考频率信号与压控振荡器的输出频率经程序N分频后在鉴相器内进行相位比较,产生误差控制电压,再经环路滤波器滤除误差信号中的噪声和高频分量,最后输出的直流脉冲电压控制压控振荡器产生所需的振荡频率。

通过锁相式频率合成实现的频率源应用广泛于通信、电视等电子设计领域,重点用于以下三方面:接收机本地振荡;发射机载波信号;信号发生器。

基于ADF4360

本电路设计中,ADF4360-2 的 PFD 输入频率为 1MHz,因此参考时 钟分频 R=40。由公式 fVCO=(B&TImes;P+A)乘以 fREFIN/R,可计算出 N 为 11250,双模预频器设置为 P/(P+1)=32/33,计数器 A 设置为 8,计数器 B 设 置为 32。根据 ADF4360-2 芯片资料,3 个控制寄存器初始化设置为 R 寄存器 00000A1H,C 寄存器 8FF12CH,N 寄存器 803E42H,配置值如表 1 所列。 单片机通过提供时钟信号 CLK、数据信号 DATA 和使能信号 LE,对 ADF4360-2 内部寄存器进行配置,使得 VCO 输出所需频率的信号,同时负 责对 ADF4360-2 的锁定标志进行检测,如果检测已经锁定,则配置数据工作 完成。单片机程序流程如图 3 所示。

结语 本文介绍了利用锁相频率合成芯片 ADF4360-2 设计 1GHz 信号的输 出方法,给出了电路系统结构框图以及单片机程序流程。由于 ADF4360-2 内 部集成 VCO,外部通过单片机 I/O 口写入控制字,因此该系统具有外围电路 简单、调试方便、功耗和成本低等特点,可广泛应用于各种电路系统中。

◆能够进行模拟与数字锁定检测; ◆支持软件和硬件掉电功能。 ADF4360-2 的功能模块图如图 1 所示。它主要由一个 14 位可编程参 考 R 计数器、一个 24 位数据寄存器、一个 24 位功能锁存器、压控振荡器、 相位比较器、锁定检测器、多路外部频率源信号和单片机控制信号,14 位可编程参考 R 分频器 对外部频率源信号分频后,得到参考频率送至鉴相器。控制信号由时钟信号 CLK、数据信号 DATA 和使能信号 LE 组成。在 CLK 的控制下,串行输入

ADF4360-7压控振荡器要点

通信原理课程设计课程名称:基于ADF4360-7的集成整形N合成器的压控振荡器指导老师:专业:班级:姓名:学号:摘要:ADF4360-7是一款整合了整形N合成器的压控振荡发生器(VCO)。

ADF4360-7的中心频率是由外部传感器进行设定的。

其允许频率范围从350MHz到1800MHz。

另外可以选择使用2分频,则用户接受的射频输出信号频率范围在175MHz到900MHz。

全部片内寄存器都是由一个简单的3线接口来控制的。

设备操作电压范围从3.0V到3.6V并且在不使用时可以随时关闭。

Abstract:The ADF4360-7 is an integrated integer-N synthesizer and voltage controlled oscillator (VCO). The ADF4360-7 center frequency is set by external inductors. This allows a frequency range of between 350 MHz to 1800 MHz. In addition, a divide-by-2 option is available, whereby the user receives an RF output of between 175 MHz and 900 MHz. Control of all the on-chip registers is through a simple 3-wire interface. The device operates with a power supply ranging from 3.0 V to 3.6 V and can be powered down when not in use.关键词:压控振荡器、合成器、频率、结构、功能Key words: VCO、synthesizer 、frequency、configuration、function目录集成整形N合成器的压控振荡器 (5)芯片特性 (5)应用范围 (5)技术规范 (6)时序特性 (7)极限工作范围 (8)管脚结构和功能描述 (9)典型工作特性 (11)电路说明 (17)参考输入部分 (17)比例器 (17)A,B计数器 (17)R 计数器 (18)PFD和CHARGE PUMP (18)MUXOUT和LOCK DETECT (19)输入转换寄存器 (20)压控振荡器VCO (20)锁存器结构 (23)开机 (26)控制写入 (28)N计数器写入 (30)R计数器写入 (30)ADF4360-7的应用 (32)外观尺寸 (39)集成整形N合成器的压控振荡器芯片特性:输出频率范围:350MHz 到 1800MHz2分频输出电源 3.0V 到 3.6V逻辑兼容 1.8V*整形N合成器可编程双模比例器 8/9,16/17可编程输出电平三线接口逻辑锁与数字锁检测硬件及软件关闭模式应用范围:手持无线通信(DECT, GSM, PCS, DCS, WCDMA)测试设备;无线局域网;有线电视设备技术规范:AV DD = DV DD = V VCO= 3.3 V ± 10%; AGND = DGND = 0 V;TA = T MIN to T MAX表11.工作温度范围 -40°C to +85°C2.设计保证符合样值3.ICP内部参数使整个频率范围保持环路增益不变4.T A= 25°C; AV DD= DV DD= V VCO= 3.3 V;P = 325.这些特征是为了保证VCO核心电流=15mA6.变频范围1.45G—1.75G,PFD频率200kHZ,环路带宽10kHz7.V VCO用50Ω负载电阻8.VCO的噪声在开环下测量9.合成器固有噪声通过测量VCO带内的相位噪声输出功率减去20logN(N为对频率的分频值)10.相位噪声符合EVAL-adf4360-xEB1和HP8562E频谱分析仪, 频谱分析仪用来测量合成器输出, 偏移频率=1kHz11.f REFIN=10 MHz;f PFD=200kHz;N=8000;环B/W=10kHz12.f REFIN=10 MHz;f PFD=1MHz;N=1600;环B/W=25kHz13.寄生信号符合EVAL-adf4360-xEB1和HP8562E频谱分析仪, 频谱分析仪用来测量合成器输出, f REFOUT = 10 MHz时序特性AV DD = DV DD = V VCO= 3.3 V ± 10%;AGND = DGND = 0 V;1.8 V and 3 V logic levels used;T A = T MIN to T MAX表2图2 时序特性表极限工作范围T A= 25°C,其它另做说明表3GND = AGND = DGND = 0 V.当芯片工作在高于以上所列的最大工作范围时将可能造成设备的损坏。

基于ADF4360-3的本振信号发生器的设计

12 工 作 原 理 _

[ 尸}日私 ] R xr E

() 2

其 中 ,。 为 V f。 v CO 的输 出 频 率 ; 前 置 分 频 器 的 预 先模 值 P为 (/ 、 6 1 8 9 1 / 7等 )B 为 1 计 数 器 预 设 分 频 比 ( - 1 1 ; 为 ; 3位 3 8 9 )A

《 业 控 制 计 算 机 } 0 2年第 2 工 21 5卷 第 2期

3 1

基于 A F 3 0 3的本振信号发生器的设计 D 46—

De i f L c lS g a n r t r B s d o sgn o o a i n lGe e a o a e n ADF 3 0- 46 3

盛

君 ’ 陈毅 华 于 玮 。 陆 毅 ’

( 江 苏技 术师 范 学院 电气信 息工程 学 院, 苏 常 州 2 3 0 ; 南京 邮电大 学 电子 科 学与工程 学院 , 1 江 10 0 2 江 苏 南京 2 0 0 ; 南京林 业 大学信 息科 学技 术学 院 , 苏 南京 2 0 3 ) 1033 江 1 0 7

ph s l k d lop nd h pef r a e oc e o a t e ro man e haacer t s c c r t i i of ul it a e v t e—co tol d sc f l negrt d ol y ag n r l os l t ADF 3 e ciaor l 4 60— a a 3.nd se y .G Hz o l i al en  ̄ o cr i i de i e Th n hi t ad 19 lca sgn g er r i t s cu sgn d. e t s pap ab ats on t e s rct e。ero man e n appi erel or e h tu ur p f r c a d l — c t o h r hi L s l h mea ur f te i i h ws t tt e ph e oie s -83 ai on ft e co e c p.a t te y s e o h cr t o ha h as n s i cu s dBc /Hz 1 k @ 00 Hz.

一种有源微波近场成像系统

一种有源微波近场成像系统吕建新;王志刚;朱肇轩【摘要】The microwave near-field imaging system is introduced in this article, which is designed on the basis of 2.45 GHz continuous wave signal and can be applied to breast-cancer detection and imaging. The design mainly includes the circuits of hardware and the algorithm of imaging. The circuits are designed using the RF and microwave integrated chip which is of small volume, high performance and low-cost, and consist of three modules, i.e., antenna, transceiver and data acquisition and control module. The algorithm is designed using finite-element microwavernconfocal imaging. Finally, the detection and imaging of target are realized.%针对早期乳腺癌检测等近场目标的探测成像,设计了一种基于2.45GHz连续波信号的微波近场成像实验系统,主要由硬件电路和成像算法组成.系统电路用小体积、高性能和低成本的射频微波集成芯片实现,大大缩小了系统的体积并降低了成本,电路由天线模块、收发模块和数据采集控制模块构成.成像算法采用有限元微波共焦算法,完成对被测区域日标的探测成像.【期刊名称】《中国测试》【年(卷),期】2012(038)004【总页数】4页(P65-68)【关键词】微波成像;天线;近场成像;有限元共焦算法【作者】吕建新;王志刚;朱肇轩【作者单位】电子科技大学自动化工程学院,四川成都611731;电子科技大学自动化工程学院,四川成都611731;电子科技大学自动化工程学院,四川成都611731【正文语种】中文【中图分类】O431.1;TN82;TN247;TP273+.50 引言近年来,微波的近场成像受到越来越多研究者的关注,可应用于医学、安全等领域,如早期乳腺检测、安检系统等,有源微波近场成像技术主要有两种。

EVAL-ADF4360-6EB1中文资料

EVAL-ADF4360-6EB1中⽂资料aFEATURESSelf-Contained Board for generating RF frequencies Flexibility for Reference Input, Output frequency, PFD Spacing & Loop BandwidthAccompanying Software allows complete control of syn-thesizer functions from PC Battery Operated: 9V suppliesTypical Phase Noise Performance of -141dBc/Hz @ 3MHz offsetTypical Spurious Performance of -70dBc/Hz @ 200kHz offset.Analog Devices, Inc., 1999One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 781-329-4700Fax: 781-326-8703 Information furnished by Analog Devices is believed to be accurate and reliable. However,no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.Evaluation Board For ADF4360-6Integrated V CO & F requency S ynthesizerBLOCK DIAGRAMREV.PrC 08/03GENERAL DESCRIPTIONThis ADF4360-6EB1 Evaluation board is designed to allow the user to evaluate the performance of theADF4360-6 Frequency Synthesizers for PLL's (Phase Locked Loops). The block diagram of the board is shown below. It contains the ADF4360-6, a PC connector, plus SMA connectors for the power supplies, Reference Input, and RF outputs. It also contains a loop filter to complete the PLL. The eval board can be setup as necessary for the customer's PLL requirements. A cable is included with the board to connect to a PC printer port to allow software programmability.The package also contains windows software to allow easy programming of the synthesizer.RF OUT BINRF OUT A V VREV.PrC 08/03–2–Figure 1. Evaluation Board Silkscreen Figure 2. PC Cable DiagramHard ware DescriptionThe evaluation board comes with a cable for connecting to the printer port of a PC. The silk screen and cable diagram for the evaluation board are shown below. The board schematic is shown on pages 3 and 4.The board is powered from a single 9V battery.All components necessary for LO generation are catered for on-board. A 10MHz TCXO from Fox provides the necessary Reference Input. Otherwise an External Reference signal can be connected via SMA1.The PLL comprises the ADF4360-6 and a passive loop filter. The VCO outputs are available at RF OUT A through a standard SMA connector, plus the complementary VCO output is available from RF OUT B complementary connector.If the user wishes they may use their own power supplies and reference input, they can use the SMA connectors as shown on the silkscreen and block diagram. Control of the Chip Enable pin can be achieved by inserting J7, and removing R12. The on board filter is a Third Order,Passive Low Pass Filter. This contains three capacitors,(C13, C14 & C15), plus two resistors (R10 & R11). To save Board space, The footprint for R10 is located on the underside of the board. For design of the loop filter, It is designed for a centre frequency of 1.15GHz, and a channel spacing of 200kHz. The charge pump current setting is chosen to be 2.5mA. It's bandwidth is 10kHz.To design a filter for different setups, Please use ADIsimPLL.ADI SimPLLA copy of ADIsimPLL is also included on the eval kit CD. This software package designs, simulates and analyses the entire frequency domain and time domain response. You can use it to design an appropriate filter for the PLL. Various passive and active filter architectures are allowed.RF OUTPUT STAGESThe output RF stages can be customised to suit therequirements of the end-user. A tuned load, consisting of a 51nH shunt Inductor for each output (L5 & L6) isconnected to to Vvco. A series 2.7pF coupling capacitor (C17 & C19) is included plus a series 7.5nH Inductor (L3& L4) before the RF output to the SMA connector. This can be changed to optimise tuning to the desired fundamental frequency.If in doubt, a 50Ohm resistor can replace the shunt Inductor, and a zero-ohm link can short out L3 & L4.ADF4360-x CABLE CONNECTIONSPC Printer PortIf the the version of version of ADIsimPLL that you are using is not configured for the ADF4360-6, then you can design the loop filter by selecting the ADF4106 as a synthesizer and inserting all other relevant parametersfrom the ADF4360-6 datasheet. Be careful to note that the charge pump current is half that of the ADF4106.Figure 3. Evaluation Board Circuit Diagram (Page 1)–3–REV.PrC 08/03Figure 4. Evaluation Board Circuit Diagram (Page 2)REV.PrC 08/03–4––5–REV.PrC 08/03Figure 5. Software Front PanelSoftware DescriptionThe software comes on a CD. If the user double clicks on “setup.exe”, then the install wizard installs the software.Follow the on-screen directions. The software will be installed in a default directory called “C:/Program Files/Analog Devices/ADF4360”. To run the software, simply double-click on “ADF4360.exe”. It should be noted that this is a beta-version of software for the ADF4360.Before the main software screen appears, the Device win-dow appears, which will ask the user to choose which de-vice is being evaluated. Choose the appropriate version of the ADF4360 and click OK. The Main Interface window will now appear. (See Figure 5).Programmable Software SettingsClick on RF VCO Output Frequency, and the Output Frequency window will appear. Enter the desired output frequency (in MHz) and also the desired PFD frequency (in kHz) and click OK.Click on Reference Frequency and Insert the desired frequency in MHz, Again click OK.Click On Prescaler, and the Prescaler window will appear.Grab the pointer, and choose the appropriate setting (Again Click OK).Click on Charge Pump Current Setting 2 or Charge Pump Current Setting 1 and the Current Setting window will appear. Grab the pointer to set the Charge Pump Current Setting to the appropriate setting based on the loop design.It will be necessary to adjust the core power current to 15mA and and the output power current to give optimum operation. These settings are clearly marked in the window shown below.Click on the RF PD Polarity button to set the RF PD Polarity bit positive.The part should now be now set up, and other features can now be examined by the user. To examine the contents written to each register, the Registers button can be selected below. As stated on the part's datasheet, The Correct sequence of Register writes is to the R Counter,The Function Latch and finally the NCounter Latch.Table 1. Bill of Materials for the EVAL-ADF4360-6EB1REV.PrC 08/03–6–。

基于ADF4360_4锁相频率合成器的混频器本振源电路设计

0引言锁相(PhaseLock)技术是一种相位负反馈频率控制技术,该技术在锁定时无剩余频差,并具有良好的窄带载波跟踪性能和带宽调制跟踪性能,而且对相位噪声和杂散也具有很好的抑制作用。

因此,通过锁相频率合成技术实现的频率源已在通信、电视等领域得了广泛应用。

本文介绍的ADl 公司的ADF4360系列芯片就是用于无线通信射频系统(GSM,DECT,PCS,WCDMA。

DCS)基站和WLAN混频电路的一款性价比很高,且应用范围较广的锁相芯片。

1ADF4360_4的性能特点ADF4360_4丰要由数字鉴相器、电荷泵、R分频器、A,B计数器及双模前置P/P+1分频器等组成。

数字鉴相器对R计数器与N计数器的输出信号进行相位比较,得到一个误差电压。

14bit可编程参考R分频器对外部晶振分频后得到参考频率。

该器件可以通过可编程6位A计数器、13位B计数器及双模前置分频器(P/P+1)来共同完成主分频比N(N=BP+A)。

因此,设计时只需外加环路滤波器,并选择合适的参考值,即可获得稳定的频率输出,其输出频率为:f0=fvco=N(fi/R)式中,fi为参考频率,它可由高稳定度晶体振荡器提供。

而其鉴相频率fr为:fr=fi/R其中,fi应小于8MHz。

ADF4360_4是美国ADI公司生产的的高性能锁相频率合成芯片,主要用于无线发射机和接收机中为上下变频提供本振信号。

该器件的主要特点如下:(1)该合成器的输出频率范围为1450~1750MHz;并可选择二分频。

选择二分频时,可输出725~875MHz的频率信号;(2)工作电压为3~3.6V;(3)合成器的输出信号的功率可控制范围为-13~-4dbm;(4)可编程双模前置分频器的分频比为8/9、16/17、32/33等;(5)能够进行模拟和数字锁定检测;(6)芯片内部集成又VCO。

ADF4360_4是一款双模前置分频型单环频率合成器,该器件可在不改变频率分辨率的同时,有效地提高频率合成器的输山频率。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ADI征文_ADF4360-9使用笔记

去年年底,公司的一块时钟单板,需要从恒温晶振的时钟频率产生一些其它的输出频率,以支持多种设备。

为了简化设计,计划选用集成VCO的频率合成器,由于输出的时钟频率不高,可选的范围也比较有限。

在ADI和TI的网站筛选了下,最终选择了ADI的ADF4360-9。

选定器件之后,便是根据输出频率确定鉴相器频率和环路滤波器带宽,这时候使用ADIsimPLL确定了环路滤波器的器件参数,再参照datasheet和官方评估板EV ALZ-ADF4360-9的原理图,很快确定了整个ADF4360-9的外围电路。

中间需要注意的是,用于确定VCO工作频段的外部电感,最好要选用高Q值的绕线电感。

这点自己做过VCO 的应该都知道,谐振回路的Q值不够,会导致振荡器无法起振。

板子焊好拿回来之后,应用官方评估板的配套评估软件,设置完成后很方便地就生成了寄存器的数值,不用对照着datasheet一位一位地去计算。

这点ADI做得非常好,我在后面调试ADF4350的时候也是这么干的,非常快速便捷。

通过单片机的SPI接口,将寄存器配置送到ADF4360-9之后,VCO就起振了,PLL也锁定了。

在后来的调试过程中,发现一个问题:PLL周期性地发生短暂的失锁,但是很快就恢复到锁定状态。

用示波器量了一下这个周期,是0.1秒,我很快就大致确定了问题可能的原因。

我是在单片机的定时器中断程序里定时发送一次SPI配置数据,以动态刷新频率合成器的配置参数,这样在输出频率设置发生变化时,频率合成器可以很快地切换到新的频点上去。

而正好,这个刷新周期与PLL失锁的周期完全一样。

查阅datasheet之后发现,只要N 计数器发生更新,VCO频段选择电路就会重新判断VCO的工作频段,这个期间,VCO的V TUNE将会从环路滤波器的输出上断开,连到片内的参考电压上。

这当然会导致PLL的失锁。

于是修改了单片机软件,每次定时器中断,都比较频率合成器配置寄存器的数值,如果没有发生变化,就不通过SPI接口刷新数据。

修改之后,问题解决。